# **Microprocessor Monitor**

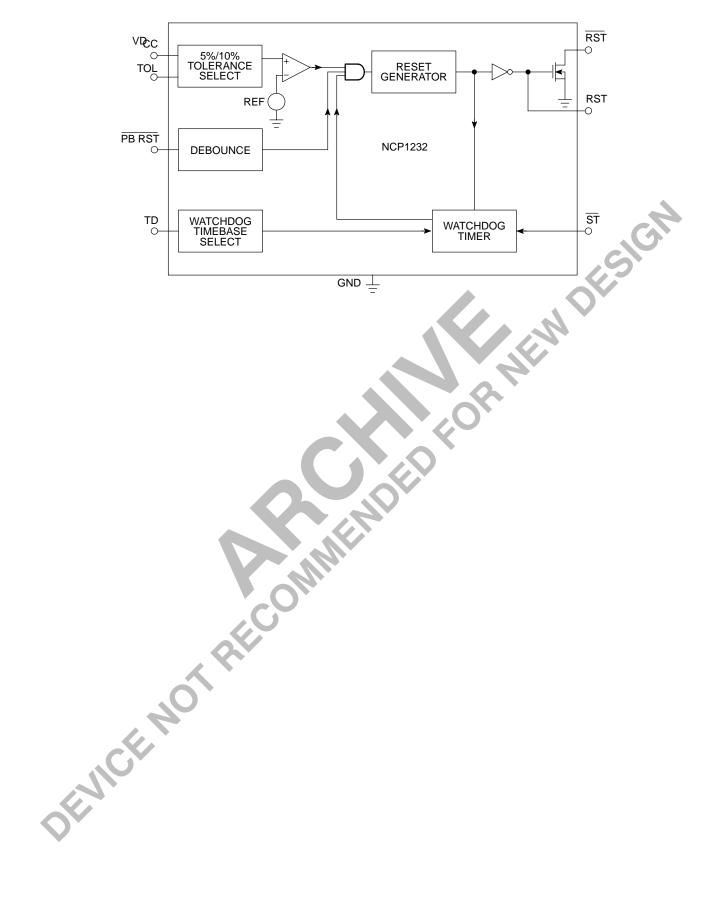

The NCP1232 is a fully-integrated processor supervisor. It provides three important functions to safeguard processor functionality: precision power on/off reset control, watchdog timer and external reset override.

On power-up, the NCP1232 holds the processor in the reset state for a minimum of 250 msec after  $V_{CC}$  is within tolerance to ensure a stable system start-up.

Microprocessor functionality is monitored by the on-board watchdog circuit. The microprocessor must provide a periodic low-going signal on the  $\overline{ST}$  input. Should the processor fail to supply this signal within the selected time-out period (150 msec, 600 msec or 1200 msec), an out-of-control processor is indicated and the NCP1232 issues a processor reset as a result.

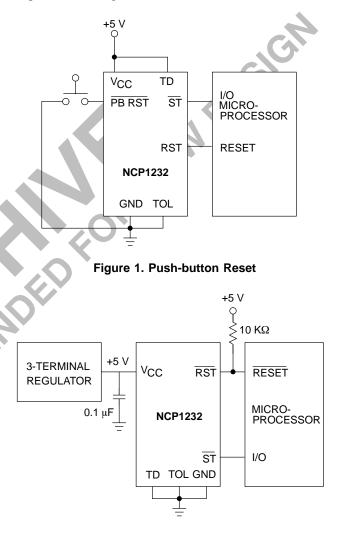

The outputs of the NCP1232 are immediately driven active when the PB input is brought low by an external push-button switch or other electronic signal. When connected to a push-button switch, the NCP1232 provides contact debounce.

The NCP1232 is packaged in a space-saving 8-pin plastic SOIC package and requires no external components.

, coi

### Features

- Precision Voltage Monitor (Adjustable +4.5 V or +4.75 V)

- Reset Pulse Width (250 msec Min)

- No External Components

- Adjustable Watchdog Timer (150 msec, 600 msec or 1.2 sec)

- Debounced Manual Reset Input for External Override

## Applications

- Computers

- Controllers

- Intelligent Instruments

- Automotive Systems

- Critical µP Power Monitoring

# ON Semiconductor<sup>®</sup>

http://onsemi.com

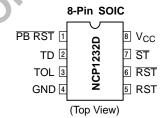

# PIN CONNECTIONS

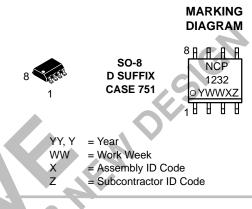

## **ORDERING INFORMATION**

| Device     | Package | Shipping         |  |  |

|------------|---------|------------------|--|--|

| NCP1232DR2 | SO-8    | 2500 Tape & Reel |  |  |

## FUNCTIONAL BLOCK DIAGRAM

# **PIN DESCRIPTION**

| (8-Pin SOIC) | Symbol          | Description                                                                                                                                                                                                                                                                      |

|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

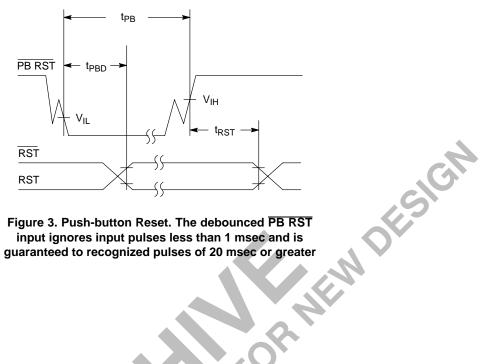

| 1            | PB RST          | Push-button Reset Input. A debounced active-low input that ignores pulses less than 1 msec duration and is guaranteed to recognize inputs of 20 msec or greater.                                                                                                                 |

| 2            | TD              | Time Delay Set. The watchdog time-out select input ( $t_{TD}$ = 150 msec for TD = 0 V, $t_{TD}$ = 600 msec for TD = open, $t_{TD}$ = 1.2 sec for TD = V <sub>CC</sub> .)                                                                                                         |

| 3            | TOL             | Tolerance Input. Connect to GND for 5% tolerance or to $V_{CC}$ for 10% tolerance.                                                                                                                                                                                               |

| 4            | GND             | Ground.                                                                                                                                                                                                                                                                          |

| 5            | RST             | <ul> <li>Reset Output (Active High) - goes active:</li> <li>1. If V<sub>CC</sub> falls below the selected reset voltage threshold</li> <li>2. If PB RST is forced low</li> <li>3. If ST is not strobed within the minimum time-out period</li> <li>4. During power-up</li> </ul> |

| 6            | RST             | Reset Output (Active Low, Open Drain) - see RST.                                                                                                                                                                                                                                 |

| 7            | ST              | Strobe Input. Input for watchdog timer.                                                                                                                                                                                                                                          |

| 8            | V <sub>CC</sub> | The +5 V Power Supply Input.                                                                                                                                                                                                                                                     |

|              |                 | CEPE                                                                                                                                                                                                                                                                             |

| ENIC         | <i>E</i> NOT    |                                                                                                                                                                                                                                                                                  |

| OFNIC        | ENO             |                                                                                                                                                                                                                                                                                  |

#### ABSOLUTE MAXIMUM RATINGS\* Voltage on any pin (with respect to GND) -0.3 V to +5.8 V

| Rating                                      | Value       | Unit |

|---------------------------------------------|-------------|------|

| Operating Temperature Range                 | -40 to +85  | °C   |

| Storage Temperature Range, T <sub>stg</sub> | -65 to +150 | °C   |

| Lead Temperature (Soldering, 10 sec)        | +300        | °C   |

\*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS ( $T_A = T_{MIN}$ to $T_{MAX}$ ; $V_{CC} = +4.5$ V to 5.5 V, unless otherwise specified.)

| Characteristic                          | Symbol            | Test Conditions         | Min  | Тур  | Max                  | Unit |

|-----------------------------------------|-------------------|-------------------------|------|------|----------------------|------|

| Supply Voltage                          | V <sub>CC</sub>   | -                       | 4.5  | 5.0  | 5.5                  | V    |

| ST and PB RST Input High Level          | V <sub>IH</sub>   | Note 1                  | 2.0  | -    | V <sub>CC</sub> +0.3 | V    |

| ST and PB RST Input Low Level           | V <sub>IL</sub>   | -                       | -0.3 | -    | +0.8                 | V    |

| Input Leakage ST, TOL                   | ١L                | -                       | -1.0 | -    | +1.0                 | μA   |

| Output Current RST                      | I <sub>OH</sub>   | V <sub>OH</sub> = 2.4 V | -1.0 | -12  | 5                    | mA   |

| Current RST, RST                        | I <sub>OL</sub>   | V <sub>OL</sub> = 0.4 V | 2.0  | 10   | -                    | mA   |

| Operating Current                       | Icc               | Note 2                  | -    | 50   | 200                  | μΑ   |

| V <sub>CC</sub> 5% Trip Point (Note 3)  | V <sub>CCTP</sub> | TOL = GND               | 4.50 | 4.62 | 4.74                 | V    |

| V <sub>CC</sub> 10% Trip Point (Note 3) | V <sub>CCTP</sub> | $TOL = V_{CC}$          | 4.25 | 4.37 | 4.49                 | V    |

## **CAPACITANCE (Note 4)** (T<sub>A</sub> = +25°C)

| Characteristic              | Symbol           | Test Conditions | Min      | Тур | Max | Unit |

|-----------------------------|------------------|-----------------|----------|-----|-----|------|

| Input Capacitance ST, TOL   | C <sub>IN</sub>  |                 | <u>J</u> | -   | 5.0 | pF   |

| Output Capacitance RST, RST | C <sub>OUT</sub> |                 | -        | -   | 7.0 | pF   |

# AC ELECTRICAL CHARACTERISTICS ( $T_A = T_{MIN}$ to $T_{MAX}$ ; $V_{CC} = +5.0$ V to $\pm 10\%$ , unless otherwise specified.)

| Characteristic                                              | Symbol              | Test Conditions                                                       | Min                | Тур                | Max                 | Unit |

|-------------------------------------------------------------|---------------------|-----------------------------------------------------------------------|--------------------|--------------------|---------------------|------|

| PB RST (Note 5)                                             | t <sub>PB</sub>     | Figure 3                                                              | 20                 | -                  | -                   | msec |

| PB RST Delay                                                | t <sub>PBD</sub>    | Figure 3                                                              | 1.0                | 4.0                | 20                  | msec |

| Reset Active Time                                           | trst                | -                                                                     | 250                | 610                | 1000                | msec |

| ST Pulse Width                                              | t <sub>ST</sub>     | Figure 4                                                              | 20                 | -                  | -                   | nsec |

| ST Time-out Period                                          | C <sup>t</sup> TD . | Figure 4<br>TD Pin = 0 V<br>TD Pin = Open<br>TD Pin = V <sub>CC</sub> | 62.5<br>250<br>500 | 150<br>600<br>1200 | 250<br>1000<br>2000 | msec |

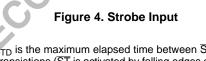

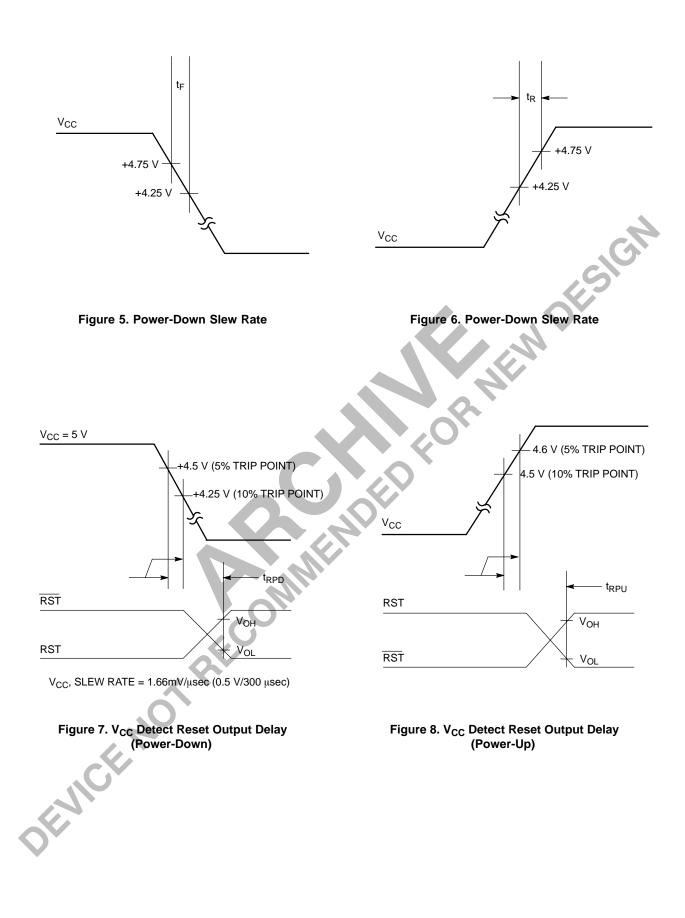

| V <sub>CC</sub> Fall Time (Note 4)                          | t <sub>F</sub>      | Figure 5                                                              | 10                 | -                  | -                   | μsec |

| V <sub>CC</sub> Rise Time (Note 4)                          | t <sub>R</sub>      | Figure 6                                                              | 0                  | -                  | -                   | μsec |

| V <sub>CC</sub> Detect to RST High and RST Low              | t <sub>RPD</sub>    | Figure 7, $V_{CC}$ Falling                                            | -                  | -                  | 100                 | nsec |

| V <sub>CC</sub> Detect to RST High and RST Open<br>(Note 6) | t <sub>RPU</sub>    | Figure 8, V <sub>CC</sub> Rising                                      | 250                | 610                | 1000                | msec |

1. PB RST is internally pulled up to  $V_{CC}$  with an internal impedance of typically 40 k $\!\Omega$

2. Measured with outputs open.

3. All voltages references to GND.

4. Guaranteed by design.

5. PB RST must be held low for a minimum of 20 msec to guarantee a reset.

6.  $t_{R} = 5 \,\mu sec.$

# **Power Monitor**

The NCP1232 detects out-of-tolerance power supply conditions and warns a processor-based system of an impending power failure. When  $V_{CC}$  is detected as below the preset level defined by TOL, the  $V_{CC}$  comparator outputs the signals RST and RST. If TOL is connected to ground, the RST and RST signals become active as  $V_{CC}$  falls below 4.75 volts. If TOL is connected to  $V_{CC}$ , the RST and RST become active as  $V_{CC}$  falls below 4.5 volts. Because the processing is stopped at the last possible moment of valid  $V_{CC}$ , the RST and RST are excellent control signals for a  $\mu$ P. The reset outputs will remain in their active states until  $V_{CC}$  has been continuously in-tolerance for a minimum of 250 msec allowing the power supply and  $\mu$ P to stabilize before RST is released.

# **Push-button Reset Input**

The debounced manual reset input ( $\overline{PB RST}$ ) manually forces the reset outputs into their active states. Once  $\overline{PB RST}$ has been low for a time, t<sub>PBD</sub>, the push-button delay time, the reset outputs go active. The reset outputs remain in their active states for a minimum of 250 msec after  $\overline{PB RST}$  rises above V<sub>IH</sub> (Figure 3).

A mechanical push-button or active logic signal can drive the  $\overline{PB}$  RST input. The debounced input ignores input pulses less than 1 msec and is guaranteed to recognize pulses of 20 msec or greater. No external pull-up resistor is required because the  $\overline{PB}$  RST input has an internal pull-up to V<sub>CC</sub> of approximately 100  $\mu A$ .

# Watchdog Timer

JENK

When the  $\overline{ST}$  input is not stimulated for a preset time period, the watchdog timer function forces RST and  $\overline{RST}$ signals to the active state. The preset time period is determined by the  $\overline{TD}$  inputs to be 150 msec with TD connected to ground, 600 msec with TD open, or 1200 msec with TD connected to V<sub>CC</sub>, typical. The watchdog timer starts timing out from the set time period as soon as RST and  $\overline{RST}$  are inactive. If a high-to-low transition occurs on the ST input pin prior to time-out, the watchdog timer is reset and begins to time-out, then the RST and  $\overline{RST}$  signals are driven to the active state for 250 msec minimum (Figure 2).

The software routine that strobes  $\overline{ST}$  is critical. The code must be in a section of software that is executed regularly so the time between toggles is less than the watchdog time-out period. One common technique controls the  $\mu$ P I/O line from two sections of the program. The software might set the I/O line high while operating in the foreground mode and set it low while in the background or interrupt mode. If both modes do not execute correctly, the watchdog timer issues reset pulses.

# **Supply Monitor Noise Sensitivity**

The NCP1232 is optimized for fast response to negative-going changes in  $V_{DD}$ . Systems with an inordinate amount of electrical noise on  $V_{DD}$  (such as systems using relays), may require a 0.01  $\mu$ F or 0.1  $\mu$ F bypass capacitor to reduce detection sensitivity. This capacitor should be installed as close to the NCP1232 as possible to keep the capacitor lead length short.

Figure 2. Watchdog Timer

tsi

ŜΤ

t<sub>TD</sub>

|        | NOTE: t <sub>TD</sub> is the maximum elapsed time between ST high-to-low transistions (ST is activated by falling edges only) which wil keep the watchdog timer from forcing the reset outputs active for a time of t <sub>RST</sub> . t <sub>TD</sub> is a function of the voltage at the TD pin as tabulated below. |                                   |                                   |           |  |  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------|-----------|--|--|

|        | CONDITION                                                                                                                                                                                                                                                                                                             | MIN                               | <sup>t</sup> TD<br>TYP            | МАХ       |  |  |

| DEVICE | TD PIN = 0 V 62.5 msec<br>TD PIN = OPEN<br>TD PIN = $V_{CC}$ 500 msec                                                                                                                                                                                                                                                 | 150 msec<br>250 msec<br>1200 msec | 250 msec<br>600 msec<br>2000 msec | 1000 msec |  |  |

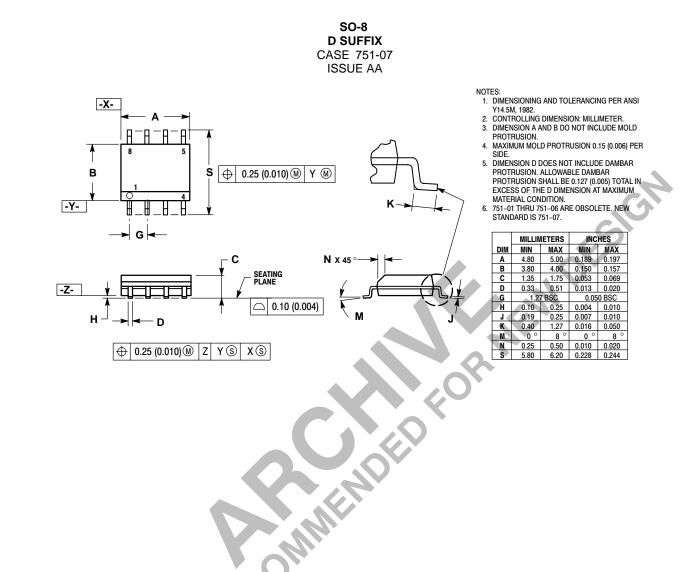

#### PACKAGE DIMENSIONS

**ON Semiconductor** and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and the sociated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

## PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 2-9-1 Kamimeguro, Meguro-ku, Tokyo, Japan 153-0051 Phone: 81-3-5773-3850

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.