## 1/2,1/3 DUTY LCD DRIVER WITH KEY SCAN

## GENERAL DESCRIPTION

The NJU6435 is a 1/2 or 1/3 duty LCD driver for segment type LCD panel with key scan function.

Display data and Key input data are communicated by serial data transmission, therefore, the communication between NJU6435 and MPU is performed by only 5 lines.

80-segment or 120-segment are displayed by 40-segment driver and 2- or 3-common driver.

The key scan function scanning up to 30 keys and the data is transferred to the MPU.

The NJU6435 can design simple front panel, therefore it is easy to apply car mounted audio, general audio and other products which have a display and key input.

## FEATURES

- 40-Segment Drivers

- Duty Ratio and<br/>Bias Level1/2 duty, 1/2 bias80-Segment Drive (Version D)1/3 duty, 1/2 bias 120-segment Drive (Version E)<br/>1/3 duty, 1/3 bias 120-segment Drive (Version F)

- 30 Key Scan Function (6-out x 5-in Matrix)

- Serial Data Transmission

- Display Off Function ( INH Terminal)

- Operating Voltage --- 5V±10%

- Package Outline --- QFP 64

- C-MOS Technology

## LINE UP

| LINE UP  | DUTY RATIO | BIAS LEVEL | MAX. DISPLAY SEGMENT | COMMON |

|----------|------------|------------|----------------------|--------|

| NJU6435D | 1/2 Duty   | 1/2 Bias   | 80 Segment           | 233    |

| NJU6435E | 1/3 Duty   | 1/2 Bias   | 120 Segment          |        |

| NJU6435F | 1/3 Duty   | 1/3 Bias   | 120 Segment          |        |

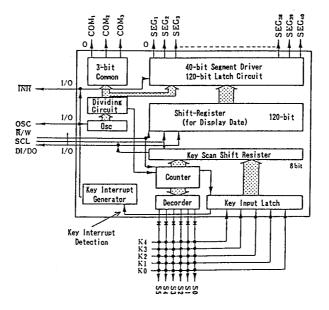

#### BLOCK DIAGRAM

-New Japan Radio Co.,Ltd.

PACKAGE OUTLINE

NJU6435XF

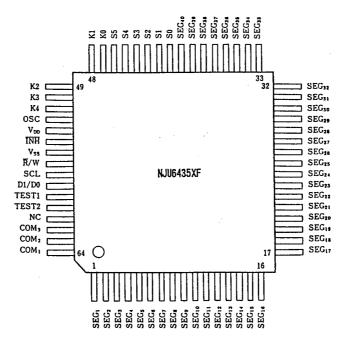

## PIN CONFIGURATION

JRC

TERMINAL DESCRIPTION

| NO.            | SYMBOL                | FUNCTION                                                               |  |  |  |  |

|----------------|-----------------------|------------------------------------------------------------------------|--|--|--|--|

| 1~40           | $SEG_1 \sim SEG_{40}$ | Segment Output Terminal                                                |  |  |  |  |

| 41~46          | SO ~ S5               | Key Scanning Signal Output Terminal                                    |  |  |  |  |

| 47~51          | K0 ~ K4               | Key Scanning Input Terminal (Built-in Pull-down Resistance)            |  |  |  |  |

| 52             | OSC                   | CR Oscillating Terminal (External C, R Connecting)                     |  |  |  |  |

| 53,55          | V <sub>DD</sub> , Vss | Power Supply                                                           |  |  |  |  |

| 54             | TNH                   | Display-Off Control<br>/Key Input Interrupt Signal Output Terminal     |  |  |  |  |

| 56             | Ī                     | Read / Write Control Terminal                                          |  |  |  |  |

| 57             | SCL                   | Serial Data Transmission Clock Terminal                                |  |  |  |  |

| 58             | D1/D0                 | Serial Data Input / Output Terminal                                    |  |  |  |  |

| 59,60          | TEST1, TEST2          | Testing Terminal (Normally OPEN)                                       |  |  |  |  |

| 61             | ŃC                    | Non Connection                                                         |  |  |  |  |

| 62<br>63<br>64 | COM3<br>COM2<br>COM1  | Common Output Terminal.<br>(In the Version D, COM₃ is no active (Vss)) |  |  |  |  |

-New Japan Radio Co.,Ltd.

## FUNCTIONAL DESCRIPTION

(1) Operation of each block

- (1-1) Oscillation Circuit

Oscillation by connecting external resistor and capacitor.

This circuits supply the basical clock signal to other circuits like as common driver and segment driver and key scan circuits.

- (1-2) Dividing Circuit This circuit divide the oscillating frequency, and generate the common and segment output timing signals.

- (1-3) Common Driver Output the common driving signal for LCD.

- (1-4) Segment Driver

Output the segment driving signal for LCD.

ON and OFF signal output according to the latched data.

- (1-5) Shift-Register During the R/W signal is "H", the data input to the shift-register by synchronousing the shift clock on SCL terminal.

- (1-6) Counter circuitThis circuits generate key scanning timing. When the key input, the data in the counter is transferred to the key scan shift resistor.

- (1-7) Decoder Decoding the counter output and generate the key scan signal.

- (1-8) Key Input Latch When the key depressed, the decoder output is transfer to the latch.

- (1-9) Key Scan Shift Register Output the data sent from counter circuits and key input latch to the MPU by serial format through the DI/DO port.

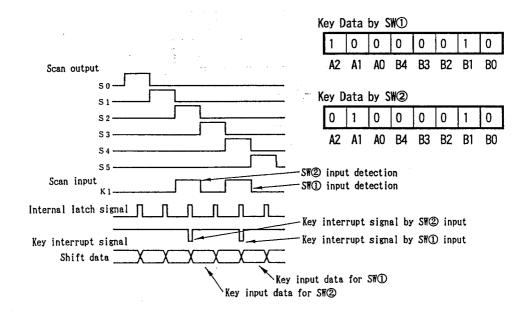

- (2) Mode of each terminal and Initialization

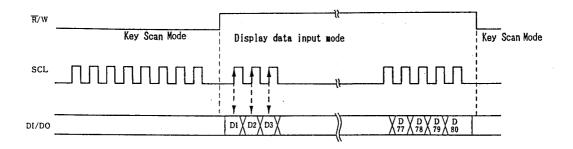

## (2-1) Mode of each Terminal controlled by $\overline{R}/W$ signal

| Ř∕₩ | I N H                                                                              | DI/D0                                                        |

|-----|------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Н   | LCD Display Control Mode (Input)<br>"H" - Display ON<br>"L" - Display Enforced OFF | LCD Display Data Input Mode (Input)<br>"H" - ON<br>"L" - OFF |

|     | Key Scan is stopped                                                                |                                                              |

|     | Key Scan Mode (Output)                                                             | Key Input Signal Output Mode (Output)                        |

| L   | When key input, Interrupt signal                                                   | After key interrupt signal output, key                       |

|     | Output                                                                             | input data output from this terminal                         |

|     | LCD enforced off is not effective                                                  | synchronized by the clock signal.                            |

## (2-2) Initialization

The NJU6435 series doesn't have a initialization function for the display data. Therefore, the data in the Shift Register and Latch connected to the segment driver is unfixed when the power turns on.

To avoid the no meaning display, the  $\overline{R}/W$  = "H" and  $\overline{INH}$  = "L" status should be kept during the display data transmission from the controller to the NJU6435.

5

-New Japan Radio Co.,Ltd.-

- (3) Display Data Correspond to Segment Terminals

- (3-1) Version D (1/2 Duty)

| Data             | Segment           | COM1        | COM2 |

|------------------|-------------------|-------------|------|

| D1               | SEG 1             | 0           |      |

| D2               | SEG <sub>2</sub>  | 0           |      |

| D3               | SEG 3             | 0           |      |

| D4               | SEG₄              | 0           |      |

| F<br>F<br>F<br>T | <br> <br> <br>    | t<br>t<br>1 | 1    |

| D37              | SEG <sub>37</sub> | 0           |      |

| D38              | SEG 38            | 0           |      |

| D39              | SEG 39            | 0           |      |

| D40              | SEG 40            | 0           |      |

| D41              | SEG 1             |             | 0    |

| D42              | SEG 2             |             | 0    |

| D43              | SEG₃              |             | 0    |

| D44              | SEG₄              |             | 0    |

|                  |                   |             |      |

| D77              | SEG 37            |             | 0    |

| D78              | SEG 38            |             | 0    |

| D79              | SEG <sub>39</sub> |             | 0    |

| D80              | SEG40             |             | 0    |

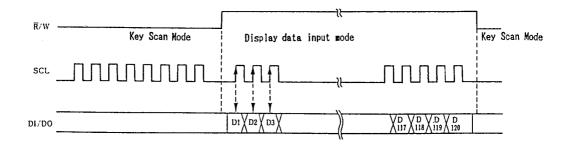

• Data Input / Output Timing

(3-2) Version E and F (1/3 Duty)

| Data   | Segment           | COM1 | COM <sub>2</sub> | COM₃ |

|--------|-------------------|------|------------------|------|

| D1     | SEG 1             | 0    |                  |      |

| D2     | SEG 2             | 0    |                  |      |

| D3     | SEG₃              | 0    |                  |      |

| D4     | SEG₄              | 0    |                  |      |

|        |                   |      | 1                | 1    |

| D37    | SEG <sub>37</sub> | 0    |                  |      |

| D38    | SEG 38            | 0    | 1 <b>.</b>       |      |

| D39    | SEG39             | 0    |                  |      |

| D40    | SEG₄₀             | 0    |                  |      |

| D41    | SEG 1             |      | 0                |      |

| D42    | SEG <sub>2</sub>  |      | 0                |      |

| D43    | SEG₃              |      | 0                |      |

| D44    | SEG₄              |      | 0                |      |

|        |                   |      |                  |      |

| D77    | SEG 37            |      | 0                |      |

| D78    | SEG38             |      | 0                |      |

| D79    | SEG <sub>39</sub> |      | 0                |      |

| D80    | SEG40             |      | 0                |      |

| D81    | SEG 1             |      |                  | 0    |

| D82    | SEG <sub>2</sub>  |      |                  | 0    |

| D83    | SEG₃              |      |                  | 0    |

| D84    | SEG₄              |      |                  | 0    |

|        |                   |      | 1                |      |

| D117   | SEG 37            |      |                  | 0    |

| D118   | SEG 38            |      |                  | 0    |

| D119 - | SEG 39            |      |                  | 0    |

| D120   | SEG₄₀             |      |                  | 0    |

• Data Input / Output Timing

-New Japan Radio Co.,Ltd.-

JRC

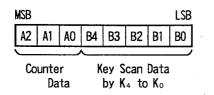

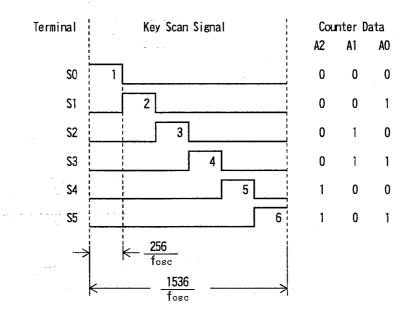

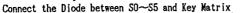

(4) Key Input Data Output Format

(4-1) Data Format

Key Scan Signal Correspond to Counter Data is as follows:

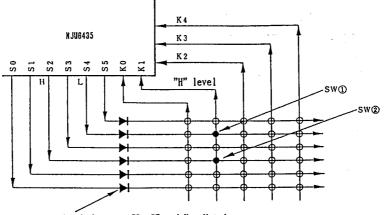

(4-2) Key Scan Output Data in Double or More Input.

In case of two or more key are depressed at same time, the output data is as follows: Below example is mentioned SW① and SW② are depressed at once.

In this time, two of key scan code is output as follows:

-New Japan Radio Co.,Ltd.

5

• Key Scan Timing Chart

-New Japan Radio Co.,Ltd.

## ■ ABSOLUTE MAXIMUM RATINGS

| PARAMETER               | SYMBOL | RATINGS         | UNIT |  |

|-------------------------|--------|-----------------|------|--|

| Operating Voltage (1)   | VDD    | - 0.3 ~ + 7.0   | V    |  |

| Input Voltage           | VIN    | - 0.3 ~ VDD+0.3 | V    |  |

| Output Current (1) * 2) | 0 (1)  | 100             | μA   |  |

| Output Current (2) * 3) | 0 (2)  | 1.0             | mA   |  |

| Power Dissipation       | Po     | 300             | m₩   |  |

| Operating Temperature   | Topr   | - 30 ~ + 85     | °C   |  |

| Storage Temperature     | Tstg   | - 55 ~ + 150    | °C   |  |

\* 1) R/W, SCL, INH, So∼S₅, DI/DO Terminals

\* 2) SEG1~SEG40 Terminals

\* 3) COM1, COM2, COM3 Terminals

## ELECTRICAL CHARACTERISTICS

DC Characteristics

(Ta=-20~+85°C, V\_DD=5.0V±10%, Vss=0V)

1.11

| PARAMETER              | SYMBOL              | CONDITIONS                            | MIN                | TYP  | MAX                | UNIT |

|------------------------|---------------------|---------------------------------------|--------------------|------|--------------------|------|

| Supply Voltage         | VDD                 |                                       | 4.5                | 5.0  | 5.5                | ٧    |

| Operating Current      | lod                 | V <sub>DD</sub> Terminal              |                    |      | 2.0                | mA   |

| "H" Input Voltage (1)  | VIH(1)              | TNH,K₀~K₄ Terminals                   | 0.7V <sub>DD</sub> | 1    | ,                  | ٧    |

| "H" Input Voltage (2)  | V1H(2)              | R/W,SCL,DI/DO Terminals               | 0.8VDD             |      |                    | ٧    |

| "L" Input Voltage (1)  | V1L(1)              | TNH,K₀~K₄ Terminals                   |                    |      | 0.3V <sub>DD</sub> | ٧    |

| "L" Input Voltage (2)  | V1L(2)              | R/W,SCL,DI/DO Terminals               |                    |      | 0.2V <sub>DD</sub> | ٧    |

| "H" Input Current      | Гін                 | R/W,SCL,DI/DO,<br>INH,K₀~K₄ Terminals |                    |      | 5                  | μA   |

| "L" Input Current      | ŀ1L                 | R/₩,SCL,DI/DO,<br>INH,K₀~K₄ Terminals |                    | · .  | . 5                | μA   |

| "H" Output Voltage (1) | <b>V</b> он(1)      | l₀=-40µA<br>TNH,DI/DO,S₀~S₅ Terminals | 4.2                |      | -                  | v    |

| "H" Output Voltage (2) | V <sub>OH (2)</sub> | i₀=-10μA<br>SEG₁~SEG₄₀ Terminals      | 4.0                |      |                    | V    |

| "H" Output Voltage (3) | <b>V</b> он (3)     | lo=-100µA<br>COM₁~COM₃ Terminals      | 4.4                |      |                    | ۷    |

| "L" Output Voltage (1) | <b>V</b> ol(1)      | l₀=400µA<br>INH,DI/DO,S₀~S₅ Terminals |                    |      | 0.4                | ٧    |

| "L" Output Voltage (2) | Vol (2)             | l₀=10µA<br>SEG₁~SEG₄₀ Terminals       |                    |      | 1.0                | V    |

| "L" Output Voltage (3) | Vol (3)             | l₀=100μA<br>COM₁~COM₃ Terminals       |                    |      | 0.6                | ۷    |

| COM 1/2 Level Voltage  | V <sub>MC1/2</sub>  | lo=±100μA<br>COM1,COM2 Terminals 1)   | 1.9                | 2.5  | 3.1                | V    |

| COM 1/3 Level Voltage  | VMC1/3              | l₀=±100µA<br>COM₁~COM₃ Terminals 2)   | 1.06               | 1.66 | 2.26               | ۷    |

| COM 2/3 Level Voltage  | V <sub>MC2∕3</sub>  | l₀=±100µA<br>COM₁~COM₃ Terminals 2)   | 2.73               | 3.33 | 3.93               | V    |

| SEG 1/3 Level Voltage  | V <sub>MS1∕3</sub>  | l₀=±10µA<br>SEG₁~SEG₄₀ Terminals 2)   | 0.66               | 1.66 | 2.66               | v    |

| SEG 2/3 Level Voltage  | V <sub>M52/3</sub>  | l₀=±10µA<br>SEG₁~SEG₄₀ Terminals 2)   | 2.33               | 3.33 | 4.33               | ۷    |

| External Resistance    | R                   | OSC Terminal                          |                    | 51   |                    | kΩ   |

| External Capacitance   | С                   | OCS Terminal                          |                    | 680  |                    | рF   |

| Oscillator Frequency   | fosc                | R=51kΩ,C=680pF                        | 40                 | 50   | 60                 | kHz  |

Note 1) Version D and E

2) Version F

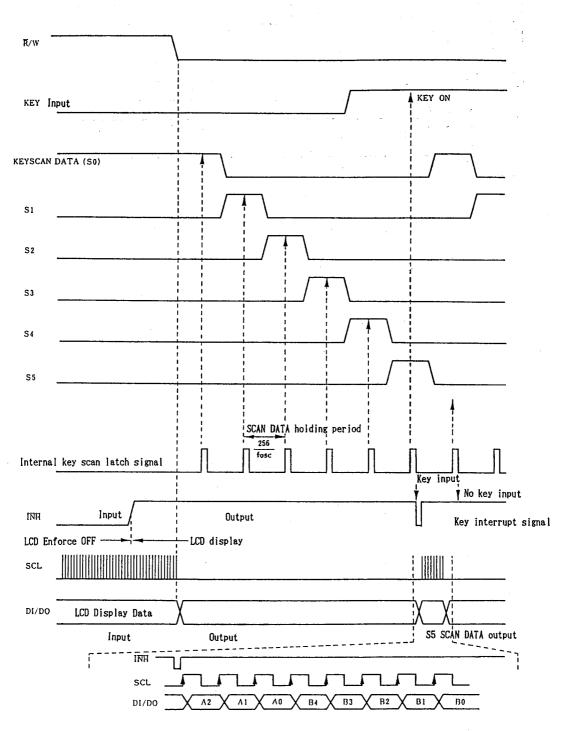

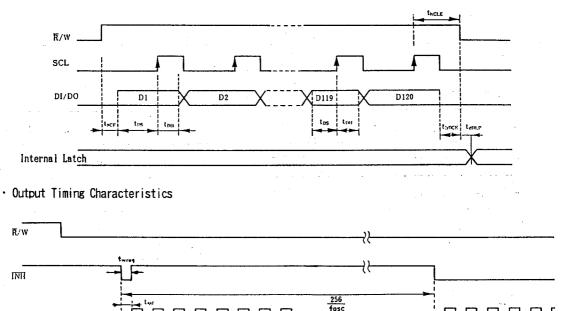

## AC Characteristics

(Ta=-20~+85°C,V<sub>DD</sub>=5.0V±10%,V<sub>SS</sub>=0V)

] [

(A2 ) A1 (A0 ) B4 (B3 )

| PARAMETER                       | SYMBOL          | CONDITIONS           | MIN  | TYP    | MAX | UNIT |

|---------------------------------|-----------------|----------------------|------|--------|-----|------|

| "L" Clock Pulse Width           | twell           | SCL Terminal         | 0.50 |        |     | μs   |

| "H" Clock Pulse Width           | twclh           | SCL Terminal         | 0.50 |        |     | μs   |

| Data Set-up Time                | tos             | SCL, DI/DO Terminals | 0.50 |        |     | μs   |

| Data Hold Time                  | t <sub>DH</sub> | SCL,DI/DO Terminals  | 0.50 |        | -   | μs   |

| CE Set-up Time                  | tsce            | R/W,DI/DO Terminals  | 1.0  |        |     | μs   |

| CE Hold Time (1)                | thdce           | R/W,DI/DO Terminals  | 1.0  |        |     | μs   |

| CE Hold Time (2)                | theis           | R/W,SCL Terminals    | 1.50 |        |     | μs   |

| Data Latch Delay Time           | tddlp           |                      |      |        | 1.0 | μs   |

| "L" Clock Enable<br>Pulse Width | twcel           | R/W Terminal         | 4.0  |        |     | μs   |

| Request Pulse Width             | twreq           | INH Terminal         |      | 1/fosc |     | μs   |

| Data Shift Set-up Time          | tssf            | INH, SCL Terminals   | 0.5  |        | -   | μs   |

| Data Output Delay Time          | tdkd            | SCL,DI/DO Terminals  | 0.1  |        |     | μs   |

· Input Timing Characteristics

સ

Ldkd

A2 A1 A0 B4 B3 B2 B1 B0

-New Japan Radio Co.,Ltd.

5

SCL

01/10

NJU6435 Series

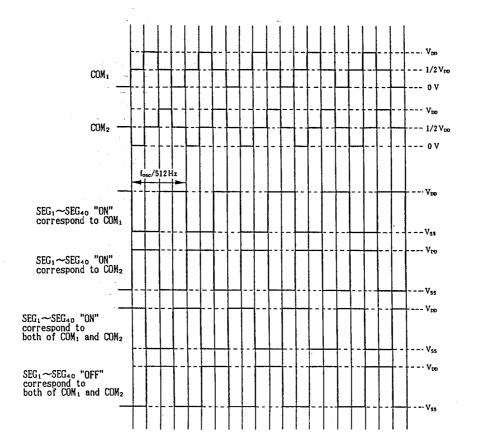

### (5) LCD Driving Waveform

JRC

(5-1) Version D (1/2Bias, 1/2Duty)

5

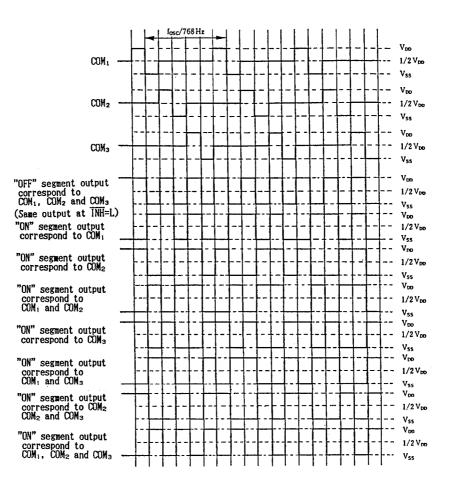

(5-2) Version E (1/2Bias, 1/3Duty)

JR

## -New Japan Radio Co.,Ltd.=

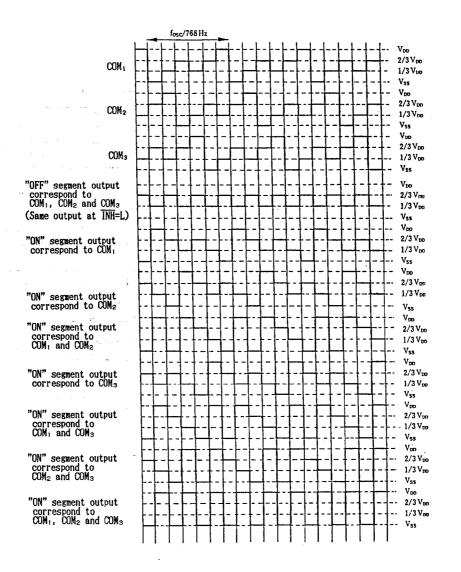

## (5-3) Version F (1/3Bias,1/3Duty)

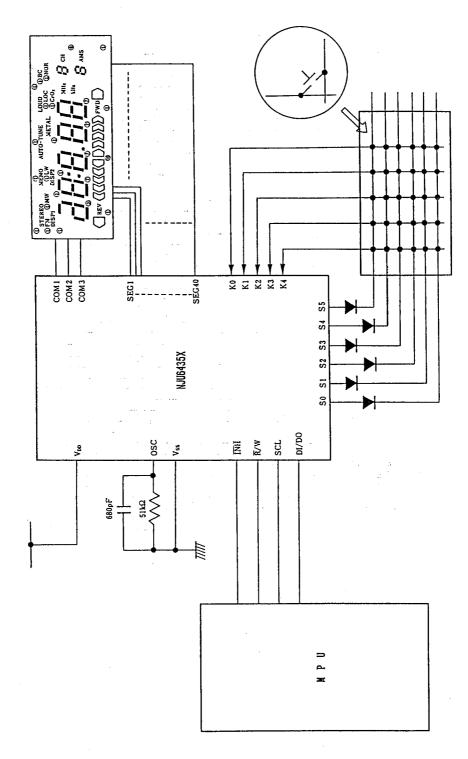

## APPLICATION CIRCUIT

-New Japan Radio Co.,Ltd.

5

# MEMO

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.