#### **Features**

· High Performance:

|                 |                                | -7K <sup>3</sup><br>CL=2 | -75B,<br>CL=3 | -8B,<br>CL=2 | Units |

|-----------------|--------------------------------|--------------------------|---------------|--------------|-------|

| f <sub>CK</sub> | Clock Frequency                | 133                      | 133           | 100          | MHz   |

| t <sub>CK</sub> | Clock Cycle                    | 7.5                      | 7.5           | 10           | ns    |

| t <sub>AC</sub> | Clock Access Time <sup>1</sup> | _                        | _             | _            | ns    |

| t <sub>AC</sub> | Clock Access Time <sup>2</sup> | 5.4                      | 5.4           | 6            | ns    |

- 1. Terminated load. See AC Characteristics on page 37.

- 2. Unterminated load. See AC Characteristics on page 37.

- 3.  $t_{RP} = t_{RCD} = 2 \text{ CKs}$

- Single Pulsed RAS Interface

- Fully Synchronous to Positive Clock Edge

- Four Banks controlled by BA0/BA1 (Bank Select)

- Programmable CAS Latency: 2, 3

- Programmable Burst Length: 1, 2, 4, 8

- Programmable Wrap: Sequential or Interleave

- Multiple Burst Read with Single Write Option

- Automatic and Controlled Precharge Command

- Data Mask for Read/Write control (x4, x8)

- Dual Data Mask for byte control (x16)

- · Auto Refresh (CBR) and Self Refresh

- Suspend Mode and Power Down Mode

- Standard Power operation

- 8192 refresh cycles/64ms

- Random Column Address every CK (1-N Rule)

- Single 3.3V ± 0.3V Power Supply

- LVTTL compatible

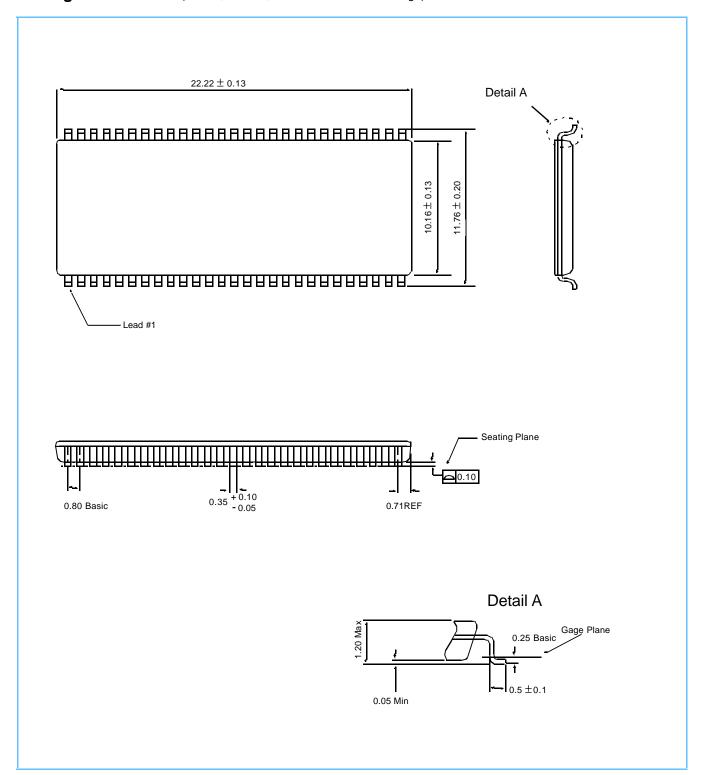

- Package: 54-pin 400 mil TSOP-Type II

- -7K parts for PC133 2-2-2 operation

- -75B parts for PC133 3-3-3 operation

- -8B parts for PC100 2-2-2 operation

### **Description**

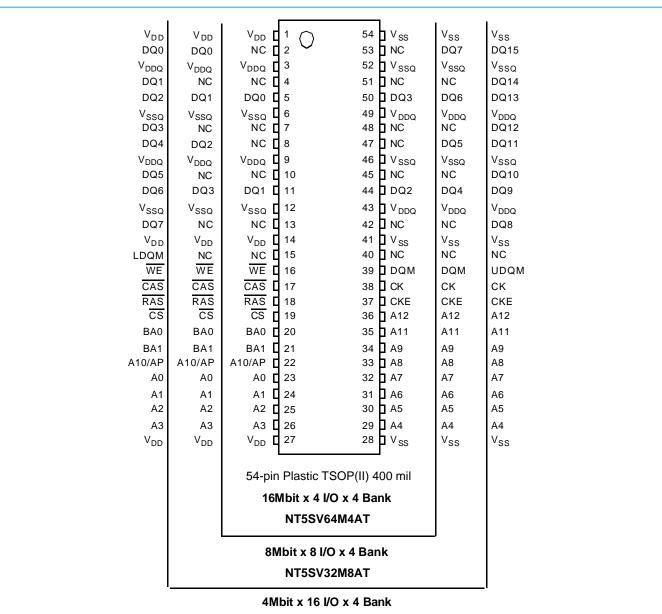

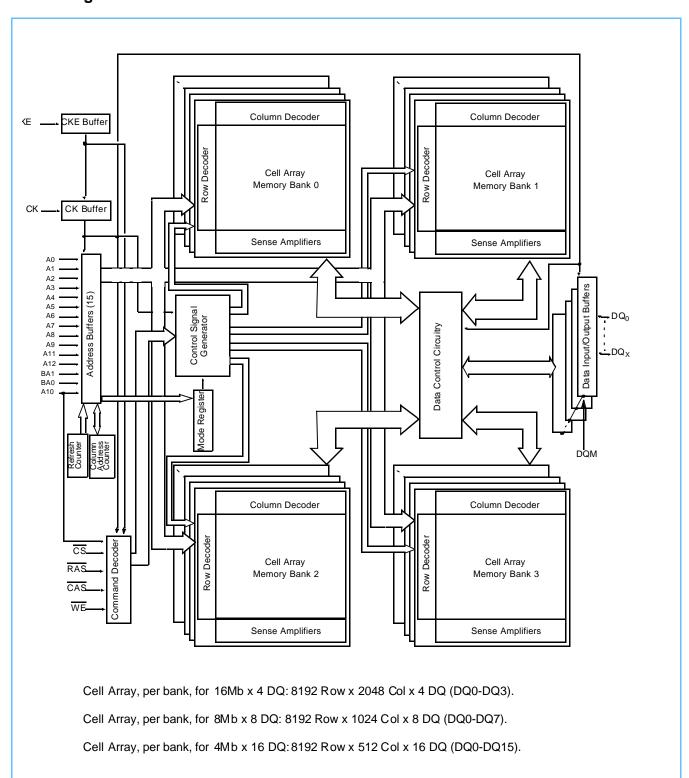

The NT5SV64M4AT, NT5SV32M8AT, and NT5SV16M16AT are four-bank Synchronous DRAMs organized as 16Mbit x 4 I/O x 4 Bank, 8Mbit x 8 I/O x 4 Bank, and 4Mbit x 16 I/O x 4 Bank, respectively. These synchronous devices achieve high-speed data transfer rates of up to 133MHz by employing a pipeline chip architecture that synchronizes the output data to a system clock. The chip is fabricated with NTC's advanced 256Mbit single transistor CMOS DRAM process technology.

The device is designed to comply with all JEDEC standards set for synchronous DRAM products, both electrically and mechanically. All of the control, address, and data input/output (I/O or DQ) circuits are synchronized with the positive edge of an externally supplied clock.

RAS, CAS, WE, and CS are pulsed signals which are examined at the positive edge of each externally applied clock (CK). Internal chip operating modes are defined by combinations of these signals and a command decoder initiates the necessary timings for each operation. A fifteen bit address bus accepts address data in the conventional RAS/CAS multiplexing style. Thirteen row addresses (A0-A12) and two bank select addresses (BA0, BA1) are strobed with RAS. Eleven column addresses (A0-A9, A11) plus bank select addresses and A10 are strobed with CAS. Column address A11 is dropped on the x8 device, and column addresses A11 and A9 are dropped on the x16 device.

Prior to any access operation, the  $\overline{\text{CAS}}$  latency, burst length, and burst sequence must be programmed into the device by address inputs A0-A12, BA0, BA1 during a mode register set

cycle. In addition, it is possible to program a multiple burst sequence with single write cycle for write through cache operation.

Operating the four memory banks in an interleave fashion allows random access operation to occur at a higher rate than is possible with standard DRAMs. A sequential and gapless data rate of up to 133MHz is possible depending on burst length, CAS latency, and speed grade of the device. Auto Refresh (CBR) and Self Refresh operation are supported.

### Pin Assignments for Planar Components (Top View)

NT5SV16M16AT

# **Pin Description**

| СК               | Clock Input           | DQ0-DQ15         | Data Input/Output     |

|------------------|-----------------------|------------------|-----------------------|

| CKE (CKE0, CKE1) | Clock Enable          | DQM, LDQM, UDQM  | Data Mask             |

| CS               | Chip Select           | V <sub>DD</sub>  | Power (+3.3V)         |

| RAS              | Row Address Strobe    | V <sub>SS</sub>  | Ground                |

| CAS              | Column Address Strobe | $V_{DDQ}$        | Power for DQs (+3.3V) |

| WE               | Write Enable          | V <sub>SSQ</sub> | Ground for DQs        |

| BA1, BA0         | Bank Select           | NC               | No Connection         |

| A0 - A12         | Address Inputs        | _                | _                     |

# **Input/Output Functional Description**

| Symbol                    | Туре             | Polarity         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СК                        | Input            | Positive<br>Edge | The system clock input. All of the SDRAM inputs are sampled on the rising edge of the clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CKE, CKE0,<br>CKE1        | Input            | Active High      | Activates the CK signal when high and deactivates the CK signal when low. By deactivating the clock, CKE low initiates the Power Down mode, Suspend mode, or the Self Refresh mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <del>cs</del>             | Input            | Active Low       | CS enables the command decoder when low and disables the command decoder when high. When the command decoder is disabled, new commands are ignored but previous operations continue.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RAS, CAS, WE              | Input            | Active Low       | When sampled at the positive rising edge of the clock, $\overline{\text{CAS}}$ , $\overline{\text{RAS}}$ , and $\overline{\text{WE}}$ define the operation to be executed by the SDRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| BA1, BA0                  | Input            | _                | Selects which bank is to be active.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A0 - A12                  | Input            | _                | During a Bank Activate command cycle, A0-A12 defines the row address (RA0-RA12) when sampled at the rising clock edge.  During a Read or Write command cycle, A0-A9 and A11 defines the column address (CA0-CA9, CA11), when sampled at the rising clock edge. Assume the x4 organization.  A10 is used to invoke auto-precharge operation at the end of the burst read or write cycle. If A10 is high, auto-precharge is selected and BA0, BA1 defines the bank to be precharged. If A10 is low, autoprecharge is disabled.  During a Precharge command cycle, A10 is used in conjunction with BA0, BA1 to control which bank(s) to precharge. If A10 is high, all banks will be precharged regardless of the state of BS. If A10 is low, then BA0 and BA1 are used to define which bank to precharge. |

| DQ0 - DQ15                | Input-<br>Output | _                | Data Input/Output pins operate in the same manner as on conventional DRAMs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DQM<br>LDQM<br>UDQM       | Input            | Active High      | The Data Input/Output mask places the DQ buffers in a high impedance state when sampled high. In x16 products, the LDQM and UDQM control the lower and upper byte I/O buffers, respectively. In Read mode, DQM has a latency of two clock cycles and controls the output buffers like an output enable. DQM low turns the output buffers on and DQM high turns them off. In Write mode, DQM has a latency of zero and operates as a word mask by allowing input data to be written if it is low but blocks the write operation if DQM is high.                                                                                                                                                                                                                                                          |

| $V_{DD}, V_{SS}$          | Supply           | _                | Power and ground for the input buffers and the core logic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| $V_{\rm DDQ} V_{\rm SSQ}$ | Supply           | _                | Isolated power supply and ground for the output buffers to provide improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# **Ordering Information**

| Organization     | Part Number        |                             | Speed Grade  |              |            |         |  |  |  |

|------------------|--------------------|-----------------------------|--------------|--------------|------------|---------|--|--|--|

| Organization     | Fart Number        | Clock Frequency             | @CAS Latency | Note         | Package    | Refresh |  |  |  |

|                  | NT5SV64M4AT-7K     | 143MHz@CL3                  | 133MHz@CL2   | PC133, PC100 |            |         |  |  |  |

| 64M x 4          | NT5SV64M4AT-75B    | 133MHz@CL3                  | 100MHz@CL2   | PC133, PC100 |            |         |  |  |  |

|                  | NT5SV64M4AT-8B     | 125MHz@CL3                  | 100MHz@CL2   | PC100        |            | SP      |  |  |  |

| 22M v 8          | NT5SV32M8AT-7K     | 143MHz@CL3                  | 133MHz@CL2   | PC133, PC100 | 400mil 54- |         |  |  |  |

| 32M x 8          | NT5SV32M8AT-75B    | 133MHz@CL3                  | 100MHz@CL2   | PC133, PC100 | PIN        |         |  |  |  |

|                  | NT5SV32M8AT-8B     | 125MHz@CL3 100MHz@CL2 PC100 |              | TSOPII       |            |         |  |  |  |

|                  | NT5SV16M16AT-7K    | 143MHz@CL3                  | 133MHz@CL2   | PC133, PC100 |            |         |  |  |  |

| 16M x 16         | NT5SV16M16AT-75B   | 133MHz@CL3                  | 100MHz@CL2   | PC133, PC100 |            |         |  |  |  |

|                  | NT5SV16M16AT-8B    | 125MHz@CL3                  | 100MHz@CL2   | PC100        |            |         |  |  |  |

|                  | NT5SV16M16AT-7KL   | 143MHz@CL3                  | 133MHz@CL2   | PC133, PC100 |            |         |  |  |  |

| 16M x 16         | NT5SV16M16AT-75BL  | 133MHz@CL3                  | 100MHz@CL2   | PC133, PC100 |            | LP      |  |  |  |

|                  | NT5SV16M16AT-8BL   | 125MHz@CL3                  | 100MHz@CL2   | PC100        |            |         |  |  |  |

| SP : Standard Po | ower; LP:Low power |                             |              |              |            |         |  |  |  |

4

## **Block Diagram**

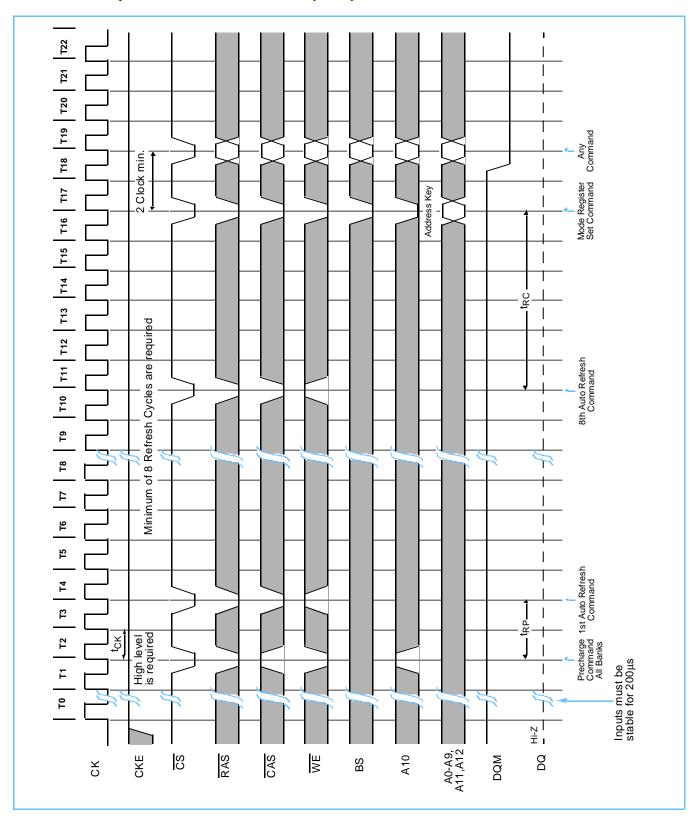

#### **Power On and Initialization**

The default power on state of the mode register is supplier specific and may be undefined. The following power on and initialization sequence guarantees the device is preconditioned to each users specific needs.

Like a conventional DRAM, the Synchronous DRAM must be powered up and initialized in a predefined manner. During power on, all  $V_{DD}$  and  $V_{DDQ}$  pins must be built up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power on voltage must not exceed  $V_{DD}$ +0.3V on any of the input pins or  $V_{DD}$  supplies. The CK signal must be started at the same time. After power on, an initial pause of 200 $\mu$ s is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power on, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. A minimum of two Auto Refresh cycles (CBR) are also required. These may be done before or after programming the Mode Register. Failure to follow these steps may lead to unpredictable start-up modes.

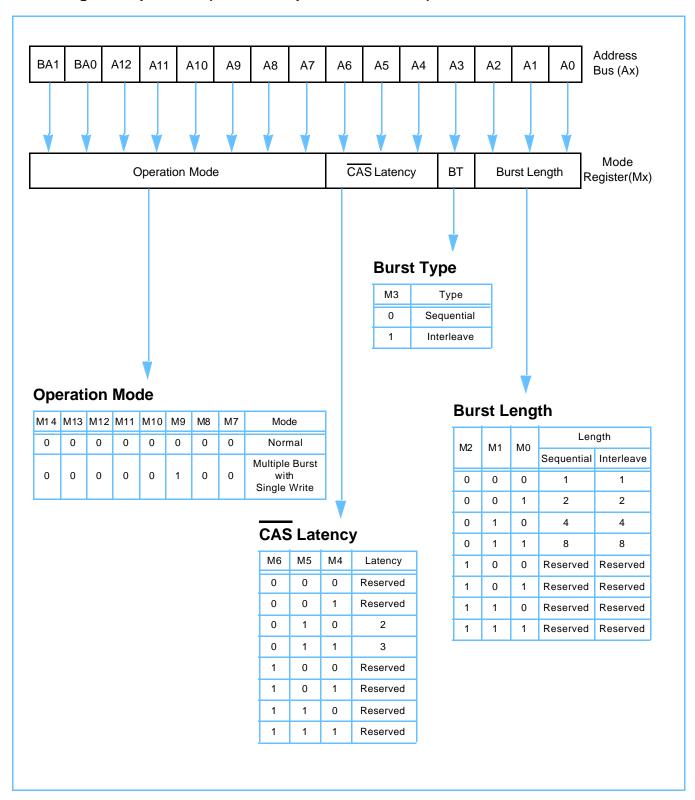

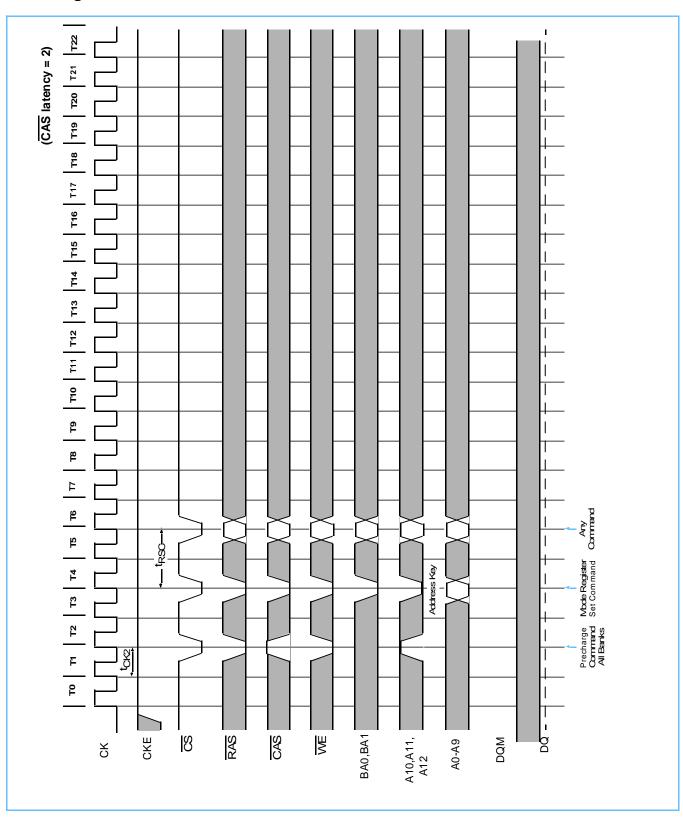

### **Programming the Mode Register**

For application flexibility,  $\overline{\text{CAS}}$  latency, burst length, burst sequence, and operation type are user defined variables and must be programmed into the SDRAM Mode Register with a single Mode Register Set Command. Any content of the Mode Register can be altered by re-executing the Mode Register Set Command. If the user chooses to modify only a subset of the Mode Register variables, all four variables must be redefined when the Mode Register Set Command is issued.

After initial power up, the Mode Register Set Command must be issued before read or write cycles may begin. All banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of RAS, CAS, CS, and WE at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued following the mode register set command once a delay equal to t<sub>RSC</sub> has elapsed.

#### **CAS** Latency

The  $\overline{\text{CAS}}$  latency is a parameter that is used to define the delay from when a Read Command is registered on a rising clock edge to when the data from that Read Command becomes available at the outputs. The  $\overline{\text{CAS}}$  latency is expressed in terms of clock cycles and can have a value of 2 or 3 cycles. The value of the  $\overline{\text{CAS}}$  latency is determined by the speed grade of the device and the clock frequency that is used in the application. A table showing the relationship between the  $\overline{\text{CAS}}$  latency, speed grade, and clock frequency appears in the Electrical Characteristics section of this document. Once the appropriate  $\overline{\text{CAS}}$  latency has been selected it must be programmed into the mode register after power up, for an explanation of this procedure see Programming the Mode Register in the previous section.

# **Mode Register Operation (Address Input For Mode Set)**

### **Burst Mode Operation**

Burst mode operation is used to provide a constant flow of data to memory locations (write cycle), or from memory locations (read cycle). There are three parameters that define how the burst mode will operate. These parameters include burst sequence, burst length, and operation mode. The burst sequence and burst length are programmable, and are determined by address bits A0 - A3 during the Mode Register Set command. Operation mode is also programmable and is set by address bits A7 - A12, BA0, and BA1.

The burst type is used to define the order in which the burst data will be delivered or stored to the SDRAM. Two types of burst sequences are supported, sequential and interleaved. See the table below.

The burst length controls the number of bits that will be output after a Read Command, or the number of bits to be input after a Write Command. The burst length can be programmed to have values of 1, 2, 4, 8 (actual page length is dependent on organization: x4, x8, or x16).

Burst operation mode can be normal operation or multiple burst with single write operation. Normal operation implies that the device will perform burst operations on both read and write cycles until the desired burst length is satisfied. Multiple burst with single write operation was added to support Write Through Cache operation. Here, the programmed burst length only applies to read cycles. All write cycles are single write operations when this mode is selected.

#### **Burst Length and Sequence**

| Burst Length | Starting Address (A2 A1 A0) | Sequential Addressing (decimal) | Interleave Addressing (decimal) |

|--------------|-----------------------------|---------------------------------|---------------------------------|

| 2            | x x 0                       | 0, 1                            | 0, 1                            |

| 2            | x x 1                       | 1, 0                            | 1, 0                            |

|              | x 0 0                       | 0, 1, 2, 3                      | 0, 1, 2, 3                      |

| 4            | x 0 1                       | 1, 2, 3, 0                      | 1, 0, 3, 2                      |

| 7            | x 1 0                       | 2, 3, 0, 1                      | 2, 3, 0, 1                      |

|              | x 1 1                       | 3, 0, 1, 2                      | 3, 2, 1, 0                      |

|              | 000                         | 0, 1, 2, 3, 4, 5, 6, 7          | 0, 1, 2, 3, 4, 5, 6, 7          |

|              | 0 0 1                       | 1, 2, 3, 4, 5, 6, 7, 0          | 1, 0, 3, 2, 5, 4, 7, 6          |

|              | 0 1 0                       | 2, 3, 4, 5, 6, 7, 0, 1          | 2, 3, 0, 1, 6, 7, 4, 5          |

| 8            | 011                         | 3, 4, 5, 6, 7, 0, 1, 2          | 3, 2, 1, 0, 7, 6, 5, 4          |

| Ü            | 100                         | 4, 5, 6, 7, 0, 1, 2, 3          | 4, 5, 6, 7, 0, 1, 2, 3          |

|              | 1 0 1                       | 5, 6, 7, 0, 1, 2, 3, 4          | 5, 4, 7, 6, 1, 0, 3, 2          |

|              | 110                         | 6, 7, 0, 1, 2, 3, 4, 5          | 6, 7, 4, 5, 2, 3, 0, 1          |

|              | 111                         | 7, 0, 1, 2, 3, 4, 5, 6          | 7, 6, 5, 4, 3, 2, 1, 0          |

Note: Page length is a function of I/O organization and column addressing.

x4 organization (CA0-CA9, CA11); Page Length = 2048 bits

x8 organization (CA0-CA9); Page Length = 1024 bits

x16 organization (CA0-CA8); Page Length = 512 bits

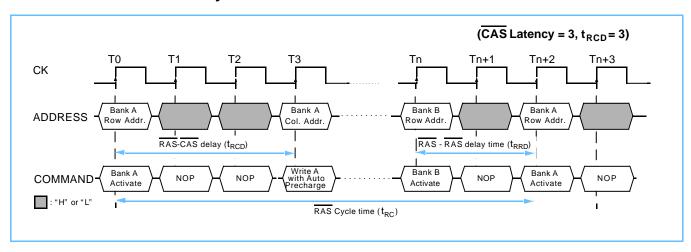

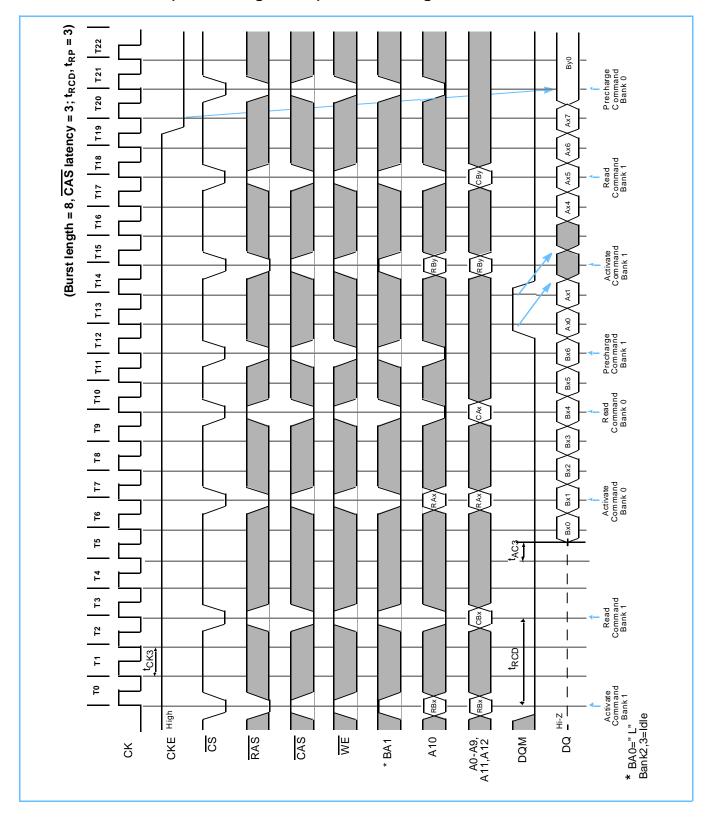

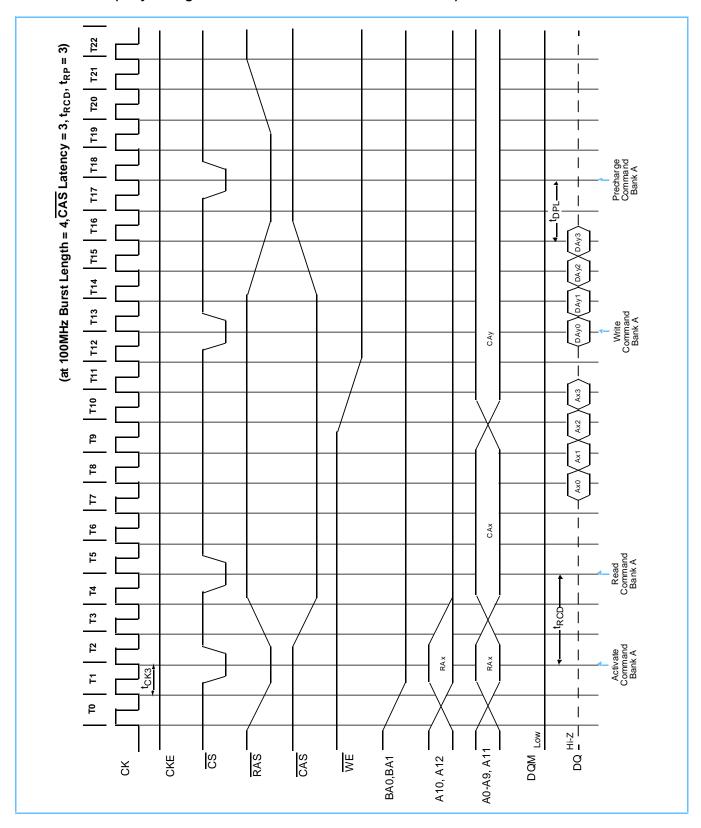

#### **Bank Activate Command**

In relation to the operation of a fast page mode DRAM, the Bank Activate command correlates to a falling RAS signal. The Bank Activate command is issued by holding CAS and WE high with CS and RAS low at the rising edge of the clock. The Bank Select address BA0 - BA1 is used to select the desired bank. The row address A0 - A12 is used to determine which row to activate in the selected bank.

The Bank Activate command must be applied before any Read or Write operation can be executed. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must meet or exceed the  $\overline{RAS}$  to  $\overline{CAS}$  delay time ( $t_{RCD}$ ). Once a bank has been activated it must be precharged before another Bank Activate command can be applied to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device ( $t_{RC}$ ). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time ( $t_{RRD}$ ). The maximum time that each bank can be held active is specified as  $t_{RAS(max)}$ .

#### **Bank Activate Command Cycle**

#### **Bank Select**

The Bank Select inputs, BA0 and BA1, determine the bank to be used during a Bank Activate, Precharge, Read, or Write operation.

#### **Bank Selection Bits**

| BA0 | BA1 | Bank   |

|-----|-----|--------|

| 0   | 0   | Bank 0 |

| 1   | 0   | Bank 1 |

| 0   | 1   | Bank 2 |

| 1   | 1   | Bank 3 |

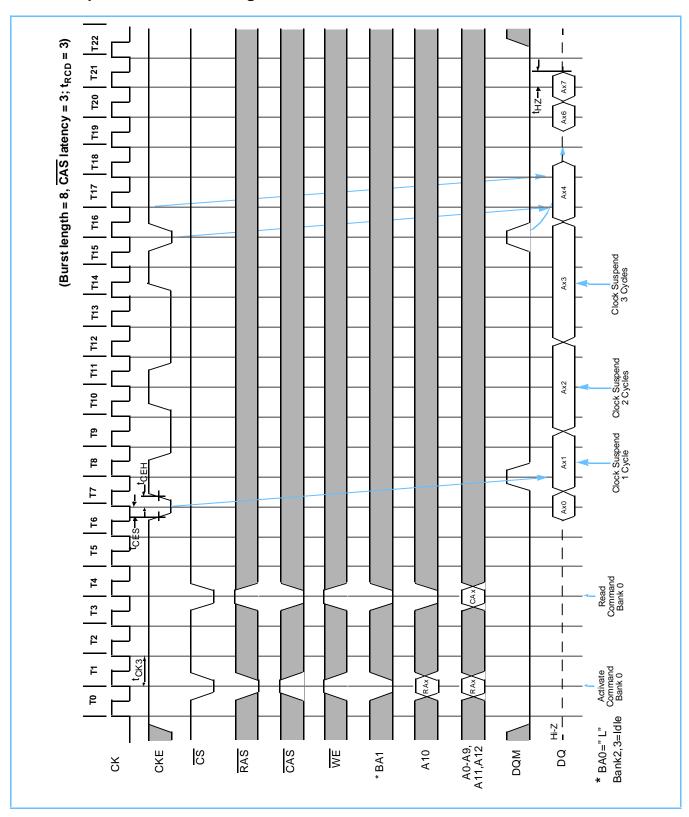

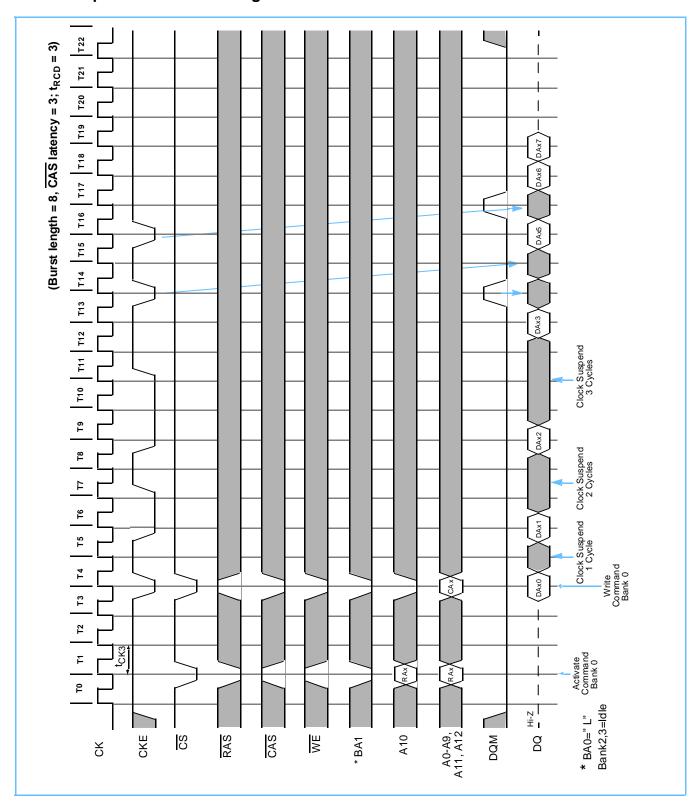

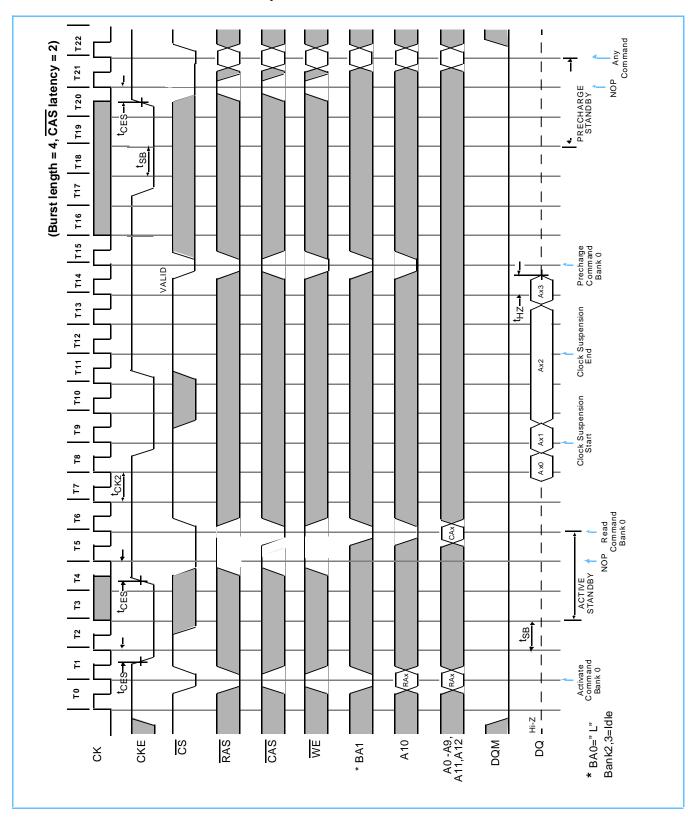

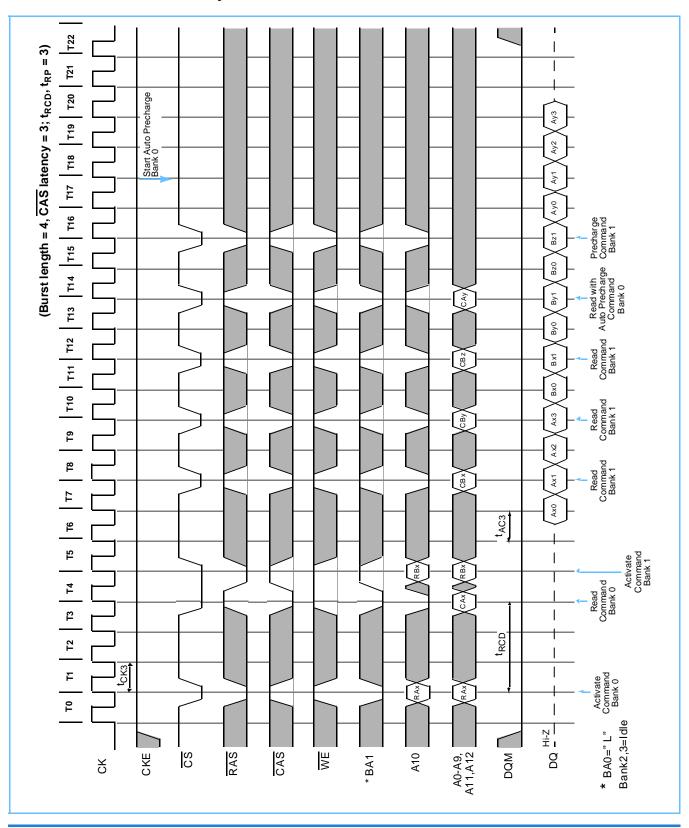

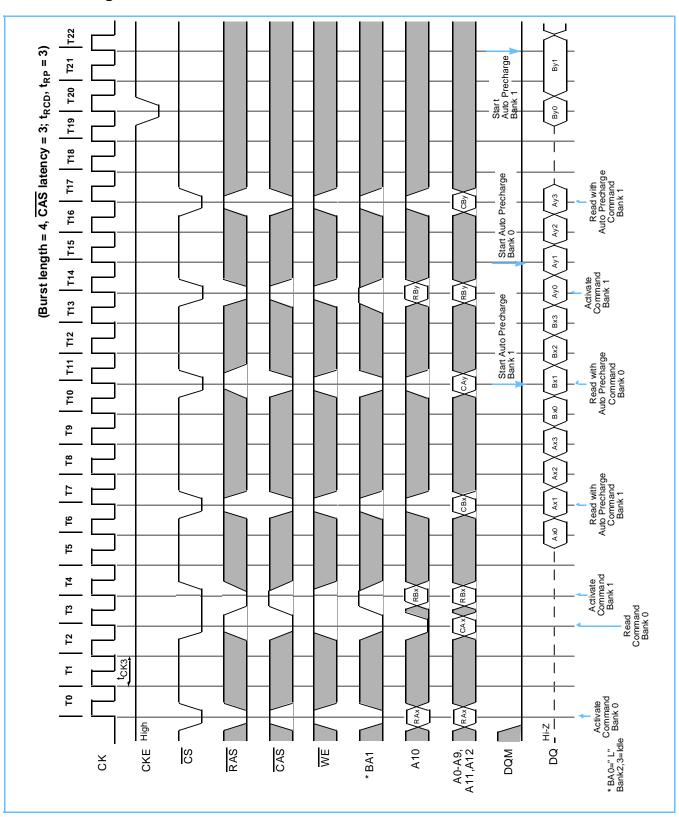

#### **Read and Write Access Modes**

After a bank has been activated, a read or write cycle can be executed. This is accomplished by setting  $\overline{RAS}$  high and  $\overline{CAS}$  low at the clock's rising edge after the necessary  $\overline{RAS}$  to  $\overline{CAS}$  delay ( $t_{RCD}$ ). WE must also be defined at this time to determine whether the access cycle is a read operation ( $\overline{WE}$  high), or a write operation ( $\overline{WE}$  low). The address inputs determine the starting column address.

The SDRAM provides a wide variety of fast access modes. A single Read or Write Command will initiate a serial read or write operation on successive clock cycles up to 133MHz. The number of serial data bits for each access is equal to the burst length, which is programmed into the Mode Register.

Similar to Page Mode of conventional DRAMs, a read or write cycle can not begin until the sense amplifiers latch the selected row address information. The refresh period (t<sub>REF</sub>) is what limits the number of random column accesses to an activated bank. A new burst access can be done even before the previous burst ends. The ability to interrupt a burst operation at every clock cycle is supported; this is referred to as the 1-N rule. When the previous burst is interrupted by another Read or Write Command, the remaining addresses are overridden by the new address.

Precharging an active bank after each read or write operation is not necessary providing the same row is to be accessed again. To perform a read or write cycle to a different row within an activated bank, the bank must be precharged and a new Bank Activate command must be issued. When more than one bank is activated, interleaved (ping pong) bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between multiple banks, fast and seamless data access operation among many different pages can be realized. When multiple banks are activated, column to column interleave operation can be done between different pages. Finally, Read or Write Commands can be issued to the same bank or between active banks on every clock cycle.

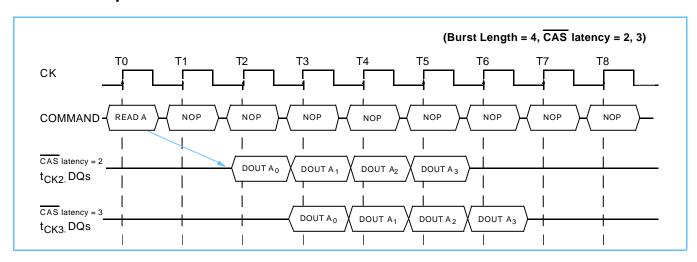

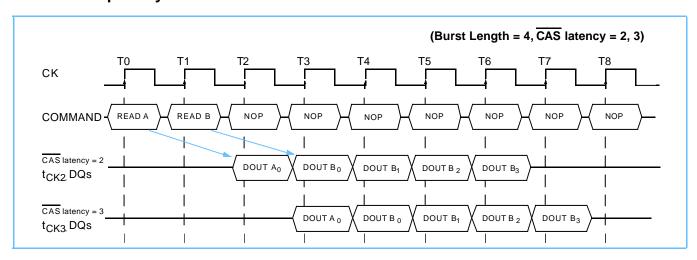

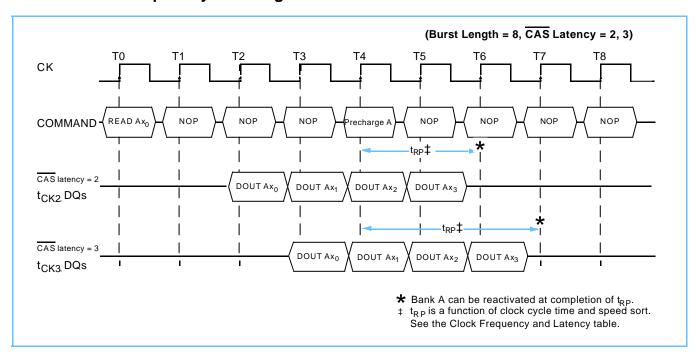

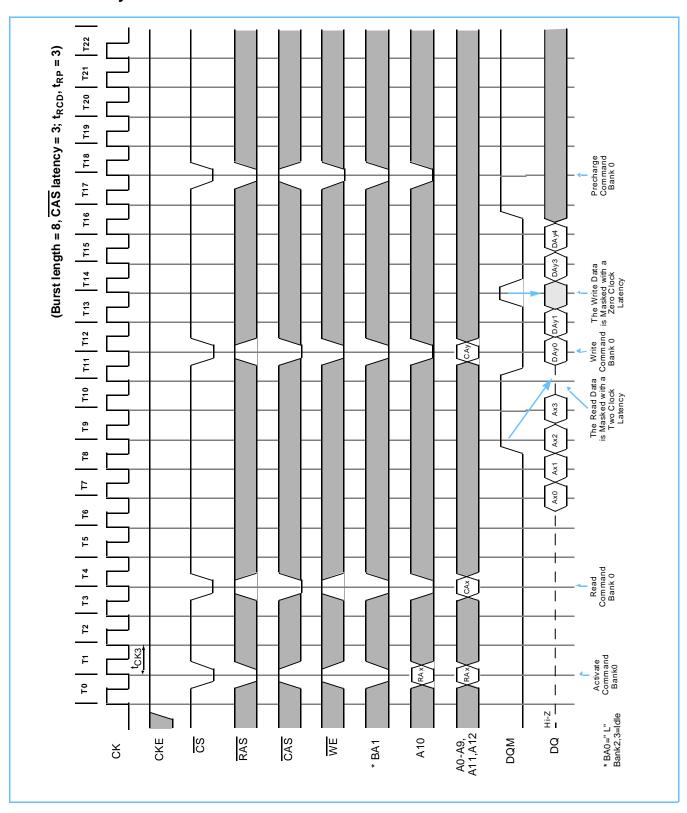

#### **Burst Read Command**

The Burst Read command is initiated by having  $\overline{CS}$  and  $\overline{CAS}$  low while holding  $\overline{RAS}$  and  $\overline{WE}$  high at the rising edge of the clock. The address inputs determine the starting column address for the burst, the Mode Register sets the type of burst (sequential or interleave) and the burst length (1, 2, 4, 8). The delay from the start of the command to when the data from the first cell appears on the outputs is equal to the value of the  $\overline{CAS}$  latency that is set in the Mode Register.

#### **Burst Read Operation**

#### Read Interrupted by a Read

A Burst Read may be interrupted before completion of the burst by another Read Command, with the only restriction being that the interval that separates the commands must be at least one clock cycle. When the previous burst is interrupted, the remaining addresses are overridden by the new address with the full burst length. The data from the first Read Command continues to appear on the outputs until the CAS latency from the interrupting Read Command is satisfied, at this point the data from the interrupting Read Command appears.

#### Read Interrupted by a Read

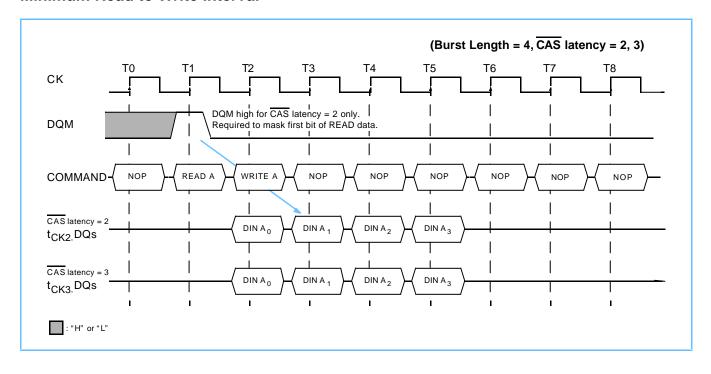

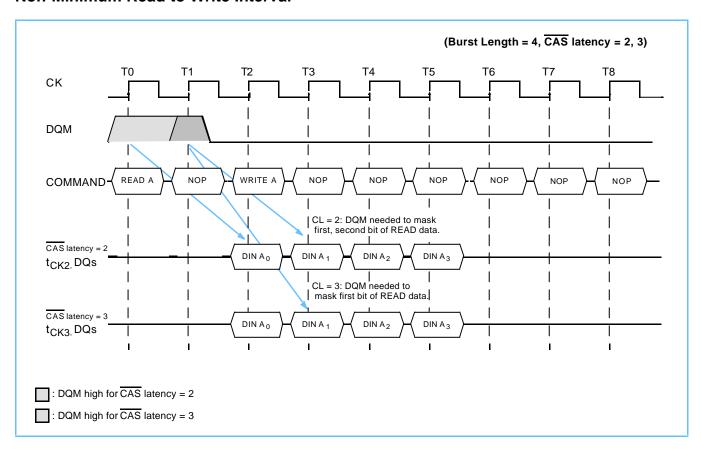

## Read Interrupted by a Write

To interrupt a burst read with a Write Command, DQM may be needed to place the DQs (output drivers) in a high impedance state to avoid data contention on the DQ bus. If a Read Command will issue data on the first or second clocks cycles of the write operation, DQM is needed to insure the DQs are tri-stated. After that point the Write Command will have control of the DQ bus.

#### **Minimum Read to Write Interval**

### **Non-Minimum Read to Write Interval**

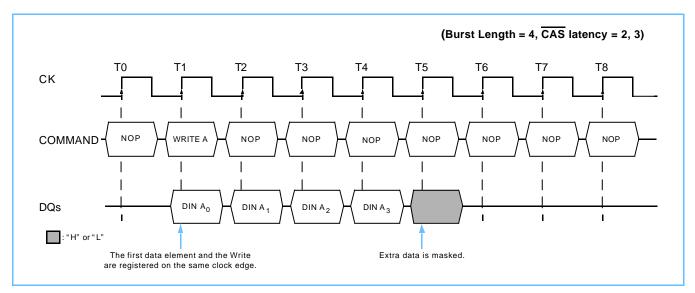

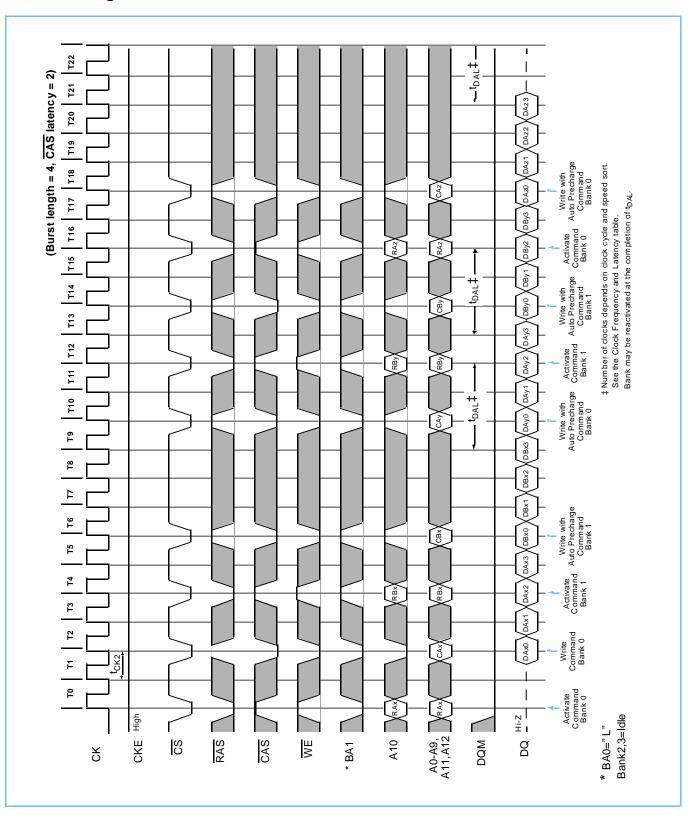

#### **Burst Write Command**

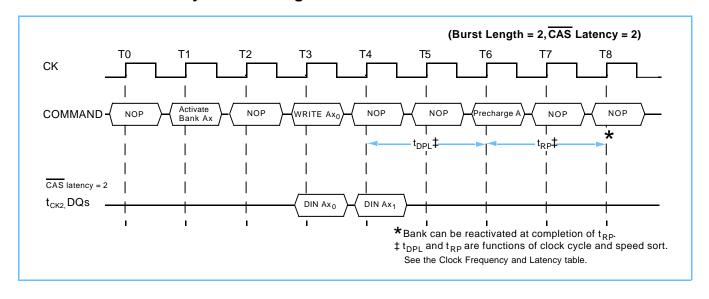

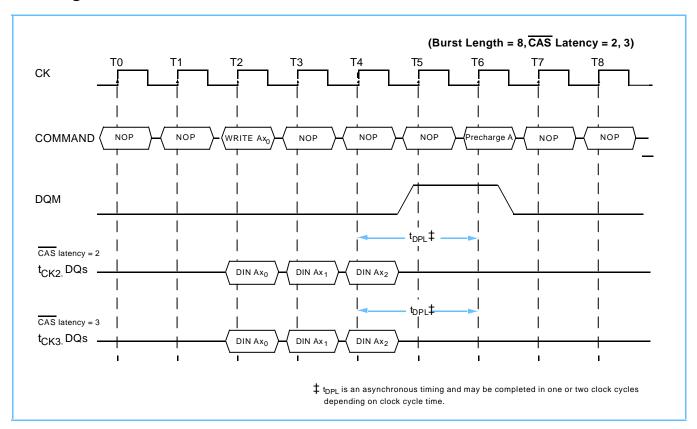

The Burst Write command is initiated by having  $\overline{CS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  low while holding  $\overline{RAS}$  high at the rising edge of the clock. The address inputs determine the starting column address. There is no  $\overline{CAS}$  latency required for burst write cycles. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. When the burst has finished, any additional data supplied to the DQ pins will be ignored.

## **Burst Write Operation**

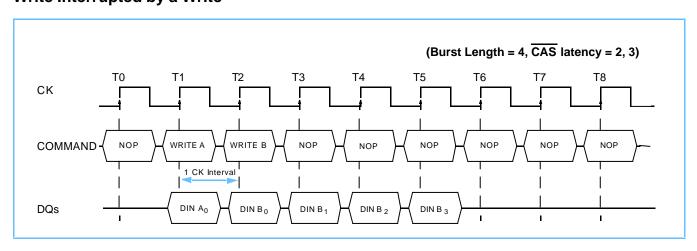

#### Write Interrupted by a Write

A burst write may be interrupted before completion of the burst by another Write Command. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.

#### Write Interrupted by a Write

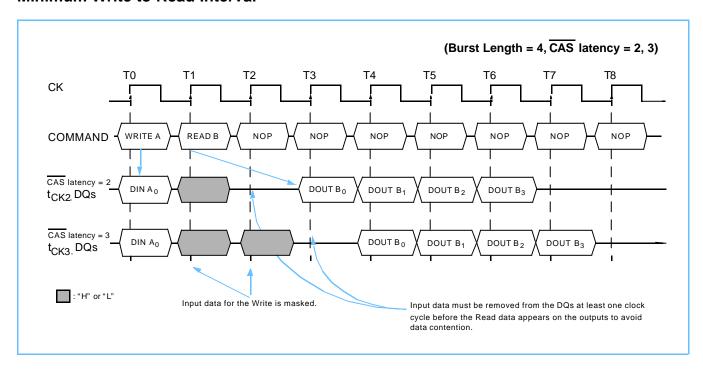

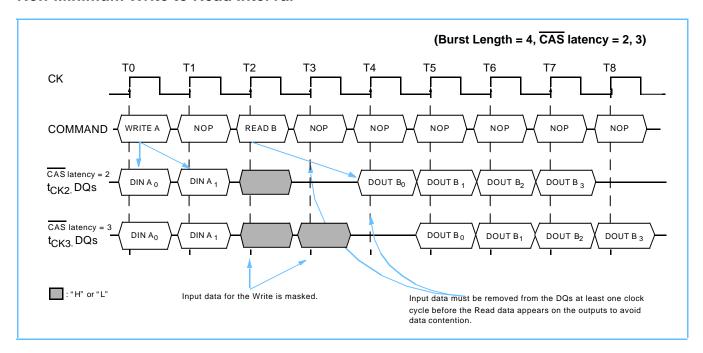

## Write Interrupted by a Read

A Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is registered. The DQs must be in the high impedance state at least one cycle before the interrupting read data appears on the outputs to avoid data contention. When the Read Command is registered, any residual data from the burst write cycle will be ignored. Data that is presented on the DQ pins before the Read Command is initiated will actually be written to the memory.

#### **Minimum Write to Read Interval**

### **Non-Minimum Write to Read Interval**

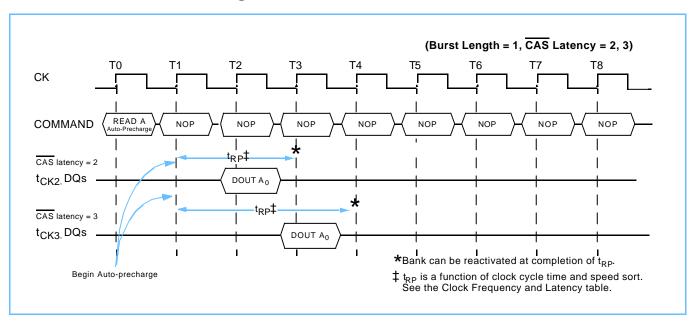

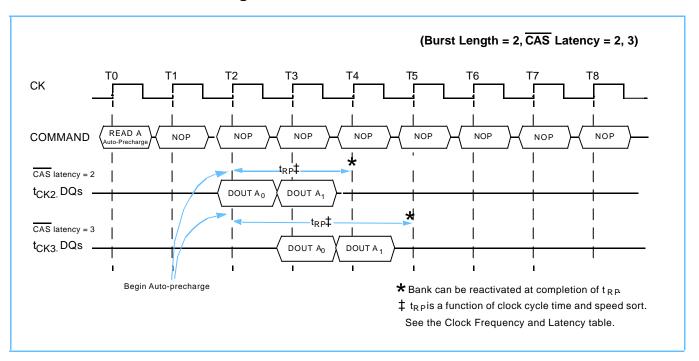

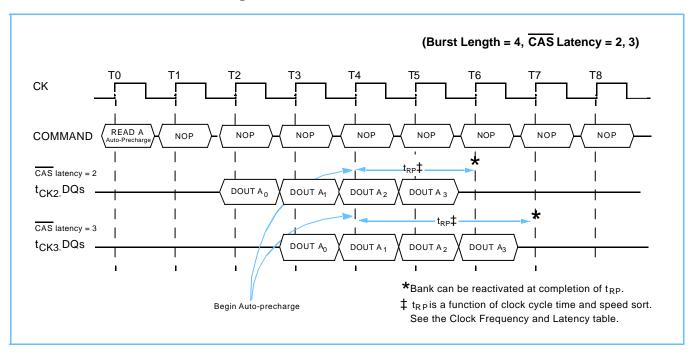

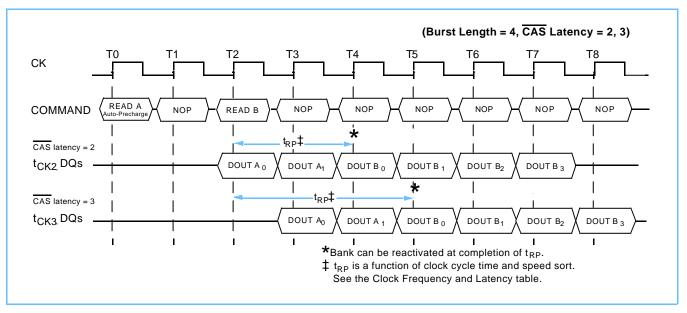

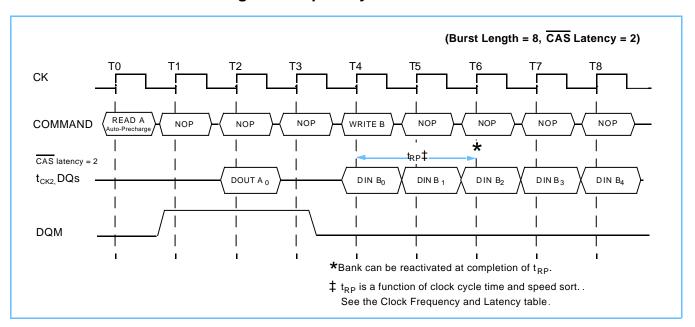

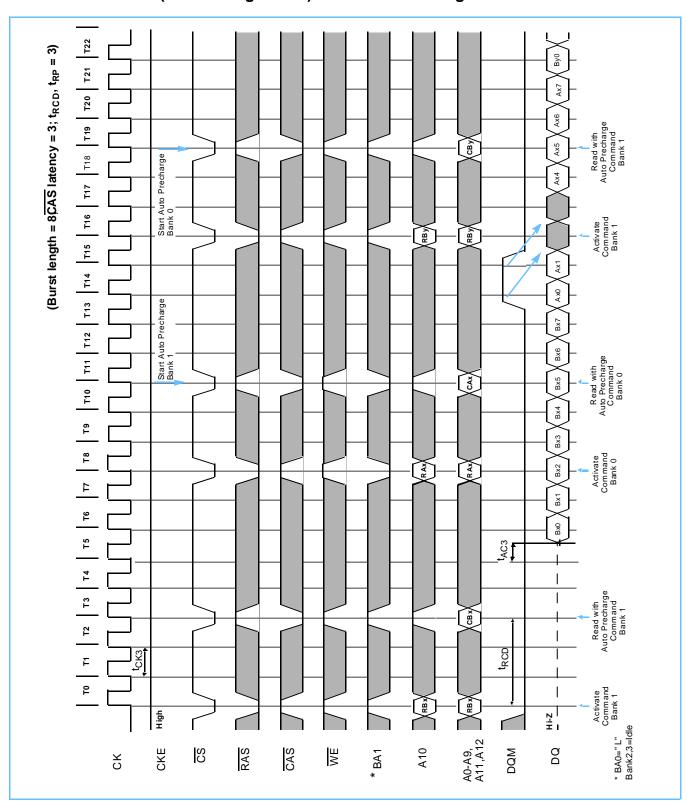

### **Auto-Precharge Operation**

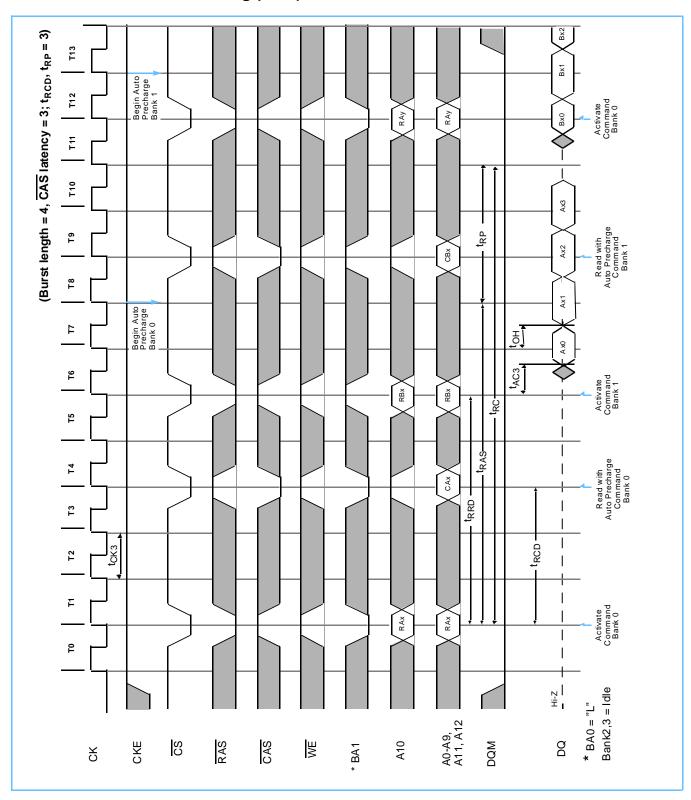

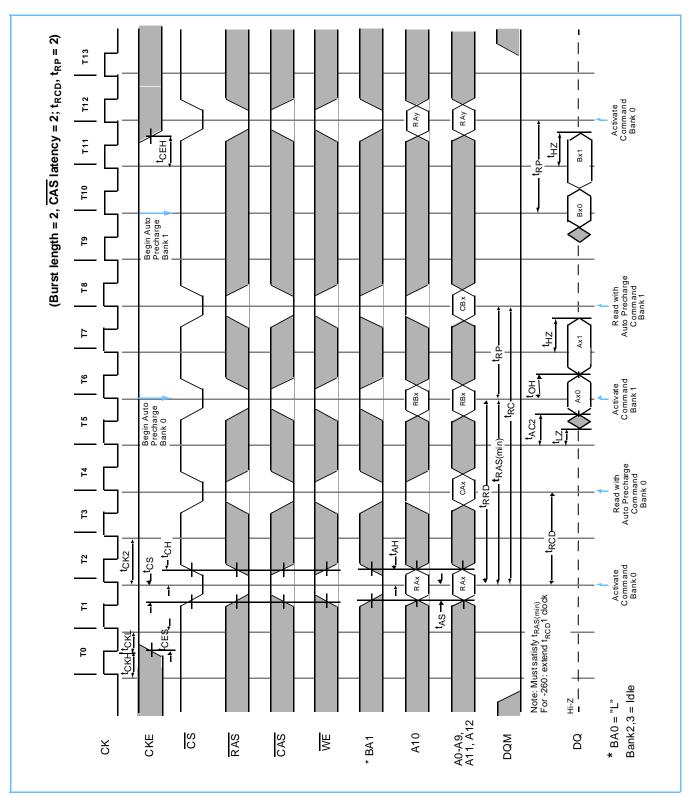

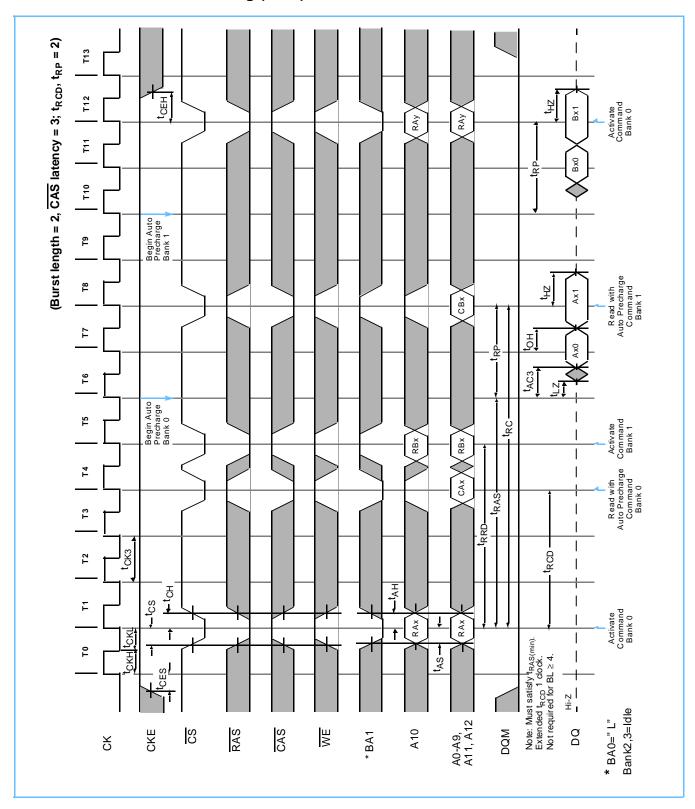

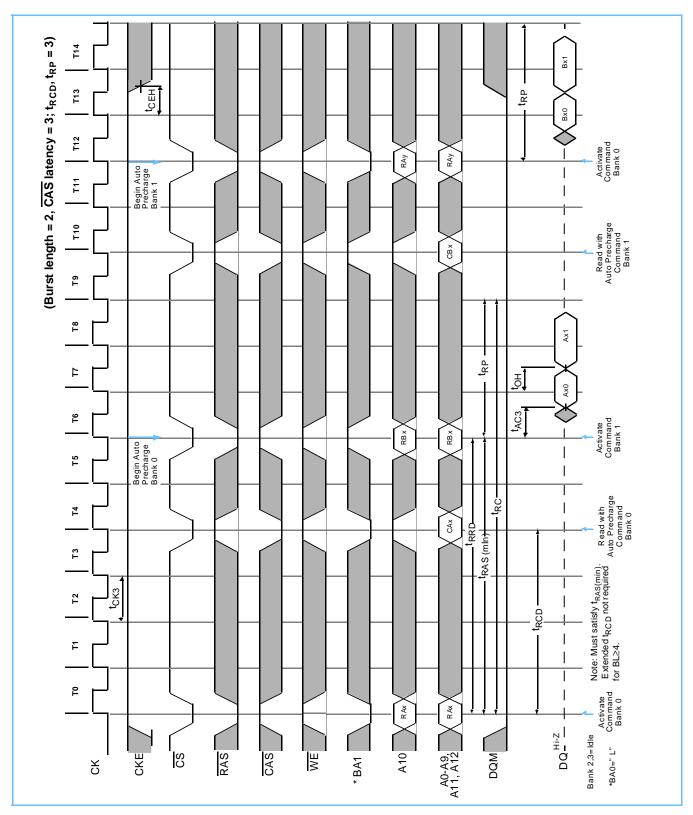

Before a new row in an active bank can be opened, the active bank must be precharged using either the Precharge Command or the auto-precharge function. When a Read or a Write Command is given to the SDRAM, the CAS timing accepts one extra address, column address A10, to allow the active bank to automatically begin precharge at the earliest possible moment during the burst read or write cycle. If A10 is low when the Read or Write Command is issued, then normal Read or Write burst operation is executed and the bank remains active at the completion of the burst sequence. If A10 is high when the Read or Write Command is issued, then the auto-precharge function is engaged. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge before all burst read cycles have been completed. Regardless of burst length, the precharge will begin (CAS latency - 1) clocks prior to the last data output. Auto-precharge can also be implemented during Write commands.

A Read or Write Command without auto-precharge can be terminated in the midst of a burst operation. However, a Read or Write Command with auto-precharge cannot be interrupted by a command to the same bank. Therefore use of a Read, Write, or Precharge Command to the same bank is prohibited during a read or write cycle with auto-precharge until the entire burst operation is completed. Once the precharge operation has started the bank cannot be reactivated until the Precharge time (t<sub>RP</sub>) has been satisfied.

When using the Auto-precharge Command, the interval between the Bank Activate Command and the beginning of the internal precharge operation must satisfy  $t_{RAS(min)}$ . If this interval does not satisfy  $t_{RAS(min)}$  then  $t_{RCD}$  must be extended.

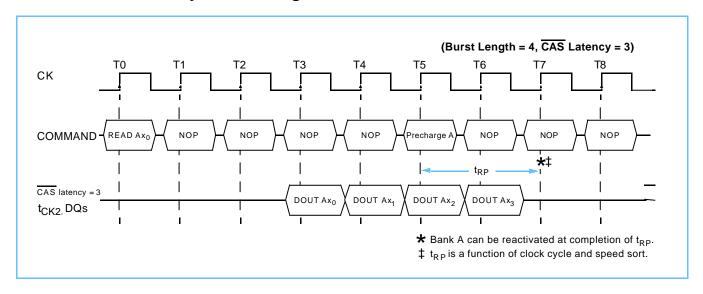

### **Burst Read with Auto-Precharge**

### **Burst Read with Auto-Precharge**

### **Burst Read with Auto-Precharge**

Although a Read Command with auto-precharge can not be interrupted by a command to the same bank, it can be interrupted by a Read or Write Command to a different bank. If the command is issued before auto-precharge begins then the precharge function will begin with the new command. The bank being auto-precharged may be reactivated after the delay  $t_{\rm RP}$ .

## **Burst Read with Auto-Precharge Interrupted by Read**

If interrupting a Read Command with auto-precharge with a Write Command, DQM must be used to avoid DQ contention.

### **Burst Read with Auto-Precharge Interrupted by Write**

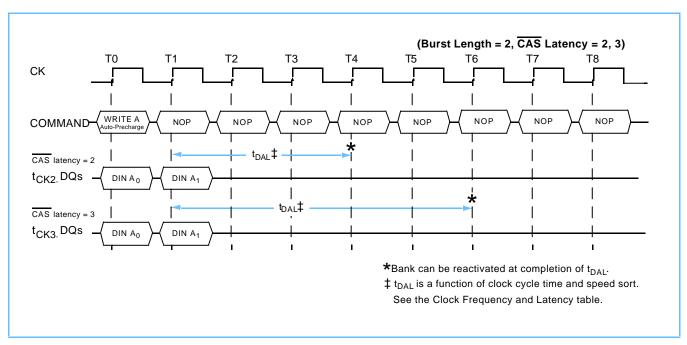

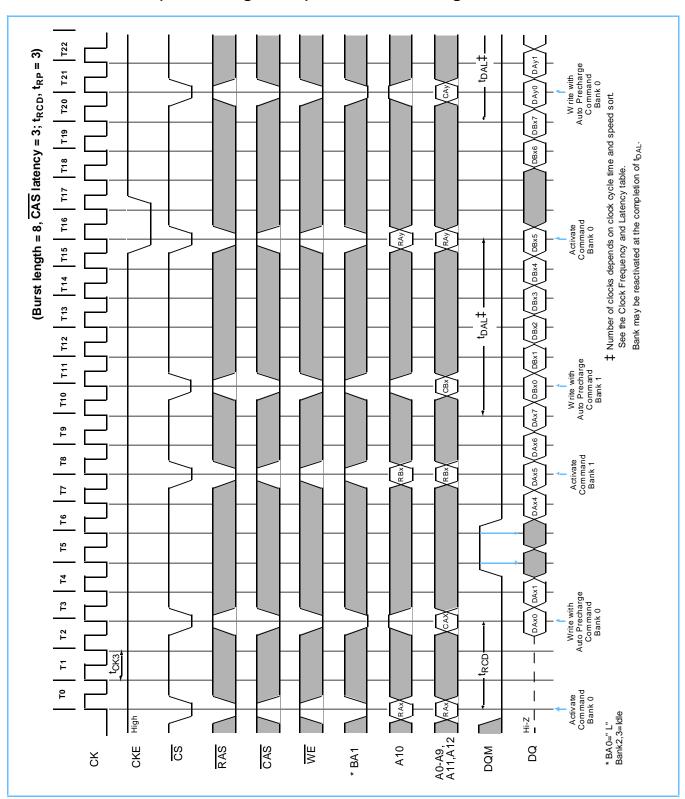

If A10 is high when a Write Command is issued, the Write with Auto-Precharge function is initiated. The bank undergoing auto-precharge cannot be reactivated until t<sub>DAL</sub>, Data-in to Active delay, is satisfied.

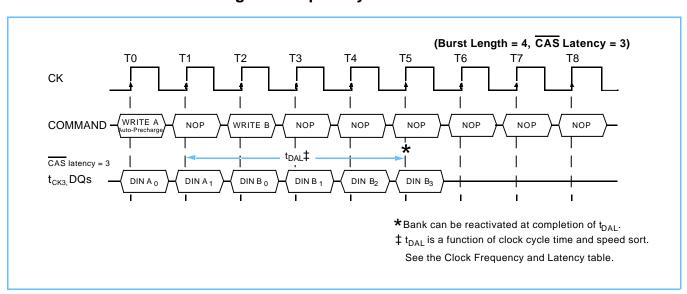

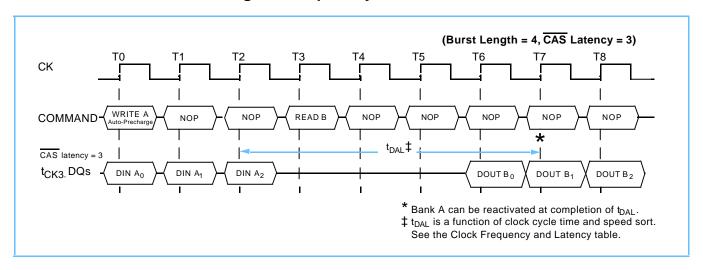

### **Burst Write with Auto-Precharge**

Similar to the Read Command, a Write Command with auto-precharge can not be interrupted by a command to the same bank. It can be interrupted by a Read or Write Command to a different bank, however. The interrupting command will terminate the write. The bank undergoing auto-precharge can not be reactivated until t<sub>DAL</sub> is satisfied.

### **Burst Write with Auto-Precharge Interrupted by Write**

### **Burst Write with Auto-Precharge Interrupted by Read**

## **Precharge Command**

The Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is triggered when CS, RAS, and WE are low and CAS is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or all banks simultaneously. Three address bits, A10, BA0, and BA1, are used to define which bank(s) is to be precharged when the command is issued.

### **Bank Selection for Precharge by Address Bits**

| A10  | Bank Select | Precharged Bank(s)              |

|------|-------------|---------------------------------|

| LOW  | BA0, BA1    | Single bank defined by BA0, BA1 |

| HIGH | DON' T CARE | All Banks                       |

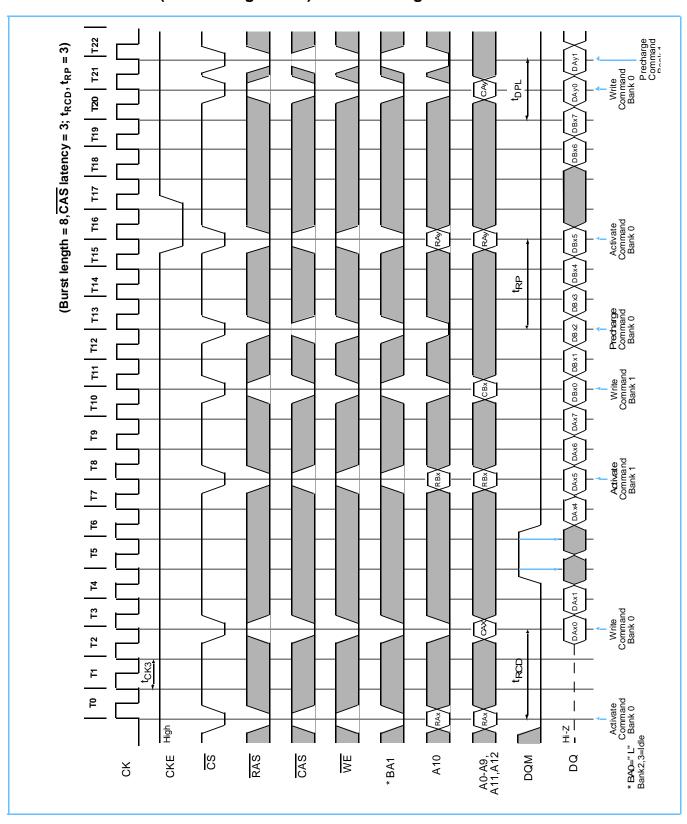

For read cycles, the Precharge Command may be applied ( $\overline{CAS}$  latency - 1) prior to the last data output. For write cycles, a delay must be satisfied from the start of the last burst write cycle until the Precharge Command can be issued. This delay is known as  $t_{DPI}$ , Data-in to Precharge delay.

After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time  $(t_{RP})$ .

## **Burst Read Followed by the Precharge Command**

## **Burst Write Followed by the Precharge Command**

## **Precharge Termination**

The Precharge Command may be used to terminate either a burst read or burst write operation. When the Precharge command is issued, the burst operation is terminated and bank precharge begins. For burst read operations, valid data will continue to appear on the data bus as a function of CAS Latency.

## **Burst Read Interrupted by Precharge**

Burst write operations will be terminated by the Precharge command. The last write data that will be properly stored in the device is that write data that is presented to the device a number of clock cycles prior to the Precharge command equal to the Data-in to Precharge delay, t<sub>DPL</sub>.

# **Precharge Termination of a Burst Write**

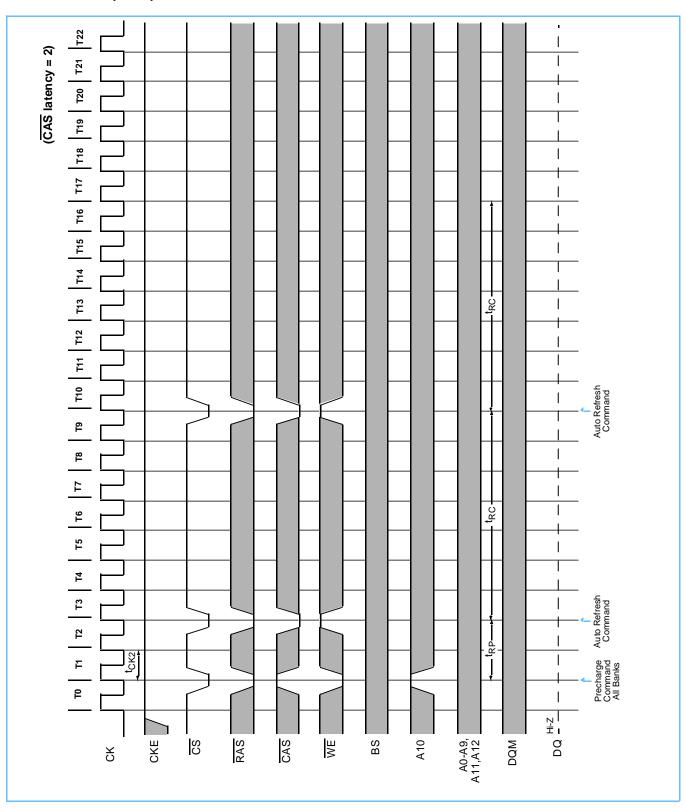

## Automatic Refresh Command (CAS before RAS Refresh)

When  $\overline{\text{CS}}$ ,  $\overline{\text{RAS}}$ , and  $\overline{\text{CAS}}$  are held low with CKE and  $\overline{\text{WE}}$  high at the rising edge of the clock, the chip enters the Automatic Refresh mode (CBR). All banks of the SDRAM must be precharged and idle for a minimum of the Precharge time ( $t_{RP}$ ) before the Auto Refresh Command (CBR) can be applied. An address counter, internal to the device provides the address during the refresh cycle. No control of the external address pins is required once this cycle has started.

When the refresh cycle has completed, all banks of the SDRAM will be in the precharged (idle) state. A delay between the Auto Refresh Command (CBR) and the next Activate Command or subsequent Auto Refresh Command must be greater than or equal to the  $\overline{RAS}$  cycle time ( $t_{RC}$ ).

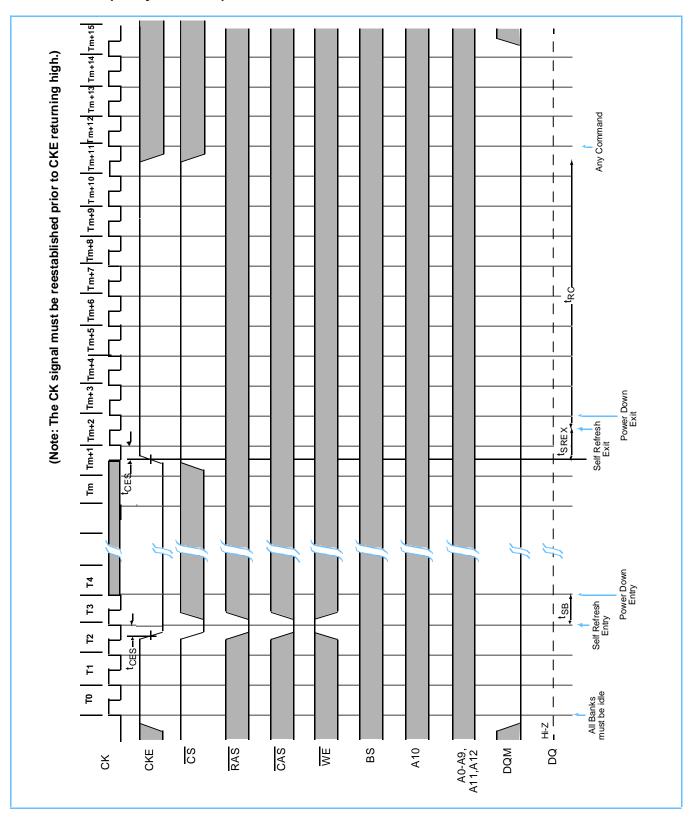

#### **Self Refresh Command**

The SDRAM device has a built-in timer to accommodate Self Refresh operation. The Self Refresh Command is defined by having CS, RAS, CAS, and CKE held low with WE high at the rising edge of the clock. All banks must be idle prior to issuing the Self Refresh Command. Once the command is registered, CKE must be held low to keep the device in Self Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The user may halt the external clock while the device is in Self Refresh mode, however, the clock must be restarted before the device can exit Self Refresh operation. Once the clock is cycling, the device will exit Self Refresh operation after CKE is returned high. A minimum delay time is required when the device exits Self Refresh Operation and before the next command can be issued. This delay is equal to the RAS cycle time (t<sub>RC</sub>) plus the Self Refresh exit time (t<sub>SREX</sub>).

#### **Power Down Mode**

In order to reduce standby power consumption, two power down modes are available: Precharge and Active Power Down mode. To enter Precharge Power Down mode, all banks must be precharged and the necessary precharge delay  $(t_{RP})$  must occur before the SDRAM can enter the power down mode. If a bank is activated but not performing a Read or Write operation, Active Power Down mode will be entered. (Issuing a Power Down Mode Command when the device is performing a Read or Write operation causes the device to enter Clock Suspend mode. See the following Clock Suspend section.) Once the Power Down mode is initiated by holding CKE low, all of the receiver circuits except CKE are gated off. The Power Down mode does not perform any refresh operations, therefore the device can't remain in Power Down mode longer than the Refresh period  $(t_{REF})$  of the device.

The Power Down mode is exited by bringing CKE high. When CKE goes high, a No Operation Command (or Device Deselect Command) is required on the next rising clock edge.

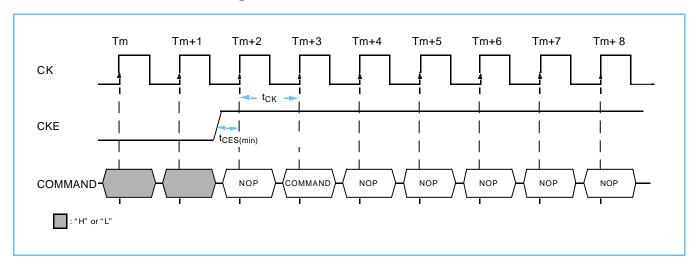

### **Power Down Mode Exit Timing**

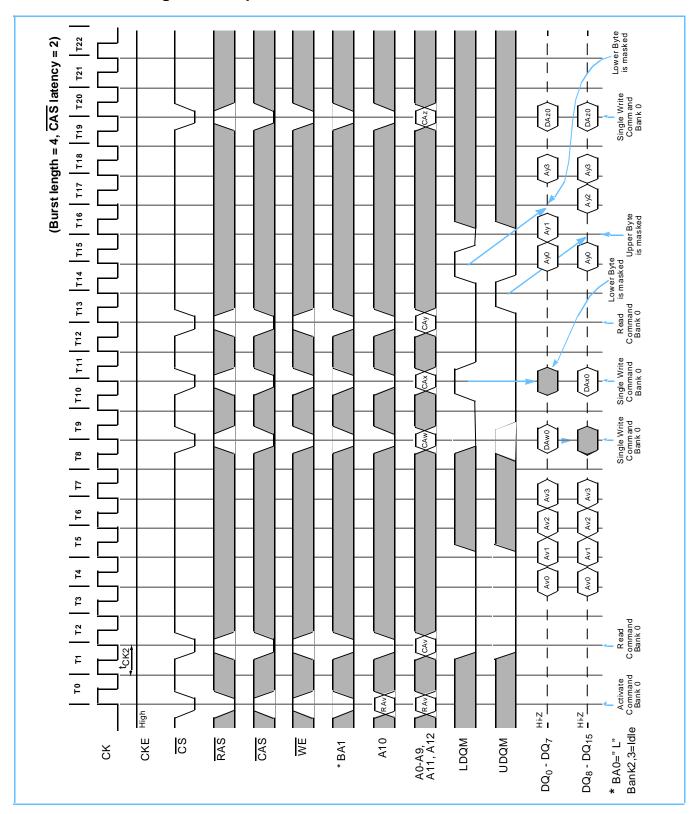

#### **Data Mask**

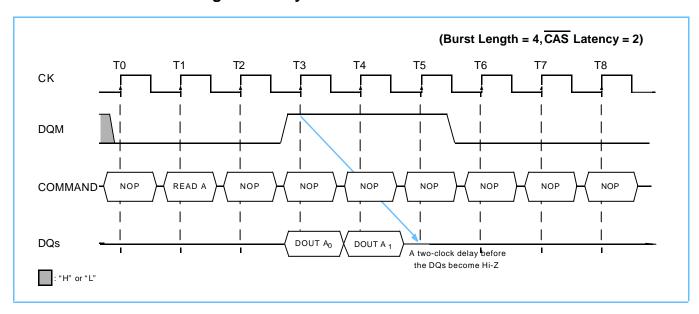

The SDRAM has a Data Mask function that can be used in conjunction with data read and write cycles. When the Data Mask is activated (DQM high) during a write cycle, the write operation is prohibited immediately (zero clock latency). If the Data Mask is activated during a read cycle, the data outputs are disabled and become high impedance after a two-clock delay, independent of CAS latency.

#### Data Mask Activated during a Read Cycle

### **No Operation Command**

The No Operation Command should be used in cases when the SDRAM is in an idle or a wait state. The purpose of the No Operation Command is to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when  $\overline{CS}$  is low with  $\overline{RAS}$ ,  $\overline{CAS}$ , and  $\overline{WE}$  held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.

#### **Deselect Command**

The Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when  $\overline{\text{CS}}$  is brought high, the  $\overline{\text{RAS}}$ ,  $\overline{\text{CAS}}$ , and  $\overline{\text{WE}}$  signals become don't cares.

#### **Clock Suspend Mode**

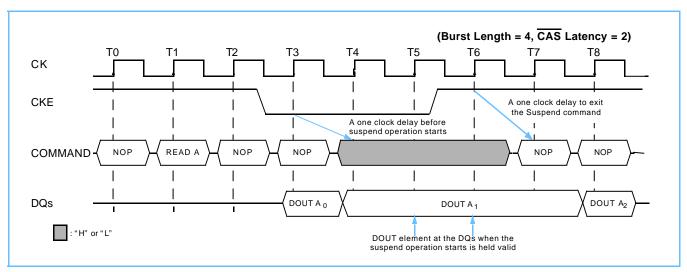

During normal access mode, CKE is held high, enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends or "freezes" any clocked operation that was currently being executed. There is a one-clock delay between the registration of CKE low and the time at which the SDRAM's operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.

When the operation of the SDRAM is suspended during the execution of a Burst Read operation, the last valid data output onto the DQ pins will be actively held valid until Clock Suspend mode is exited.

### Clock Suspend during a Read Cycle

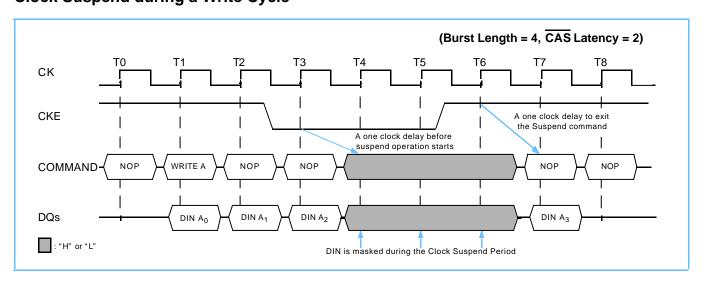

If Clock Suspend mode is initiated during a burst write operation, the input data is masked and is ignored until the Clock Suspend mode is exited.

### **Clock Suspend during a Write Cycle**

#### Command Truth Table (See note 1)

|                           |                            | Ck                | Œ                |    |     |     |    |     | BA0.        |        | A12,          |       |

|---------------------------|----------------------------|-------------------|------------------|----|-----|-----|----|-----|-------------|--------|---------------|-------|

| Function                  | Device State               | Previous<br>Cycle | Current<br>Cycle | CS | RAS | CAS | WE | DQM | BA0,<br>BA1 | A10    | A11,<br>A9-A0 | Notes |

| Mode Register Set         | Idle                       | Н                 | Х                | L  | L   | L   | L  | Χ   |             | OP Cod | de            |       |

| Auto (CBR) Refresh        | Idle                       | Н                 | Н                | L  | L   | L   | Н  | Х   | Х           | Х      | Х             |       |

| Entry Self Refresh        | Idle                       | Н                 | L                | L  | L   | L   | Н  | Х   | Х           | Х      | Х             |       |

| Exit Self Refresh         | Idle (Self-                | L                 | Н                | Н  | Х   | Х   | Х  | Х   | Х           | Х      | Х             |       |

|                           | Refresh)                   |                   |                  | L  | Н   | Н   | Н  |     |             |        |               |       |

| Single Bank Precharge     | See Current<br>State Table | Н                 | Х                | L  | L   | Н   | L  | Х   | BS          | L      | Х             | 2     |

| Precharge all Banks       | See Current<br>State Table | Н                 | Х                | L  | L   | Н   | L  | Х   | Х           | Н      | Х             |       |

| Bank Activate             | Idle                       | Н                 | Х                | L  | L   | Н   | Н  | Х   | BS          | Row    | Row Address   |       |

| Write                     | Active                     | Н                 | Х                | L  | Н   | L   | L  | Х   | BS          | L      | Column        | 2     |

| Write with Auto-Precharge | Active                     | Н                 | Х                | L  | Н   | L   | L  | Х   | BS          | Н      | Column        | 2     |

| Read                      | Active                     | Н                 | Х                | L  | Н   | L   | Н  | Х   | BS          | L      | Column        | 2     |

| Read with Auto-Precharge  | Active                     | Н                 | Х                | L  | Н   | L   | Н  | Х   | BS          | Н      | Column        | 2     |

| Reserved                  |                            | Н                 | Х                | L  | Н   | Н   | L  | Х   | Х           | Х      | Х             |       |

| No Operation              | Any                        | Н                 | Х                | L  | Н   | Н   | Н  | Х   | Х           | Х      | Х             |       |

| Device Deselect           | Any                        | Н                 | Х                | Н  | Х   | Х   | Х  | Х   | Χ           | Х      | Х             |       |

| Clock Suspend Mode Entry  | Active                     | Н                 | L                | Х  | Х   | Х   | Х  | Х   | Х           | Х      | Х             | 4     |

| Clock Suspend Mode Exit   | Active                     | L                 | Н                | Х  | Х   | Х   | Х  | Х   | Х           | Х      | Х             | 4     |

| Data Write/Output Enable  | Active                     | Н                 | Х                | Х  | Х   | Х   | Х  | L   | Χ           | Х      | Х             | -     |

| Data Mask/Output Disable  | Active                     | Н                 | Х                | Х  | Х   | Х   | Х  | Н   | Х           | Х      | Х             | 5     |

| Power Down Mode Entry     | Idle/Active                | Н                 | L                | Н  | Х   | Х   | Х  | Х   | Х           | Х      | Х             | 6, 7  |

| rower Down wode Entry     | idie/Active                | п                 | L                | L  | Н   | Н   | Н  | ^   | ^           | ^      | X             | ο, ι  |

| Power Down Mode Exit      | Any (Power                 |                   |                  | Н  | Х   | Х   | Х  | Х   | Х           | v      | Х             | 6.7   |

| Power Down Mode Exit      | Down)                      | L                 | Н                | L  | Н   | Н   | Н  | ۸   | ۸           | Х      | ۸             | 6, 7  |

- 1. All of the SDRAM operations are defined by states of  $\overline{CS}$ ,  $\overline{WE}$ ,  $\overline{RAS}$ ,  $\overline{CAS}$ , and DQM at the positive rising edge of the clock. Refer to the Current State Truth Table.

- 2. Bank Select (BA0, BA1): BA0, BA1 = 0,0 selects bank 0; BA0, BA1 = 1,0 selects bank 1; BA0, BA1 = 0,1 selects bank 2; BA0, BA1 = 1,1 selects bank 3.

- 3. Not applicable.

- 4. During normal access mode, CKE is held high and CK is enabled. When it is low, it freezes the internal clock and extends data Read and Write operations. One clock delay is required for mode entry and exit.

- 5. The DQM has two functions for the data DQ Read and Write operations. During a Read cycle, when DQM goes high at a clock timing the data outputs are disabled and become high impedance after a two-clock delay. DQM also provides a data mask function for Write cycles. When it activates, the Write operation at the clock is prohibited (zero clock latency).

- 6. All banks must be precharged before entering the Power Down Mode. (If this command is issued during a burst operation, the device state will be Clock Suspend Mode.) The Power Down Mode does not perform any refresh operations; therefore the device can't remain in this mode longer than the Refresh period (t<sub>REF</sub>) of the device. One clock delay is required for mode entry and exit.

- 7. A No Operation or Device Deselect Command is required on the next clock edge following CKE going high.

## **Clock Enable (CKE) Truth Table**

|                      | CI                | KE               |    |     | Co  | mmand |             |           |                                                                     |       |

|----------------------|-------------------|------------------|----|-----|-----|-------|-------------|-----------|---------------------------------------------------------------------|-------|

| Current State        | Previous<br>Cycle | Current<br>Cycle | cs | RAS | CAS | WE    | BA0,<br>BA1 | A 12 - A0 | Action                                                              | Notes |

|                      | Н                 | Х                | Х  | Х   | Х   | Х     | Х           | Х         | INVALID                                                             | 1     |

|                      | L                 | Н                | Н  | Х   | Х   | Х     | Х           | Х         | Exit Self Refresh with Device Deselect                              | 2     |

|                      | L                 | Н                | L  | Н   | Н   | Н     | Х           | Х         | Exit Self Refresh with No Operation                                 | 2     |

| Self Refresh         | L                 | Н                | L  | Н   | Н   | L     | Х           | Х         | ILLEGAL                                                             | 2     |

|                      | L                 | Н                | L  | Н   | L   | Х     | Х           | Х         | ILLEGAL                                                             | 2     |

|                      | L                 | Н                | L  | L   | Х   | Х     | X           | Х         | ILLEGAL                                                             | 2     |

|                      | L                 | L                | Х  | Х   | Х   | Х     | Х           | Х         | Maintain Self Refresh                                               |       |

|                      | Н                 | Х                | Х  | Х   | Х   | Х     | Х           | Х         | INVALID                                                             | 1     |

| Power Down           | L                 | Н                | Н  | Х   | Х   | Х     | Х           | Х         | Power Down mode exit, all banks idle                                | 2     |

| Fower Down           | L                 | Н                | L  | Х   | Х   | Х     | Х           | Х         | ILLEGAL                                                             | 2     |

| 1                    | L                 | L                | Х  | Х   | Х   | Х     | Х           | Х         | Maintain Power Down Mode                                            |       |

|                      | Н                 | Н                | Н  | Х   | Х   | Х     |             |           |                                                                     | 3     |

|                      | Н                 | Н                | L  | Н   | Х   | Х     |             |           | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                      | Н                 | Н                | L  | L   | Н   | Х     |             |           |                                                                     | 3     |

|                      | Н                 | Н                | L  | L   | L   | Н     | Х           | Х         | CBR Refresh                                                         |       |

|                      | Н                 | Н                | L  | L   | L   | L     | OP (        | Code      | Mode Register Set                                                   | 4     |

| All Banks Idle       | Н                 | L                | Н  | Х   | Х   | Х     |             |           | <u>.</u>                                                            | 3     |

|                      | Н                 | L                | L  | Н   | Х   | Х     |             |           | Refer to the Idle State section of the<br>Current State Truth Table | 3     |

|                      | Н                 | L                | L  | L   | Н   | Х     |             |           |                                                                     | 3     |

|                      | Н                 | L                | L  | L   | L   | Н     | Х           | Х         | Entry Self Refresh                                                  | 4     |

|                      | Н                 | L                | L  | L   | L   | L     | OP (        | Code      | Mode Register Set                                                   |       |

|                      | L                 | Х                | Х  | Х   | Х   | Х     | Х           | Х         | Power Down                                                          | 4     |

| A 0: 1               | Н                 | Н                | Х  | Х   | Х   | Х     | Х           | х         | Refer to operations in the Current State Truth Table                |       |

| Any State other than | Н                 | L                | Х  | Х   | Х   | Х     | Х           | Х         | Begin Clock Suspend next cycle                                      | 5     |

| listed above         | L                 | Н                | Х  | Х   | Х   | Х     | Х           | Х         | Exit Clock Suspend next cycle                                       |       |

|                      | L                 | L                | Х  | Х   | Х   | Х     | Х           | Х         | Maintain Clock Suspend                                              |       |

- 1. For the given Current State CKE must be low in the previous cycle.

- 2. When CKE has a low to high transition, the clock and other inputs are re-enabled asynchronously. The minimum setup time for CKE (t<sub>CES</sub>) must be satisfied. When exiting power down mode, a NOP command (or Device Deselect Command) is required on the first rising clock after CKE goes high (see page 26).

- 3. The address inputs depend on the command that is issued. See the Idle State section of the Current State Truth Table for more information.

- 4. The Precharge Power Down Mode, the Self Refresh Mode, and the Mode Register Set can only be entered from the all banks idle state.

- 5. Must be a legal command as defined in the Current State Truth Table.

#### Current State Truth Table (Part 1 of 3)(See note 1)

| Current State |    |     |     |    | Con     | nmand             |                      | Action                                   | Notes  |

|---------------|----|-----|-----|----|---------|-------------------|----------------------|------------------------------------------|--------|

| Current State | CS | RAS | CAS | WE | BA0,BA1 | A12 - A0          | Description          | Action                                   | 140163 |

|               | L  | L   | L   | L  | OF      | Code              | Mode Register Set    | Set the Mode Register                    | 2      |

|               | L  | L   | L   | Н  | Х       | Х                 | Auto or Self Refresh | Start Auto or Self Refresh               | 2, 3   |

|               | L  | L   | Н   | L  | BS      | Х                 | Precharge            | No Operation                             |        |

| ldle          | L  | L   | Н   | Н  | BS      | Row Address       | Bank Activate        | Activate the specified bank and row      |        |

| lule          | L  | Н   | L   | L  | BS      | Column            | Write w/o Precharge  | ILLEGAL                                  | 4      |

|               | L  | Н   | L   | Н  | BS      | Column            | Read w/o Precharge   | ILLEGAL                                  | 4      |

|               | L  | Н   | Н   | Н  | Х       | Х                 | No Operation         | No Operation                             |        |

|               | Н  | Χ   | Х   | Х  | Х       | Х                 | Device Deselect      | No Operation or Power Down               | 5      |

|               | L  | L   | L   | L  | OF      | Code              | Mode Register Set    | ILLEGAL                                  |        |

|               | L  | L   | L   | Н  | Х       | Х                 | Auto or Self Refresh | ILLEGAL                                  |        |

|               | L  | L   | Н   | L  | BS      | Х                 | Precharge            | Precharge                                | 6      |

| Row Active    | L  | L   | Н   | Н  | BS      | Row Address       | Bank Activate        | ILLEGAL                                  | 4      |

| Now Active    | L  | Н   | L   | L  | BS      | Column            | Write                | Start Write; Determine if Auto Precharge | 7, 8   |

|               | L  | Н   | L   | Н  | BS      | Column            | Read                 | Start Read; Determine if Auto Precharge  | 7, 8   |

|               | L  | Н   | Н   | Н  | Х       | Х                 | No Operation         | No Operation                             |        |

|               | Н  | Х   | Х   | Х  | Х       | Х                 | Device Deselect      | No Operation                             |        |

|               | L  | L   | L   | L  | OF      | <sup>2</sup> Code | Mode Register Set    | ILLEGAL                                  |        |

|               | L  | L   | L   | Н  | Х       | Х                 | Auto or Self Refresh | ILLEGAL                                  |        |

|               | L  | L   | Н   | L  | BS      | Х                 | Precharge            | Terminate Burst; Start the Precharge     |        |

| Read          | L  | L   | Н   | Н  | BS      | Row Address       | Bank Activate        | ILLEGAL                                  | 4      |

| Read          | L  | Н   | L   | L  | BS      | Column            | Write                | Terminate Burst; Start the Write cycle   | 8, 9   |

|               | L  | Н   | L   | Н  | BS      | Column            | Read                 | Terminate Burst; Start a new Read cycle  | 8, 9   |

|               | L  | Н   | Н   | Н  | Х       | Х                 | No Operation         | Continue the Burst                       |        |

|               | Н  | Х   | Х   | Х  | Х       | Х                 | Device Deselect      | Continue the Burst                       |        |

|               | L  | L   | L   | L  | OF      | <sup>2</sup> Code | Mode Register Set    | ILLEGAL                                  |        |

|               | L  | L   | L   | Н  | Х       | Х                 | Auto or Self Refresh | ILLEGAL                                  |        |

|               | L  | L   | Н   | L  | BS      | Х                 | Precharge            | Terminate Burst; Start the Precharge     |        |

| Write         | L  | L   | Н   | Н  | BS      | Row Address       | Bank Activate        | ILLEGAL                                  | 4      |

| VVIILE        | L  | Н   | L   | L  | BS      | Column            | Write                | Terminate Burst; Start a new Write cycle | 8, 9   |

|               | L  | Н   | L   | Н  | BS      | Column            | Read                 | Terminate Burst; Start the Read cycle    | 8, 9   |

|               | L  | Н   | Н   | Н  | Х       | Х                 | No Operation         | Continue the Burst                       |        |

|               | Н  | Х   | Χ   | Χ  | X       | Х                 | Device Deselect      | Continue the Burst                       |        |

- 1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

- 2. All Banks must be idle; otherwise, it is an illegal action.

- 3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh operation, if CKE is inactive (low) than the Self Refresh mode is entered

- 4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

- 5. If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.

- 6. The minimum and maximum Active time  $(t_{RAS})$  must be satisfied.

- 7. The RAS to CAS Delay (t<sub>RCD</sub>) must occur before the command is given.

- 8. Column address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

- 10. The command is illegal if the minimum bank to bank delay time  $(t_{\mbox{\scriptsize RRD}})$  is not satisfied.

### Current State Truth Table (Part 2 of 3)(See note 1)

| Current State          |    |     |     |    | Con     | nmand       |                      | Action                                           | Notes  |

|------------------------|----|-----|-----|----|---------|-------------|----------------------|--------------------------------------------------|--------|

| ourrent otate          | CS | RAS | CAS | WE | BA0,BA1 | A12 - A0    | Description          | Action                                           | 140103 |

|                        | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                          |        |

|                        | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |        |

|                        | L  | L   | Н   | L  | BS      | Х           | Precharge            | ILLEGAL                                          | 4      |

| Read with<br>Auto Pre- | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4      |

| charge                 | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4      |

| Ö                      | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                          | 4      |

|                        | L  | Н   | Н   | Н  | X       | Х           | No Operation         | Continue the Burst                               |        |

|                        | Н  | Х   | Х   | Х  | X       | Х           | Device Deselect      | Continue the Burst                               |        |

|                        | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                          |        |

|                        | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |        |

|                        | L  | L   | Н   | L  | BS      | Х           | Precharge            | ILLEGAL                                          | 4      |

| Write with Auto        | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4      |

| Precharge              | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4      |

|                        | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                          | 4      |

|                        | L  | Н   | Н   | Н  | Х       | Х           | No Operation         | Continue the Burst                               |        |

|                        | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | Continue the Burst                               |        |

|                        | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                          |        |

|                        | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |        |

|                        | L  | L   | Н   | L  | BS      | Х           | Precharge            | No Operation; Bank(s) idle after t <sub>RP</sub> |        |

| Precharging            | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4      |

| Frecharging            | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4      |

|                        | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                          | 4      |

|                        | L  | Н   | Н   | Н  | X       | Х           | No Operation         | No Operation; Bank(s) idle after t <sub>RP</sub> |        |

|                        | Н  | Х   | Х   | Х  | X       | Х           | Device Deselect      | No Operation; Bank(s) idle after t <sub>RP</sub> |        |

|                        | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                          |        |

|                        | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                          |        |

|                        | L  | L   | Н   | L  | BS      | Х           | Precharge            | ILLEGAL                                          | 4      |

| Row                    | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                          | 4, 10  |

| Activating             | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                          | 4      |

|                        | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                          | 4      |

|                        | L  | Н   | Н   | Н  | Х       | Х           | No Operation         | No Operation; Row Active after t <sub>RCD</sub>  |        |

|                        | Н  | Χ   | Х   | Х  | Х       | X           | Device Deselect      | No Operation; Row Active after t <sub>RCD</sub>  |        |

- 1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

- 2. All Banks must be idle; otherwise, it is an illegal action.

- 3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh operation, if CKE is inactive (low) than the Self Refresh mode is

- 4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

- $5. \ \ \text{If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.}$

- 6. The  $\underline{\text{minimum}}$  and maximum Active time ( $t_{\text{RAS}}$ ) must be satisfied.

- 7. The  $\overline{RAS}$  to  $\overline{CAS}$  Delay (t<sub>RCD</sub>) must occur before the command is given.

- 8. Column address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

- 10. The command is illegal if the minimum bank to bank delay time (t<sub>RRD</sub>) is not satisfied.

## Current State Truth Table (Part 3 of 3)(See note 1)

| Current State      |    |     |     |    | Con     | nmand       |                      | Action                                          | Notes  |

|--------------------|----|-----|-----|----|---------|-------------|----------------------|-------------------------------------------------|--------|

| Ourrent State      | CS | RAS | CAS | WE | BA0,BA1 | A12 - A0    | Description          | Action                                          | 140163 |

|                    | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                         |        |

|                    | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |        |

|                    | L  | L   | Н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         | 4      |

| Write              | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         | 4      |

| Recovering         | L  | Н   | L   | L  | BS      | Column      | Write                | Start Write; Determine if Auto Precharge        | 9      |

|                    | L  | Н   | L   | Н  | BS      | Column      | Read                 | Start Read; Determine if Auto Precharge         | 9      |

|                    | L  | Н   | Н   | Н  | Х       | Х           | No Operation         | No Operation; Row Active after t <sub>DPL</sub> |        |

|                    | Н  | Х   | Х   | Х  | X       | X           | Device Deselect      | No Operation; Row Active after t <sub>DPL</sub> |        |

|                    | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                         |        |

|                    | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |        |

| Write              | L  | L   | Н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         | 4      |

| Recovering<br>with | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         | 4      |

| Auto Pre-          | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                         | 4, 9   |

| charge             | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                         | 4, 9   |

|                    | L  | Н   | Н   | Н  | Х       | Х           | No Operation         | No Operation; Precharge after t <sub>DPL</sub>  |        |

|                    | Н  | Х   | Х   | Х  | Х       | Х           | Device Deselect      | No Operation; Precharge after t <sub>DPL</sub>  |        |

|                    | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                         |        |

|                    | L  | L   | L   | Н  | Х       | Х           | Auto or Self Refresh | ILLEGAL                                         |        |

|                    | L  | L   | Н   | L  | BS      | Х           | Precharge            | ILLEGAL                                         |        |

| Refreshing         | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         |        |

| Refreshing         | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                         |        |

|                    | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                         |        |

|                    | L  | Н   | Н   | Н  | Х       | X           | No Operation         | No Operation; Idle after t <sub>RC</sub>        |        |

|                    | Н  | Х   | Х   | Х  | Х       | X           | Device Deselect      | No Operation; Idle after t <sub>RC</sub>        |        |

|                    | L  | L   | L   | L  | OF      | Code        | Mode Register Set    | ILLEGAL                                         |        |

|                    | L  | L   | L   | Н  | Х       | X           | Auto or Self Refresh | ILLEGAL                                         |        |

|                    | L  | L   | Н   | L  | BS      | X           | Precharge            | ILLEGAL                                         |        |

| Mode<br>Register   | L  | L   | Н   | Н  | BS      | Row Address | Bank Activate        | ILLEGAL                                         |        |

| Accessing          | L  | Н   | L   | L  | BS      | Column      | Write                | ILLEGAL                                         |        |

| · ·                | L  | Н   | L   | Н  | BS      | Column      | Read                 | ILLEGAL                                         |        |

|                    | L  | Н   | Н   | Н  | Х       | Х           | No Operation         | No Operation; Idle after two clock cycles       |        |

|                    | Н  | Х   | Х   | Х  | Х       | X           | Device Deselect      | No Operation; Idle after two clock cycles       |        |

- 1. CKE is assumed to be active (high) in the previous cycle for all entries. The Current State is the state of the bank that the Command is being applied to.

- 2. All Banks must be idle; otherwise, it is an illegal action.

- 3. If CKE is active (high) the SDRAM will start the Auto (CBR) Refresh operation, if CKE is inactive (low) than the Self Refresh mode is

- 4. The Current State refers to only one of the banks. If BS selects this bank then the action is illegal. If BS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

- 5. If CKE is inactive (low) then the Power Down mode is entered; otherwise there is a No Operation.

- 6. The  $\underline{\text{minimum}}$  and maximum Active time  $(t_{\text{RAS}})$  must be satisfied.

- 7. The RAS to CAS Delay (t<sub>RCD</sub>) must occur before the command is given.

- 8. Column address A10 is used to determine if the Auto Precharge function is activated.

- 9. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements.

- 10. The command is illegal if the minimum bank to bank delay time  $(t_{\mbox{\scriptsize RRD}})$  is not satisfied.

## **Absolute Maximum Ratings**

| Symbol           | Parameter                       | Rating                       | Units | Notes |

|------------------|---------------------------------|------------------------------|-------|-------|

| V <sub>DD</sub>  | Power Supply Voltage            | -0.3 to +4.6                 | V     | 1     |

| $V_{DDQ}$        | Power Supply Voltage for Output | -0.3 to +4.6                 | V     | 1     |

| V <sub>IN</sub>  | Input Voltage                   | -0.3 to V <sub>DD</sub> +0.3 | V     | 1     |

| V <sub>OUT</sub> | Output Voltage                  | -0.3 to V <sub>DD</sub> +0.3 | V     | 1     |

| T <sub>A</sub>   | Operating Temperature (ambient) | 0 to +70                     | °C    | 1     |

| T <sub>STG</sub> | Storage Temperature             | -55 to +125                  | °C    | 1     |

| $P_{D}$          | Power Dissipation               | 1.0                          | W     | 1     |

| I <sub>OUT</sub> | Short Circuit Output Current    | 50                           | mA    | 1     |

<sup>1.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **Recommended DC Operating Conditions** $(T_A = 0^{\circ}C \text{ to } 70^{\circ}C)$

| Symbol                            | Dozomator                 |      | Rating | Units                 | Notos |       |  |

|-----------------------------------|---------------------------|------|--------|-----------------------|-------|-------|--|

|                                   | Parameter                 | Min. | Тур.   | Max.                  | Units | Notes |  |

| $V_{DD}$                          | Supply Voltage            | 3.0  | 3.3    | 3.6                   | V     | 1     |  |

| $V_{DDQ}$                         | Supply Voltage for Output | 3.0  | 3.3    | 3.6                   | V     | 1     |  |

| V <sub>IH</sub>                   | Input High Voltage        | 2.0  | _      | V <sub>DD</sub> + 0.3 | V     | 1, 2  |  |

| V <sub>IL</sub> Input Low Voltage |                           | -0.3 | _      | 0.8                   | V     | 1, 3  |  |

<sup>1.</sup> All voltages referenced to  $V_{\mbox{SS}}$  and  $V_{\mbox{SSQ}}$

## **Capacitance** ( $T_A = 25^{\circ}C$ , f = 1MHz, $V_{DD} = 3.3V \pm 0.3V$ )

|                | Symbol                                                           | Parameter                       | Min. | Тур | Max. | Units | Notes |

|----------------|------------------------------------------------------------------|---------------------------------|------|-----|------|-------|-------|

| C <sub>I</sub> | Input Capacitance (A0-A12, BA0, BA1, CS, RAS, CAS, WE, CKE, DQM) | 2.5                             | 3.0  | 3.8 | pF   |       |       |

|                | Input Capacitance (CK)                                           | 2.5                             | 2.8  | 3.5 | pF   |       |       |

|                | C <sub>O</sub>                                                   | Output Capacitance (DQ0 - DQ15) | 4.0  | 4.5 | 6.5  | pF    |       |

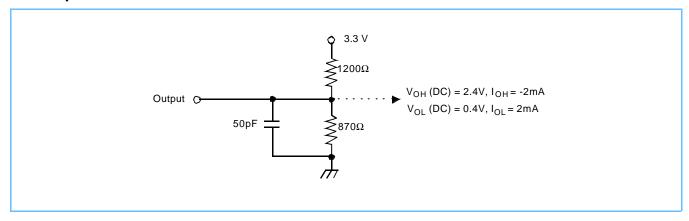

<sup>2.</sup>  $V_{IH}$  (max) =  $V_{DD}$  + 1.2V for pulse width  $\leq$  5ns.