### INTEGRATED CIRCUITS

# DATA SHEET

# OM5193H Disk drive spindle and VCM with servo controller

Product specification

File under Integrated Circuits, IC11

1998 Nov 02

# Disk drive spindle and VCM with servo controller

### OM5193H

| CONTENT        | rs                                   | 9            | LIMITING VALUES                 |

|----------------|--------------------------------------|--------------|---------------------------------|

| 1              | FEATURES                             | 10           | HANDLING                        |

|                |                                      | 11           | THERMAL CHARACTERISTICS         |

| 1.1<br>1.2     | Servo control  Motor control         | 12           | CHARACTERISTICS                 |

| 1.2.1          | Spindle motor driver                 | 13           | APPLICATION INFORMATION         |

| 1.2.2          | Voice coil motor driver              | 14           |                                 |

| 1.3            | Miscellaneous items                  |              | PACKAGE OUTLINE                 |

| 2              | APPLICATIONS                         | 15           | SOLDERING                       |

| 3              | GENERAL DESCRIPTION                  | 15.1         | Introduction                    |

| 3.1            | Overview                             | 15.2<br>15.3 | Reflow soldering Wave soldering |

| 3.2            | Servo controller                     | 15.4         | Repairing soldered joints       |

| 3.3            | Spindle and voice coil motor         | 16           | DEFINITIONS                     |

| 3.4            | Safety functions                     |              |                                 |

| 4              | QUICK REFERENCE DATA                 | 17           | LIFE SUPPORT APPLICATIONS       |

| 5              | ORDERING INFORMATION                 |              |                                 |

| 6              | BLOCK DIAGRAMS                       |              |                                 |

| 7              | PINNING                              |              |                                 |

| 8              | FUNCTIONAL DESCRIPTION               |              |                                 |

| 8.1            | Serial interface                     |              |                                 |

| 8.2            | Commutation and sleep mode           |              |                                 |

| 8.3            | Commutation control                  |              |                                 |

| 8.3.1          | Blanks, Watchdog and Start-up delays |              |                                 |

| 8.3.2          | Comdelim delay                       |              |                                 |

| 8.4            | 10-bit ADC with 7 analog inputs      |              |                                 |

| 8.4.1          | Input channels                       |              |                                 |

| 8.4.2<br>8.4.3 | Input ranges Conversion modes        |              |                                 |

| 8.4.4          | Programming register#0               |              |                                 |

| 8.4.5          | Converter clock frequency values     |              |                                 |

| 8.5            | 10-bit VCM DAC                       |              |                                 |

| 8.6            | Reference voltage                    |              |                                 |

| 8.7            | Stand-alone op-amps                  |              |                                 |

| 8.8            | Analog switch                        |              |                                 |

| 8.9            | Charge pump voltage                  |              |                                 |

| 8.10           | Spindle driver                       |              |                                 |

| 8.11           | VCM driver                           |              |                                 |

| 8.12           | Park the VCM                         |              |                                 |

| 8.13           | Precharge the VCM                    |              |                                 |

| 8.14           | Brake the motor                      |              |                                 |

| 8.15           | Power-on reset                       |              |                                 |

| 8.16           | Thermal monitor and shutdown         |              |                                 |

| 8.17           | Power supply isolation               |              |                                 |

| 8.17.1         | External isolation diode             |              |                                 |

| 8.17.2         | External power FET                   |              |                                 |

| 8.18           | Thermal behaviour                    |              |                                 |

### Disk drive spindle and VCM with servo controller

OM5193H

#### 1 FEATURES

#### 1.1 Servo control

- 10-bit VCM Digital-to-Analog Converter (DAC)

- 7-channel 10-bit Analog-to-Digital Converter (ADC)

- Programmable spindle commutation control logic

- · 3-wire serial interface

- Two stand-alone operational amplifiers (op-amps) with outputs connected to the ADC

- Analog multiplexer with two inputs used to select VCM seek mode or track-following mode.

### 1.2 Motor control

#### 1.2.1 SPINDLE MOTOR DRIVER

- · 3-phase output motor driver

- 1.9 A maximum available start-up current

- Total  $R_{ds(on)} = 0.6 \Omega$  (typical) at 25 °C

- Back ElectroMotive Force (BEMF) processing for sensorless motor commutation

- · Linear current control

- External current sense resistor

- · External current control loop compensation

- · Adjustable slew rate control

- Short-circuit brake

- Adjustable brake-after-park delay time.

### 1.2.2 VOICE COIL MOTOR DRIVER

- 1.5 A maximum current capability

- Total  $R_{ds(on)} = 0.8 \Omega$  (typical) at 25 °C

- Linear class AB output with low cross-over distortion delay

- Precision current control loop with external current sense resistor

- Programmable seek and track-following mode with adjustable current loop gain

- External current control loop compensation

- · Precharge during brake mode

- 20 kHz current control loop bandwidth

- · Parking function

- · Adjustable park voltage with limiter.

#### 1.3 Miscellaneous items

- Precision low voltage 5 and 12 V power monitor with hysteresis

- Precision internal voltage reference for servo and power control circuits

- Thermal sense circuit with over-temperature shutdown sensor

- · Internal charge pump voltage generator

- Automatic brake-after-park at power-down, thermal shutdown or sleep mode

- Sleep mode: low power consumption mode.

#### 2 APPLICATIONS

12 V hard disk drive products.

### 3 GENERAL DESCRIPTION

#### 3.1 Overview

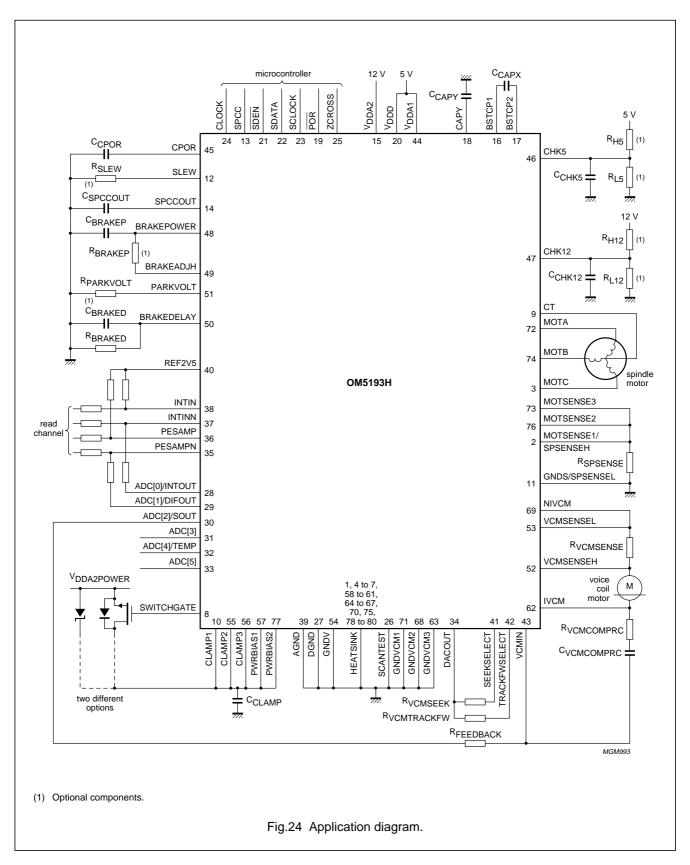

The OM5193H is a combination of a voice coil motor and a spindle motor driver with embedded servo controller designed for use in disk drives. Configuration and control registers are set via a 3-wire serial port running up to 30 MHz to interface commonly to a microcontroller or a digital signal processor.

The device operates at 5 and 12 V power supplies and integrates safety functions such as power stages overvoltage protection, power and temperature monitor, over-temperature shutdown and dynamic brake-after-park.

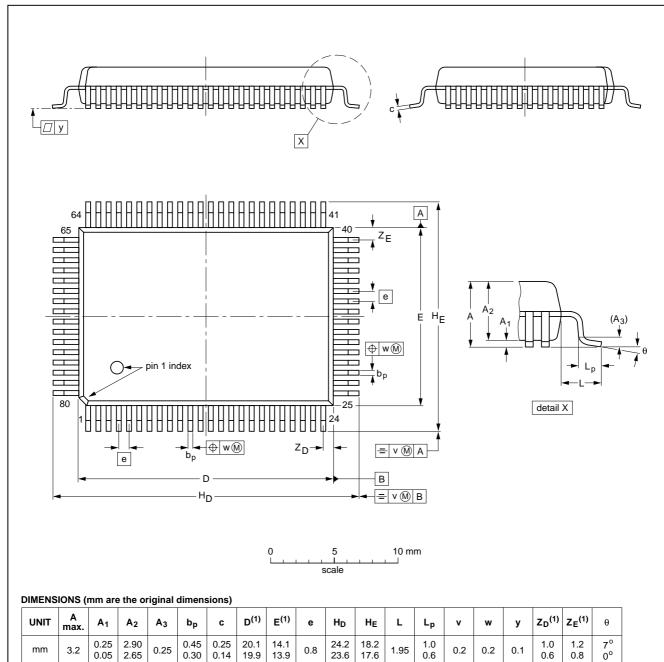

The device is contained in a QFP80 package with 18 pins connected to the leadframe thus providing low thermal resistance.

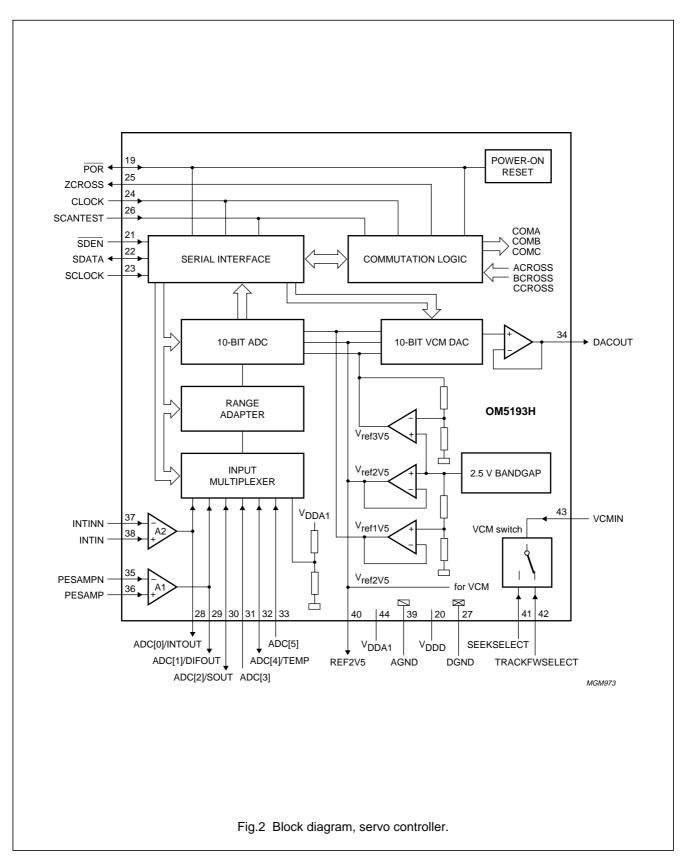

#### 3.2 Servo controller

The servo controller includes the following circuits:

- 3-wire serial interface

- Spindle commutation logic

- A 10-bit ADC with 7 inputs selected by an internal multiplexer

- A 10-bit VCM DAC with 1.5, 2.5 and 3.5 V voltage references

- Two low-offset stand-alone op-amps

- · Analog multiplexer with 2 inputs.

### Disk drive spindle and VCM with servo controller

OM5193H

The serial interface is used:

- To adjust the timing parameters for proper spindle commutation sequence

- To accurately adjust head positioning via the 10-bit VCM DAC

- To set VCM seek or track-following mode via the low-impedance switch

- To select and process analog signals via a 7-channel multiplexer connected to the 10-bit ADC.

The spindle commutation logic circuit ensures proper spindle start-up (no reverse rotation) and commutation sequence for the spindle driver by processing BEMF sensing circuit output signals.

The two stand-alone op-amps, with the inputs connected to the read channel IC, provide servo track signals processed by the microcontroller to perform accurate track-following mode.

### 3.3 Spindle and voice coil motor

The OM5193H drives a 3-phase brushless, sensorless DC spindle motor and a voice coil motor.

Spindle and voice coil motor power stages with low  $R_{ds(on)}$  and high current capability are suitable for mid-end and low-end 12 V disk drives. Power stages are designed in such a way that external Schottky diodes are not needed.

Spindle current is sensed by an external resistor and monitored by the external signal SPCC (SPindle Current Control). Spindle speed is regulated by the microcontroller via the ZCROSS signal (Zero CROSSing detection frequency output). BEMF comparators provide the digital zero crossing signals. These are processed by the commutation logic circuit to properly switch-on and switch-off spindle power drivers thus ensuring the rotation of the motor.

The control of the heads positioning is accomplished by the internal 10-bit VCM DAC. Seek and track-following VCM current loop gain is set by external resistors. VCM zero current is referenced to the 2.5 V internal voltage reference.

An internal precharge of the actuator (magnetic latch) during brake mode guarantees total control of the current when VCM starts running without current spikes.

### 3.4 Safety functions

The OM5193H is protected against transient voltage spikes that are generated by the inductive loads of spindle and VCM.

Power supplies and temperature are monitored in order to guarantee data reliability and self-protection of the device in case of power loss or temperatures beyond maximum rating.

Park and brake functions secure heads and disk media in case of power-down or high temperature failure. This function is also activated by the sleep mode.

An internal temperature monitor is available to monitor the chip temperature and thus prevents over-temperature shutdown. Internally connected to the ADC channel 4, it can be used by the microcontroller as an early 'temperature-too-high' warning during a long VCM seek sequence.

# Disk drive spindle and VCM with servo controller

OM5193H

### 4 QUICK REFERENCE DATA

| SYMBOL              | PARAMETER                  | МІІ  | I. TYP. | MAX. | UNIT |  |  |  |  |  |

|---------------------|----------------------------|------|---------|------|------|--|--|--|--|--|

| Supply voltage      |                            |      |         |      |      |  |  |  |  |  |

| V <sub>DDA1</sub>   | 5 V analog supply voltage  | 4.5  | 5.0     | 5.5  | V    |  |  |  |  |  |

| $V_{DDD}$           | 5 V digital supply voltage | 4.5  | 5.0     | 5.5  | V    |  |  |  |  |  |

| V <sub>DDA2</sub>   | 12 V analog supply voltage | 10.8 | 12.0    | 13.2 | V    |  |  |  |  |  |

| Drivers             | Drivers                    |      |         |      |      |  |  |  |  |  |

| I <sub>SPOUT</sub>  | spindle start-up current   | _    | _       | 1.9  | А    |  |  |  |  |  |

| I <sub>VCMRUN</sub> | VCM current                | _    | _       | 1.5  | А    |  |  |  |  |  |

### 5 ORDERING INFORMATION

| TYPE    |       | PACKAGE                                                                                      |          |  |  |  |  |

|---------|-------|----------------------------------------------------------------------------------------------|----------|--|--|--|--|

| NUMBER  | NAME  | DESCRIPTION                                                                                  | VERSION  |  |  |  |  |

| OM5193H | QFP80 | plastic quad flat package; 80 leads (lead length 1.95 mm); body $14 \times 20 \times 2.8$ mm | SOT318-2 |  |  |  |  |

### Disk drive spindle and VCM with servo controller

OM5193H

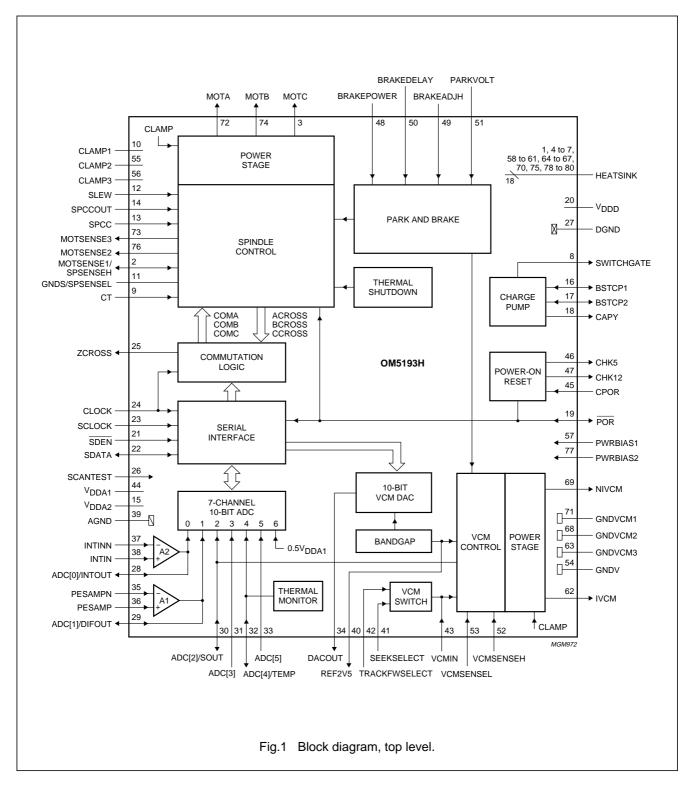

### **6 BLOCK DIAGRAMS**

Figures 1, 2, 3 and 4 provide block diagrams of the OM5193H servo and motor control (top level diagram, servo controller, spindle motor driver and voice coil motor driver).

# Disk drive spindle and VCM with servo controller

OM5193H

# Disk drive spindle and VCM with servo controller

OM5193H

9

Philips Semiconductors

Product specification

Fig.4 Block diagram, voice coil motor driver.

# Disk drive spindle and VCM with servo controller

OM5193H

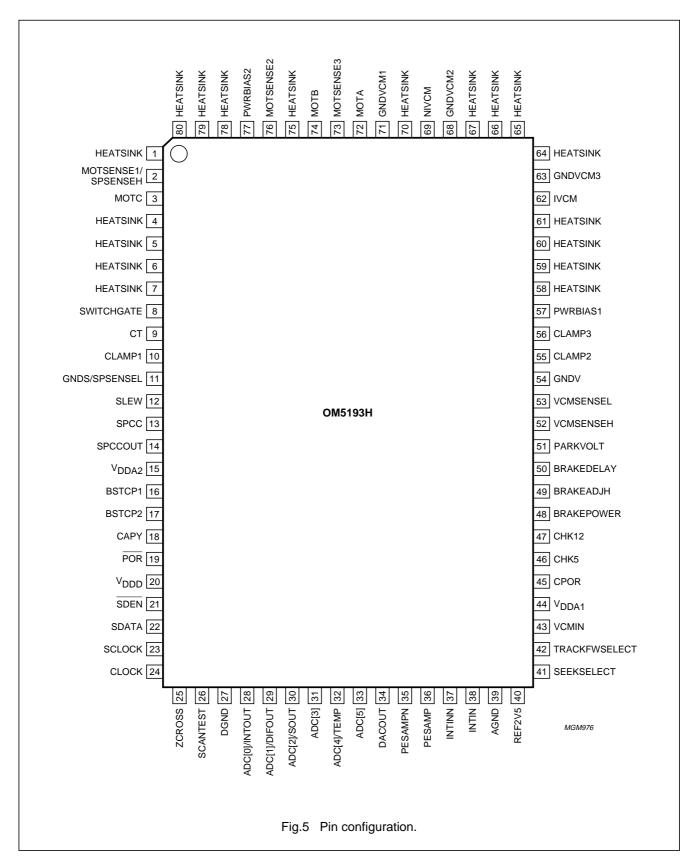

### 7 PINNING

| SYMBOL             | PIN | I/O            | DESCRIPTION                                               |

|--------------------|-----|----------------|-----------------------------------------------------------|

| HEATSINK           | 1   | _              | dissipation pin; internally connected to the leadframe    |

| MOTSENSE1/SPSENSEH | 2   | analog I/O     | sense line of the spindle/spindle sense amplifier input   |

| MOTC               | 3   | analog output  | spindle motor power output                                |

| HEATSINK           | 4   | _              | dissipation pin; internally connected to the leadframe    |

| HEATSINK           | 5   | _              | dissipation pin; internally connected to the leadframe    |

| HEATSINK           | 6   | _              | dissipation pin; internally connected to the leadframe    |

| HEATSINK           | 7   | _              | dissipation pin; internally connected to the leadframe    |

| SWITCHGATE         | 8   | analog output  | isolation FET driver                                      |

| СТ                 | 9   | analog input   | centre tap of the spindle                                 |

| CLAMP1             | 10  | supply         | power stage supply voltage                                |

| GNDS/SPSENSEL      | 11  | ground         | spindle ground connection/spindle sense amplifier ground  |

| SLEW               | 12  | analog input   | spindle motor slope control                               |

| SPCC               | 13  | analog input   | spindle current control                                   |

| SPCCOUT            | 14  | analog input   | compensation point of the spindle current control loop    |

| V <sub>DDA2</sub>  | 15  | supply         | 12 V analog supply voltage                                |

| BSTCP1             | 16  | analog I/O     | booster capacitor 1                                       |

| BSTCP2             | 17  | analog I/O     | booster capacitor 2                                       |

| CAPY               | 18  | analog output  | DC-to-DC converter output (19 V)                          |

| POR                | 19  | digital I/O    | power-on reset signal; active LOW                         |

| $V_{DDD}$          | 20  | supply         | 5 V digital supply voltage                                |

| SDEN               | 21  | digital input  | serial interface data enable; active LOW                  |

| SDATA              | 22  | digital I/O    | serial interface data line                                |

| SCLOCK             | 23  | digital input  | serial interface clock line                               |

| CLOCK              | 24  | digital input  | clock input                                               |

| ZCROSS             | 25  | digital output | zero crossing detection signal                            |

| SCANTEST           | 26  | digital input  | scantest mode control; at LOW-level in normal conditions  |

| DGND               | 27  | ground         | servo digital ground                                      |

| ADC[0]/INTOUT      | 28  | analog I/O     | ADC channel 0 input/output of the A2 amplifier            |

| ADC[1]/DIFOUT      | 29  | analog I/O     | ADC channel 1 input/output of the A1 amplifier            |

| ADC[2]/SOUT        | 30  | analog I/O     | ADC channel 2 input/VCM sense amplifier output            |

| ADC[3]             | 31  | analog input   | ADC channel 3 input                                       |

| ADC[4]/TEMP        | 32  | analog I/O     | ADC channel 4 input/temperature monitor, thermal shutdown |

| ADC[5]             | 33  | analog input   | ADC channel 5 input                                       |

| DACOUT             | 34  | analog output  | 10-bit VCM DAC output                                     |

| PESAMPN            | 35  | analog input   | inverting input of the A1 amplifier.                      |

| PESAMP             | 36  | analog input   | non-inverting input of the A1 amplifier                   |

| INTINN             | 37  | analog input   | inverting input of the A2 amplifier                       |

| INTIN              | 38  | analog input   | non-inverting input of the A2 amplifier                   |

| AGND               | 39  | ground         | servo analog ground                                       |

| REF2V5             | 40  | analog output  | 2.5 V bandgap reference voltage                           |

# Disk drive spindle and VCM with servo controller

OM5193H

| SYMBOL            | PIN | I/O           | DESCRIPTION                                                    |

|-------------------|-----|---------------|----------------------------------------------------------------|

| SEEKSELECT        | 41  | analog input  | input for the seek mode                                        |

| TRACKFWSELECT     | 42  | analog input  | input for the track-following mode                             |

| VCMIN             | 43  | analog input  | VCM control input                                              |

| V <sub>DDA1</sub> | 44  | supply        | 5 V analog supply voltage                                      |

| CPOR              | 45  | analog input  | set the POR delay time                                         |

| CHK5              | 46  | analog output | set the V <sub>DDA1</sub> POR threshold                        |

| CHK12             | 47  | analog output | set the V <sub>DDA2</sub> POR threshold                        |

| BRAKEPOWER        | 48  | analog input  | brake power capacitor                                          |

| BRAKEADJH         | 49  | analog input  | adjust current consumption during park mode                    |

| BRAKEDELAY        | 50  | analog input  | set the brake-after-park delay time                            |

| PARKVOLT          | 51  | analog input  | set the park voltage                                           |

| VCMSENSEH         | 52  | analog input  | positive input of the VCM sense amplifier                      |

| VCMSENSEL         | 53  | analog input  | negative input of the VCM sense amplifier                      |

| GNDV              | 54  | ground        | VCM ground connection                                          |

| CLAMP2            | 55  | supply        | power stage supply voltage                                     |

| CLAMP3            | 56  | supply        | power stage supply voltage                                     |

| PWRBIAS1          | 57  | analog input  | power stages isolation bias; externally connected to the clamp |

| HEATSINK          | 58  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 59  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 60  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 61  | _             | dissipation pin; internally connected to the leadframe         |

| IVCM              | 62  | analog output | inverted output of the VCM (master stage)                      |

| GNDVCM3           | 63  | ground        | VCM power stage ground                                         |

| HEATSINK          | 64  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 65  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 66  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 67  | _             | dissipation pin; internally connected to the leadframe         |

| GNDVCM2           | 68  | ground        | VCM power stage ground                                         |

| NIVCM             | 69  | analog output | non-inverted VCM output (slave stage)                          |

| HEATSINK          | 70  | _             | dissipation pin; internally connected to the leadframe         |

| GNDVCM1           | 71  | ground        | VCM power stage ground                                         |

| MOTA              | 72  | analog output | spindle motor power output                                     |

| MOTSENSE3         | 73  | analog output | sense line of the spindle                                      |

| МОТВ              | 74  | analog output | spindle motor power output                                     |

| HEATSINK          | 75  | _             | dissipation pin; internally connected to the leadframe         |

| MOTSENSE2         | 76  | analog output | sense line of the spindle                                      |

| PWRBIAS2          | 77  | analog input  | power stages isolation bias; externally connected to the clamp |

| HEATSINK          | 78  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 79  | _             | dissipation pin; internally connected to the leadframe         |

| HEATSINK          | 80  | _             | dissipation pin; internally connected to the leadframe         |

### Disk drive spindle and VCM with servo controller

OM5193H

1998 Nov 02

### Disk drive spindle and VCM with servo controller

OM5193H

#### 8 FUNCTIONAL DESCRIPTION

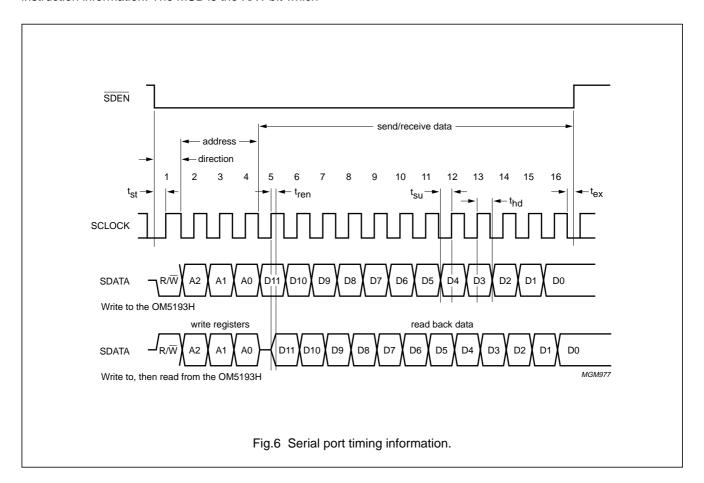

#### 8.1 Serial interface

The serial interface is a 3-wire bidirectional port for writing and reading data to and from the internal registers of the OM5193H. Each read or write will be composed of 16 bits. For data transfer \$\overline{SDEN}\$ is brought LOW, serial data is presented at the SDATA pin, and a serial clock is applied to the SCLOCK pin. After the \$\overline{SDEN}\$ pin goes LOW, the first 16 pulses applied to the SCLOCK pin shift the data presented at the SDATA pin into an internal shift register on the rising edge of each clock pulse. An internal counter prevents more than 16 bits from being shifted into the register. The data in the shift register is latched when \$\overline{SDEN}\$ goes HIGH. If less than 16 clock pulses are provided before \$\overline{SDEN}\$ goes HIGH, the data transfer is aborted.

All transfers are shifted into the serial port with the MSB first. The first 4 bits of the transfer contain address and instruction information. The MSB is the  $R/\overline{W}$  bit which

determines if the transfer is a read (logic 1) or a write (logic 0).

The remaining 3 bits determine the internal register to be accessed. The other 12 bits contain the programming data. In the read mode ( $R/\overline{W}=1$ ), the OM5193H outputs the register contents of the selected address. In the write mode ( $R/\overline{W}=0$ ), the OM5193H loads the selected register with the data presented on the SDATA pin. During sleep mode, the serial port remains active and register programmed data is retained.

SCLOCK is driven by the microcontroller. When the microcontroller drives the SDATA line, the data is valid on the rising edge of SCLOCK. When the OM5193H is driving the SDATA line (in read mode after the R/W bit and 3 bits) the data is valid on the falling edge of SCLOCK.

SDEN marks the end of the serial transfer. When the SDEN pin goes HIGH, the shift register data is latched into the addressed register of the OM5193H.

1998 Nov 02

# Disk drive spindle and VCM with servo controller

OM5193H

Table 1

Timing information for the serial interface

| SYMBOL           | PARAMETER                                           | MIN.                | MAX. | UNIT         |

|------------------|-----------------------------------------------------|---------------------|------|--------------|

| f <sub>clk</sub> | clock frequency                                     | _                   | 30   | MHz          |

| t <sub>st</sub>  | chip select to first active clock edge              | ¹/₂T <sub>clk</sub> | _    | ns           |

| t <sub>su</sub>  | data to clock set-up time                           | 12                  | _    | ns           |

| t <sub>hd</sub>  | clock to data hold time                             | 12                  | _    | ns           |

| t <sub>rd</sub>  | time data line is driven after 5th negative clock   | _                   | 5    | ns           |

| t <sub>ren</sub> | time from positive clock for data line to be driven | 0                   | _    | ns           |

| t <sub>rhd</sub> | receive data hold time                              | 0                   | _    | ns           |

| t <sub>rsu</sub> | receive data set-up time                            | 12                  | _    | ns           |

| t <sub>exW</sub> | last active clock to chip select; inactive on write | 0                   | _    | ns           |

| t <sub>exR</sub> | last active clock to chip select; inactive on read  | 10                  | _    | ns           |

| T <sub>bpa</sub> | time between successive serial port accesses        | 5                   | _    | clock cycles |

Table 2 Writeable registers of the serial interface

| REG |                       | BITS        |                   |                    |                         |                 |                        |            |              |                 |            |            |  |

|-----|-----------------------|-------------|-------------------|--------------------|-------------------------|-----------------|------------------------|------------|--------------|-----------------|------------|------------|--|

| KEG | 11                    | 10          | 9                 | 8                  | 7                       | 6               | 5                      | 4          | 3            | 2               | 1          | 0          |  |

| 0   |                       |             | opamp<br>Select_N | increm.<br>Channel | auto<br>Conv.<br>select | range<br>Select | test<br>Mode_N         | not used   |              | ADC MUX address |            |            |  |

| 1   | reverse<br>break      | not<br>used | seek/<br>trackfw  | not u              | sed                     | sleep_N         | n N   spindiv   manual |            | run/<br>stop | comC            | comB       | comA       |  |

| 2   | not used              |             | DAC<br>(9)        | DAC<br>(8)         | DAC<br>(7)              | DAC<br>(6)      | DAC<br>(5)             | DAC<br>(4) | DAC<br>(3)   | DAC<br>(2)      | DAC<br>(1) | DAC<br>(0) |  |

| 3   |                       |             | •                 |                    |                         | not used        |                        |            |              | •               | •          |            |  |

| 4   |                       |             |                   |                    |                         | not used        |                        |            |              |                 |            |            |  |

| 5   | Watchdog              |             |                   |                    |                         |                 | Blank 1                |            |              |                 |            |            |  |

| 6   | high Clock_N Comdelim |             |                   |                    |                         |                 |                        |            |              |                 |            |            |  |

| 7   |                       |             | Start             | -up                |                         |                 |                        |            | Blank        | : 2             |            |            |  |

Table 3

Readable registers of the serial interface

| DEC | BITS |            |            |            |            |            |            |            |            |            |            |            |

|-----|------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|

| REG | 11   | 10         | 9          | 8          | 7          | 6          | 5          | 4          | 3          | 2          | 1          | 0          |

| 0   |      | ADC status | ADC<br>(9) | ADC<br>(8) | ADC<br>(7) | ADC<br>(6) | ADC<br>(5) | ADC<br>(4) | ADC<br>(3) | ADC<br>(2) | ADC<br>(1) | ADC<br>(0) |

| 1   |      |            |            |            |            |            |            |            |            | Ccross     | Bcross     | Across     |

### Disk drive spindle and VCM with servo controller

OM5193H

Table 4 Address of registers

| R/W | A2 | A1 | A0 | REG. | DESCRIPTION                                                      |

|-----|----|----|----|------|------------------------------------------------------------------|

| 0   | 0  | 0  | 0  | 0    | ADC channel and programmable options                             |

| 1   | 0  | 0  | 0  | 0    | ADC status and value                                             |

| 0   | 0  | 0  | 1  | 1    | commutation, sleep, and VCM switch controls                      |

| 1   | 0  | 0  | 1  | 1    | commutation state in manual mode                                 |

| 0   | 0  | 1  | 0  | 2    | 10-bit DAC                                                       |

| 0   | 0  | 1  | 1  | 3    | not used                                                         |

| 0   | 1  | 0  | 0  | 4    | not used                                                         |

| 0   | 1  | 0  | 1  | 5    | Blank 1 and Watchdog delays                                      |

| 0   | 1  | 1  | 0  | 6    | commutation delay limit (11 bits), internal clock divider factor |

| 0   | 1  | 1  | 1  | 7    | Start-up and Blank 2 delays                                      |

### 8.2 Commutation and sleep mode

Spindle control and sleep mode are controlled by writing or reading on register#1.

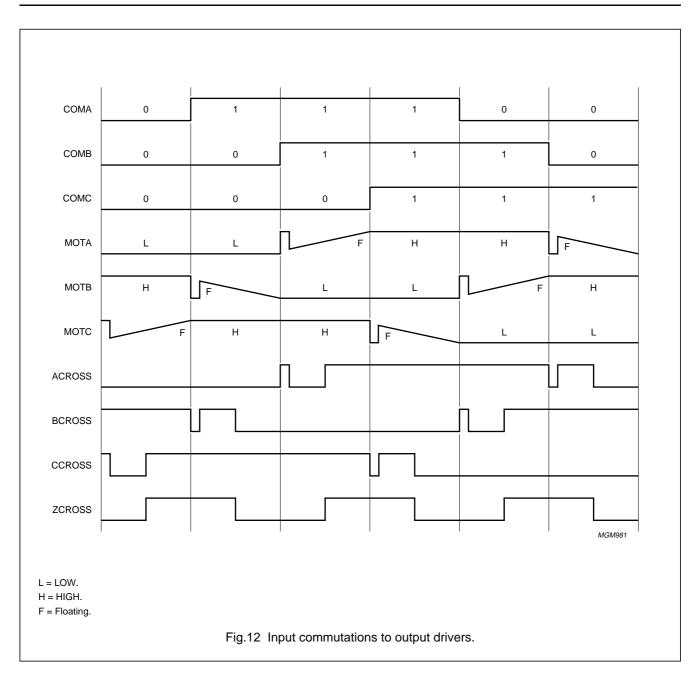

- Register#1 (0, 1 and 2) control the spindle commutations in manual mode when run/stop, manual and sleep bits are correctly set. The commutation sequence is described in Section "Spindle driver" (see also Table 16 and Fig.12).

- Register#1 (3) is the run/stop bit. After the power is turned on and POR is HIGH, the motor will not start spinning until register#1 (3) has been set to logic 1.

The motor stops spinning when this bit is set to logic 0.

- Register#1 (4) is the manual commutation mode bit.

When this bit is set to logic 1 and register#1 (3) set to logic 1, the commutation logic in the OM5193H will be disabled so that the spindle will not automatically go to the next commutation.

When register#1 (3 and 4) are set to logic 1, the microcontroller is expected to generate the different commutation states for the motor. The OM5193H will still provide the coil status which will be available by reading register#1. The different waveforms are shown in Section "Spindle driver" (see also Fig.12). Note that depending on the coil status acquisition moment, transient states (due to the flyback pulses) can be read.

When register#1 (4) is set to logic 0, the manual mode is disabled and the OM5193H will automatically commutate the motor each time a zero crossing is detected. The time between the zero crossing and the next commutation is half the time between the two preceding zero crossings. This is explained in the detailed description in Section "Commutation control".

- Register#1 (5) is the spindiv bit. This bit together with register#6 (11) enables the selection of a divider factor for both converter clock and spindle clock. Clock configurations are described in Section "Commutation control" (see also Table 6).

- Register#1 (6) is the sleep mode bit. When it is set to logic 0, the OM5193H will enter the low power mode. Then the commutation control generates (101) output codes on commutation signals to set spindle and VCM head into sleep mode. This causes the OM5193H to go into the brake-after-park mode. The only operating circuits are the power monitor, the voltage reference generator, the VCM precharge circuit and the serial interface. The OM5193H is in sleep mode when POR is LOW.

When the power is first turned on, the  $\overline{POR}$  signal goes HIGH after the POR delay. The OM5193H is then automatically set in sleep mode and thus in low power consumption mode. The VCM DAC output is in high-impedance mode, the spindle is in the brake mode and the VCM is in the precharge mode. Only after  $\overline{POR}$  is HIGH and register#1 (6) is set to logic 1, OM5193H is ready to be functional. When register#1 (6) goes HIGH, the VCM DAC outputs the 2.5 V reference voltage.

Register#1 (11) is dedicated to brake the spindle motor without going in 'brake-after-park' mode.

The commutation sequence is shifted in order to efficiently brake the motor. This brake, called reverse brake, is activated when register#1 (11) bit is set to logic 1. Note that there is no action on the VCM input signal when the reverse brake is used. When this bit is set to logic 0, the spindle motor starts again with normal spindle commutations.

1998 Nov 02

### Disk drive spindle and VCM with servo controller

OM5193H

Reading register#1 will read the state of the 3 coils coming from the spindle control block (ACROSS, BCROSS and CCROSS). The 3 input lines will be in bits 0, 1, and 2. The different waveforms are shown in Section "Spindle

driver" (see also Fig.12). Note that depending on the coil status acquisition moment, transient states (due to the flyback pulses) can be read.

Table 5 Writing register#1

| BIT | DEFAULT<br>VALUE | NAME          | DESCRIPTION                                                                                    |  |  |  |

|-----|------------------|---------------|------------------------------------------------------------------------------------------------|--|--|--|

| 0   | 0                | comA          | drives COMA when in manual commutation                                                         |  |  |  |

| 1   | 0                | comB          | drives COMB when in manual commutation                                                         |  |  |  |

| 2   | 0                | comC          | drives COMC when in manual commutation                                                         |  |  |  |

| 3   | 0                | run/stop      | 0 = motor to brake-after-park mode                                                             |  |  |  |

|     |                  |               | 1 = motor spinning; VCM active                                                                 |  |  |  |

| 4   | 0                | manual        | 0 = automatic commutation mode with run/stop = 1                                               |  |  |  |

|     |                  |               | 1 = manual commutation mode with run/stop = 1                                                  |  |  |  |

| 5   | 0                | spindiv       | 0 = the internal spindle clock frequency is controlled by register#6 (11) (bit highClock_N)    |  |  |  |

|     |                  |               | 1 = an additional divider by 4 is added on the internal spindle clock                          |  |  |  |

| 6   | 0                | sleep_N       | 0 = sleep mode: low power mode, serial interface active, power stages in brake-after-park mode |  |  |  |

|     |                  |               | 1 = fully functional mode: sleep_N has higher priority than run/stop if both are active        |  |  |  |

| 7   | 0                | _             | not used                                                                                       |  |  |  |

| 8   | 0                | _             | not used                                                                                       |  |  |  |

| 9   | 1                | seek/trackfw  | 0 = VCMIN connected to SEEKSELECT                                                              |  |  |  |

|     |                  |               | 1 = VCMIN connected to TRACKFWSELECT                                                           |  |  |  |

| 10  | 1                | _             | not used                                                                                       |  |  |  |

| 11  | 0                | reverse break | 1 = active brake control                                                                       |  |  |  |

|     |                  |               | 0 = normal commutations as defined by bits above                                               |  |  |  |

### 8.3 Commutation control

The commutation logic block generates the six different states to rotate the spindle motor. The spindle driver block provides the BEMF zero crossing information.

The commutation block interprets the zero crossing information and determines the commutation delay time and the next coil state. The commutation block must take into account the following situations:

- Start-up

- No start

- · Reverse rotating

- Run

- · Manual commutation.

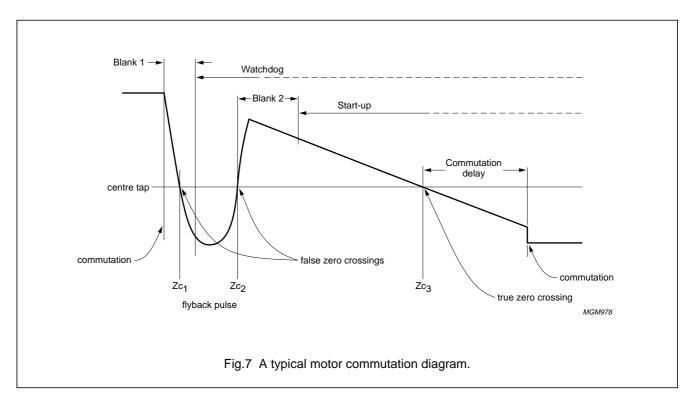

The commutation logic keeps the motor spinning by commutating the motor after each detected zero crossing. It measures the time between two successive BEMF zero crossings and then determines the next commutation. The delay (commutation delay) between a zero crossing and the next commutation is half the time between the two preceding zero crossings. The commutation delay (Comdelim) can be limited to guarantee a faster lock after the motor has gone out of lock. A maximum commutation delay can be set via the serial port. The time is a function of both the external clock frequency, the individual register prescalers and the time programmed into the registers. Figure 7 shows a typical motor commutation timing diagram.

### Disk drive spindle and VCM with servo controller

OM5193H

#### • Blank 1

After a commutation occurs, the leading edge of the flyback pulse has a zero crossing (Zc<sub>1</sub>). Blank 1 timer is used to ignore this zero crossing by masking it while the timer initialized at Blank 1 value is counting. The state associated to Blank 1 down-counter will end when the counter reaches the zero value.

#### Blank 2

The Blank 2 timer starts counting as soon as the second zero crossing occurs ( $Zc_2$ ). After the second flyback pulse zero crossing, all extra zero crossings are ignored during the Blank 2 time. This allows the ringing of the coil voltage without causing a commutation advance. The state associated to Blank 2 down-counter will end when the counter reaches the zero value.

#### Watchdog

The Watchdog timer makes sure the motor is running in forward direction. If the motor is rotating in reverse direction, the BEMF voltage is inverted and the second crossing of the flyback pulse (Zc<sub>2</sub>) will not occur until the true BEMF zero crossing is detected. Therefore, if the Watchdog timer expires before a zero crossing occurs, the motor is assumed to be rotating backwards. The commutation is advanced by one step to correct this condition. The Watchdog time must be set to a value that is greater than the flyback pulse duration, measured when the spindle motor stands still.

The state associated to the Watchdog timer will start when the one associated to Blank 1 timer is finished and will end when  $Zc_2$  occurs or when the Watchdog counter expires.

### Start-up

If the motor is not spinning, the BEMF zero crossings will not occur. The Start-up timer detects this if it expires before the true zero crossing ( $Zc_3$ ) has occurred. It will advance the commutation by one step if this happens. The state associated to Start-up timer will start when the one associated to Blank 2 timer is finished and will end when  $Zc_3$  occurs or when Start-up expires.

#### Comdelim

The timer associated to Comdelim value allows to control the maximum commutation delay (between zero crossing and next commutation). When the true zero crossing is detected (Zc<sub>3</sub>), the timer will count until it expires and then will commutate the motor to the next step. This commutation delay time is equal to half the measured value between 2 zero crossings. The Comdelim value should be set to the maximum allowable delay value. If  $\Delta Zc_{meas}$  is lower than the programmed Comdelim value, the next timer value will be  $\Delta Zc_{meas}$  divided by 2. If  $\Delta Zc_{meas}$  is higher than the programmed Comdelim value, the next timer value will

be the programmed Comdelim value divided by 2.

1998 Nov 02

### Disk drive spindle and VCM with servo controller

OM5193H

The clock used in the commutation logic block is obtained by dividing the master clock of the chip ( $f_{CLOCK}$ ) by a clock divider (Prescaler). This internal clock will be named internal Spindle Clock. Internal spindle clock configurations are described in Table 6.

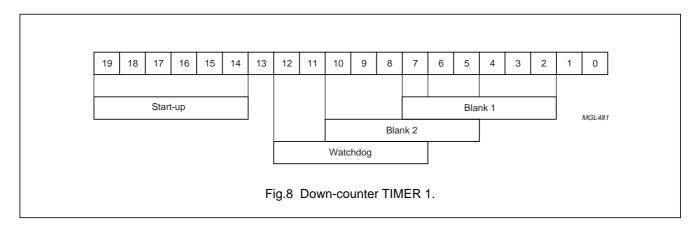

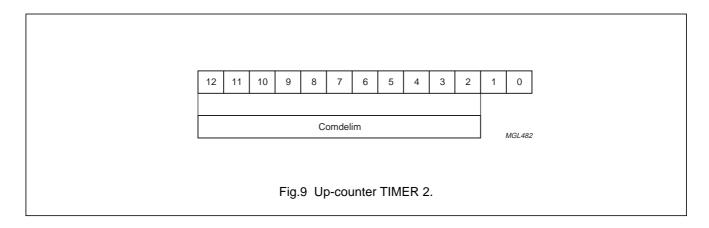

All the delays described above (Blank 1, Watchdog, Blank 2, Start-up and Comdelim) are generated by one down-counter (called TIMER 1), see Fig.8 and one up-counter (called TIMER 2), see Fig.9. Each of them uses internalSpindleClock signal.

Table 6 Spindle clock configurations

| spindiv<br>REGISTER#1 (5) | highClock_N<br>REGISTER#6 (11) | internalSpindleClock     |

|---------------------------|--------------------------------|--------------------------|

| 0                         | 0                              | ¹∕16 <sup>f</sup> CLOCK  |

| 0                         | 1                              | ¹⁄32 <sup>f</sup> CLOCK  |

| 1                         | 0                              | ¹/ <sub>64</sub> fclock  |

| 1                         | 1                              | ¹∕ <sub>128</sub> fclock |

### 8.3.1 BLANKS, WATCHDOG AND START-UP DELAYS

An internal down-counter called TIMER 1 is used to generate Blank 1, Blank 2, Watchdog and Start-up delays. It loads one of these programmed values and counts down till it reaches zero.

(1)

The actual delay time will be:

Value is the decimal representation of the binary code programmed in one of the 6 bit registers.

$$Step = \frac{2^{LSB}}{internalSpindleClock}$$

maxValue =

$$\frac{\left(2^{(MSB+1)} - 1\right) - \left(2^{LSB} - 1\right)}{\text{internalSpindleClock}}$$

$$= \frac{2^{(MSB+1)} - 2^{LSB}}{\text{internalSpindleClock}}$$

(3)

(2) We have to subtract  $(2^{LSB} - 1)$  to obtain maxValue because all the bits from 0 to (LSB - 1) are set internally to zero by design.

### Disk drive spindle and VCM with servo controller

OM5193H

Table 7 Delays used for TIMER 1

| DELAY    | LSB | MSB | BITS |

|----------|-----|-----|------|

| Blank 1  | 2   | 7   | 6    |

| Blank 2  | 5   | 10  | 6    |

| Watchdog | 7   | 12  | 6    |

| Start-up | 14  | 19  | 6    |

**Table 8** Numerical application with f<sub>CLOCK</sub> = 30 MHz

|                  | internalSpindleClock                |         |                                                 |         |                         |         |                                      |         |  |  |  |

|------------------|-------------------------------------|---------|-------------------------------------------------|---------|-------------------------|---------|--------------------------------------|---------|--|--|--|

| DELAYS           | <sup>1</sup> ⁄16 <sup>f</sup> сLоск |         | <sup>1</sup> / <sub>32</sub> f <sub>CLOCK</sub> |         | ¹∕ <sub>64</sub> fclock |         | <sup>1</sup> ∕ <sub>128</sub> fcLocκ |         |  |  |  |

|                  | STEP                                | MAX.    | STEP                                            | MAX.    | STEP                    | MAX.    | STEP                                 | MAX.    |  |  |  |

| Blank 1; note 1  | 2.13 μs                             | 134 μs  | 4.27 μs                                         | 269 μs  | 8.53 μs                 | 538 ms  | 17.1 μs                              | 1.08 ms |  |  |  |

| Blank 2; note 2  | 17.1 μs                             | 1.08 ms | 34.1 μs                                         | 2.15 ms | 68.3 μs                 | 4.30 ms | 137 μs                               | 8.60 ms |  |  |  |

| Watchdog; note 3 | 68.3 μs                             | 4.30 ms | 137 μs                                          | 8.60 ms | 273 μs                  | 17.2 ms | 546 μs                               | 34.4 ms |  |  |  |

| Start-up; note 4 | 8.74 ms                             | 550 ms  | 17.5 ms                                         | 1.101 s | 35 ms                   | 2.202 s | 70 ms                                | 4.404 s |  |  |  |

#### **Notes**

- 1. The first zero crossing of the flyback should occur within this time.

- 2. The real zero crossing should not come within this time after the second zero crossing of the flyback pulse.

- 3. The time should be larger than the duration of the flyback pulse measured when the motor stands still.

- 4. The actual zero crossing should occur within this time after the Blank 2 time has expired.

### 8.3.2 COMDELIM DELAY

An internal up-counter called TIMER 2 is used to measure the time between two zero crossings and also to set the maximum commutation delay through Comdelim delay.

### Disk drive spindle and VCM with servo controller

OM5193H

Comdelim is the maximum value that can be reached by TIMER 2. So, this is the maximum time between 2 zero crossings ( $\Delta Zc$ ). The maximum commutation delay (Comdelim delay) is then half this value.

The actual delay will be:

$$\Delta Zc = value \times step + Offset$$

(4)

$$ComdelimDelay = \frac{\Delta Zc}{2}$$

(5)

Value is the decimal representation of the binary code programmed in the 11-bit register.

$$Step = \frac{2^{LSB}}{internalSpindleClock}$$

(6)

$$Offset = \frac{3}{internalSpindleClock}$$

(7)

(we have to add this offset because bits 0 and 1 are set internally to logic 1 by design).

$$maximum\Delta Zc = \frac{2^{(MSB+1)} - 1}{internalSpindleClock}$$

(8)

$$maximumComdelimDelay = \frac{2^{(MSB)} - \frac{1}{2}}{internalSpindleClock}$$

(9)

Table 9 Delay used for TIMER 2

| DELAY    | LSB | MSB | BITS |

|----------|-----|-----|------|

| Comdelim | 2   | 12  | 11   |

**Table 10** Numerical application with f<sub>CLOCK</sub> = 30 MHz

|                |                                     | CLOCKOUT/PRESCALER |                         |              |                         |              |              |                                      |              |              |                |              |

|----------------|-------------------------------------|--------------------|-------------------------|--------------|-------------------------|--------------|--------------|--------------------------------------|--------------|--------------|----------------|--------------|

| DELAYS         | <sup>1</sup> ⁄16 <sup>f</sup> сLоск |                    | ¹⁄ <sub>32</sub> fcLock |              | ¹∕ <sub>64</sub> fcLock |              |              | <sup>1</sup> ⁄128 <sup>f</sup> сLоск |              |              |                |              |

|                | STEP<br>(μs)                        | OFFSET<br>(μs)     | MAX.<br>(ms)            | STEP<br>(μs) | OFFSET<br>(μs)          | MAX.<br>(ms) | STEP<br>(μs) | OFFSET<br>(μs)                       | MAX.<br>(ms) | STEP<br>(μs) | OFFSET<br>(μs) | MAX.<br>(ms) |

| ΔZc            | 2.13                                | 1.6                | 4.37                    | 4.27         | 3.2                     | 8.74         | 8.53         | 6.4                                  | 17.48        | 17.1         | 12.8           | 35           |

| Comdelim delay | 1.07                                | 0.8                | 2.18                    | 2.13         | 1.6                     | 4.37         | 4.27         | 3.2                                  | 8.74         | 8.53         | 6.4            | 17.48        |

The commutation delay counter, which starts counting at a zero crossing, has two operating modes:

- In the adaptive mode, the next zero crossing is detected before the commutation delay counter has reached its

programmed value. In this mode, the next commutation will occur at the measured t<sub>Zcross</sub> divided by 2 after the last

zero crossing.

- In the forced mode, the next zero crossing is detected after the commutation delay counter reaches its programmed value. In this mode, the counter is stopped and the commutation logic block waits until the next zero crossing occurs.

After it occurs, the next commutation will be forced at the programmed commutation delay divided by 2.

### Disk drive spindle and VCM with servo controller

OM5193H

### 8.4 10-bit ADC with 7 analog inputs

The ADC is a signed 10-bit converter which uses the successive approximation conversion technique. The overall accuracy is 2% absolute error not including contribution of the reference voltage and guaranteed monotonicity.

#### 8.4.1 INPUT CHANNELS

7 analog input channels can be sampled and converted:

- Channel 0: conversion of the op-amp A2 output

- · Channel 1: conversion of the op-amp A1 output

- Channel 2: conversion of the VCM sense amplifier output

- · Channel 3: conversion of an analog external signal

- Channel 4: conversion of the temperature monitor + temperature shutdown signal

- Channel 5: conversion of an analog external signal

- Channel 6: conversion of an internal signal, controlling analog supply voltage over two ranges.

Channels 0 and 1 can be used as external inputs by deactivating the 2 stand-alone op-amps A1 and A2 (op-amps are put in sleep mode), that means by putting register#0 (9) at logic 1.

The ADC does not include input filtering. If this is required in the application then it must be implemented externally.

#### 8.4.2 INPUT RANGES

Two analog input ranges are possible: either between 1.5 and 3.5 V or between 0 and 5 V. The input range is selected with register#0 (6):

- Register#0 (6) = 0: means input analog value between 1.5 and 3.5 V

- Register#0 (6) = 1: means input analog value between 0 and 5 V.

Table 11 Input analog voltage and corresponding output code

| BIT                | MIN. OUTPUT = 200H          | MIDDLE OUTPUT = 000H       | MAX. OUTPUT = 1FFH          |

|--------------------|-----------------------------|----------------------------|-----------------------------|

| register#0 (6) = 0 | minimum input value = 1.5 V | middle input value = 2.5 V | maximum input value = 3.5 V |

| register#0 (6) = 1 | minimum input value = 0 V   | middle input value = 2.5 V | maximum input value = 5 V   |

### 8.4.3 CONVERSION MODES

Three different conversion modes are possible depending on the states of register#0 (7) and register#0 (8):

Auto conversion and input channel auto incrementation mode.

This mode is obtained with register#0 (7) = 1 and register#0 (8) = 1. The conversion sequence works as follows: the first A/D conversion is started by writing to serial port register#0. The address of the channel is decoded from the three LSBs in register#0 [2 to 0]. Then the OM5193H selects the addressed analog channel, samples and holds the analog input and starts the analog to digital conversion. The conversion result is obtained by reading the serial port register#0. Register#0 (10) provides the status of the conversion: it is set to 0 as long as the conversion is running and indicates that the low 10 bits of register#0 are invalid. Register#0 (10) going HIGH means the conversion is complete and guarantees the validity of the data in register#0 [9 to 0].

• Auto conversion on the same channel.

This input channel automatic incrementation option can be deactivated by setting register#0 (8) to logic 0 with register#0 (7) at logic 1. So the behaviour of the ADC is the same as explained above, except that all the conversions are made on the channel specified by the last write access on register#0.

• Single conversion mode.

The automatic conversion mode can also be deactivated by setting register#0 (7) to logic 0. In this mode, a write access on register#0 will start a conversion on the specified channel and a read access will not launch any other conversion.

### Disk drive spindle and VCM with servo controller

OM5193H

### 8.4.4 PROGRAMMING REGISTER#0

### Table 12 Writing register#0

| BIT | DEFAULT VALUES | NAME                    | DESCRIPTION                                                                                                       |

|-----|----------------|-------------------------|-------------------------------------------------------------------------------------------------------------------|

| 0   |                | ADC MUX address; note 1 | ADC MUX address 0                                                                                                 |

| 1   |                |                         | ADC MUX address 1                                                                                                 |

| 2   |                |                         | ADC MUX address 2                                                                                                 |

| 3   |                | not used                |                                                                                                                   |

| 4   |                | not used                | should be at logic 0 under normal operating conditions                                                            |

| 5   | 0              | testMode_N              | dedicated for test purposes of the DAC in ADC or DAC mode; should be at logic 0 under normal operating conditions |

| 6   | 0              | rangeSelect             | selects the analog input range of the ADC:  0 = range 1.5 to 3.5 V  1 = range 0 to 5 V                            |

| 7   | 0              | autoConvSelect          | selects the automatic conversion option; see details in Table 13                                                  |

| 8   | 0              | incrementChannel        | selects the automatic channel increment option; see details in Table 13                                           |

| 9   | 0              | opampSelect_N           | selects the stand-alone op-amps:                                                                                  |

|     |                |                         | 0 = op-amps activated                                                                                             |

|     |                |                         | 1 = op-amps deactivated                                                                                           |

| 10  |                | not used                |                                                                                                                   |

| 11  |                | not used                |                                                                                                                   |

### Note

- 1. Possible addresses:

- a) ADC MUX address = 000: channel 0 selected;

- b) ADC MUX address = 001: channel 1 selected;

- c) ADC MUX address = 010: channel 2 selected;

- d) ADC MUX address = 011: channel 3 selected;

- e) ADC MUX address = 100: channel 4 selected;

- f) ADC MUX address = 101: channel 5 selected;

- g) ADC MUX address = 110: channel 6 selected;

- h) ADC MUX address = 111 is an illegal address. No analog input will be selected if a conversion is asked in this channel and the ADC will convert a random analog value.

For a correct initialization of the converter just after power up, when  $\overline{POR}$  is HIGH (before using the ADC or the DAC), the register#0 has to be programmed as follows: write 020H and then write 000H. A read of register#0 between the 2 write accesses is not necessary.

### Disk drive spindle and VCM with servo controller

OM5193H

Table 13 Truth table for bits 7 and 8 on register#0 in write mode; conversion mode options; note 1

| autoConvSelect<br>REGISTER#0 (7) | incrementChannel<br>REGISTER#0 (8) | DESCRIPTION                                                                                                                                |

|----------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                | 0                                  | Default state: no auto channel incrementation, no A/D conversion started automatically after each read of the result.                      |

| 1                                | 0                                  | Starts automatically an A/D conversion on the same channel (no channel incrementation) after each read of the result.                      |

| 1                                | 1                                  | Starts automatically an A/D conversion on the next channel (increment the channel by 1) after each read of the result.                     |

| 0                                | 1                                  | No auto channel incrementation, no A/D conversion started automatically after each read of the result (similar to the default state '00'). |

### Note

1. The autoConvSelect bit has priority over the incrementChannel bit.

### 8.4.5 CONVERTER CLOCK FREQUENCY VALUES

The ADC internal clock named converterClock can have two different frequency values by programming register#6 (11) (bit highClock\_N):

Register#6 (11) = 1: means converterClock = Master clock (f<sub>CLOCK</sub>) divided by 8 (clockDivider = 8)

Register#6 (11) = 0: means converterClock = Master clock (f<sub>CLOCK</sub>) divided by 4 (clockDivider = 4)

$$conversionTime = \frac{13 \times clockDivider}{f_{CLOCK}}$$

(10)

Table 14 Numerical application

|                 | MASTER CLO       | OCK = 10 MHz     | MASTER CLC       | OCK = 20 MHz     | MASTER CLOCK = 30 MHz |                  |  |

|-----------------|------------------|------------------|------------------|------------------|-----------------------|------------------|--|

| TIME            | DIVISION<br>BY 8 | DIVISION<br>BY 4 | DIVISION<br>BY 8 | DIVISION<br>BY 4 | DIVISION<br>BY 8      | DIVISION<br>BY 4 |  |

| Conversion time | 10.4 μs          | 5.2 μs           | 5.2 μs           | 2.6 μs           | 3.4 μs                | 1.7 μs           |  |

### 8.5 10-bit VCM DAC

The VCM DAC is a signed 10-bit digital-to-analog convertor. It will start the conversion when register#2 is written. The lowest 10 bits contain the value to be converted.

Table 15 Input code and corresponding output analog voltage

| INPUT CODE | OUTPUT VOLTAGE |

|------------|----------------|

| 200H       | 1.5 V          |

| 000H       | 2.5 V          |

| 1FFH       | 3.5 V          |

The overall accuracy is 2% absolute error not including the contribution of the reference voltage and guaranteed monotonicity.

### Disk drive spindle and VCM with servo controller

OM5193H

### 8.6 Reference voltage

$V_{\text{ref2V5}}$  is a 2.5 V bandgap reference used as the reference voltage for the VCM circuit. Stable voltages of 1.5 and 3.5 V are generated from the 2.5 V reference and used as reference voltages for the VCM DAC and for the ADC. The 1.5 and 3.5 V voltages are only available inside the IC and are not connected to external pins.

### 8.7 Stand-alone op-amps

This block is composed of two low-offset stand-alone op-amps (A1 and A2) with outputs connected to the ADC channels 0 and 1.

The stand-alone op-amps can be deactivated if they are not used in the application. When deactivated, they are put in sleep mode and outputs are in high-impedance. In that case, ADC channels 0 and 1 can be used as input signals. The op-amps are controlled by writing to the serial port on register#0 (9); bit opampSelect\_N:

Register#0 (9) = 0: means the op-amps are selected and put in normal mode

Register#0 (9) = 1: means the op-amps are not selected and put in sleep mode.

### 8.8 Analog switch

This block is composed of a 2 input analog multiplexer used to select the seek mode or the track-following mode.

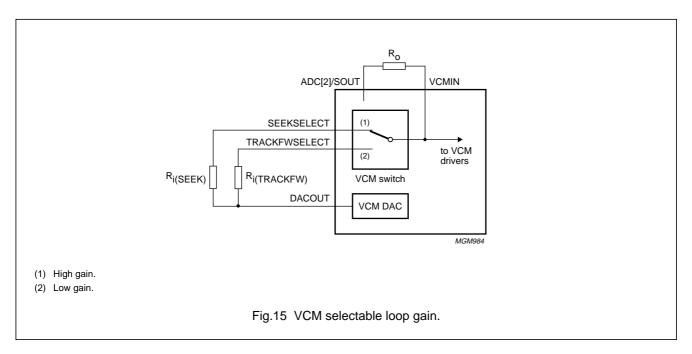

It is controlled by writing to serial port register#1 (9); bit seek/trackfw:

Register#1 (9) = 0: means input SEEKSELECT is selected and connected to VCMIN

Register#1 (9) = 1: means input TRACKFWSELECT is selected and connected to VCMIN.

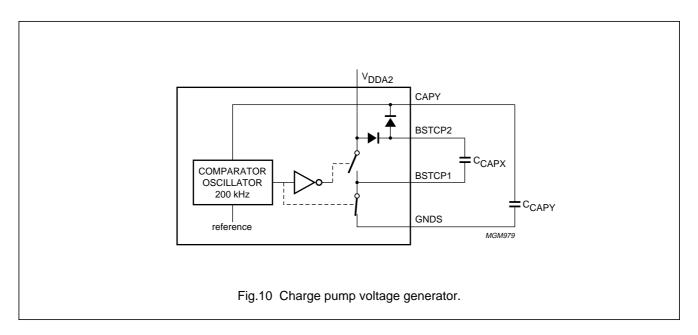

### 8.9 Charge pump voltage

The charge pump voltage circuit (voltage doubler) generates a power supply voltage higher than V<sub>DDA2</sub> (12 V) power supply. This voltage is used to:

- Drive the upper N-channel FETs of the power stages

- Drive an optional external FET (see Section 8.18)

- Set a voltage independent of the power supply and temperature for the functions BRAKEPOWER and BRAKEDELAY.

Two external capacitors are used to generate the higher voltage on pin CAPY. The capacitor between BSTCP1 and BSTCP2 is charged and discharged with a frequency, which is a function of the charge pump output current and an internal oscillator frequency. The voltage on pin CAPY is typically 19.2 V. Figure 10 illustrates the charge pump block diagram.

### Disk drive spindle and VCM with servo controller

OM5193H

### 8.10 Spindle driver

The spindle block contains both the low-side and high-side drivers configured as a H-bridge for a 3-phase DC brushless, sensorless motor. In each of the six possible states, two outputs are active, one sourcing current and one sinking current. The third output presents a high impedance to the motor which enables measurement of the BEMF in the corresponding motor coil. The BEMF zero crossing comparator outputs (xCROSS) are processed by the commutation logic circuit to calculate the correct moment for the next commutation, so the change to the next output state. The commutation logic circuit provides proper commutation commands for the spindle drivers thus ensuring the rotation of the motor. The commutation logic circuit also controls the spindle motor driver during start-up (no reverse rotation).

The spindle should be set in the high-impedance mode (see Table 16) between the sleep mode (brake-after-park mode) and the normal running mode. Register#1 should be programmed as follows:

- Write 00x001x11010 to activate the manual mode during typically less than 1 ms (time discharge of low-side power FETs)

- Write 00x001x01xxx to activate the automatic running mode. The 'x' states concern the seek or track-following mode register#1 (9) and the spindle prescaler value used on the application register#1 (5). Their states are specific to the application needs.

The ZCROSS signal is a combination of the xCROSS signals. It can be used by the microcontroller as a tacho information for the spindle speed control loop.

The external SPCC signal is used to control the spindle current. The external SPCCOUT capacitor is connected to the spindle current control amplifier to ensure the stability of the spindle current control loop.

The short-circuit brake mode is entered if power-down, thermal shutdown or sleep mode occurs.

A Miller network is used to obtain soft switching on the low-side and high-side drivers.

The slew rate of the driver stage that is switched-off can be controlled by means of a resistor connected to the pins SLEW and GND. The slew rate is calculated using the following equation:

$$SR = \frac{3 \mu A + \frac{2.55}{4 \times (1 k\Omega + R_{SLEW})}}{20 pF}$$

(11)

$R_{SLEW}$  is in  $\Omega$  and SR in V/s. Without a resistor, SR is typical 0.15 V/ $\mu$ s and with a resistor of 90 k $\Omega$ , the typical value is 0.5 V/ $\mu$ s. The maximum slew rate depends on the limit for stability of the spindle loop.

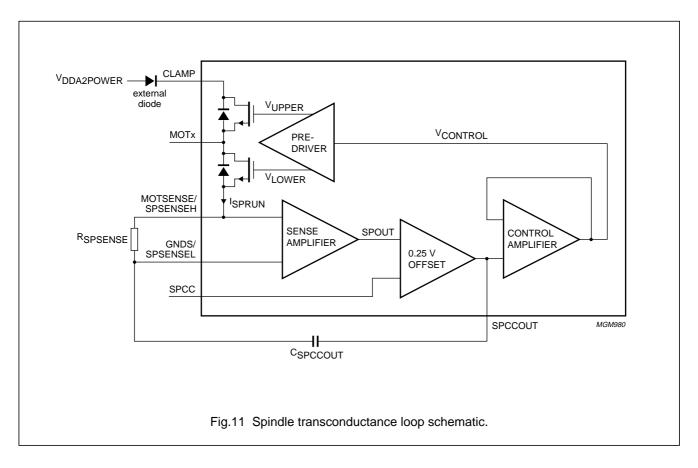

The spindle current  $I_{SPRUN}$  is sensed by an external resistor  $R_{SPSENSE}$  connected to a sense amplifier providing the internal signal SPOUT. The gain  $G_v$  of the sense amplifier is typical 10.

$$V_{SPOUT} = G_v \times R_{SPSENSE} \times I_{SPRUN}$$

(12)

=  $G_v \times V_{SPSENSEH}$

The transconductance gain of the spindle loop is given by the following equation:

$$g_{s} = \frac{I_{SPRUN}}{V_{SPOUT}} = \frac{1}{R_{SPSENSE}} \times \frac{V_{SPSENSEH}}{V_{SPOUT}}$$

$$= \frac{1}{R_{SPSENSE} \times G_{v}}$$

(13)

The control amplifier differentiates the control signal on pin SPCC from the signal SPOUT. A 0.25 V offset is subtracted from the input voltage on pin SPCC to ensure that the current command includes the zero current. With the spindle loop closed, the voltage SPOUT is given by the following equation:

$$V_{SPOUT} = V_{SPCC} - V_{OFFSET}$$

(14)

The control signal  $V_{CONTROL}$  provided by the control amplifier is then applied to the spindle drivers. The spindle drivers control the voltage on the gate of the low-side power drivers. One of the three high-side drivers is fully on. The charge pump voltage is applied to the gate. One of the three low-side drivers is controlled by the control amplifier. Purpose is to adjust the voltage on the gate to adjust the total output resistance  $R_{ds(on)}$  at the specified running current.

The current in the spindle loop is given by the following formula:

$$I_{SPRUN} = g_s \times (V_{SPCC} - V_{OFFSET})$$

(15)

With R<sub>SPSENSE</sub> =  $0.25 \Omega$ :  $I_{SPRUN} = 0.4 \times (V_{SPCC} - 0.25)$  (16)

The maximum start-up current is  $I_{SPRUN} = 1.9$  A with SPCC signal at 5 V.

Figure 11 illustrates the spindle current control loop.

# Disk drive spindle and VCM with servo controller

OM5193H

Table 16 and Fig.12 illustrate the relationship between the commutation signals and the associated output drivers and output comparators.

Table 16 Input commutations to output drivers

| COMA | СОМВ | СОМС | МОТА               | МОТВ               | мотс               | STATE                  |

|------|------|------|--------------------|--------------------|--------------------|------------------------|

| 0    | 0    | 0    | LOW                | HIGH               | float              | 1                      |

| 1    | 0    | 0    | LOW                | float              | HIGH               | 2                      |

| 1    | 1    | 0    | float              | LOW                | HIGH               | 3                      |

| 1    | 1    | 1    | HIGH               | LOW                | float              | 4                      |

| 0    | 1    | 1    | HIGH               | float              | LOW                | 5                      |

| 0    | 0    | 1    | float              | HIGH               | LOW                | 6                      |

| 1    | 0    | 1    | F_L <sup>(1)</sup> | F_L <sup>(1)</sup> | F_L <sup>(1)</sup> | SLEEP                  |

| 0    | 1    | 0    | float              | float              | float              | Spindle high-impedance |

### Note

1. F\_L is for float-and-then-LOW (brake-after-park mode).

### Disk drive spindle and VCM with servo controller

OM5193H

### 8.11 VCM driver

The VCM driver is a linear, class AB amplifier with both low-side and high-side drivers configured as an H-bridge.

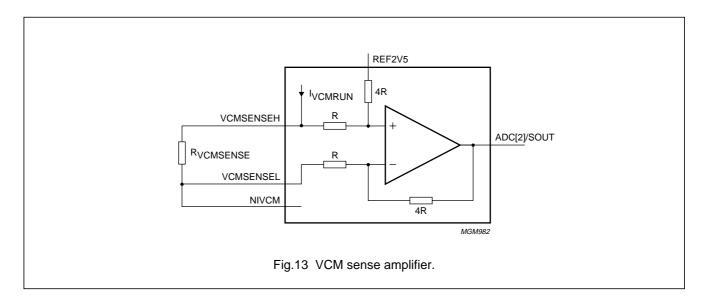

The zero-current reference voltage for the VCM loop is internally set at 2.5 V. The sense resistor  $R_{VCMSENSE}$  enables the VCM current ( $I_{VCMRUN}$ ) to be measured through the sense amplifier. The gain  $G_v$  of the sense amplifier is typically 4. The output voltage ( $V_{sout}$ ) on pin ADC[2]/SOUT is given by the following equation:

$$V_{\text{sout}} = G_{\text{v}} \times R_{\text{VCMSENSE}} \times I_{\text{VCMRUN}} + V_{\text{ref2V5}}$$

$$= G_{\text{v}} \times (V_{\text{VCMSENSEH}} - V_{\text{VCMSENSEL}}) + V_{\text{ref2V5}}$$

(17)

Figure 13 presents the VCM sense amplifier.

### Disk drive spindle and VCM with servo controller

OM5193H

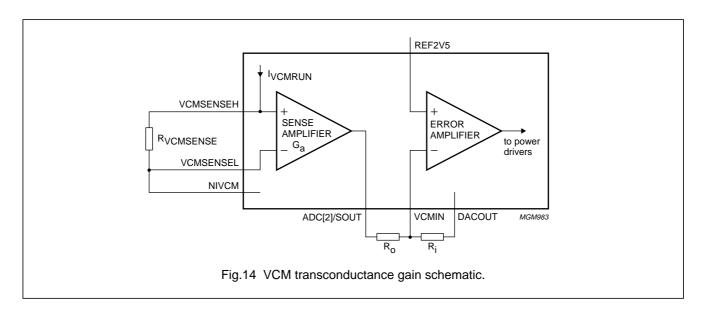

The error amplifier (see Fig.14) compares the DACOUT input command and the output signal  $V_{sout}$  of the sense amplifier to generate the control voltage of the power drivers.

$$\frac{V_{\text{ref2V5}} - V_{\text{DACOUT}}}{R_{i}} = \frac{V_{\text{sout}} - V_{\text{ref2V5}}}{R_{o}} = \frac{G_{v} \times R_{\text{VCMSENSE}} \times I_{\text{VCMRUN}}}{R_{o}}$$

(18)

Finally, the transconductance gain of the VCM loop is given by the following equation:

$$g_{v} = \frac{I_{VCMRUN}}{V_{ref2V5} - V_{DACOUT}} = \frac{R_{o}}{R_{i}} \times \frac{1}{G_{v} \times R_{VCMSENSE}}$$

(19)

### Disk drive spindle and VCM with servo controller

OM5193H

The VCM loop gain is set through external resistors. The seek (high gain) or the track-following (low gain) mode is controlled with the serial bus. Purpose is to set the appropriate gain by selecting the  $R_i$  resistor through the low impedance analog 2 input switch.

#### 8.12 Park the VCM

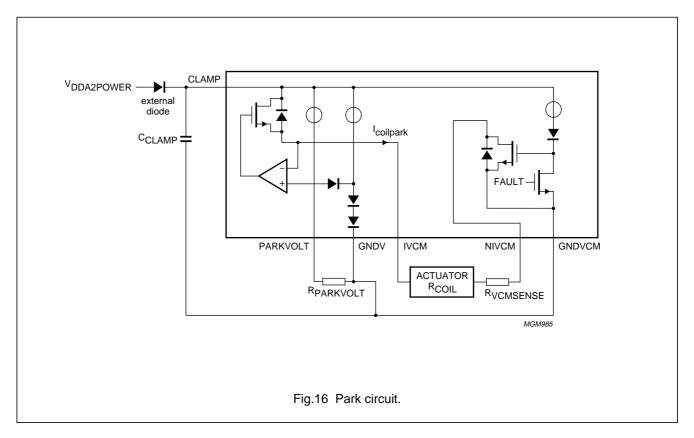

A VCM park sequence is initiated any time a power-down, a thermal shutdown and/or a sleep mode situation occurs. The fault signal (FAULT) initiates the VCM park sequence.

This secure function is accomplished even in case of power loss. In this case, the energy provided by the rectified BEMF of the spindle motor coils is used to supply the park circuit and park the heads above a landing area. Otherwise, the energy is provided by the V<sub>DDA2</sub> power supply through an external diode or power FET.

To accomplish this function, the spindle power stage is automatically set in a high-impedance mode. The NIVCM low-side power driver is fully on while the remaining power drivers of the VCM power stage are off.

The current flowing in the PARKVOLT resistor sets the voltage on the PARKVOLT pin. The voltage across the VCM load is internally regulated by the voltage on the PARKVOLT pin. An internal circuit clamps the voltage on PARKVOLT at  $3V_{BE}$ . Without resistor, the voltage on PARKVOLT is  $3V_{BE}$ . The park current  $I_{coilpark}$  is applied to the VCM coil. The  $I_{coilpark}$  park current is given by the following equation:

$$I_{coilpark} = \frac{V_{PARKVOLT}}{R_{VCMSENSE} + R_{coil} + R_{ds (on) (sink)}}$$

(20)

An RC network is connected to pin BRAKEDELAY. During the normal functioning, the voltage on the BRAKEDELAY pin is typically  $V_{BDC}$  = 12.55 V. This value is independent of the power supply and the temperature. During park mode, the RC network discharges with a time constant  $\tau$ .

The park mode is activated as long as the voltage on the BRAKEDELAY pin is greater than the internal brake delay threshold voltage  $V_{BDT}$  of typically 2.2 V.

The  $t_{BDT}$  park time duration (or brake delay time duration) is set by the following equation:

$$t_{BDT} = \tau \times In \left( \frac{V_{BDC}}{V_{BDT}} \right)$$

(21)

where

$$\tau = C_{BRAKED} \times R_{BRAKED} \tag{22}$$

$C_{BRAKED}$  and  $R_{BRAKED}$  are respectively the capacitor and the resistor connected to the BRAKEDELAY pin.

Typically, with C\_{BRAKED} = 330 nF and R\_{BRAKED} = 650 k $\Omega$ ,  $t_{BDT}$  = 400 ms.

Figure 16 shows the equivalent park circuit.

### Disk drive spindle and VCM with servo controller

OM5193H

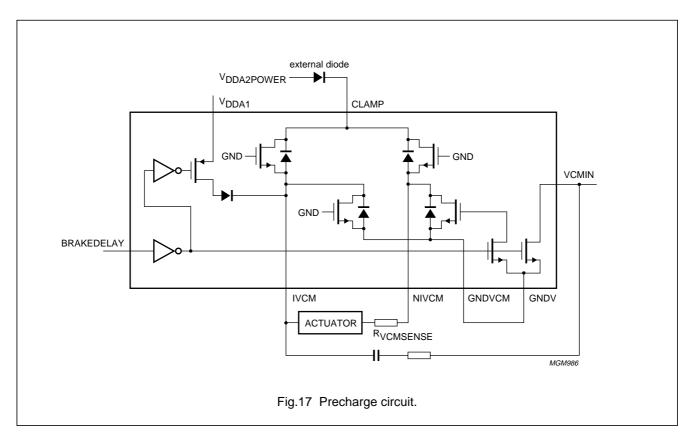

### 8.13 Precharge the VCM

When the voltage on the BRAKEDELAY pin goes below the brake delay threshold voltage  $V_{BDT},$  the BRAKEDELAY pin is short-circuited to ground. While the brake mode is activated, the VCM outputs are precharged to  $V_{DDA1} - V_{BE}$  while pin VCMIN is short-circuited to ground.

This function precharges the external RC compensation network.

The NIVCM low-side power driver is set off during VCM precharge. This is convenient for actuators with a magnetic latch.

The park circuit is powered off during VCM precharge with the actuator latched.

### Disk drive spindle and VCM with servo controller

OM5193H

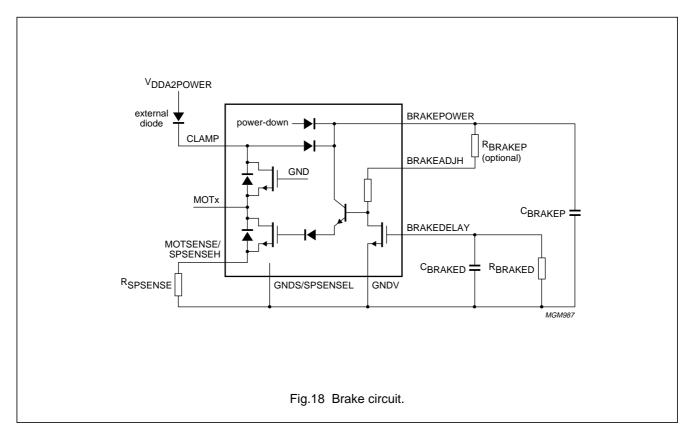

### 8.14 Brake the motor

A spindle brake sequence is initiated any time a power-down, a thermal shutdown and/or a sleep mode situation occurs. The fault signal activates the brake-after-park sequence.

When the heads are parked, the motor has to be braked in order to guarantee heads reliability. During the brake sequence, the heads land on a dedicated area of the disk.

The OM5193H integrates a highly efficient, low cost brake circuit. It is guaranteed to be functional in case of power loss and thermal shutdown with a short time brake duration thus minimizing friction of the heads on the landing zone.

The energy stored by an external capacitor connected to the BRAKEPOWER pin supplies the brake circuit during the brake-after-park sequence.

The brake of the motor is accomplished by turning on the spindle low-side power components while high-side power drivers are off. This causes a short-circuit of the spindle motor coils and thus reversing the current and torque of the motor.

During normal operation, the voltage  $V_{BDC}$  on the BRAKEPOWER pin is typically  $V_{BDC} = 12.55 \text{ V}$ . This value is independent of the power supply and the temperature. During the park sequence, the discharge of the BRAKEPOWER capacitor is set by an internal resistor, with or without an optional external resistor between BRAKEPOWER and BRAKEADJUST. The typical value of the internal resistor is 4 M $\Omega$ .

The brake sequence is started when the voltage on BRAKEDELAY goes below the brake delay threshold voltage  $V_{BDT}$  of 2.2 V. The gates of the three spindle low-side power drivers are charged by the energy stored in the BRAKEPOWER capacitor and thus braking the motor.

The OM5193H will stay in the brake-after-park mode until register#1 (3) bit run/stop is set to logic 1.

### Disk drive spindle and VCM with servo controller

OM5193H

The typical value for the BRAKEPOWER capacitor is 1  $\mu$ F. An optional resistance could be added between the BRAKEPOWER and BRAKEADJUST pins. The values of the capacitor and the resistor are depending on the application.

Without resistor, the BRAKEADJH pin must be connected to the BRAKEPOWER pin.

### 8.15 Power-on reset

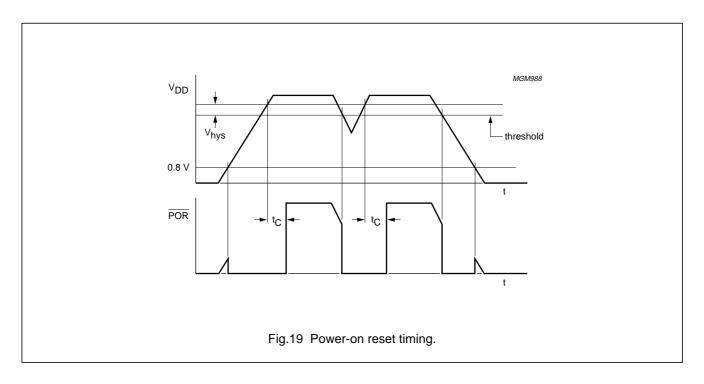

The Power-On Reset (POR) circuit monitors the voltage level of both 5 and 12 V supply voltages as shown in Fig.19.

The  $\overline{\text{POR}}$  active LOW logic line is set HIGH following the 5 and 12 V supply voltage rise above a specified voltage threshold plus a hysteresis, and delayed by a time  $t_C$  that is determined by the external CPOR capacitor.

This POR output remains HIGH until either the 5 or 12 V supplies drop below their voltage threshold, at which point the POR output becomes LOW.

The  $C_{CPOR}$  capacitor is charged with a typically 2.7  $\mu A$  current. The voltage on CPOR is compared to the POR circuit voltage reference of 2.55 V. The  $t_C$  time is set by the following equation:

$$t_{C} = \frac{C_{CPOR} \times V_{PORREF}}{I_{CPOR}}$$

(23)

where  $V_{PORREF}$  = 2.55 V and  $I_{CPOR}$  = 2.5  $\mu$ A typically.

The value of the  $t_{\text{C}}$  time is set by the  $C_{\text{CPOR}}$  capacitor value.

### Disk drive spindle and VCM with servo controller

OM5193H

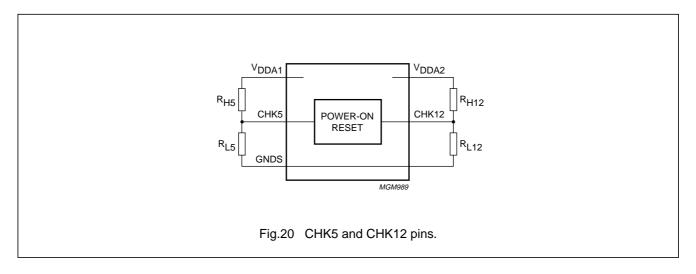

The values of the 5 and 12 V supply threshold voltages can be adjusted by adding external bridge resistors respectively on the CHK5 and CHK12 pins. Internally, the CHK5 and CHK12 pins are designed as described in Fig.20.

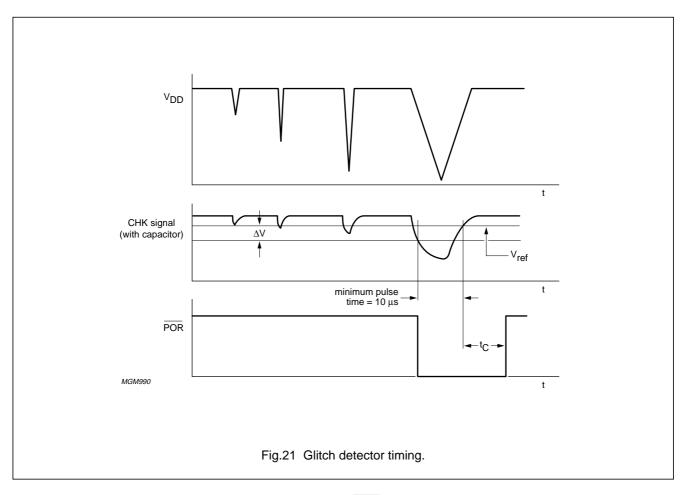

A glitch monitor prevents premature  $\overline{POR}$  signals due to voltage spikes on power supplies. An external capacitor has to be connected to the CHK5 and CHK12 pins to filter the noise on CHK5 and CHK12 pins caused by spikes on the power supplies; see Fig.21.

### Disk drive spindle and VCM with servo controller

OM5193H

During a power-down situation, the POR circuit must not only generate an output  $\overline{POR}$  signal, but must also activate the brake-after-park sequence. In doing so, the VCM driver draws power from the BEMF of the motor coils through the clamp line during spin-down, and uses this power to bias the VCM against one of the hard stops of the actuator. This prevents the heads from landing on data zones.

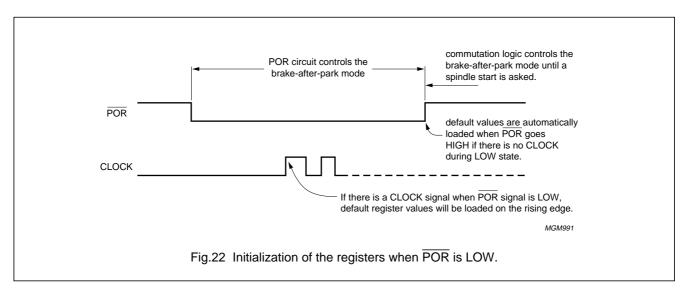

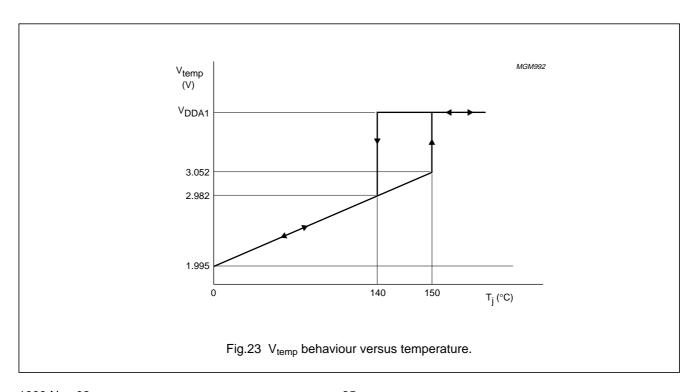

POR also controls the digital part of the chip.