INTEGRATED CIRCUITS

Preliminary specification File under Integrated Circuits, IC17 1996 Dec 11

### CONTENTS

| 1                                                    | FEATURES                                                                                                                                                                                               |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                    | DESCRIPTION                                                                                                                                                                                            |

| 2.1                                                  | Compatibility between P90CL301AFH and P90CL301BFH                                                                                                                                                      |

| 3                                                    | ORDERING INFORMATION                                                                                                                                                                                   |

| 4                                                    | BLOCK DIAGRAM                                                                                                                                                                                          |

| 5                                                    | PINNING INFORMATION                                                                                                                                                                                    |

| 5.1<br>5.2                                           | Pinning<br>Pin description                                                                                                                                                                             |

| 6                                                    | SYSTEM CONTROL                                                                                                                                                                                         |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7<br>6.8 | Memory organization<br>Programmable chip-select<br>Dynamic bus port sizing<br>System Control Register (SYSCON)<br>Reset operation<br>Clock generation<br>Interrupt controller<br>Power reduction modes |

| 7                                                    | CPU FUNCTIONAL DESCRIPTION                                                                                                                                                                             |

| 7.1<br>7.2<br>7.3<br>7.4<br>7.5<br>7.6<br>7.7<br>8   | General<br>Programming model and data organization<br>Processing states and exception processing<br>Tracing<br>Stack format<br>CPU interrupt processing<br>Bus arbitration<br>PORTS                    |

| 8.1                                                  | Port P Control Register (PCON)                                                                                                                                                                         |

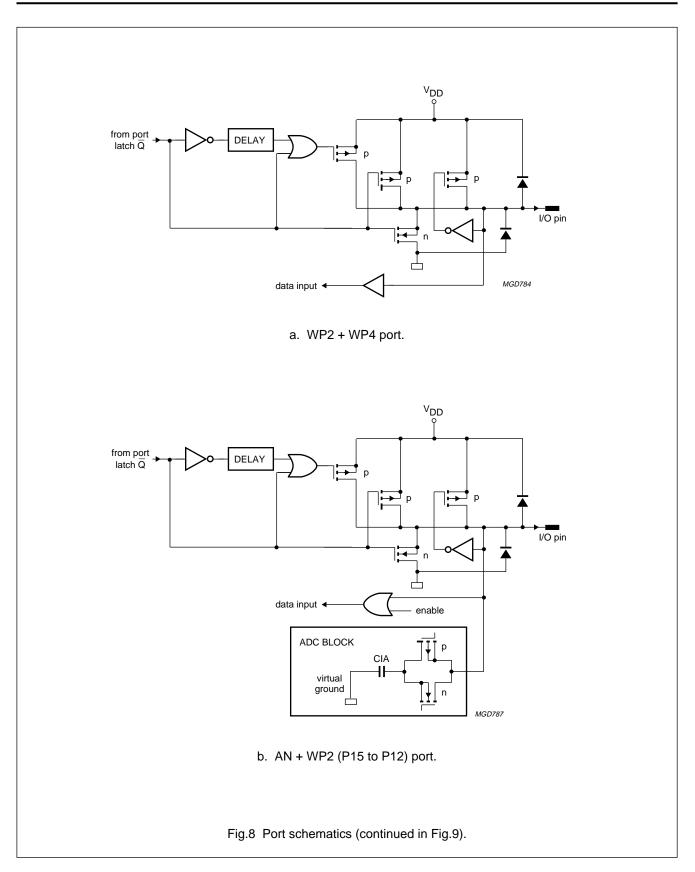

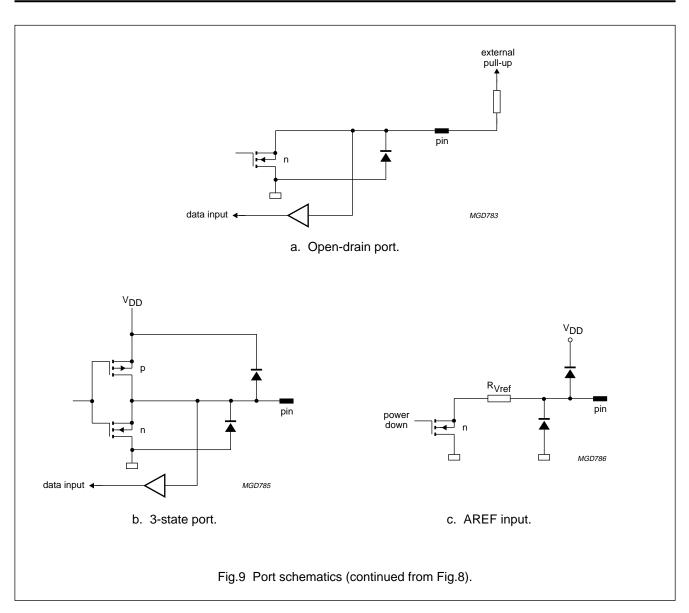

| 8.2<br>8.3                                           | Port SP<br>Ports schematics                                                                                                                                                                            |

| 9                                                    | 8051 PERIPHERAL BUS                                                                                                                                                                                    |

| 10                                                   | ON-CHIP PERIPHERAL FUNCTIONS                                                                                                                                                                           |

| 10.1                                                 | Peripheral interrupt control                                                                                                                                                                           |

| 11                                                   | TIMERS                                                                                                                                                                                                 |

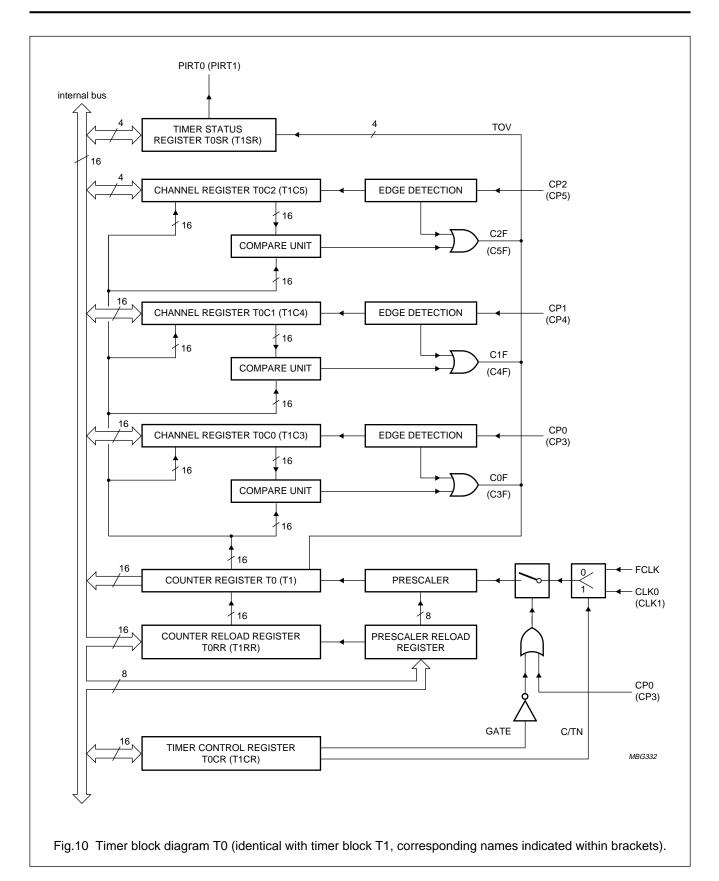

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5<br>11.6         | Timer array<br>Timebase<br>Channel function<br>Pin parallel functions for the timer<br>Timer Control Registers<br>Timer Status Register                                                                |

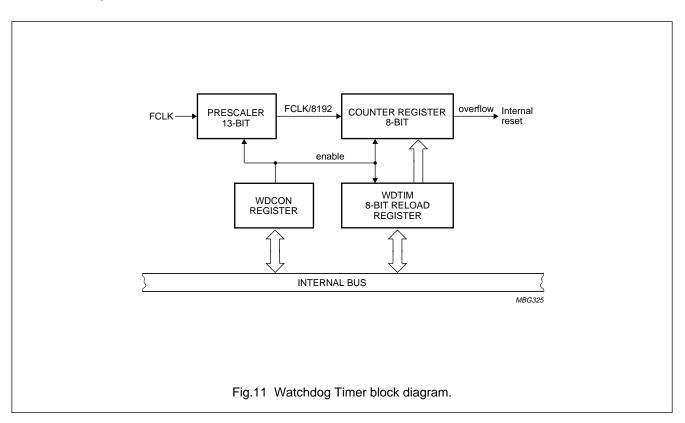

11.7 Watchdog Timer

# P90CL301BFH (C100)

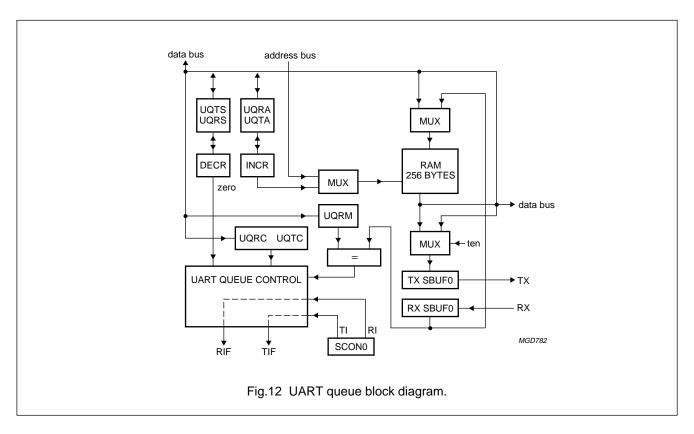

| 12           | SERIAL INTERFACES                                                   |

|--------------|---------------------------------------------------------------------|

| 12.1         | UART interface                                                      |

| 12.2         | Baud rate generator                                                 |

| 12.3<br>12.4 | UART queue<br>I <sup>2</sup> C-bus interface                        |

| 12.4         | Serial Control Register (SCON)                                      |

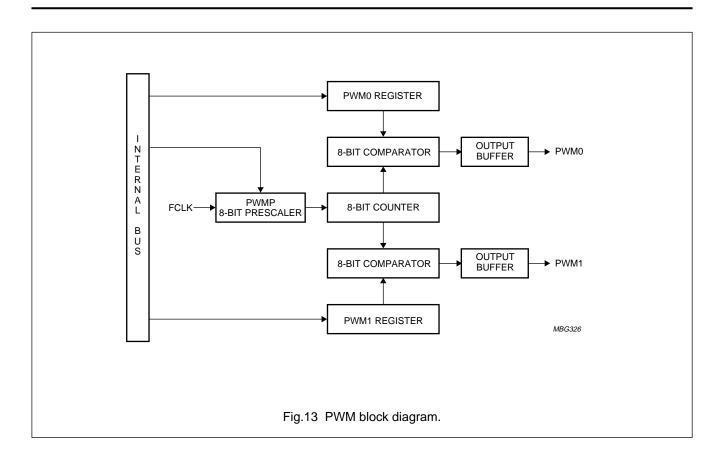

| 13           | PULSE WIDTH MODULATION OUTPUTS<br>(PWM)                             |

| 13.1<br>13.2 | Prescaler PWM Register (PWMP)<br>PWM Data Registers (PWM0 and PWM1) |

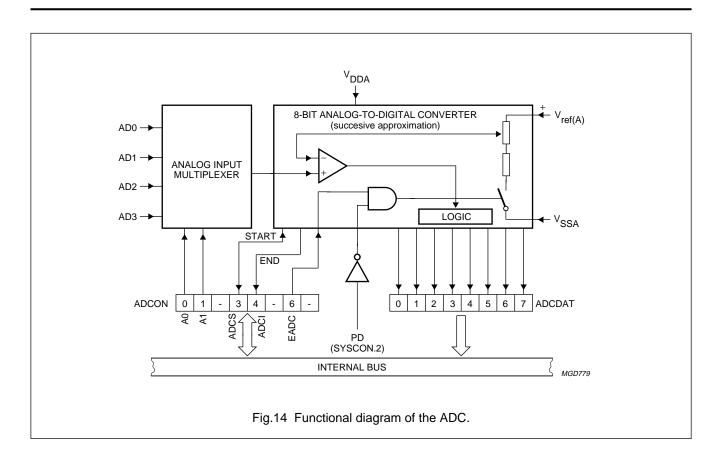

| 14           | ANALOG-TO-DIGITAL CONVERTER (ADC)                                   |

| 14.1         | ADC Control Register (ADCON)                                        |

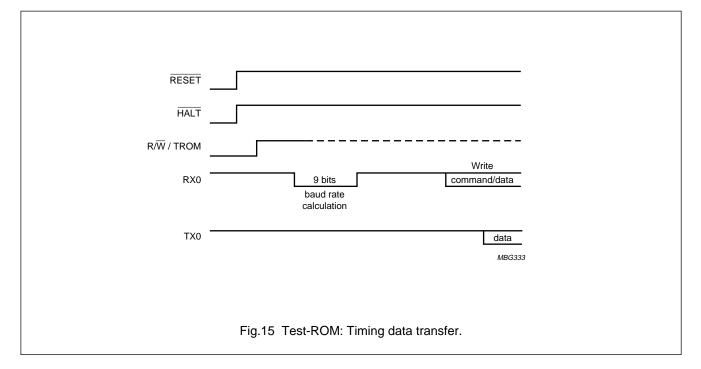

| 15           | ON-BOARD TEST CONCEPT                                               |

| 15.1<br>15.2 | ONCE mode<br>Test ROM                                               |

| 16           | ON-CHIP RAM                                                         |

| 17           | REGISTER MAPPING                                                    |

| 18           | LIMITING VALUES                                                     |

| 19           | DC CHARACTERISTICS                                                  |

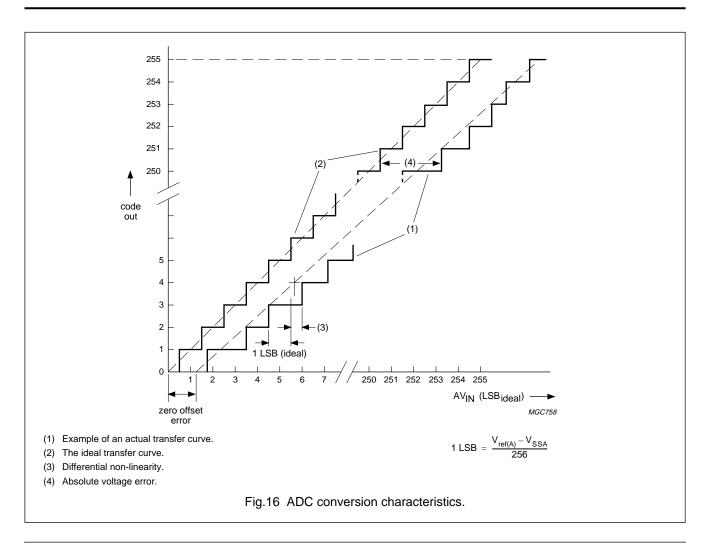

| 20           | ADC CHARACTERISTICS                                                 |

| 21           | AC CHARACTERISTICS                                                  |

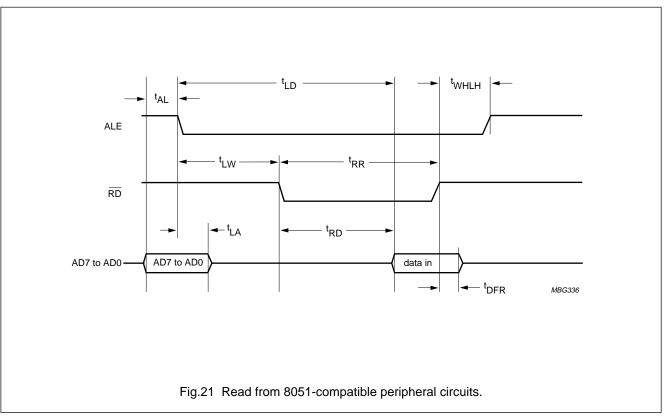

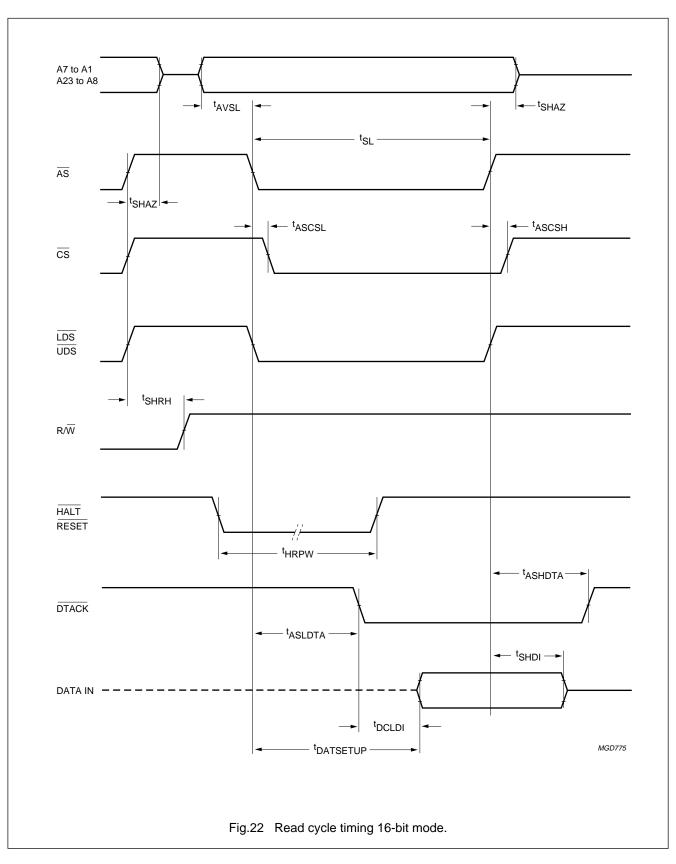

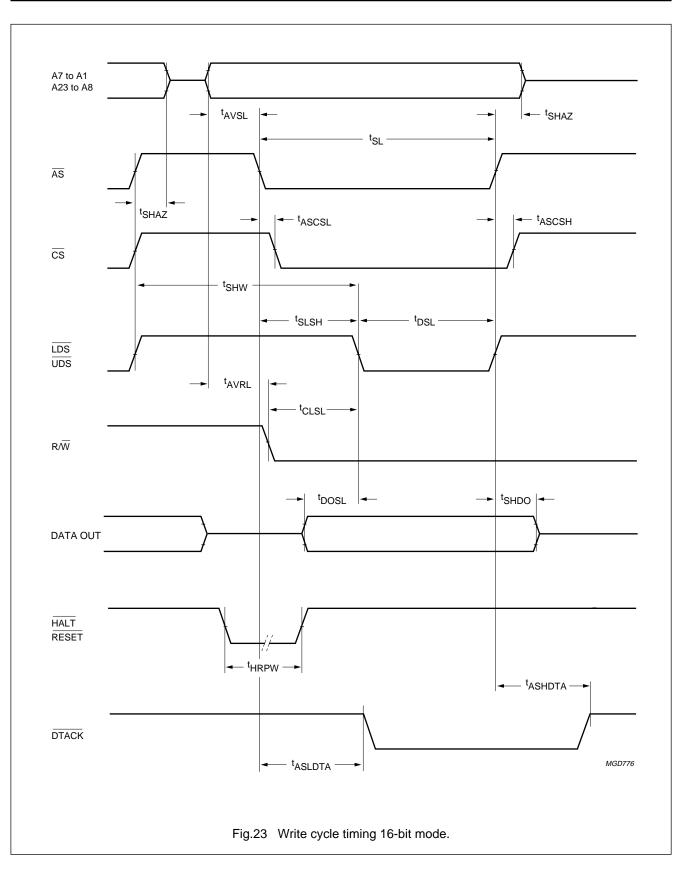

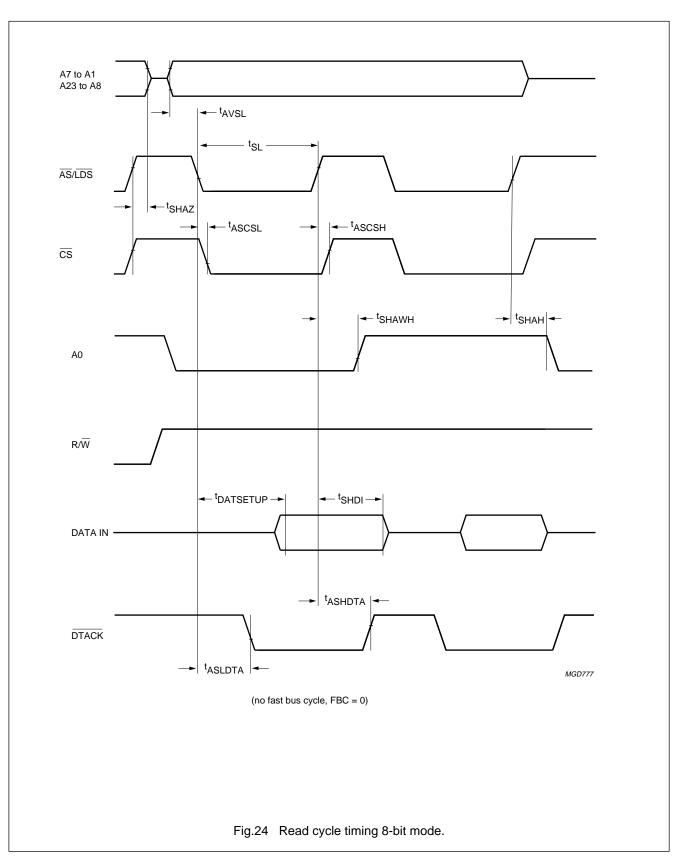

| 22           | 8051 BUS TIMING                                                     |

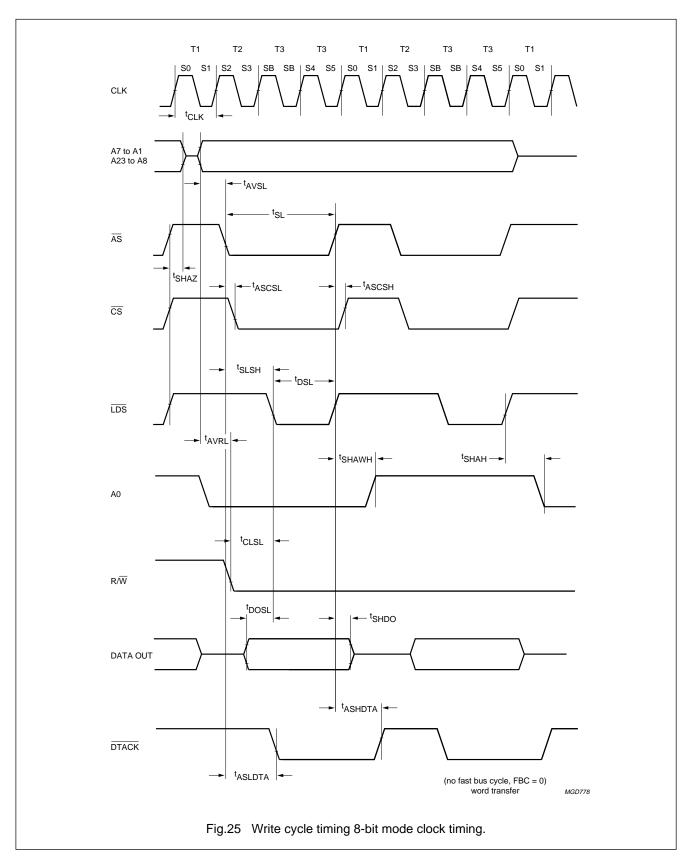

| 23           | TIMING DIAGRAMS                                                     |

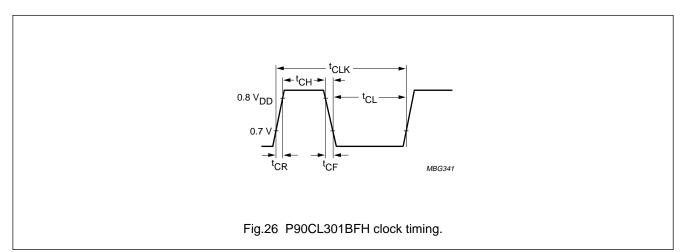

| 24           | CLOCK TIMING                                                        |

| 25           | PIN STATES IN VARIOUS MODES                                         |

| 26           | INSTRUCTION SET AND ADDRESSING MODES                                |

| 26.1         | Addressing modes                                                    |

| 27           | INSTRUCTION TIMING                                                  |

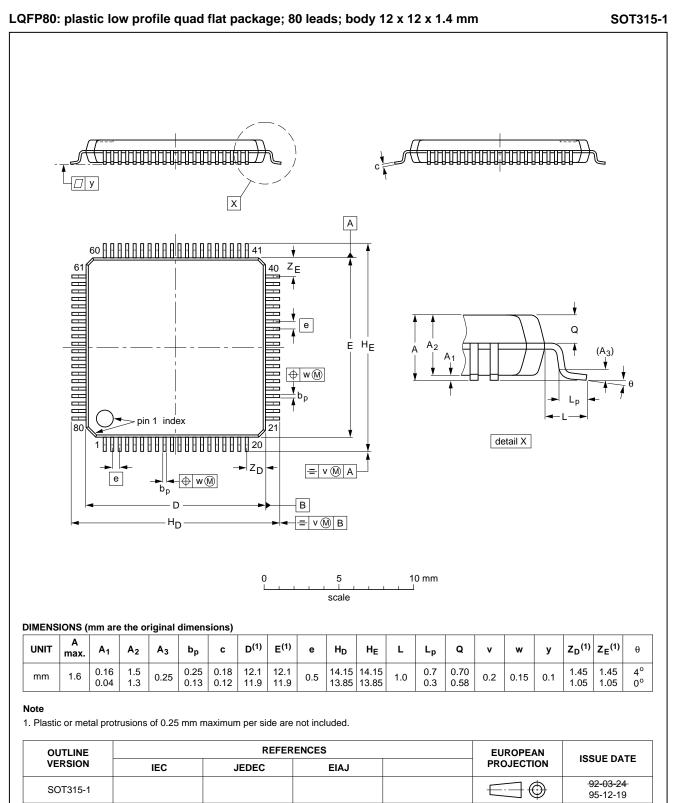

| 28           | PACKAGE OUTLINE                                                     |

| 29           | SOLDERING                                                           |

| 29.1         | Introduction                                                        |

| 29.2<br>29.3 | Reflow soldering                                                    |

| 29.3<br>29.4 | Wave soldering<br>Repairing soldered joints                         |

| 30           | DEFINITIONS                                                         |

| 31           | LIFE SUPPORT APPLICATIONS                                           |

| 32           | PURCHASE OF PHILIPS I <sup>2</sup> C COMPONENTS                     |

|              |                                                                     |

### **1 FEATURES**

- Fully 68000 software compatible

- Static design with 32-bit internal structure

- Power saving modes: Power-down, Standby and Idle mode

- External clock input: 27 MHz at 2.7 V

- Single supply voltage of 2.7 to 3.6 V; down to 1.8 V for RAM retention

- 68000 compatible bus interface

- Intel 8051 compatible bus interface

- 16 Mbytes program/data address range

- 8 programmable chip-selects

- Dynamic bus sizing, 16 or 8-bit memory bus port size

- 56 powerful instruction types:

- 5 basic data types, and

- 14 addressing modes

- 7 programmable interrupt inputs:

- a Non-Maskable Interrupt input (NMIN)

- 14 auto-vectored interrupts and 7 interrupt priority levels

- 24 port pins (multiplexed with other functions)

- 2 UART serial interfaces; an independent baud rate generator with two programmable outputs (UART0 and UART1)

- UART queue with maximum 256 bytes

- I<sup>2</sup>C-bus serial interface 100 kbaud

- 2 timer arrays including:

- two 16-bit reference counters and 8-bit programmable prescalers

- six 16-bit match/capture registers with equality comparators

- Watchdog Timer with 21-bit resolution

- Two 8-bit Pulse Width Modulation (PWM) outputs with 8-bit prescaler

- Four 8-bit Analog-to-Digital Converter (ADC) inputs with Power-down mode

- 512 bytes RAM on-chip

- On-Circuit Emulation (ONCE) mode and internal Test-ROM (256 bytes) for on-board testing

- 80-pin LQFP package

- Temperature range –40 to +85 °C

- 0.5 micron CMOS low voltage technology.

### 2 DESCRIPTION

The P90CL301BFH is a highly integrated low-voltage 16/32-bit microcontroller especially suitable for digital mobile systems such as GSM, DCS1900, IS54/95 and other applications requiring low voltage, low power consumption and high computing power. It is fully software compatible with the 68000.

The P90CL301BFH optimizes system cost by providing both standard as well as advanced peripheral functions on-chip. The P90CL301BFH has a full static design and special Idle, Standby and Power-down modes which allow further reduction of the total system power consumption. An 80-pin LQFP package dramatically reduces system size requirements.

# 2.1 Compatibility between P90CL301AFH and P90CL301BFH

For functional compatibility between P90CL301AFH (SAC1 process) and P90CL301BFH (C100 process), the following points should be considered when using the P90CL301BFH:

- Wake-up; to wake-up the processor from Power-down mode via the activation of an external SPn pin, it is necessary to enable the interrupt mode first by setting the corresponding bit in the SPCON register.

- SYSCON register; for the P90CL301AFH bits 11 to 15 in the SYSCON register should not be set in order to keep additional functionality in the P90CL301BFH inactive.

| TYPE NUMBER |        |                                                                                    |          |            |  |  |  |

|-------------|--------|------------------------------------------------------------------------------------|----------|------------|--|--|--|

| ITFE NUMBER | NAME   | DESCRIPTION                                                                        | VERSION  | RANGE (°C) |  |  |  |

| P90CL301BFH | LQFP80 | plastic low profile quad flat package; 80 leads; body $12 \times 12 \times 1.4$ mm | SOT315-1 | -40 to +85 |  |  |  |

#### **3 ORDERING INFORMATION**

### P90CL301BFH (C100)

# P90CL301BFH (C100)

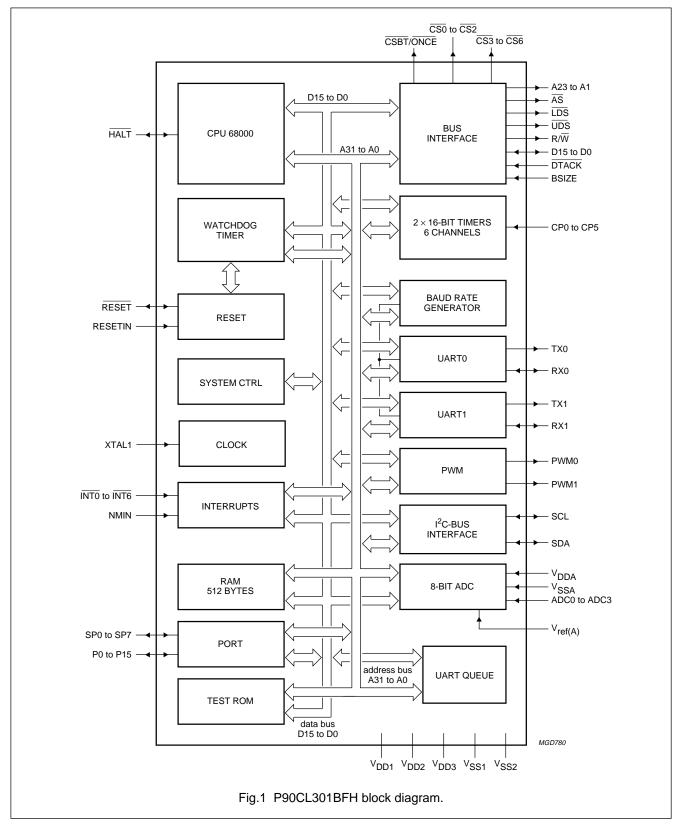

### 4 BLOCK DIAGRAM

P90CL301BFH (C100)

### Low voltage 16-bit microcontroller

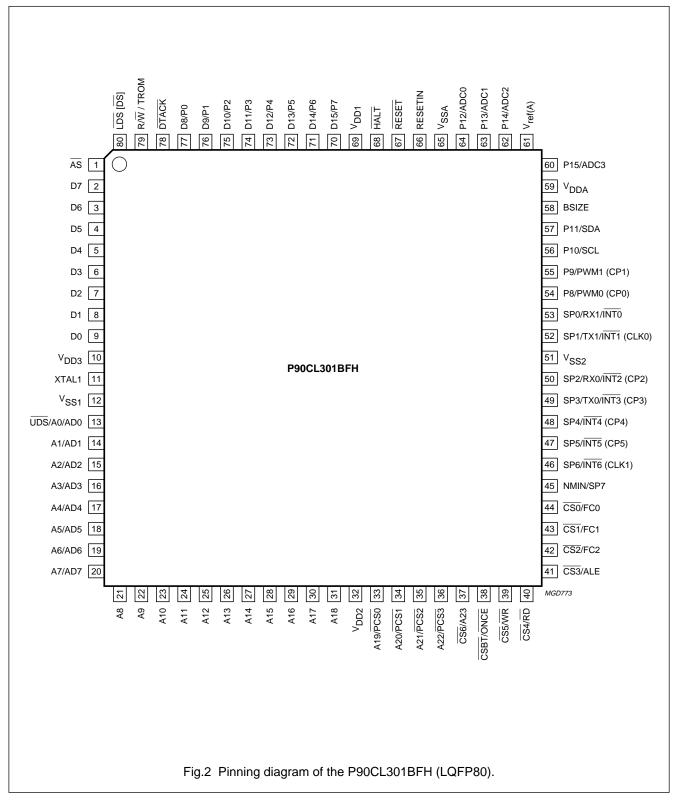

### 5 PINNING INFORMATION

### 5.1 Pinning

# P90CL301BFH (C100)

#### 5.2 Pin description

**Table 1**Pin description for the P90CL301BFH

| SYMBOL <sup>(1)</sup> | PIN      | DESCRIPTION                                                                                                  |  |  |  |

|-----------------------|----------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| ĀS                    | 1        | address strobe                                                                                               |  |  |  |

| D7 to D0              | 2 to 9   | lower 8-bits of data bus                                                                                     |  |  |  |

| V <sub>DD3</sub>      | 10       | supply voltage; third pin                                                                                    |  |  |  |

| XTAL1                 | 11       | external clock input                                                                                         |  |  |  |

| V <sub>SS1</sub>      | 12       | ground; first pin                                                                                            |  |  |  |

| UDS/A0/AD0            | 13       | upper data strobe or LSB of address bus or LSB of 8051 address/data                                          |  |  |  |

| A1/AD1 to A7/AD7      | 14 to 20 | lower 7-bits of the 68000 address bus or lower 7-bits of the 8051 bus                                        |  |  |  |

| A8 to A18             | 21 to 31 | upper 11-bits of the 68000 address bus                                                                       |  |  |  |

| V <sub>DD2</sub>      | 32       | supply voltage; second pin                                                                                   |  |  |  |

| A19/PCS0 to A22/PCS3  | 33 to 36 | upper 4-bits of the address bus or 8051 bus chip-select                                                      |  |  |  |

| CS6/A23               | 37       | chip-select 6 or address bit 23                                                                              |  |  |  |

| CSBT/ONCE             | 38       | chip-select boot or ONCE mode forced input                                                                   |  |  |  |

| CS5/WR                | 39       | chip-select 5 or 8051 bus write strobe                                                                       |  |  |  |

| CS4/RD                | 40       | chip-select 4 or 8051 bus read strobe                                                                        |  |  |  |

| CS3/ALE               | 41       | chip-select 3 or 8051 bus address latch                                                                      |  |  |  |

| CS2/FC2 to CS0/FC0    | 42 to 44 | chip-select 2 to 0 or data bus function code 2 to 0                                                          |  |  |  |

| NMIN/SP7              | 45       | Non-Maskable Interrupt or second port pin (bit 7)                                                            |  |  |  |

| SP6/INT6 (CLK1)       | 46       | second port pin (bit 6) external interrupt input 6 (external clock of timer 1)                               |  |  |  |

| SP5/INT5 (CP5)        | 47       | second port pin (bit 5) or external interrupt input 5 (Timer 1 capture input 5)                              |  |  |  |

| SP4/INT4 (CP4)        | 48       | second port pin (bit 4) or external interrupt input 4 (Timer 1 capture input 4)                              |  |  |  |

| SP3/TX0/INT3 (CP3)    | 49       | second port pin (bit 3) or Transmit data for UART0 or external interrupt input 3 (Timer 1 capture input 3)   |  |  |  |

| SP2/RX0/INT2 (CP2)    | 50       | second port pin (bit 2) or Receive data for UART0 or external interrupt input 2 (Timer 0 capture input 2)    |  |  |  |

| V <sub>SS2</sub>      | 51       | ground; second pin                                                                                           |  |  |  |

| SP1/TX1/INT1 (CLK0)   | 52       | second port pin (bit 1) or transmit data for UART1 or external interrupt input 1 (external clock of Timer 0) |  |  |  |

| SP0/RX1/INT0          | 53       | second port pin (bit 0) or receive data for UART1 or external interrupt input 0                              |  |  |  |

| P8/PWM0 (CP0)         | 54       | port pin (bit 8) or PWM0 output (Timer 0 capture input 0)                                                    |  |  |  |

| P9/PWM1 (CP1)         | 55       | port pin (bit 9) or PWM1 output (Timer 0 capture input 1)                                                    |  |  |  |

| P10/SCL               | 56       | port pin (bit 10) or I <sup>2</sup> C-bus Serial Clock.                                                      |  |  |  |

| P11/SDA               | 57       | port pin (bit 11) or I <sup>2</sup> C-bus Serial Data.                                                       |  |  |  |

| BSIZE                 | 58       | data bus size; 8 or 16-bit wide                                                                              |  |  |  |

| V <sub>DDA</sub>      | 59       | ADC supply voltage                                                                                           |  |  |  |

| P15/ADC3              | 60       | port pin (bit 15) or ADC input 3                                                                             |  |  |  |

| V <sub>ref(A)</sub>   | 61       | ADC reference voltage                                                                                        |  |  |  |

| P14/ADC2 to P12/ADC0  | 62 to 64 | port pin (bit 14 to bit 12) or ADC inputs 2 to 0                                                             |  |  |  |

| V <sub>SSA</sub>      | 65       | ADC ground                                                                                                   |  |  |  |

| RESETIN               | 66       | external Power-on-reset input                                                                                |  |  |  |

# P90CL301BFH (C100)

| SYMBOL <sup>(1)</sup> | PIN      | DESCRIPTION                                                                                                 |  |  |  |

|-----------------------|----------|-------------------------------------------------------------------------------------------------------------|--|--|--|

| RESET                 | 67       | reset (bidirectional)                                                                                       |  |  |  |

| HALT                  | 68       | nalt (bidirectional)                                                                                        |  |  |  |

| V <sub>DD1</sub>      | 69       | supply voltage; first pin                                                                                   |  |  |  |

| D15/P7 to D8/P0       | 70 to 77 | upper 8-bits of data bus or 8-bit Port 7 to Port 0; the selected function after resist defined by pin BSIZE |  |  |  |

| DTACK                 | 78       | data transfer acknowledge                                                                                   |  |  |  |

| R/W / TROM            | 79       | read/write bus control or Test-ROM forced input                                                             |  |  |  |

| LDS [DS]              | 80       | lower data strobe [word data strobe]                                                                        |  |  |  |

### Note

- a) Function1/Function2/Function3: multiplexed functions on the same pin. During and after reset the Function1 is selected.

- b) Function1 (Function2): function done in parallel.

- c) Function1 [Function2]: equivalent function.

<sup>1.</sup> The following notation is used to describe the multiple pin definitions:

### P90CL301BFH (C100)

#### 6 SYSTEM CONTROL

#### 6.1 Memory organization

The maximum external address space of the controller is 16 Mbytes. It can be partitioned into five address spaces. These address spaces are designated as either User or Supervisor space and as either Program or Data space or as interrupt acknowledge.

For slow memories the CPU can be programmed to insert a number of wait states. This is done via the eight Chip-select Control Registers CSON to CS7N; further to be denoted as CSnN, where n = 0 to 7. The number of inserted wait states can vary from 0 to 6, or wait states are inserted until the DTACK is pulled LOW by the external address decoding circuitry. If DTACK is asserted continuously, the P90CL301BFH will run without wait states using bus cycles of three or four clock periods depending on the state of the FBC bit in the SYSCON register.

#### 6.1.1 MEMORY MAP

The memory address space is divided as shown in Table 2; short addressing space with A31 to A15 = 1.

| ADDRESS (HEX)          | DESCRIPTION                |

|------------------------|----------------------------|

| 0000 0000 to 00FF FFFF | external 16 Mbytes         |

|                        | memory                     |

| 0100 0000 to 8000 FFFF | not used                   |

| 8001 0000 to 8001 FFFF | off-chip 64 kbytes on 8051 |

|                        | bus                        |

| 8002 0000 to FFFF 7FFF | not used                   |

| FFFF 8000 to FFFF 8AFF | internal registers         |

| FFFF 8B00 to FFFF 8FFF | not used                   |

| FFFF 9000 to FFFF 91FF | internal 512 bytes RAM     |

| FFFF 9200 to FFFF BFFF | not used                   |

| FFFF C000 to FFFF C0FF | internal 256 bytes         |

|                        | Test-ROM                   |

| FFFF C100 to FFFF FFFF | not used                   |

#### Table 2 Memory address space

#### 6.2 Programmable chip-select

In order to reduce the external components associated with memory interface, the P90CL301BFH provides 8 programmable chip-selects. A specific chip-select CSBT provides default reset values to support a bootstrap operation.

Each chip-select can be programmed with:

- A base address (A23 to A19)

- A memory bank width of 512 kbytes, 1, 2, 4 or 8 Mbytes memory size

- A number of wait states (0 to 6 states, or wait for DTACK) to adapt the bus cycle to the memory cycle time.

Chip-selects can be synchronized with read, write, or both read and write, either Address strobe or Data strobe. They can also be programmed to address low byte, high byte or word.

Each chip-select is controlled by a control register CSnN (n = 0 to 7). The control registers are described in Table 3 to 7.

The RESET instruction does not affect the contents of the CSnN registers.

Register CS7N corresponds to register  $\overline{\text{CSBT}}$  (address FFFF 8A0EH). After reset  $\overline{\text{CSBT}}$  is programmed with a block size of 8 Mbytes with:

- A19 to A23 at logic 0

- M19 to M22 at logic 1

- · 6 wait states

- · read only mode.

The other chip-selects are held HIGH and will be activated after initialization of their control registers.

When programmed in reduced access mode (read only, write only, low byte, high byte), the wait states are generated internally and if there is any access-violation when the bit WD in the SYSCON register is set to a logic 1 (time-out), the processor will execute a bus error after the time-out delay.

# P90CL301BFH (C100)

6.2.1 CHIP SELECT CONTROL REGISTERS (CS0N TO CS7N)

### Table 3 Chip Select Control Registers CS0N to CS7N (address FFFF 8A00H to FFFF 8A0CH)

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| M22 | M21 | M20 | M19 | RW1 | RW0 | MD1 | MD0 | A23 | A22 | A21 | A20 | A19 | WS2 | WS1 | WS0 |

### Table 4 Description of CS0N to CS7N bits

| BIT      | SYMBOL     | DESCRIPTION                                                                                                                                                                                                                                            |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 | M22 to M19 | Address mask for block size selection; see Table 5.                                                                                                                                                                                                    |

| 11 to 10 | RW1 to RW0 | Read/Write bus control ( $R/\overline{W}$ ); see Table 6.                                                                                                                                                                                              |

| 9 to 8   | MD1 to MD0 | MODE selection; see Table 7.                                                                                                                                                                                                                           |

| 7 to 3   | A23 to A19 | Decoded base address; this should be a multiple of the block size (other codes are reserved for test or reset state); after reset: A23 to A19 = 11111 except for $\overline{CSBT}$ .                                                                   |

| 2 to 0   | WS2 to WS0 | Wait states 0 to 6 (see Table 8); 7 wait states for $\overline{\text{DTACK}}$ to be pulled LOW by the external address decoding circuitry. The default value after reset is '110B' for $\overline{\text{CSBT}}$ and '111B' for the other chip-selects. |

#### Table 5 Address mask for block size selection

| M22 | M21 | M20 | M19 | BLOCK SIZE                                |

|-----|-----|-----|-----|-------------------------------------------|

| 0   | 0   | 0   | 0   | 512 kbytes                                |

| 0   | 0   | 0   | 1   | 1 Mbyte                                   |

| 0   | 0   | 1   | 1   | 2 Mbytes                                  |

| 0   | 1   | 1   | 1   | 4 Mbytes                                  |

| 1   | 1   | 1   | 1   | 8 Mbytes; default value after a CPU reset |

#### **Table 6**Read/Write bits $(R/\overline{W})$

| RW1 | RW0 | FUNCTION                                                                    |

|-----|-----|-----------------------------------------------------------------------------|

| 0   | 0   | Read only with length of $\overline{AS}$                                    |

| 0   | 1   | Write only with length of DS                                                |

| 1   | 0   | Write only with length of $\overline{AS}$                                   |

| 1   | 1   | Read/write with length of $\overline{AS}$ ; default value after a CPU reset |

#### Table 7Mode selection

| MD1 | MD0 | FUNCTION                                     |  |  |  |  |  |

|-----|-----|----------------------------------------------|--|--|--|--|--|

| 0   | 0   | Alternate function                           |  |  |  |  |  |

| 0   | 1   | Low byte access only                         |  |  |  |  |  |

| 1   | 0   | High byte access only                        |  |  |  |  |  |

| 1   | 1   | Word access; default value after a CPU reset |  |  |  |  |  |

#### Table 8 Wait states selection

| WS2 | WS1 | WS0 | WAIT STATES      |

|-----|-----|-----|------------------|

| 0   | 0   | 0   | 0                |

| 0   | 0   | 1   | 1                |

| 0   | 1   | 0   | 2                |

| 0   | 1   | 1   | 3                |

| 1   | 0   | 0   | 4                |

| 1   | 0   | 1   | 5                |

| 1   | 1   | 0   | 6 <sup>(1)</sup> |

### Note

1. The default value after a CPU reset.

### P90CL301BFH (C100)

corresponding bit of the register BSREG is used to define the sequence of bus transfer in 16 or 8-bit mode. Several

chip-selects with different bus sizes should not address

the same memory segment. For each case the number of

bus cycles necessary to transfer a byte, word or long word

is a function of the bus size. For example, a word read on

a 8-bit bus will take 2 bus cycles and the high byte is read

See Table 11 and 12 and also Section 6.2 for more

detailed information on the programmable chip-selects

first. The 8-bit port uses the pins D7 to D0.

and the dynamic bus sizing.

Number of clock periods per bus cycle, dependent on the programmed length of FBC (Fast Bus Cycle bit in the SYSCON register) and CSn (chip-select).

|                | LENGTH O | OF CSn = LENC | STH OF AS | LENGTH OF $\overline{\text{CSn}}$ = LENGTH OF $\overline{\text{DS}}$ |       |         |       |  |

|----------------|----------|---------------|-----------|----------------------------------------------------------------------|-------|---------|-------|--|

| WAIT<br>STATES | FBC      | ; = 1         | FBC = 0   | FBC                                                                  | ; = 1 | FBC = 0 |       |  |

|                | READ     | WRITE         | R/W       | READ                                                                 | WRITE | READ    | WRITE |  |

| 0              | 3        | 4             | 4         | 3                                                                    | 4     | 4       | 4     |  |

| 1              | 4        | 4             | 4         | 4                                                                    | 5     | 4       | 5     |  |

| 2              | 5        | 5             | 5         | 5                                                                    | 6     | 5       | 6     |  |

| 3              | 6        | 6             | 6         | 6                                                                    | 7     | 6       | 7     |  |

| 4              | 7        | 7             | 7         | 7                                                                    | 8     | 7       | 8     |  |

| 5              | 8        | 8             | 8         | 8                                                                    | 9     | 8       | 9     |  |

| 6              | 9        | 9             | 9         | 9                                                                    | 10    | 9       | 10    |  |

#### 6.3 Dynamic bus port sizing

The memory bus size can be selected to be 16 or 8-bit wide depending on the ports width of external memories and peripherals. It is possible via the register BSREG to define for each chip-select the bus width to 16-bit or 8-bit used for the transfer of data to or from external memory.

The 7-bit register BSREG defines the bus size associated with each chip-select function (except for  $\overline{\text{CSBT}}$ ).

The bus size of the chip-select boot  $\overline{\text{CSBT}}$  (CS7N) is hardware defined by the pin BSIZE.The state of the pin BSIZE is latched at the end of the reset sequence.

When an address generated by the CPU is identified by a chip-select block as belonging to it's address segment, the

6.3.1 BUS SIZE REGISTER (BSREG)

Table 10 Bus Size Register (address FFFF A811H)

| 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|

| - | BS6 | BS5 | BS4 | BS3 | BS2 | BS1 | BS0 |

#### Table 11 Description of BSREG bits

| BIT    | SYMBOL     | DESCRIPTION                                                                                                                                                                                                                                                                          |

|--------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | —          | Reserved.                                                                                                                                                                                                                                                                            |

| 6 to 0 | BS6 to BS0 | Bus size for the data transfer with respect to the corresponding chip-select $(\overline{CS6} \text{ to } \overline{CS0})$ . If BSn = 0, then the bus size is in 16-bit mode; the default value after a CPU reset. If BSn = 1, then the bus size is in 8-bit mode. Where n = 0 to 6. |

### P90CL301BFH (C100)

|           |           | BUS SIZE OF | CS0 TO CS6 <sup>(1)</sup> | BUS SIZE   | OF CSBTX      | PORT PL AVAILABLE |  |

|-----------|-----------|-------------|---------------------------|------------|---------------|-------------------|--|

| PIN BSIZE | BIT CSBTX | BSn = 0     | BSn = 1                   | AT<br>BOOT | AFTER<br>BOOT | (P0 TO P7)        |  |

| 0         | 0         | 16 bit      | 8 bit                     | 16         | 16            | no                |  |

| 0         | 1         | 16 bit      | 8 bit                     | 16         | 8             | yes               |  |

| 1         | 0         | note 2      | 8 bit                     | 8          | 8             | yes               |  |

| 1         | 1         | 16 bit      | 8 bit                     | 8          | 16            | no                |  |

#### Table 12 Bus size depending on BSIZE, CSBTX and BSn (n = 0 to 6)

#### Notes

- 1. Depending on bit BSn in register BSREG.

- The default value after reset of bits BSn in register BSREG is logic 0 which corresponds to 16-bit mode for CS0 to CS6. In this case, it is recommended to set BSn to logic 1 in the boot routine. Afterwards if CSBTX is set to logic 1, BSn can be reset to logic 0 by software for further transfers in 16-bit mode.

#### 6.4 System Control Register (SYSCON)

The P90CL301BFH uses a System Control Register (SYSCON) for adjusting system parameters.

Table 13 System Control Register (address FFFF 8000H)

| 15 | 5    | 14  | 13    | 12   | 11    | 10    | 9   | 8  | <b>7</b> <sup>(1)</sup> | <b>6</b> <sup>(1)</sup> | 5  | 4  | 3   | 2  | <b>1</b> <sup>(2)</sup> | 0    |

|----|------|-----|-------|------|-------|-------|-----|----|-------------------------|-------------------------|----|----|-----|----|-------------------------|------|

| WD | SC E | BPE | CSBTX | STBY | PCLK3 | PCLK2 | PDE | GF | PCLK1                   | PCLK0                   | IM | WD | FBC | PD | IDL                     | DOFF |

#### Notes

1. The default values after a CPU reset: PCLK1 = 1 and PCLK0 = 1; all other SYSCON bits are a logic 0.

2. All bits are reset by the RESET instruction, except the IDL bit which is only reset by a CPU reset.

# P90CL301BFH (C100)

| BIT            | SYMBOL                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15             | WDSC                      | <b>Bus error Watchdog short cycle</b> . WDSC = 0 for normal mode; the bus error Watchdog counts 2048 periods before activating the bus error sequence. WDSC = 1 for Bus error Watchdog short cycle; the Watchdog counts 16 periods before activating the bus error sequence.                                                                                                                                   |

| 14             | BPE                       | <b>Bus pull-up enable</b> . If BPE = 0, the Address and Data bus internal pull-ups are switched off. If BPE = 1, the Address and Data bus internal pull-ups are switched on.                                                                                                                                                                                                                                   |

| 13             | CSBTX                     | <b>Invert bus size for chip select boot and mode of port P0 to P7</b> . CSBTX = 0 for normal mode; bus size is defined by the pin BSIZE. If CSBTX = 1, the chip select boot is defined by the inverted value of the pin BSIZE. The mode change should be executed from the internal RAM or from a memory activated by any other chip select than $\overline{CSBT}$ . For further details see also Section 6.3. |

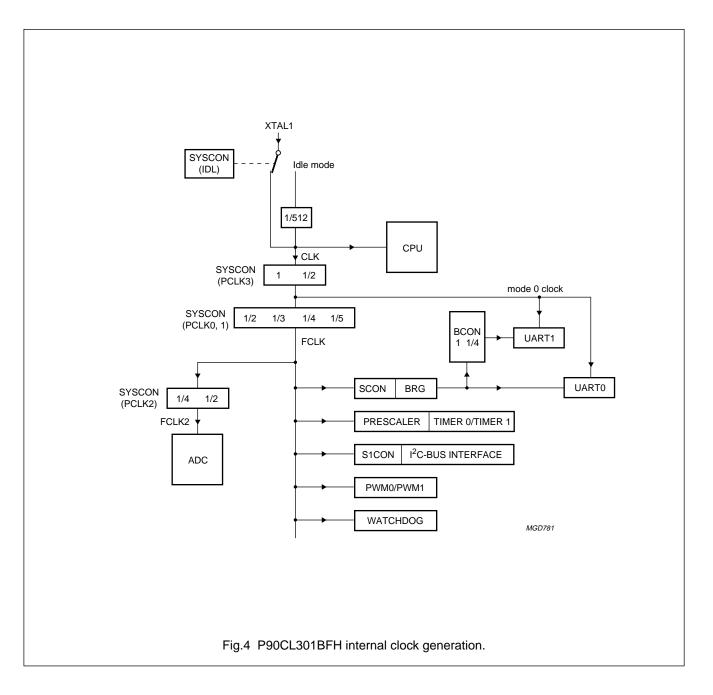

| 12             | STBY                      | <b>CPU Standby mode</b> . STBY = 0, for normal mode. STBY = 1, for Standby mode; only the CPU clock is switched off, the peripheral clocks are still running (see Fig.4).                                                                                                                                                                                                                                      |

| 11, 7<br>and 6 | PCLK3, PCLK1<br>and PCLK0 | <b>Prescaler for primary peripheral clock (FCLK) and the UART clock in mode 0</b> .<br>The CPU clock = CLK; FCLK = $\frac{1}{\text{divisor}} \times \text{CLK}$ . See Table 15 for the divisor values.                                                                                                                                                                                                         |

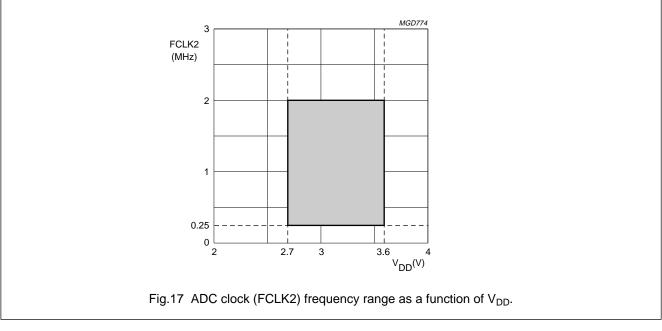

| 10             | PCLK2                     | <b>Prescaler for secondary peripheral clock FCLK2</b> (derived from the primary peripheral clock FCLK), used for the ADC; the maximum value of the FCLK2 clock is dependent on the supply voltage $V_{DD}$ ; see Section 19. If PCLK2 = 0, then FCLK is divided by 2; if PCLK2 = 1, then FCLK is divided by 4.                                                                                                 |

| 9              | PDE                       | If PDE = 0, then bits A22 to A19 are in normal operation; If PDE =1, then bits A22 to A19 are used as 8051 peripheral chip-select $\overline{PCS3}$ to $\overline{PCS0}$ .                                                                                                                                                                                                                                     |

| 8              | GF                        | General purpose flag bit; reset to a logic 0 after CPU reset.                                                                                                                                                                                                                                                                                                                                                  |

| 5              | IM                        | For IM = 0, level 7 is loaded into the Status Register during interrupt processing to prevent the CPU from being interrupted by another interrupt source. For IM = 1, the current interrupt level is loaded into the Status Register allowing nested interrupts.                                                                                                                                               |

| 4              | WD                        | For WD = 0, the time-out for bus error detection is switched off. If the time-out is not used, the Watchdog Timer can be used to stop a non-acknowledged bus transfer.<br>For WD = 1, the time-out for bus error detection is activated. If no DTACK has been sent by the addressed device after $128 \times 16$ internal clock cycles the on-chip bus error signal is activated.                              |

| 3              | FBC                       | FBC = 0, normal bus cycle; $FBC = 1$ , fast bus cycle. An external read bus cycle can take<br>a minimum of 3 clock periods; the minimum write cycle is still 4 clock periods; in order to<br>get this access time $\overline{DTACK}$ should be asserted on time.                                                                                                                                               |

| 2              | PD                        | PD = 0, for normal mode; PD = 1, for Power-down mode (see Section 6.8).                                                                                                                                                                                                                                                                                                                                        |

| 1              | IDL                       | IDL = 0, for normal mode; IDL = 1, for Idle mode (see Section 6.8).                                                                                                                                                                                                                                                                                                                                            |

| 0              | DOFF                      | DOFF = 0, for normal mode. DOFF = 1, for delay counter off; if set at wake-up from Power-down the delay counter waiting period is skipped.                                                                                                                                                                                                                                                                     |

### Table 14 Description of SYSCON bits

P90CL301BFH (C100)

### Low voltage 16-bit microcontroller

|       | •     |       |                                     |                            |

|-------|-------|-------|-------------------------------------|----------------------------|

| PCLK3 | PCLK1 | PCLK0 | DIVISOR (D)                         | DIVISOR FOR UART IN MODE 0 |

| 0     | 0     | 0     | 2                                   | 6                          |

| 0     | 0     | 1     | 3                                   | 6                          |

| 0     | 1     | 0     | 4                                   | 6                          |

| 0     | 1     | 1     | 5 (default value after a CPU reset) | 6                          |

| 1     | 0     | 1     | 6                                   | 12                         |

| 1     | 1     | 0     | 8                                   | 12                         |

| 1     | 1     | 1     | 10                                  | 12                         |

#### Table 15 Selection of prescaler divisor values

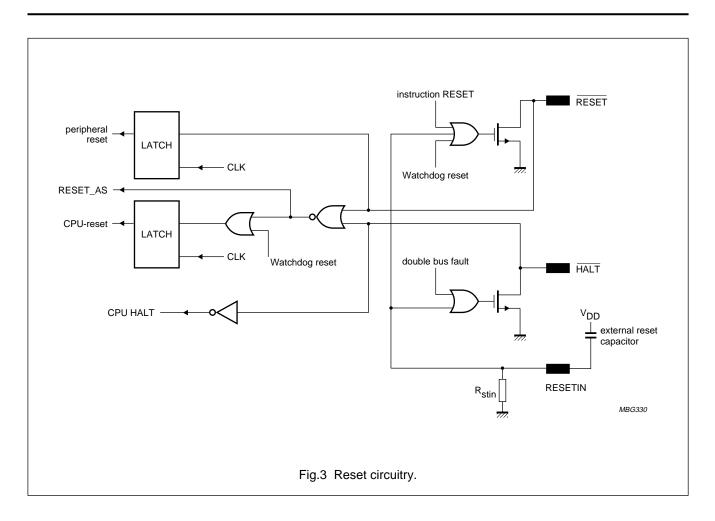

#### 6.5 Reset operation

The reset circuitry of the P90CL301BFH is connected to the pins RESET, HALT, RESETIN and to the internal Watchdog Timer. A Schmitt trigger is used at the input pin for noise rejection. After Power-on a CPU reset is accomplished by holding the RESET pin and the HALT pin LOW for at least 50 oscillator clocks after the oscillator has stabilized.

For further information on the clock generation, see Section 6.6. The CPU responds by reading the reset vectors; the long word at address 000000H is loaded into the Supervisor stack and the long word data at address 000004H is loaded into the program counter PC. The interrupt level is set to 7 in the Status Register and execution starts at the PC location. By pulling the RESET pin LOW and keeping HALT HIGH, only the peripherals are reset.

When  $V_{DD}$  is turned on and its rise time does not exceed 10 ms, an automatic reset can be performed by connecting the RESETIN pin to  $V_{DD}$  via an external capacitor. The external capacitor is charged via an internal pull-down resistor. The RESET pin can also be pulled LOW internally by a pull-down transistor activated by an overflow of the Watchdog Timer. When the CPU executes a RESET instruction, the RESET pin is pulled LOW. When the CPU is internally halted (at double bus fault), the HALT pin is pulled LOW and only a CPU reset can restart the processor.

The internal signal RESET\_AS (Reset Asynchronous) resets the core and all registers.

When an internal Watchdog Timer overflow occurs, an internal CPU reset is generated which resets all registers except the SYSCON, PCON, PRL and PRH registers and pulls the RESET pin LOW during 12 clock cycles.

# P90CL301BFH (C100)

#### 6.6 Clock generation

An external clock can be used with the P90CL301BFH. The duty cycle of the external clock should be  $50/50 \pm 5\%$  over the full temperature and voltage range.

For peripherals like Watchdog Timer, I<sup>2</sup>C-bus, PWM, Timer and baud rate generator, a programmable prescaler generates a peripheral clock FCLK.

# P90CL301BFH (C100)

The prescaler is controlled by the System Control Register (SYSCON). The internal clock is divided by a factor 2, 3, 4, 5, 6, 8 or 10 (function of bits PCLK0, PCLK1 and PCLK3; see Table 15).

For the ADC a secondary peripheral clock FCLK2 is derived from the peripheral clock by dividing it either by 4 or 2 (function of the bit PCLK2; see Table 14).

P90CL301BFH (C100)

### Low voltage 16-bit microcontroller

#### 6.7 Interrupt controller

An interrupt controller handles all internal and external interrupts. It delivers the interrupt with the highest priority level to the CPU. The following interrupt requests are generated by the on-chip peripherals:

- I<sup>2</sup>C-bus

- UARTs: received data / transmitted data

- Timers: two flags for the timers T0 and T1

- ADC: analog-to-digital conversion completed.

The external interrupt requests are generated with the pins NMIN and the seven external interrupts INTO to INTO.

#### 6.7.1 **INTERRUPT ARBITRATION**

The interrupt priority levels are programmable with a value between 0 and 7. Level 7 has the highest priority, level 0 disables the corresponding interrupt source. In case of interrupt requests of equal priority level at the same time a hardware priority mechanism gives priority order as shown in Table 16.

The execution of interrupt routines can be interrupted by another interrupt request of a higher priority level. In 68070 mode (SYSCON bit IM = 1) when an interrupt is serviced by the CPU, the corresponding level is loaded into the Status Register. This prevents the current interrupt from getting interrupted by any other interrupt request on the same or a lower priority level. If IM is reset, priority level 7 will always be loaded into the Status Register and so the current interrupt cannot be interrupted by an interrupt request of a level less than 7.

Each on-chip peripheral unit including the eight interrupt lines generate only auto-vectored interrupts. No acknowledge is necessary. For external interrupts the vectors 25 to 31 are used, for on-chip peripheral circuits a second table of 7 vectors are used (57 to 63); see Section 7.3.2.

#### Table 16 Priority order

| SIGNAL               | PRIORITY ORDER |

|----------------------|----------------|

| NMIN                 | highest        |

| INT6                 |                |

| INT5                 |                |

| INT4                 |                |

| INT3                 |                |

| INT2                 |                |

| INT1                 |                |

| INT0                 |                |

| l <sup>2</sup> C-bus |                |

| ADC                  |                |

| UART1 receiver       |                |

| UART1 transmitter    |                |

| UART0 receiver       |                |

| UART0 transmitter    |                |

| Timer 1              |                |

| Timer 0              | lowest         |

#### 6.7.2 **EXTERNAL LATCHED INTERRUPTS**

NMIN and INTO to INT6 are 8 external interrupt inputs. These pins are connected to the interrupt function only when the corresponding bit in the SPCON control register is set (see Section 8.2; Table 29). Seven interrupt inputs INT0 to INT6 are edge sensitive on HIGH-to-LOW transition and their priority levels are programmable. The interrupt NMIN is non-maskable (except if it is programmed as a port) and is also edge sensitive on HIGH-to-LOW transition. The priority level of NMIN is fixed to 7.

The external interrupts are controlled by the registers LIR0 to LIR3; see Tables 17 and 18.

| ADDRESS   | REGISTER | 7    | 6      | 5      | 4      | 3    | 2      | 1      | 0      |

|-----------|----------|------|--------|--------|--------|------|--------|--------|--------|

| FFF 8101H | LIR0     | PIR1 | IPL1.2 | IPL1.1 | IPL1.0 | PIR0 | IPL0.2 | IPL0.1 | IPL0.0 |

| FFF 8103H | LIR1     | PIR3 | IPL3.2 | IPL3.1 | IPL3.0 | PIR2 | IPL2.2 | IPL2.1 | IPL2.0 |

| FFF 8105H | LIR2     | PIR5 | IPL5.2 | IPL5.1 | IPL5.0 | PIR4 | IPL4.2 | IPL4.1 | IPL4.0 |

| FFF 8107H | LIR3     | PIR7 | 1      | 1      | 1      | PIR6 | IPL6.2 | IPL6.1 | IPL6.0 |

### Latched Interrupt Registers (LIR0 to LIR3) Table 17 Latched Interrupt Registers

6.7.2.1

# P90CL301BFH (C100)

#### Table 18 Description of LIR0 to LIR3 bits

| BIT     | SYMBOL           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 and 3 | PIRn             | <b>Pending interrupt request</b> . n = 0 to 7; $\overline{INT7}$ corresponds to the interrupt NMIN;<br>PIRn = 1, pending interrupt request for pin $\overline{INTn}$ . PIRn = 0 (default value after a CPU reset), no pending interrupt. When a valid interrupt request has been detected this bit is set. It is automatically reset by the interrupt acknowledge cycle from the CPU. It can be reset by software by writing a logic 0, however writing a logic 1 has no effect on the flag. To reset only one flag, a logic 0 should be written to the bit address and a logic 1 to the other interrupt requests. The use of BCLR instruction should be avoided (PIR7 is cleared when the pin NMIN is set HIGH) |

| 6 to 4  | IPLm.2 to IPLm.0 | Interrupt priority level of pins $\overline{INT0}$ to $\overline{INT6}$ (fixed to '111B' for NMIN in LIR3);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2 to 0  |                  | m = 0 to 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### 6.7.2.2 Pending Interrupt Flag Register (PIFR)

An additional register PIFR contains copies of the PIR flags. The PIF flags are set at the same time as the PIR flags when an interrupt is activated, but these flags are not reset automatically during the interrupt acknowledge cycle. They can only be cleared by software and keep a trace of the interrupt event. The detection of an external interrupt is indicated by the corresponding PIF-bit being set to a logic 1.

#### Table 19 Pending Interrupt Flag Register (address FFFF 810F)

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| PIF7 | PIF6 | PIF5 | PIF4 | PIF3 | PIF2 | PIF1 | PIF0 |

#### 6.7.3 NOTE ON SIMULTANEOUS INTERRUPTS

If an internal interrupt is immediately followed by an external interrupt (i.e. both interrupts occurring within 12 clock cycles) and both these interrupts have the same interrupt level, then the CPU might hang up during the acknowledge cycle of the internal interrupt.

In the interrupt controller a flag WIN is set for each interrupt as soon as the interrupt is activated and will be reset when an interrupt of higher priority occurs or during the acknowledge cycle. The WIN flag is used to determine which PIR flag should be reset.

A conflict occurs if within the interval starting at the CPU sampling of the first internal interrupt and ending at the acknowledge cycle, a second external interrupt resets the WIN flag of the first interrupt (external interrupts have higher priority than internal).

When the CPU acknowledges the first internal interrupt the auto-vector acknowledge signal cannot be asserted as its WIN flag was reset, and the CPU hangs up.

This situation can be solved by using the bus time-out counter controlled by the System Control Register (SYSCON) with the bits WD and WDSC set. In the case of hang-up an internal bus error condition will be asserted after 16 clocks and the CPU will execute the exception SPURIOUS INTERRUPT at vector 60H. In the exception service routine the interrupt flags PIR should be polled to detect which interrupts caused the conflict, the corresponding PIR flags should be cleared by software and a call to the interrupt routines executed.

P90CL301BFH (C100)

### Low voltage 16-bit microcontroller

#### 6.8 Power reduction modes

The P90CL301BFH supports three power reduction modes. A Power-down mode where the clock is frozen, a Standby mode where only the CPU is stopped, and an Idle mode where the external clock is divided by 512 (see Fig.4).

#### 6.8.1 POWER-DOWN MODE

The Power-down operation freezes the oscillator. It can only be activated by setting the PD bit in the SYSCON register and thereafter execute the STOP instruction.

The instruction flow to enter the Power-down mode is:

BSET #PD, SYSCON

STOP #\$2700.

In this state all the register contents are preserved. The CPU remains in this state until an internal reset occurs or a LOW level is present on any of the external interrupt pins  $\overline{INT0}$  to  $\overline{INT6}$  or NMIN. If the wake-up is done via an external interrupt, the processor will first execute an external interrupt of level 7. If the IPL level in the LIR register is set to 7, a second interrupt of level 7 will be executed. It is preferable to set the IPL to 0.

In Power-down mode  $V_{DD}$  may be reduced to minimize power consumption. However, the supply voltage must not be reduced until Power-down mode is active, and must be restored before a external reset or an interrupt is activated.

In case of an external reset, the pin should be held active until the external oscillator has restarted and stabilized.

In case of an external interrupt wake-up, any INTn or NMIN pin should go LOW and the corresponding bit ESn (n = 0 to 7) in register SPCON should be set. If the DOFF bit in the SYSCON is not set, an internal delay counter ensures that the internal clock is not active before 1536 clock cycles. After that time the oscillator is stable and normal exception processing can be executed. The PD bit is cleared automatically during the wake-up.

In order to have a fast start-up the DOFF bit should be set, switching off the delay counter and enabling the immediate clocking and restart of the controller.

For minimum power consumption during Power-down mode, the address and data pins should be pulled HIGH externally or bit BPE in register SYSCON should be set (i.e. internal pull-ups enabled).

#### 6.8.2 STANDBY MODE

When the STBY bit in the SYSCON register is set, the CPU clock is stopped and the status of the processor is frozen, however, the clocks of all other on-chip peripherals are still running at the nominal frequency; these peripherals are:

- Timers

- · External and internal interrupts

- UARTs and baud rate generator

- I<sup>2</sup>C-bus interface

- Watchdog Timer

- PWMs

- ADC.

The CPU exits this mode when an internal or external interrupt is activated, and proceeds with the normal program execution.

For minimum power consumption internal pull-ups on address and data buses can be switched on by setting the control bit BPE in the SYSCON register. The pull-ups should be switched off in normal mode if not needed.

#### 6.8.3 IDLE MODE

In the Idle mode the crystal or external clock is divided by a factor 512. The current is reduced drastically but the controller continues to operate. This mode is entered by setting the bit IDL in the SYSCON register. The next instruction will be executed at a slower speed. To return to normal mode the IDL bit should be reset.

It should be noted that all peripheral functions are also slowed down, and some cannot be used normally, for example UART, I<sup>2</sup>C-bus, ADC and PWM. The Power-down mode can also be entered from the Idle mode. After a wake-up the controller restarts in Idle mode.

# P90CL301BFH (C100)

### 7 CPU FUNCTIONAL DESCRIPTION

#### 7.1 General

The CPU of the P90CL301BFH is software compatible with the Motorola MC68000, hence programs written for the MC68000 will run on the P90CL301BFH without modifications. However, for certain applications the following differences between processors should be noted:

- Differences exist in the address/bus error exception processing since the P90CL301BFH can provide full error recovery.

- The timing is different for the P90CL301BFH due to a new internal architecture and technology. The instruction execution timing is different for the same reasons.

#### 7.2 Programming model and data organization

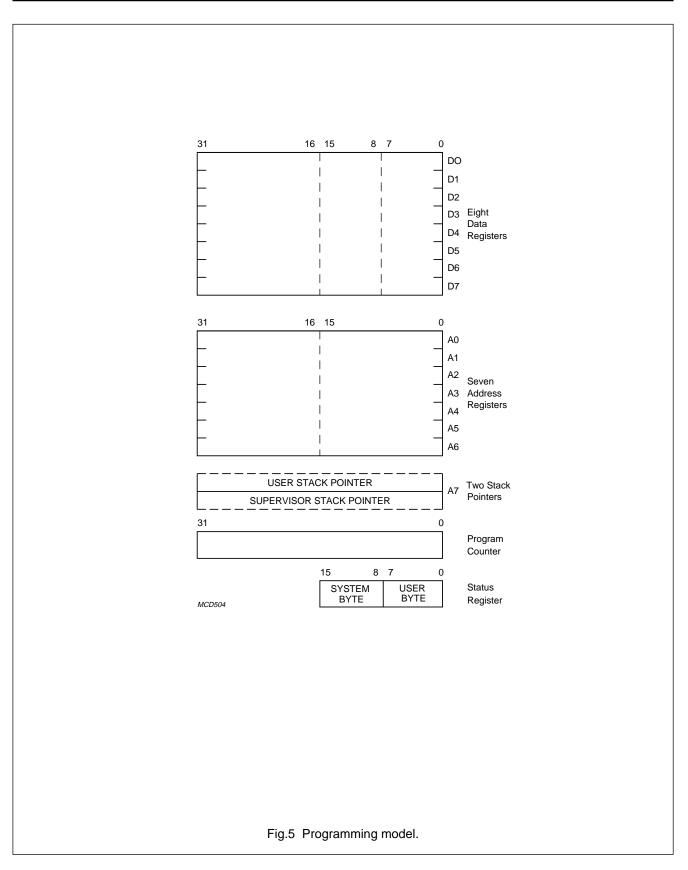

The programming model is identical to that of the MC68000 (see Fig.5), with seventeen 32-bit registers, a 32-bit Program Counter and a 16-bit Status Register. The eight data registers (D0 to D7) are used for byte, word and long-word operations. The Address Registers (A0 to A6) and the System Stack Pointer A7 can be used as software stack pointers and base address registers. In addition, these registers can be used for word and long-word address operations. All seventeen registers can be used as index registers.

The P90CL301BFH supports 8, 16 and 32-bit integers as well as BCD data and 32-bit addresses. Each data type is arranged in the memory as shown in Fig.6.

Table 20

Format of the Status Register and description of the bits; r = reserved

| 15         | 14 | 13         | 12 | 11 | 10    | 9      | 8    | 7 | 6 | 5 | 4      | 3        | 2    | 1        | 0     |

|------------|----|------------|----|----|-------|--------|------|---|---|---|--------|----------|------|----------|-------|

| Т          | _  | S          | _  | _  | 12    | 11     | 10   | _ | _ | _ | Х      | N        | Z    | V        | С     |

| Trace mode | r  | Supervisor | I  | r  | Inter | rupt r | nask |   | r |   | Extend | Negative | Zero | Overflow | Carry |

# P90CL301BFH (C100)

# P90CL301BFH (C100)

|     | bit                    | 7 6 5 4 3                    | <sup>3</sup> 2 1 0<br>yte = 8 bits). |                 |   |

|-----|------------------------|------------------------------|--------------------------------------|-----------------|---|

| bit | 15 14 13 12            | 11 10 9 8                    | 7 6 5 4                              | 3 2 1 0         |   |

|     | MSB BYT                | TE 0 LSB                     | BYTE 1                               |                 |   |

|     | BYT                    | E 2                          | BYTE                                 | 3               | I |

|     |                        | (b) Integer data (           | 1 Byte = 8 bits).                    |                 |   |

| bit | 15 14 13 12            | 11 10 9 8                    | 7654                                 | 3 2 1 0         |   |

|     | MSB                    | WORD                         | 0 0                                  | LSB             |   |

|     |                        | WORD                         | 01                                   |                 |   |

|     |                        | WORD                         | 2                                    |                 | I |

|     |                        | (c) Word data                | (16 bits).                           |                 |   |

| bit | 15 14 13 12<br>MSB LON | G WORD 0 — H                 | 7 6 5 4<br>IGH ORDER                 | 3 2 1 0         |   |

|     | — — — LON              | G WORD 1 — — ·               |                                      |                 |   |

|     | — — — LON              | G WORD 2 — — -               |                                      |                 |   |

|     |                        | (d) Long-word dat            | a (32 bits).                         |                 |   |

| bit | 15 14 13 12<br>MSB A   | .DDRESS 0                    | 7 6 5 4<br>IGH ORDER                 | 3 2 1 0         |   |

|     | A                      | DDRESS 1                     | IGH ORDER                            |                 |   |

|     | ———— A                 | DDRESS 2                     |                                      |                 |   |

|     | (6                     | e) Addresses (1 addre        | ess =32 bits).                       |                 |   |

| bit | 15 14 13 12            |                              | 654                                  | 3 2 1 0         |   |

|     | MSB BCD 0              | BCD 1 LSB                    | BCD 2                                | BCD 3           |   |

|     | BCD 4                  | BCD 5<br>(f) BCD data (2 BCE | BCD 6<br>0 digits = 1 Byte).         | BCD 7<br>MCD505 |   |

|     |                        | J.6 Memory dat               |                                      |                 |   |

#### 7.3 Processing states and exception processing

The P90CL301BFH operates with a maximum internal clock frequency of 27 MHz down to static operation. Each clock cycle is divided into 2 states. A non-access machine cycle has 3 clock cycles or 6 states (S0 to S5). A minimum bus cycle normally consists of 3 clock cycles (6 states). When DTACK is not asserted, indicating that data transfer has not yet been terminated, wait states (WS) are inserted in multiples of 2.

The CPU is always in one of the four processing states:

- Normal

- Exception

- Halt

- Stopped.

The Normal processing state is associated with instruction execution; the memory references fetch instructions or load/save results. A special case of the Normal state is the Stopped state which is entered by the processor when a STOP instruction is executed. In this state the CPU does not make any further memory references.

The Exception state is associated with interrupts, trap instruction, tracing and other exceptional conditions. The exception may be generated internally by an instruction or by any unusual condition arising during the execution of an instruction. Externally, exception processing can be forced by an interrupt or by reset.

The halted processing state is an indication of a catastrophic hardware failure. For example, if during exception processing of a bus error another bus error occurs, the CPU assumes that the system is unusable and halts. Only an external reset can restart a halted processor. Note that a CPU in the stopped state is not in the halted state or vice versa.

The Supervisor can work in the User or Supervisor state determined by the state of bit S in the Status Register. Accesses to the on-chip peripherals are achieved in the Supervisor state.

All exception processing is performed in the Supervisor state once the current contents of the Status Register has been saved. Then the exception vector number is determined and copies of the Status Register, the program counter and the format/vector number are saved on the Supervisor stack using the Supervisor Stack Pointer (SSP). Finally the contents of the exception vector location is fetched and loaded into the Program Counter (PC).

# P90CL301BFH (C100)

#### 7.3.1 REFERENCE CLASSIFICATION

When the processor makes a reference, it classifies the kind of reference being made, using the encoding of the three function code internal lines. This allows external translation of addresses, control of access, and differentiation of special processor states, such as interrupt acknowledge. Table 21 shows the classification of references.

Table 21 Reference classification

| FUN |     | DDE | REFERENCE CLASS       |

|-----|-----|-----|-----------------------|

| FC2 | FC1 | FC0 | - REFERENCE CLASS     |

| 0   | 0   | 0   | unassigned            |

| 0   | 0   | 1   | User Data             |

| 0   | 1   | 0   | User Program          |

| 0   | 1   | 1   | unassigned            |

| 1   | 0   | 0   | unassigned            |

| 1   | 0   | 1   | Supervisor Data       |

| 1   | 1   | 0   | Supervisor Program    |

| 1   | 1   | 1   | interrupt acknowledge |

### 7.3.2 EXCEPTION VECTORS

Exception vectors are memory locations from where the CPU fetches the address of a routine that will handle that exception. All exception vectors are 2 words long, except for the reset vector which consists of 4 words, containing the PC and the SSP. All exception vectors are in the Supervisor Data space.

A vector number is an 8-bit number which, multiplied by 4, gives the address of an exception vector. Vector numbers are generated internally. The memory map for the exception vectors is shown in the Table 22.

# P90CL301BFH (C100)

| Table 22 E | Exception | vector | assignment |

|------------|-----------|--------|------------|

|------------|-----------|--------|------------|

| VECTOR NO.              | DECIMAL     | HEX        | ASSIGNMENT                             |  |  |

|-------------------------|-------------|------------|----------------------------------------|--|--|

| 0                       | 0           | 000        | reset: initial SSP                     |  |  |

| _                       | 4           | 004        | reset: initial PC                      |  |  |

| 2                       | 8           | 008        | bus error                              |  |  |

| 3                       | 12          | 00C        | address error                          |  |  |

| 4                       | 16          | 010        | illegal instruction                    |  |  |

| 5                       | 20          | 014        | zero divide                            |  |  |

| 6                       | 24          | 018        | CHK instruction                        |  |  |

| 7                       | 28          | 01C        | TRAPV instruction                      |  |  |

| 8                       | 32          | 020        | privilege violation                    |  |  |

| 9                       | 36          | 024        | trace                                  |  |  |

| 10                      | 40          | 028        | line 1010 emulator                     |  |  |

| 11                      | 44          | 02C        | line 1111 emulator                     |  |  |

| 12 <sup>(1)</sup>       | 48          | 030        | unassigned, reserved                   |  |  |

| 13 <sup>(1)</sup>       | 52          | 034        | unassigned, reserved                   |  |  |

| 14                      | 56          | 038        | format error                           |  |  |

| 15                      | 60          | 03C        | uninitialized interrupt vector         |  |  |

| 16 to 23 <sup>(1)</sup> | 64 to 95    | 040 to 05C | unassigned, reserved                   |  |  |

| 24                      | 96          | 060        | spurious interrupt                     |  |  |

| 25                      | 100         | 064        | level 1 external interrupt auto-vector |  |  |

| 26                      | 104         | 068        | level 2 external interrupt auto-vector |  |  |

| 27                      | 108         | 06C        | level 3 external interrupt auto-vector |  |  |

| 28                      | 112         | 070        | level 4 external interrupt auto-vector |  |  |

| 29                      | 116         | 074        | level 5 external interrupt auto-vector |  |  |

| 30                      | 120         | 078        | level 6 external interrupt auto-vector |  |  |

| 31                      | 124         | 07C        | level 7 external interrupt auto-vector |  |  |

| 32 to 47                | 128 to 191  | 080 to 0BF | TRAP instruction vectors               |  |  |

| 48 to 56 <sup>(1)</sup> | 192 to 227  | 0C0 to 0E3 | reserved                               |  |  |

| 57                      | 228         | 0E4        | level 1 on-chip interrupt auto-vector  |  |  |

| 58                      | 232         | 0E8        | level 2 on-chip interrupt auto-vector  |  |  |

| 59                      | 236         | 0EC        | level 3 on-chip interrupt auto-vector  |  |  |

| 60                      | 240         | 0F0        | level 4 on-chip interrupt auto-vector  |  |  |

| 61                      | 244         | 0F4        | level 5 on-chip interrupt auto-vector  |  |  |

| 62                      | 248         | 0F8        | level 6 on-chip interrupt auto-vector  |  |  |

| 63                      | 252         | 0FC        | level 7 on-chip interrupt auto-vector  |  |  |

| 64 to 255               | 256 to 1023 | 100 to 3FF | reserved                               |  |  |

#### Note

1. Vectors 12, 13, 16 to 23 and 48 to 56 are reserved for future enhancements.

#### 7.3.3 INSTRUCTION TRAPS

Traps are exceptions caused by instructions arising from CPU recognition of abnormal conditions during instruction execution or from instructions whose normal behaviour is to cause traps.

Some instructions are used specifically to generate traps. The TRAP instruction always forces an exception and is useful for implementing system calls for User Programs. The TRAPV and CHK instructions force an exception if the User Program detects a run-time error, possibly an arithmetic overflow or a subscript out of bounds. The signed divide (DIVS) and unsigned divide (DIVU) instructions will force an exception if a divide-by-zero operation is attempted.

#### 7.3.4 ILLEGAL AND UNIMPLEMENTED INSTRUCTIONS

Illegal instruction is the term used to refer to any word that is not the first word of a legal instruction. During execution, if such an instruction is fetched an illegal exception occurs.

Words with bits 15 to 12 equal to '1010' or '1111' are defined as unimplemented instructions and separate exception vectors are allocated to these patterns for efficient emulation. This facility means the operating system can detect program errors, or can emulate unimplemented instructions in software.

#### 7.3.5 PRIVILEGE VIOLATIONS

To provide system security, various instructions are privileged and any attempt to execute one of the privileged instruction while the CPU is in the User state provokes an exception. The privileged instructions are:

- STOP

- RESET

- RTE

- MOVE to SR

- AND (word) immediate to SR

- EOR (word) immediate to SR

- OR (word) immediate to SR

- MOVE to USP.

### 7.4 Tracing

The CPU includes a facility to trace instructions one by one to assist in program development. In the trace state, after each instruction is executed, an exception is forced so that the debugging program can monitor execution of the program under test.

### P90CL301BFH (C100)

The trace facility uses the T-bit in the Supervisor part of the Status Register. If the T-bit is cleared, tracing is disabled and instructions are executed normally. If the T-bit is set at the beginning of the execution of an instruction, a trace exception will be generated once the instruction has been executed. If the instruction is not executed, either because of an interrupt, or because the instruction is illegal or privileged, the trace exception does also not occur if the instruction is aborted by a reset, bus error, or address error exception. If the instruction is processed before the interrupt. If the execution of an instruction forces an exception, the forced exception is processed before the trace exception.

As an extreme illustration of the above rules, consider the arrival of an interrupt during the execution of a TRAP instruction, while tracing is enabled. First the trap exception is processed, followed by the trace exception, and finally the interrupt handling routine.

### 7.5 Stack format

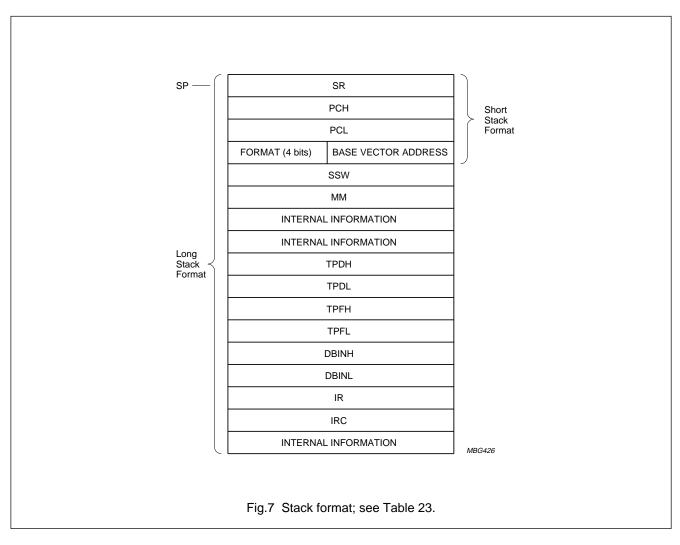

The stack format for exception processing is similar to the MC68010 although the instruction stored is not the same, due to the different architecture. To handle this format the P90CL301BFH differs from the MC68000 in that:

- The stack format is changed.

- The minimum number of words put into or restored from stack is 4 (MC68010 compatible, not 3 as with the MC68000).

- The RTE instruction decides (with the aid of the 4 format bits) whether or not more information has to be restored as follows:

- The P90CL301BFH long format is used for bus errors and address error exceptions.

- All other exceptions use the short format.

- If another format code, other than those listed above, is detected during the restored action, a FORMAT ERROR occurs.

If the user wants to finish the instruction in which the bus or address error occurred, the P90CL301BFH format must be used on RTE. If no changes to the stack are required during exception processing, the stack format is transparent to the user.

# P90CL301BFH (C100)

### Table 23 Description of the stack format

| SYMBOL                 | DESCRIPTION                                                                                                       |

|------------------------|-------------------------------------------------------------------------------------------------------------------|

| SR                     | Status Register.                                                                                                  |

| PCH/PCL                | Program Counter High/Low Word.                                                                                    |

| FORMAT                 | Indicating either a short stack (only the first four words), or the long for bus and address error exceptions.    |

| BASE VECTOR<br>ADDRESS | The base vector address of the exception in the vector table; e.g. 8 for a bus error and 12 for an address error. |

| SSW                    | Special Status Word.                                                                                              |

| MM                     | Current Move Multiple Mask.                                                                                       |

| TPDH/TPDL              | In the event of faulty write cycle, the data can be found here.                                                   |

| TPFH/TPFL              | The address used during the faulty bus cycle.                                                                     |

| DBINH/DBINL            | Data that has been read prior to the faulty bus cycle can in some cases be found here.                            |

| IR                     | Holds the present instruction executed.                                                                           |