# **PCF85133**

# Universal LCD driver for low multiplex rates

Rev. 1 — 17 February 2009

**Product data sheet**

## 1. General description

The PCF85133 is a peripheral device which interfaces to almost any Liquid Crystal Display (LCD) with low multiplex rates. It generates the drive signals for any static or multiplexed LCD containing up to four backplanes and up to 80 segments and can easily be cascaded for larger LCD applications. The PCF85133 is compatible with most microprocessors or microcontrollers and communicates via a two-line bidirectional I<sup>2</sup>C-bus. Communication overheads are minimized by a display RAM with auto-incremental addressing, by hardware subaddressing and by display memory switching (static and duplex drive modes).

#### 2. Features

- Single-chip LCD controller and driver

- Selectable backplane drive configuration: static or 2, 3 or 4 backplane multiplexing

- Selectable display bias configuration: static,  $\frac{1}{2}$  or  $\frac{1}{3}$

- Selectable frame frequency: 82 Hz or 110 Hz

- Internal LCD bias generation with voltage-follower buffers

- 80 segment drives:

- ◆ Up to 40 7-segment numeric characters

- ◆ Up to 21 14-segment alphanumeric characters

- Any graphics of up to 320 elements

- 80 × 4 bit RAM for display data storage

- Auto-incremental display data loading across device subaddress boundaries

- Display memory bank switching in static and duplex drive modes

- Versatile blinking modes

- Independent supplies possible for LCD and logic voltages

- Wide power supply range: from 1.8 V to 5.5 V

- Wide LCD supply range for low-threshold LCDs, for guest-host LCDs and high-threshold (automobile) twisted nematic LCDs: from 2.5 V to 6.5 V

- Low power consumption

- 400 kHz I<sup>2</sup>C-bus interface

- May be cascaded for large LCD applications (up to 5120 elements possible)

- May be cascaded with PCF8532 to gain more flexibility in the number of addressable segments

- No external components

- Compatible with Chip-On-Glass (COG) technology

- Manufactured using silicon gate CMOS process

#### Universal LCD driver for low multiplex rates

# 3. Ordering information

Table 1. Ordering information

| Type number     | Package  |                                            |                         |          |

|-----------------|----------|--------------------------------------------|-------------------------|----------|

|                 | Name     | Description                                | Delivery form[1]        | Version  |

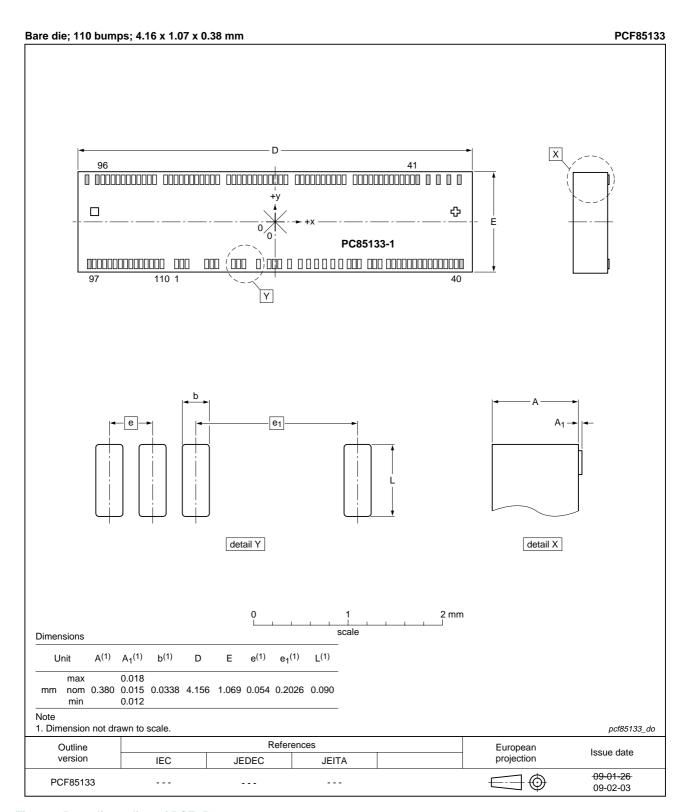

| PCF85133U/2DA/1 | PCF85133 | bare die; 110 bumps; 4.16 × 1.07 × 0.38 mm | chip with bumps in tray | PCF85133 |

<sup>[1]</sup> Bump hardness see Table 20.

# 4. Marking

Table 2. Marking codes

| Type number     | Marking code |

|-----------------|--------------|

| PCF85133U/2DA/1 | PC85133-1    |

# 5. Block diagram

#### Universal LCD driver for low multiplex rates

# 6. Pinning information

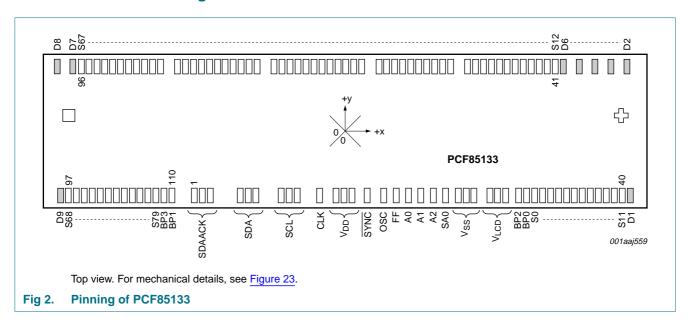

### 6.1 Pinning

# 6.2 Pin description

Table 3. Pin description overview

| •                     |                     |                                          |

|-----------------------|---------------------|------------------------------------------|

| Symbol                | Pin                 | Description                              |

| SDAACK                | 1 to 3              | I <sup>2</sup> C-bus acknowledge output  |

| SDA                   | 4 to 6              | I <sup>2</sup> C-bus serial data input   |

| SCL                   | 7 to 9              | I <sup>2</sup> C-bus serial clock input  |

| CLK                   | 10                  | clock input/output                       |

| $V_{DD}$              | 11 to 13            | supply voltage                           |

| SYNC                  | 14                  | cascade synchronization input/output     |

| OSC                   | 15                  | oscillator select                        |

| FF                    | 16                  | frame frequency select                   |

| A0, A1 and A2         | 17 to 19            | subaddress input                         |

| SA0                   | 20                  | I <sup>2</sup> C-bus slave address input |

| V <sub>SS</sub>       | 21 to 23            | ground supply voltage                    |

| V <sub>LCD</sub>      | 24 to 26            | LCD supply voltage                       |

| BP2, BP0, BP3 and BP1 | 27, 28, 109 and 110 | LCD backplane output                     |

| S0 to S79             | 29 to 108           | LCD segment output                       |

| D1 to D9              | -                   | dummy pads                               |

|                       |                     |                                          |

3 of 41

#### Universal LCD driver for low multiplex rates

# 7. Functional description

The PCF85133 is a versatile peripheral device designed to interface between any microprocessor or microcontroller to a wide variety of LCDs. It can directly drive any static or multiplexed LCD containing up to four backplanes and up to 80 segments.

The display configurations possible with the PCF85133 depend on the required number of active backplane outputs. A selection of display configurations is shown in Table 4.

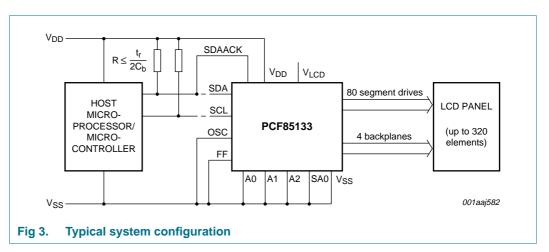

All of the display configurations can be implemented in a typical system as shown in Figure 3.

Table 4. Possible display configurations

| Number of  |          | 7-segment numeric |                   | 14-segment | Dot matrix        |              |

|------------|----------|-------------------|-------------------|------------|-------------------|--------------|

| Backplanes | Elements | Digits            | Indicator symbols | Characters | Indicator symbols |              |

| 4          | 320      | 40                | 40                | 20         | 40                | 320 (4 × 80) |

| 3          | 240      | 30                | 30                | 16         | 16                | 240 (3 × 80) |

| 2          | 160      | 20                | 20                | 10         | 20                | 160 (2 × 80) |

| 1          | 80       | 10                | 10                | 5          | 10                | 80 (1 × 80)  |

The host microprocessor or microcontroller maintains the 2-line I<sup>2</sup>C-bus communication channel with the PCF85133.

The internal oscillator is selected by connecting pin OSC to  $V_{SS}$ . The only other connections required to complete the system are the power supplies ( $V_{DD}$ ,  $V_{SS}$  and  $V_{LCD}$ ) and the LCD panel selected for the application.

#### Universal LCD driver for low multiplex rates

#### 7.1 Power-on reset

At power-on the PCF85133 resets to the following starting conditions:

- All backplane and segment outputs are set to V<sub>LCD</sub>

- The selected drive mode is 1:4 multiplex with \(^{1}\)\_3 bias

- · Blinking is switched off

- · Input and output bank selectors are reset

- The I<sup>2</sup>C-bus interface is initialized

- The data pointer and the subaddress counter are cleared (set to logic 0)

- The display is disabled

**Remark:** Do not transfer data on the I<sup>2</sup>C-bus for at least 1 ms after a power-on to allow the reset action to complete.

#### 7.2 LCD bias generator

Fractional LCD biasing voltages are obtained from an internal voltage divider of three series resistors between  $V_{LCD}$  and  $V_{SS}$ . The center resistor can be bypassed to provide a  $\frac{1}{2}$  bias voltage level for the 1:2 multiplex configuration.

#### 7.3 LCD voltage selector

The LCD voltage selector coordinates the multiplexing of the LCD in accordance with the selected LCD drive configuration. The operation of the voltage selector is controlled by mode-set commands from the command decoder. The biasing configurations that apply to the preferred modes of operation, together with the biasing characteristics as functions of  $V_{LCD}$  and the resulting discrimination ratios (D), are given in Table 5.

Table 5. Discrimination ratios

| LCD drive mode |            |        | LCD bias      | $V_{off(RMS)}$   | $V_{on(RMS)}$    | $D = \frac{V_{on(RMS)}}{}$               |

|----------------|------------|--------|---------------|------------------|------------------|------------------------------------------|

|                | Backplanes | Levels | configuration | V <sub>LCD</sub> | V <sub>LCD</sub> | $D = \frac{\delta n(RMS)}{V_{off}(RMS)}$ |

| static         | 1          | 2      | static        | 0                | 1                | ∞                                        |

| 1:2 multiplex  | 2          | 3      | 1/2           | 0.354            | 0.791            | 2.236                                    |

| 1:2 multiplex  | 2          | 4      | 1/3           | 0.333            | 0.745            | 2.236                                    |

| 1:3 multiplex  | 3          | 4      | 1/3           | 0.333            | 0.638            | 1.915                                    |

| 1:4 multiplex  | 4          | 4      | 1/3           | 0.333            | 0.577            | 1.732                                    |

A practical value for  $V_{LCD}$  is determined by equating  $V_{off(RMS)}$  with a defined LCD threshold voltage ( $V_{th}$ ), typically when the LCD exhibits approximately 10 % contrast. In the static drive mode a suitable choice is  $V_{LCD} > 3V_{th}$ .

Multiplex drive modes of 1:3 and 1:4 with  $\frac{1}{2}$  bias are possible but the discrimination and hence the contrast ratios are smaller.

Bias is calculated by  $\frac{1}{1+a}$ , where the values for a are

$$a = 1$$

for  $\frac{1}{2}$  bias

$$a = 2$$

for  $\frac{1}{3}$  bias

#### Universal LCD driver for low multiplex rates

The RMS on-state voltage (Von(RMS)) for the LCD is calculated with the equation

$$V_{on(RMS)} = \sqrt[V_{LCD}]{\frac{1}{n} + \left[ (n-1) \times \left( \frac{1}{1+a} \right) \right]^2}$$

(1)

where V<sub>LCD</sub> is the resultant voltage at the LCD segment and where the values for n are

n = 1 for static mode

n = 2 for 1:2 multiplex

n = 3 for 1:3 multiplex

n = 4 for 1:4 multiplex

The RMS off-state voltage (Voff(RMS)) for the LCD is calculated with the equation:

$$V_{off(RMS)} = V_{LCD} \sqrt{\frac{a^2 - (2a+n)}{n \times (1+a)^2}}$$

(2)

Discrimination is the ratio of  $V_{on(RMS)}$  to  $V_{off(RMS)}$  and is determined from the equation:

$$\frac{V_{on(RMS)}}{V_{off(RMS)}} = \sqrt{\frac{(a+1)^2 + (n-1)}{(a-1)^2 + (n-1)}}$$

(3)

Using Equation 3, the discrimination for an LCD drive mode of

- 1:3 multiplex with  $\frac{1}{2}$  bias is  $\sqrt{3} = 1.732$

- 1:4 multiplex with  $\frac{1}{2}$  bias is  $\frac{\sqrt{21}}{3} = 1.528$

The advantage of these LCD drive modes is a reduction of the LCD full scale voltage V<sub>LCD</sub> as follows:

- 1:3 multiplex ( $\frac{1}{2}$  bias):  $V_{LCD} = \sqrt{6} \times V_{off(RMS)} = 2.449 V_{off(RMS)}$

- 1:4 multiplex (½ bias):  $V_{LCD} = \left[\frac{(4 \times \sqrt{3})}{3}\right] = 2.309 V_{off(RMS)}$

These compare with  $V_{LCD} = 3V_{off(RMS)}$  when  $\frac{1}{3}$  bias is used.

It should be noted that  $V_{\text{LCD}}$  is sometimes referred as the LCD operating voltage.

#### Universal LCD driver for low multiplex rates

#### 7.4 LCD drive mode waveforms

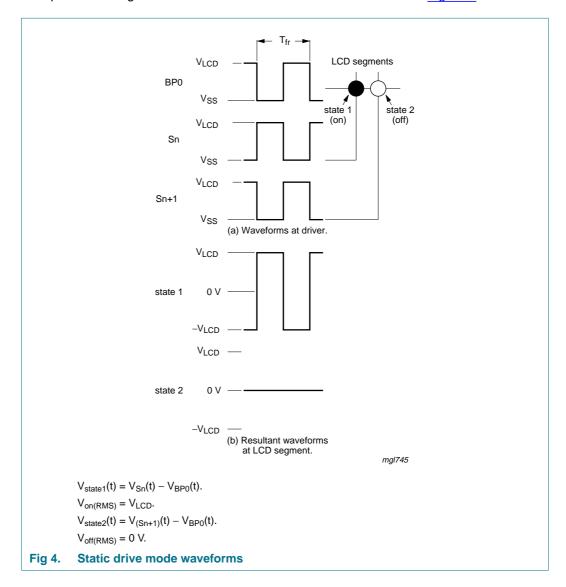

## 7.4.1 Static drive mode

The static LCD drive mode is used when a single backplane is provided in the LCD. Backplane and segment drive waveforms for this mode are shown in Figure 4.

#### Universal LCD driver for low multiplex rates

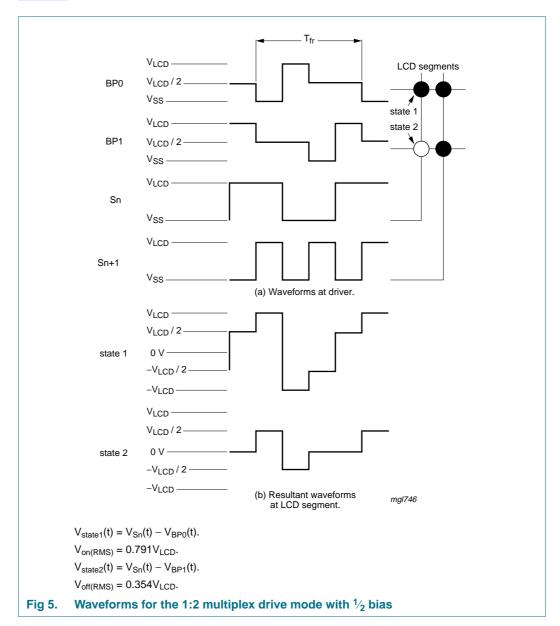

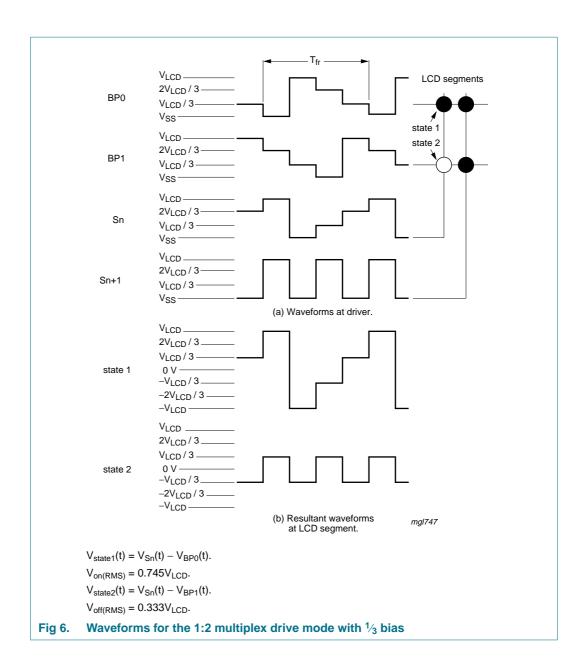

# 7.4.2 1:2 multiplex drive mode

When two backplanes are provided in the LCD, the 1:2 multiplex mode applies. The PCF85133 allows the use of  $\frac{1}{2}$  bias or  $\frac{1}{3}$  bias in this mode as shown in Figure 5 and Figure 6.

#### Universal LCD driver for low multiplex rates

#### Universal LCD driver for low multiplex rates

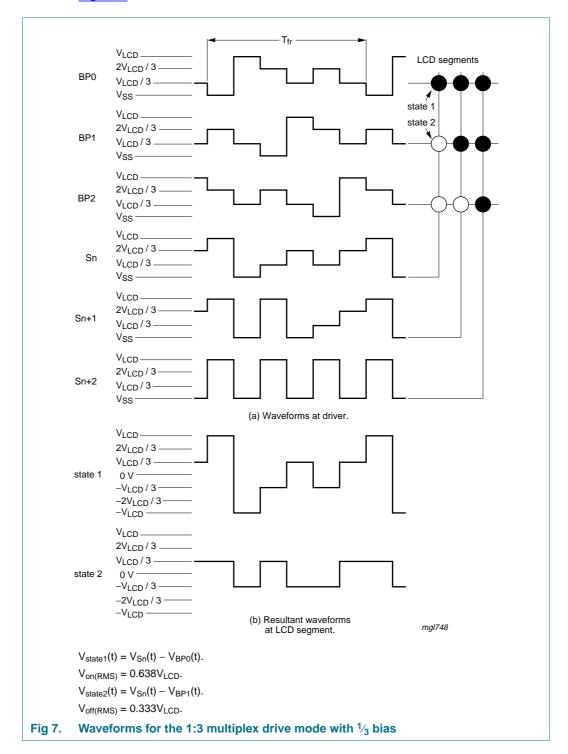

## 7.4.3 1:3 multiplex drive mode

When three backplanes are provided in the LCD, the 1:3 multiplex drive mode applies as shown in Figure 7.

#### Universal LCD driver for low multiplex rates

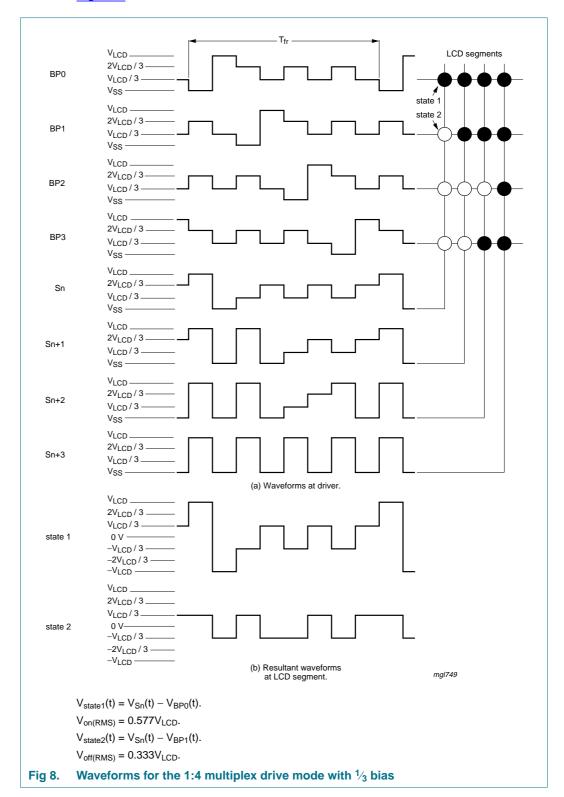

# 7.4.4 1:4 multiplex drive mode

When four backplanes are provided in the LCD, the 1:4 multiplex drive mode applies as shown in Figure 8.

#### Universal LCD driver for low multiplex rates

#### 7.5 Oscillator

The internal logic and the LCD drive signals of the PCF85133 are timed by a frequency  $f_{clk}$  which either is derived from the built-in oscillator frequency  $f_{osc}$ :

$$f_{clk} = \frac{f_{osc}}{64} \tag{4}$$

or equals an external clock frequency f<sub>clk(ext)</sub>:

$$f_{clk} = f_{clk(ext)} \tag{5}$$

#### 7.5.1 Internal clock

The internal oscillator is enabled by connecting pin OSC to  $V_{SS}$ . In this case the output from pin CLK provides the clock signal for cascaded PCF85133s in the system. After power-up, pin SDA must be HIGH to guarantee that the clock starts.

#### 7.5.2 External clock

Connecting pin OSC to  $V_{DD}$  enables an external clock source. Pin CLK then becomes the external clock input.

A clock signal must always be supplied to the device; removing the clock may freeze the LCD in a DC state.

## 7.6 Timing

The clock frequency  $f_{clk}$  determines the LCD frame frequency  $f_{fr}$  and is calculated as follows:

$$f_{fr} = \frac{f_{clk}}{24} \tag{6}$$

The internal clock frequency  $f_{clk}$  can be selected using pin FF. As a result 2 frame frequencies are available: 82 Hz or 110 Hz (typical), see <u>Table 6</u>.

Table 6. LCD frame frequencies

| Pin FF tied to  | Typical clock frequency (Hz) | LCD frame frequency (Hz) |

|-----------------|------------------------------|--------------------------|

| $V_{DD}$        | 1970                         | 82                       |

| V <sub>SS</sub> | 2640                         | 110                      |

The timing of the PCF85133 organizes the internal data flow of the device. This includes the transfer of display data from the display RAM to the display segment outputs. In cascaded applications, the synchronization signal (SYNC) maintains the correct timing relationship between all the PCF85133s in the system.

## 7.7 Display register

The display register holds the display data while the corresponding multiplex signals are generated. There is a one-to-one relationship between the data in the display register, the LCD segment outputs and one column of the display RAM.

#### Universal LCD driver for low multiplex rates

### 7.8 Segment outputs

The LCD drive section includes 80 segment outputs (S0 to S79) which must be connected directly to the LCD. The segment output signals are generated in accordance with the multiplexed backplane signals and with data residing in the display register. When less than 80 segment outputs are required the unused segment outputs must be left open-circuit.

#### 7.9 Backplane outputs

The LCD drive section includes four backplane outputs: BP0 to BP3. The backplane output signals are generated in accordance with the selected LCD drive mode.

In the 1:4 multiplex drive mode BP0 to BP3 must be connected directly to the LCD.

If less than four backplane outputs are required the unused outputs can be left open-circuit.

- In 1:3 multiplex drive mode BP3 carries the same signal as BP1, therefore these two adjacent outputs can be tied together to give enhanced drive capabilities.

- In 1:2 multiplex drive mode BP0 and BP2, BP1 and BP3 respectively carry the same signals and may also be paired to increase the drive capabilities.

- In static drive mode the same signal is carried by all four backplane outputs and they can be connected in parallel for very high drive requirements.

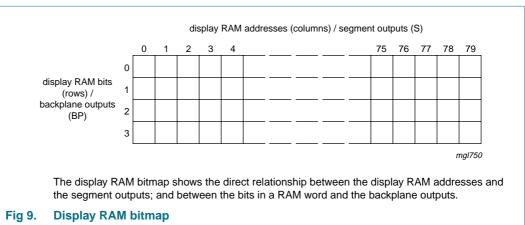

## 7.10 Display RAM

The display RAM is a static  $80 \times 4$  bit RAM which stores LCD data. A logic 1 in the RAM bit map indicates the on-state of the corresponding LCD element; similarly, a logic 0 indicates the off state. There is a one-to-one correspondence between the RAM addresses and the segment outputs and between the individual bits of a RAM word and the backplane outputs. The display RAM bit map Figure 9 shows rows 0 to 3 which correspond with the backplane outputs BP0 to BP3, and columns 0 to 79 which correspond with the segment outputs S0 to S79. In multiplexed LCD applications the segment data of the first, second, third and fourth row of the display RAM are time-multiplexed with BP0, BP1, BP2 and BP3 respectively.

When display data is transmitted to the PCF85133 the received display bytes are stored in the display RAM in accordance with the selected LCD drive mode. The data is stored as it arrives and does not wait for the acknowledge cycle as with the commands. Depending on the current multiplex drive mode, data is stored singularly, in pairs, triplets or quadruplets. To illustrate the filling order, an example of a 7-segment numeric display showing all drive modes is given in <a href="Figure 10">Figure 10</a>; the RAM filling organization depicted applies equally to other LCD types.

The following applies to Figure 10:

• In static drive mode the eight transmitted data bits are placed into row 0 of eight successive 4-bit RAM words.

13 of 41

In 1:2 multiplex mode the eight transmitted data bits are placed in pairs into row 0 and 1 of four successive 4-bit RAM words.

#### Universal LCD driver for low multiplex rates

• In 1:3 multiplex mode the eight bits are placed in triples into row 0, 1 and 2 of three successive 4-bit RAM words, with bit 3 of the third address left unchanged. It is not recommended to use this bit in a display because of the difficult addressing. This last bit may, if necessary, be controlled by an additional transfer to this address but care should be taken to avoid overwriting adjacent data because always full bytes are transmitted.

• In the 1:4 multiplex mode the eight transmitted data bits are placed in quadruples into row 0, 1, 2 and 3 of two successive 4-bit RAM words.

# 7.11 Data pointer

The addressing mechanism for the display RAM is realized using a data pointer.

This allows the loading of an individual display data byte, or a series of display data bytes, into any location of the display RAM. The sequence commences with the initialization of the data pointer by the load-data-pointer command.

Following this command, an arriving data byte is stored at the display RAM address indicated by the data pointer. The filling order is shown in Figure 10.

After each byte is stored, the content of the data pointer is automatically incremented by a value dependent on the selected LCD drive mode:

- In static drive mode by eight

- In 1:2 multiplex drive mode by four

- In 1:3 multiplex drive mode by three

- In 1:4 multiplex drive mode by two

If an I<sup>2</sup>C-bus data access is terminated early then the state of the data pointer is unknown. The data pointer must be re-written prior to further RAM accesses.

| drive mode       | LCD segments                                                                                                                                    | LCD backplanes | display RAM filling order                                                                                                                                                                                                                                                                                                                              | transmitted display byte  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                  | S <sub>n+2</sub> a                                                                                                                              |                | display RAM addresses (columns)/segment outputs (S) byte1                                                                                                                                                                                                                                                                                              |                           |

| static           | S <sub>n+3</sub> - f b - S <sub>n+1</sub> S <sub>n+4</sub> - g - S <sub>n</sub> S <sub>n+5</sub> - e c S <sub>n+7</sub> S <sub>n+6</sub> - d DP | вро            | display RAM 0 c b a f g e d DP bits (rows)/ 1 x x x x x x x x x x x x x x x x x x                                                                                                                                                                                                                                                                      | MSB LSB                   |

| 1:2<br>multiplex | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                            | BP0  BP1       | display RAM addresses (columns)/segment outputs (S)           byte1         byte2           n         n + 1         n + 2         n + 3           display RAM 0         a         f         e         d           bits (rows)/ 1         b         g         c         DP           backplane 2 outputs (BP) 3         x         x         x         x | MSB LSB                   |

| 1:3<br>multiplex | S <sub>n+1</sub> — a b S <sub>n</sub> S <sub>n+2</sub> — f DP                                                                                   | BP0  BP1  BP2  | display RAM addresses (columns)/segment outputs (S)   byte1   byte2   byte3                                                                                                                                                                                                                                                                            | MSB LSB                   |

| 1:4<br>multiplex | S <sub>n</sub> a b g g c c DP                                                                                                                   | BP1 BP3        | display RAM addresses (columns)/segment outputs (S)   byte1   byte2   byte3   byte4   byte5                                                                                                                                                                                                                                                            | MSB LSB  a c b DP f e g d |

x = data bit unchanged

Fig 10. Relationships between LCD layout, drive mode, display RAM filling order and display data transmitted over the I<sup>2</sup>C-bus

PCF85133\_1

Product data sheet

Rev. 1 — 17 February 2009

#### Universal LCD driver for low multiplex rates

#### 7.12 Subaddress counter

The storage of display data is conditioned by the content of the subaddress counter. Storage is allowed only when the content of the subaddress counter match with the hardware subaddress applied to A0, A1 and A2. The subaddress counter value is defined by the device-select command (see <u>Table 12</u>). If the content of the subaddress counter and the hardware subaddress do not match then data storage is inhibited but the data pointer is incremented as if data storage had taken place. The subaddress counter is also incremented when the data pointer overflows.

The storage arrangements described lead to extremely efficient data loading in cascaded applications. When a series of display bytes are sent to the display RAM, automatic wrap-over to the next PCF85133 occurs when the last RAM address is exceeded. Subaddressing across device boundaries is successful even if the change to the next device in the cascade occurs within a transmitted character (such as during the 27th display data byte transmitted in 1:3 multiplex mode).

The hardware subaddress must not be changed whilst the device is being accessed on the I<sup>2</sup>C-bus interface.

## 7.13 Output bank selector

The output bank selector selects one of the four rows per display RAM address for transfer to the display register. The actual row selected depends on the particular LCD drive mode in operation and on the instant in the multiplex sequence.

- In 1:4 multiplex mode, all RAM addresses of row 0 are selected, these are followed by the contents of row 1, row 2 and then row 3

- In 1:3 multiplex mode, rows 0, 1 and 2 are selected sequentially

- In 1:2 multiplex mode, rows 0 and 1 are selected

- In static mode, row 0 is selected

The PCF85133 includes a RAM bank switching feature in the static and 1:2 multiplex drive modes. In the static drive mode, the bank-select command may request the contents of row 2 to be selected for display instead of the contents of row 0. In the 1:2 mode, the contents of rows 2 and 3 may be selected instead of rows 0 and 1. This gives the provision for preparing display information in an alternative bank and to be able to switch to it once it is assembled.

#### 7.14 Input bank selector

The input bank selector loads display data into the display RAM in accordance with the selected LCD drive configuration. Display data can be loaded in row 2 in static drive mode or in rows 2 and 3 in 1:2 multiplex drive mode by using the bank-select command. The input bank selector functions independently to the output bank selector.

#### 7.15 Blinker

The display blinking capabilities of the PCF85133 are very versatile. The whole display can blink at frequencies selected by the blink-select command (see <u>Table 14</u>). The blink frequencies are fractions of the clock frequency. The ratios between the clock and blink frequencies depend on the blink mode in which the device is operating (see <u>Table 7</u>).

#### Universal LCD driver for low multiplex rates

| Blink mode | Operating mode ratio   | Blink frequency wit          | th respect to f <sub>clk</sub> (typical) | Unit |  |

|------------|------------------------|------------------------------|------------------------------------------|------|--|

|            |                        | f <sub>clk</sub> = 1.970 kHz | f <sub>clk</sub> = 2.640 kHz             |      |  |

| off        | -                      | blinking off                 | blinking off                             | Hz   |  |

| 1          | $\frac{f_{clk}}{768}$  | 2.5                          | 3.5                                      | Hz   |  |

| 2          | $\frac{f_{clk}}{1536}$ | 1.3                          | 1.7                                      | Hz   |  |

| 3          | $\frac{f_{clk}}{3072}$ | 0.6                          | 0.9                                      | Hz   |  |

Table 7. Blink frequencies

An additional feature is for an arbitrary selection of LCD segments to blink. This applies to the static and 1:2 multiplex drive modes and can be implemented without any communication overheads. By means of the output bank selector, the displayed RAM banks are exchanged with alternate RAM banks at the blink frequency. This mode can also be specified by the blink-select command.

In the 1:3 and 1:4 multiplex modes, where no alternate RAM bank is available, groups of LCD segments can blink by selectively changing the display RAM data at fixed time intervals.

If the entire display can blink at a frequency other than the typical blink frequency. This can be effectively performed by resetting and setting the display enable bit E at the required rate using the mode-set command (see <u>Table 10</u>).

#### 7.16 Characteristics of the I<sup>2</sup>C-bus

The  $I^2C$ -bus is for bidirectional, two-line communication between different ICs or modules. The two lines are a Serial Data line (SDA) and a Serial Clock Line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

By connecting pin SDAACK to pin SDA on the PCF85133, the SDA line becomes fully I²C-bus compatible. Having the acknowledge output separated from the serial data line is advantageous in Chip-On-Glass (COG) applications¹. In COG applications where the track resistance from the SDAACK pin to the system SDA line can be significant, possibly a voltage divider is generated by the bus pull-up resistor and the Indium Tin Oxide (ITO) track resistance. It is possible that during the acknowledge cycle the PCF85133 will not be able to create a valid logic 0 level. By splitting the SDA input from the output the device could be used in a mode that ignores the acknowledge bit. In COG applications where the acknowledge cycle is required, it is necessary to minimize the track resistance from the SDAACK pin to the system SDA line to guarantee a valid LOW level.

The following definition assumes SDA and SDAACK are connected and refers to the pair as SDA.

CF85133\_1 © NXP B.V. 2009. All rights reserved.

For further information, please consider the NXP application note: AN10170, Design guidelines for COG modules with NXP monochrome LCD drivers.

#### Universal LCD driver for low multiplex rates

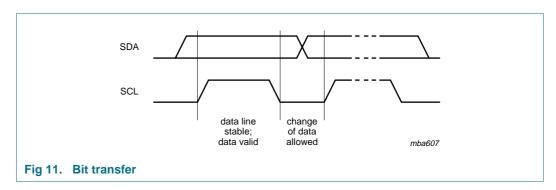

#### 7.16.1 Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as a control signal (see Figure 11).

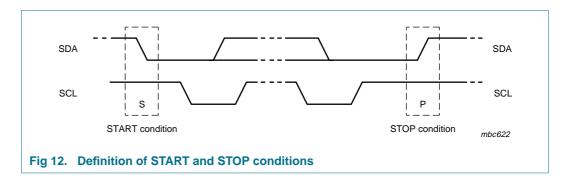

#### 7.16.1.1 START and STOP conditions

Both data and clock lines remain HIGH when the bus is not busy.

A HIGH-to-LOW change of the data line, while the clock is HIGH is defined as the START condition (S).

A LOW-to-HIGH change of the data line while the clock is HIGH is defined as the STOP condition (P).

The START and STOP conditions are shown in Figure 12.

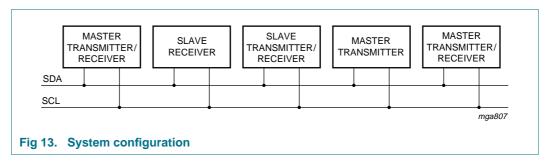

#### 7.16.2 System configuration

A device generating a message is a transmitter, a device receiving a message is the receiver. The device that controls the message is the master and the devices which are controlled by the master are the slaves. The system configuration is shown in Figure 13.

PCF85133\_1 © NXP B.V. 2009. All rights reserved.

#### Universal LCD driver for low multiplex rates

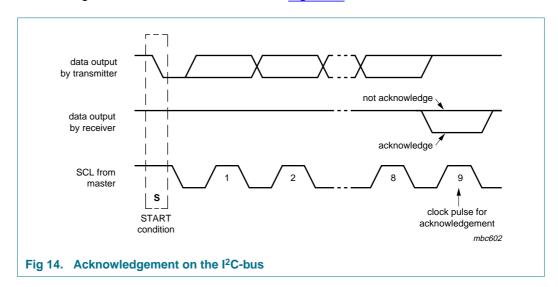

#### 7.16.3 Acknowledge

The number of data bytes transferred between the START and STOP conditions from transmitter to receiver is unlimited. Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH level signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse.

- A slave receiver which is addressed must generate an acknowledge after the reception of each byte.

- Also a master receiver must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter.

- The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse (set-up and hold times must be taken into consideration).

- A master receiver must signal an end of data to the transmitter by not generating an

acknowledge on the last byte that has been clocked out of the slave. In this event the

transmitter must leave the data line HIGH to enable the master to generate a STOP

condition.

Acknowledgement on the I<sup>2</sup>C-bus is shown in Figure 14.

#### 7.16.4 I<sup>2</sup>C-bus controller

The PCF85133 acts as an  $I^2$ C-bus slave receiver. It does not initiate  $I^2$ C-bus transfers or transmit data to an  $I^2$ C-bus master receiver. The only data output from the PCF85133 are the acknowledge signals from the selected devices. Device selection depends on the  $I^2$ C-bus slave address, on the transferred command data and on the hardware subaddress.

In a single device application, the hardware subaddress inputs A0, A1 and A2 are normally tied to  $V_{SS}$  which defines the hardware subaddress 0. In multiple device applications A0, A1 and A2 are tied to  $V_{SS}$  or  $V_{DD}$  in accordance with a binary coding scheme such that no two devices with a common  $I^2C$ -bus slave address have the same hardware subaddress.

#### Universal LCD driver for low multiplex rates

#### 7.16.5 Input filters

To enhance noise immunity in electrically adverse environments, RC low-pass filters are provided on the SDA and SCL lines.

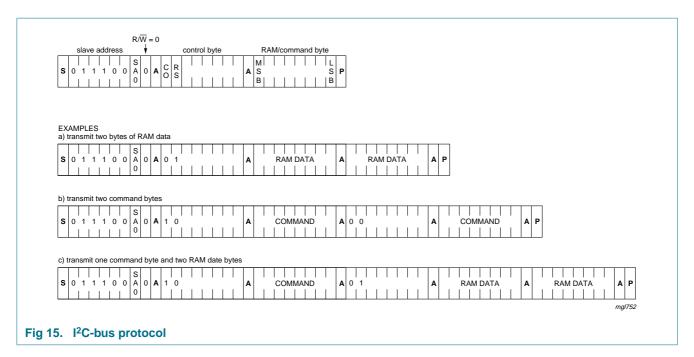

## 7.16.6 I<sup>2</sup>C-bus protocol

Two I $^2$ C-bus slave addresses (0111 000 and 0111 001) are reserved for the PCF85133. The least significant bit of the slave address is bit R/ $\overline{W}$ . The PCF85133 is a write-only device and will not respond to a read access, so this bit should always be logic 0. The second bit of the slave address is defined by the level tied at input SA0. Two types of PCF85133 can be distinguished on the same I $^2$ C-bus which allows:

- Up to 16 PCF85133s on the same I<sup>2</sup>C-bus for very large LCD applications

- The use of two types of LCD multiplex on the same I2C-bus

The  $I^2C$ -bus protocol is shown in <u>Figure 15</u>. The sequence is initiated with a START condition (S) from the  $I^2C$ -bus master which is followed by one of two possible PCF85133 slave addresses available. All PCF85133s with the corresponding SA0 level acknowledge in parallel to the slave address, but all PCF85133 with the alternative SA0 level ignore the whole  $I^2C$ -bus transfer.

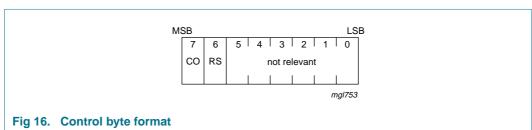

After acknowledgement, a control byte follows which defines if the next byte is RAM or command information. The control byte also defines if the next byte is a control byte or further RAM or command data.

In this way it is possible to configure the device and then fill the display RAM with little overhead.

The command bytes and control bytes are also acknowledged by all addressed PCF85133s connected to the bus.

The display bytes are stored in the display RAM at the address specified by the data pointer and the subaddress counter; see Section 7.11 and Section 7.12.

The acknowledgement after each byte is made only by the (A0, A1 and A2) addressed PCF85133. After the last (display) byte, the I<sup>2</sup>C-bus master issues a STOP condition (P). Alternatively a START may be asserted to RESTART an I<sup>2</sup>C-bus access.

#### Universal LCD driver for low multiplex rates

Table 8. Load-data-pointer command bit description

| Bit    | Symbol | Value | Description            |

|--------|--------|-------|------------------------|

| 7      | CO     |       | continue bit           |

|        |        | 0     | last control byte      |

|        |        | 1     | control bytes continue |

| 6      | RS     |       | register selection     |

|        |        | 0     | command register       |

|        |        | 1     | data register          |

| 5 to 0 | -      |       | not relevant           |

#### Universal LCD driver for low multiplex rates

#### 7.17 Command decoder

The command decoder identifies command bytes that arrive on the  $I^2C$ -bus. The commands available to the PCF85133 are defined in Table 9.

Table 9. Definition of commands

| Command           | Ope | Operation code |    |    |    |    | Reference |     |          |

|-------------------|-----|----------------|----|----|----|----|-----------|-----|----------|

| mode-set          | 1   | 1              | 0  | 0  | Е  | В  | M1        | MO  | Table 10 |

| load-data-pointer | 0   | P6             | P5 | P4 | P3 | P2 | P1        | P0  | Table 11 |

| device-select     | 1   | 1              | 1  | 0  | 0  | A2 | A1        | A0  | Table 12 |

| bank-select       | 1   | 1              | 1  | 1  | 1  | 0  | I         | 0   | Table 13 |

| blink-select      | 1   | 1              | 1  | 1  | 0  | Α  | BF1       | BF0 | Table 14 |

Table 10. Mode-set command bit description

| Bit    | Symbol | Value | Description                 |  |  |  |  |

|--------|--------|-------|-----------------------------|--|--|--|--|

| 7 to 4 | -      | 1100  | fixed value                 |  |  |  |  |

| 3      | Е      |       | display status[1]           |  |  |  |  |

|        |        | 0     | disabled (blank)            |  |  |  |  |

|        |        | 1     | enabled                     |  |  |  |  |

| 2      | В      |       | LCD bias configuration      |  |  |  |  |

|        |        | 0     | $\frac{1}{3}$ bias          |  |  |  |  |

|        |        | 1     | $\frac{1}{2}$ bias          |  |  |  |  |

| 1 to 0 | M[1:0] |       | LCD drive mode selection    |  |  |  |  |

|        |        | 01    | static; 1 backplane         |  |  |  |  |

|        |        | 10    | 1:2 multiplex; 2 backplanes |  |  |  |  |

|        |        | 11    | 1:3 multiplex; 3 backplanes |  |  |  |  |

|        |        | 00    | 1:4 multiplex; 4 backplanes |  |  |  |  |

|        |        |       |                             |  |  |  |  |

<sup>[1]</sup> The possibility to disable the display allows implementation of blinking under external control.

Table 11. Load-data-pointer command bit description See Section 7.11.

| Bit    | Symbol | Value      | Description                                                                                              |

|--------|--------|------------|----------------------------------------------------------------------------------------------------------|

| 7      | -      | 0          | fixed value                                                                                              |

| 6 to 0 | P[6:0] | 0000000 to | immediate data                                                                                           |

|        |        | 0111011    | 7-bit binary value of 0 to 79, transferred to the data pointer to define one of 80 display RAM addresses |

Table 12. Device-select command bit description See Section 7.12.

| Bit    | Symbol | Value      | Description                                                                                                                  |

|--------|--------|------------|------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | -      | 11100      | fixed value                                                                                                                  |

| 2 to 0 | A[2:0] | 000 to 111 | immediate data  3-bit binary value of 0 to 7, transferred to the subaddress counter to define one of 8 hardware subaddresses |

#### Universal LCD driver for low multiplex rates

Table 13. Bank-select command bit description[1]

See Section 7.10, Section 7.11, Section 7.12, Section 7.13 and Section 7.14.

| Bit    | it Symbol | Value  | Description                                            |                     |  |  |

|--------|-----------|--------|--------------------------------------------------------|---------------------|--|--|

|        |           |        | Static                                                 | 1:2 multiplex       |  |  |

| 7 to 2 | -         | 111110 | fixed value                                            |                     |  |  |

| 1      | I         |        | Input bank selection: storage of arriving display data |                     |  |  |

|        | 0         | 0      | RAM bit 0                                              | RAM bits 0 and 1    |  |  |

|        |           | 1      | RAM bit 2                                              | RAM bits 2 and 3    |  |  |

| 0      | 0         |        | Output bank selection: retrieval of                    | of LCD display data |  |  |

|        |           |        | RAM bit 0                                              | RAM bits 0 and 1    |  |  |

|        |           | 1      | RAM bit 2                                              | RAM bits 2 and 3    |  |  |

<sup>[1]</sup> The bank-select command has no effect in 1:3 or 1:4 multiplex drive modes.

Table 14. Blink-select command bit description See Section 7.15.

| Bit    | Symbol  | Value | Description                               |

|--------|---------|-------|-------------------------------------------|

| 7 to 3 | -       | 11110 | fixed value                               |

| 2      | Α       |       | blink mode selection[1]                   |

|        |         | 0     | normal blinking                           |

|        |         | 1     | blinking by alternating display RAM banks |

| 1 to 0 | BF[1:0] |       | blink mode selection[2]                   |

|        |         | 00    | off                                       |

|        |         | 01    | 1                                         |

|        |         | 10    | 2                                         |

|        |         | 11    | 3                                         |

<sup>[1]</sup> Normal blinking is assumed when the LCD multiplex drive modes 1:3 or 1:4 are selected.

# 7.18 Display controller

The display controller executes the commands identified by the command decoder. It contains the device's status registers and co-ordinates their effects. The display controller is also responsible for loading display data into the display RAM as required by the filling order.

<sup>[2]</sup> For the blink frequencies see Table 7.

# Universal LCD driver for low multiplex rates

# 8. Internal circuitry

#### Universal LCD driver for low multiplex rates

# 9. Limiting values

#### **CAUTION**

Static voltages across the liquid crystal display can build up when the LCD supply voltage  $(V_{LCD})$  is on while the IC supply voltage  $(V_{DD})$  is off, or vice versa. This may cause unwanted display artifacts. To avoid such artifacts,  $V_{LCD}$  and  $V_{DD}$  must be applied or removed together.

Table 15. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol            | Parameter                       | Conditions                       |            | Min  | Max   | Unit |

|-------------------|---------------------------------|----------------------------------|------------|------|-------|------|

| $V_{DD}$          | supply voltage                  |                                  |            | -0.5 | +6.5  | V    |

| $V_{LCD}$         | LCD supply voltage              |                                  |            | -0.5 | +9.0  | V    |

| V <sub>i(n)</sub> | voltage on any input            | V <sub>DD</sub> related inputs   |            | -0.5 | +6.5  | V    |

| V <sub>o(n)</sub> | voltage on any output           | V <sub>LCD</sub> related outputs |            | -0.5 | +9.0  | V    |

| I <sub>I</sub>    | input current                   |                                  |            | -10  | +10   | mA   |

| I <sub>O</sub>    | output current                  |                                  |            | -10  | +10   | mA   |

| I <sub>DD</sub>   | supply current                  |                                  |            | -50  | +50   | mA   |

| $I_{SS}$          | ground supply current           |                                  |            | -50  | +50   | mA   |

| $I_{DD(LCD)}$     | LCD supply current              |                                  |            | -50  | +50   | mA   |

| P <sub>tot</sub>  | total power dissipation         |                                  |            | -    | 400   | mW   |

| P/out             | power dissipation per output    |                                  |            | -    | 100   | mW   |

| V <sub>esd</sub>  | electrostatic discharge voltage | Human Body Model                 | <u>[1]</u> | -    | ±4500 | V    |

|                   |                                 | Machine Model                    | [2]        | -    | ±250  | V    |

| I <sub>lu</sub>   | latch-up current                |                                  | [3]        | -    | 200   | mA   |

| T <sub>stg</sub>  | storage temperature             |                                  | <u>[4]</u> | -65  | +150  | °C   |

<sup>[1]</sup> Pass level; Human Body Model (HBM) according to JESD22-A114.

<sup>[2]</sup> Pass level; Machine Model (MM), according to JESD22-A115.

<sup>[3]</sup> Pass level; latch-up testing, according to JESD78.

<sup>[4]</sup> According to the NXP store and transport conditions (document *SNW-SQ-623*) the devices have to be stored at a temperature of +5 °C to +45 °C and a humidity of 25 % to 75 %.

#### Universal LCD driver for low multiplex rates

# 10. Static characteristics

Table 16. Static characteristics

$V_{DD}$  = 1.8 V to 5.5 V;  $V_{SS}$  = 0 V;  $V_{LCD}$  = 2.5 V to 6.5 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol               | Parameter                           | Conditions                                                                                |            | Min            | Тур | Max            | Unit      |

|----------------------|-------------------------------------|-------------------------------------------------------------------------------------------|------------|----------------|-----|----------------|-----------|

| Supplies             | S                                   |                                                                                           |            |                |     |                |           |

| $V_{DD}$             | supply voltage                      |                                                                                           |            | 1.8            | -   | 5.5            | V         |

| $V_{LCD}$            | LCD supply voltage                  |                                                                                           |            | 2.5            | -   | 6.5            | V         |

| $V_{POR}$            | power-on reset voltage              |                                                                                           |            | 1.0            | 1.3 | 1.6            | V         |

| I <sub>DD(LCD)</sub> | LCD supply current                  | f <sub>clk</sub> = 1536 Hz                                                                | <u>[1]</u> | -              | 16  | 60             | μΑ        |

| $I_{DD}$             | supply current                      | f <sub>clk</sub> = 1536 Hz                                                                | [1]        | -              | 2   | 20             | μΑ        |

| Logic                |                                     |                                                                                           |            |                |     |                |           |

| VI                   | input voltage                       |                                                                                           |            | $V_{SS} - 0.5$ | -   | $V_{DD} + 0.5$ | V         |

| $V_{IH}$             | HIGH-level input voltage            | on pins CLK, SYNC, OSC, A0 to A2, SA0, FF                                                 |            | $0.7V_{DD}$    | -   | $V_{DD}$       | V         |

| $V_{IL}$             | LOW-level input voltage             | on pins CLK, SYNC, OSC, A0 to A2, SA0, FF                                                 |            | $V_{SS}$       | -   | $0.3V_{DD}$    | V         |

| $V_{OH}$             | HIGH-level output voltage           |                                                                                           |            | $0.8V_{DD}$    | -   | -              | V         |

| $V_{OL}$             | LOW-level output voltage            |                                                                                           |            | -              | -   | $0.2V_{DD}$    | V         |

| I <sub>OH</sub>      | HIGH-level output current           | at pin CLK; $V_{OH} = 4.6 \text{ V}$ ; $V_{DD} = 5 \text{ V}$                             |            | 1              | -   | -              | mΑ        |

| $I_{OL}$             | LOW-level output current            | at pins CLK, $\overline{\text{SYNC}}$ ; $V_{OL} = 0.4 \text{ V}$ ; $V_{DD} = 5 \text{ V}$ |            | -              | -   | -1             | mΑ        |

| IL                   | leakage current                     | at pins OSC, CLK, SCL, SDA, A0 to A2, SA0, FF; $V_I = V_{DD}$ or $V_{SS}$                 |            | -1             | -   | +1             | μΑ        |

| Cı                   | input capacitance                   |                                                                                           | [2]        | -              | -   | 7              | pF        |

| I <sup>2</sup> C-bus |                                     |                                                                                           |            |                |     |                |           |

| Input on             | pins SDA and SCL                    |                                                                                           |            |                |     |                |           |

| VI                   | input voltage                       |                                                                                           |            | $V_{SS}-0.5$   | -   | 5.5            | V         |

| $V_{IH}$             | HIGH-level input voltage            |                                                                                           |            | $0.7V_{DD}$    | -   | 5.5            | V         |

| $V_{IL}$             | LOW-level input voltage             |                                                                                           |            | $V_{SS}$       | -   | $0.3V_{DD}$    | V         |

| Cı                   | input capacitance                   |                                                                                           | [2]        | -              | -   | 7              | pF        |

| I <sub>OL(SDA)</sub> | LOW-level output current on pin SDA | $V_{OL} = 0.4 \text{ V}; V_{DD} = 5 \text{ V}$                                            |            | -              | -   | -3             | mA        |

| LCD out              | puts                                |                                                                                           |            |                |     |                |           |

| $\Delta V_{O}$       | output voltage variation            | on pins BP0 to BP3; $C_{bpl} = 35 \text{ nF}$                                             |            | -100           | -   | +100           | mV        |

|                      |                                     | on pins S0 to S79; C <sub>sgm</sub> = 5 nF                                                |            | -100           | -   | +100           | mV        |

| Ro                   | output resistance                   | $V_{LCD} = 5 \text{ V}$                                                                   |            |                |     |                |           |

|                      |                                     | on pins BP0 to BP3                                                                        | [3]        | -              | 1.5 | 10             | $k\Omega$ |

|                      |                                     | on pins S0 to S79                                                                         | [3]        | -              | 6.0 | 13.5           | kΩ        |

<sup>[1]</sup> LCD outputs are open-circuit; inputs at  $V_{SS}$  or  $V_{DD}$ ; external clock with 50 % duty factor;  $I^2C$ -bus inactive.

<sup>[2]</sup> Not tested, design specification only.

<sup>[3]</sup> Outputs measured individually and sequentially.

#### Universal LCD driver for low multiplex rates

# 11. Dynamic characteristics

Table 17. Dynamic characteristics

$V_{DD}$  = 1.8 V to 5.5 V;  $V_{SS}$  = 0 V;  $V_{LCD}$  = 2.5 V to 6.5 V;  $T_{amb}$  = -40 °C to +85 °C; unless otherwise specified.

| Symbol                    | Parameter Conditions                             |                 |        |      | Тур  | Max  | Unit |

|---------------------------|--------------------------------------------------|-----------------|--------|------|------|------|------|

| Clock                     |                                                  |                 |        |      |      |      |      |

| Internal: out             | out pin CLK                                      |                 |        |      |      |      |      |

| f <sub>clk</sub>          | clock frequency                                  | $FF = V_{DD}$   | [1][2] | 1440 | 1970 | 2640 | Hz   |

|                           |                                                  | $FF = V_{SS}$   | [1][2] | 1920 | 2640 | 3600 | Hz   |

| f <sub>fr</sub>           | frame frequency                                  | $FF = V_{DD}$   |        | 60   | 82   | 110  | Hz   |

|                           |                                                  | $FF = V_{SS}$   |        | 80   | 110  | 150  | Hz   |

| External: inp             | ut pin CLK                                       |                 |        |      |      |      |      |

| f <sub>clk(ext)</sub>     | external clock frequency                         |                 | [2]    | 800  | -    | 3600 | Hz   |

| t <sub>clk(H)</sub>       | HIGH-level clock time                            |                 |        | 130  | -    | -    | μs   |

| t <sub>clk(L)</sub>       | LOW-level clock time                             |                 |        | 130  | -    | -    | μs   |

| Synchroniz                | ation: input pin SYNC                            |                 |        |      |      |      |      |

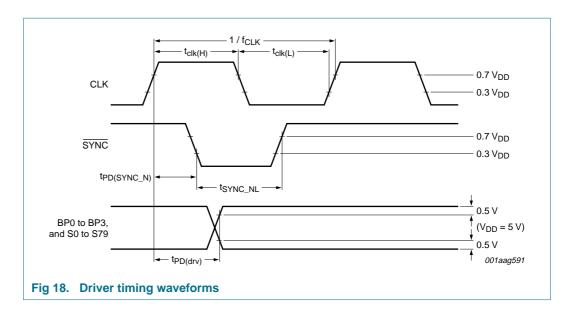

| t <sub>PD(SYNC_N)</sub>   | SYNC propagation delay                           |                 |        | -    | 30   | -    | ns   |

| t <sub>SYNC_NL</sub>      | SYNC LOW time                                    |                 |        | 1    | -    | -    | μs   |

| Outputs: pi               | ns BP0 to BP3 and S0 to S79                      |                 |        |      |      |      |      |

| t <sub>PD(drv)</sub>      | driver propagation delay                         | $V_{LCD} = 5 V$ |        | -    | -    | 30   | μs   |

| I <sup>2</sup> C-bus: tim | ing[ <u>3][4]</u>                                |                 |        |      |      |      |      |

| Pin SCL                   |                                                  |                 |        |      |      |      |      |

| f <sub>SCL</sub>          | SCL clock frequency                              |                 |        | -    | -    | 400  | kHz  |

| t <sub>HIGH</sub>         | HIGH period of the SCL clock                     |                 |        | 0.6  | -    | -    | μs   |

| $t_{LOW}$                 | LOW period of the SCL clock                      |                 |        | 1.3  | -    | -    | μs   |

| Pin SDA                   |                                                  |                 |        |      |      |      |      |

| t <sub>SU;DAT</sub>       | data set-up time                                 |                 |        | 100  | -    | -    | ns   |

| t <sub>HD;DAT</sub>       | data hold time                                   |                 |        | 0    | -    | -    | ns   |

| Pins SCL an               | d SDA                                            |                 |        |      |      |      |      |

| t <sub>BUF</sub>          | bus free time between a STOP and START condition |                 |        | 1.3  | -    | -    | μs   |

| t <sub>SU;STO</sub>       | set-up time for STOP condition                   |                 |        | 0.6  | -    | -    | μs   |

| t <sub>HD;STA</sub>       | hold time (repeated) START condition             |                 |        | 0.6  | -    | -    | μs   |

| t <sub>SU;STA</sub>       | set-up time for a repeated START condition       |                 |        | 0.6  | -    | -    | μs   |

| t <sub>r</sub>            | rise time of both SDA and SCL signals            |                 |        | -    | -    | 0.3  | μs   |

| t <sub>f</sub>            | fall time of both SDA and SCL signals            |                 |        | -    | -    | 0.3  | μs   |

| C <sub>b</sub>            | capacitive load for each bus line                |                 |        | -    | -    | 400  | pF   |

| t <sub>w(spike)</sub>     | spike pulse width                                | on bus          |        | -    | -    | 50   | ns   |

<sup>[1]</sup> Typical output duty cycle of 50 %.

<sup>[2]</sup> The corresponding frame frequency is  $f_{fr} = \frac{f_{clk}}{24}$  .

<sup>[3]</sup> All timing values are valid within the operating supply voltage and ambient temperature range and are referenced to V<sub>IL</sub> and V<sub>IH</sub> with an input voltage swing of V<sub>SS</sub> to V<sub>DD</sub>.

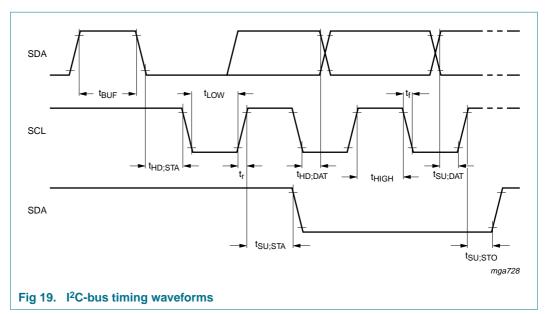

<sup>[4]</sup> For I<sup>2</sup>C-bus timings see Figure 19.

#### Universal LCD driver for low multiplex rates

Universal LCD driver for low multiplex rates

# 12. Application information

#### 12.1 Cascaded operation

In large display configurations of up to sixteen PCF85133s can be recognized on the same I<sup>2</sup>C-bus by using the 3-bit hardware subaddress (A0, A1 and A2) and the programmable I<sup>2</sup>C-bus slave address (SA0).

Table 18. Addressing cascaded PCF85133

| Cluster | Bit SA0 | Pin A2 | Pin A1 | Pin A0 | Device |

|---------|---------|--------|--------|--------|--------|

| 1       | 0       | 0      | 0      | 0      | 0      |

|         |         | 0      | 0      | 1      | 1      |

|         |         | 0      | 1      | 0      | 2      |

|         |         | 0      | 1      | 1      | 3      |

|         |         | 1      | 0      | 0      | 4      |

|         |         | 1      | 0      | 1      | 5      |

|         |         | 1      | 1      | 0      | 6      |

|         |         | 1      | 1      | 1      | 7      |

| 2       | 1       | 0      | 0      | 0      | 8      |

|         |         | 0      | 0      | 1      | 9      |

|         |         | 0      | 1      | 0      | 10     |

|         |         | 0      | 1      | 1      | 11     |

|         |         | 1      | 0      | 0      | 12     |

|         |         | 1      | 0      | 1      | 13     |

|         |         | 1      | 1      | 0      | 14     |

|         |         | 1      | 1      | 1      | 15     |

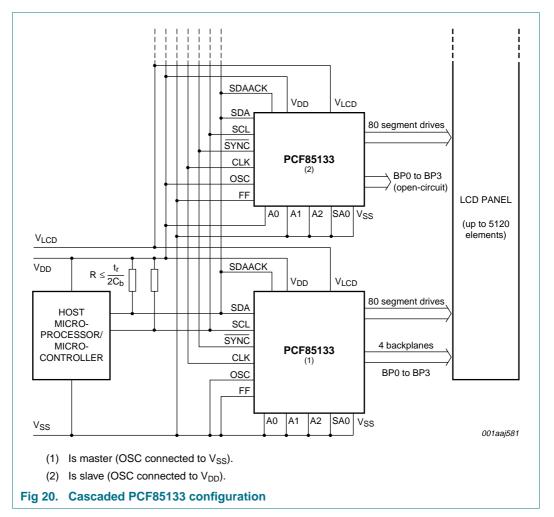

When cascaded PCF85133s are synchronized, they can share the backplane signals from one of the devices in the cascade. Such an arrangement is cost-effective in large LCD applications since the backplane outputs of only one device need to be through-plated to the backplane electrodes of the display. The other PCF85133s of the cascade contribute additional segment outputs but their backplane outputs are left open-circuit (see Figure 20).

For display sizes that are not multiple of 320 elements, a mixed cascaded system can be considered containing only devices like PCF85133 and PCF8532. Depending on the application, one must take care of the software commands compatibility and pin connection compatibility.

In a cascade only one master but multiple slaves are allowed. No external clock should be used; the slaves get the clock from the master.

The SYNC line is provided to maintain the correct synchronization between all cascaded PCF85133s. This synchronization is guaranteed after the power-on reset. The only time that SYNC is likely to be needed is if synchronization is accidentally lost (e.g. by noise in adverse electrical environments, or by the definition of a multiplex mode when PCF85133s with different SA0 levels are cascaded).

#### Universal LCD driver for low multiplex rates

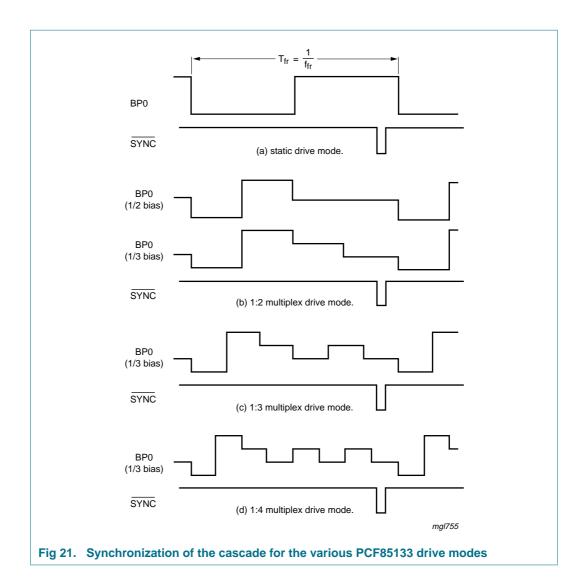

SYNC is organized as an input/output pin; the output selection being realized as an open-drain driver with an internal pull-up resistor. A PCF85133 asserts the SYNC line at the onset of its last active backplane signal and monitors the SYNC line at all other times. Should synchronization in the cascade be lost, it will be restored by the first PCF85133 to assert SYNC. The timing relationships between the backplane waveforms and the SYNC signal for the various drive modes of the PCF85133 are shown in Figure 21.

The contact resistance between the SYNC bumps of cascaded devices must be controlled. If the resistance is too high then the device will not be able to synchronize properly. This is particularly applicable to COG applications. Table 19 shows the limiting values for contact resistance.

Table 19. SYNC contact resistance

| Number of devices | Maximum contact resistance |

|-------------------|----------------------------|

| 2                 | 6000 Ω                     |

| 3 to 5            | 2200 Ω                     |

| 6 to 10           | 1200 Ω                     |

| 11 to 16          | 700 Ω                      |

**PCF85133 NXP Semiconductors**

## Universal LCD driver for low multiplex rates

#### Universal LCD driver for low multiplex rates

# 13. Bare die description

#### 13.1 General description

Table 20. Gold bump hardness

| Type number     | Min | Max | Unit <sup>[1]</sup> |

|-----------------|-----|-----|---------------------|

| PCF85133U/2DA/1 | 60  | 120 | HV                  |

<sup>[1]</sup> Pressure of diamond head: 10 g to 50 g.

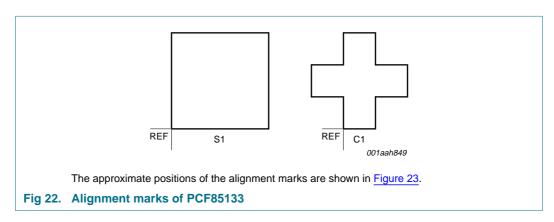

## 13.2 Alignment marks

Table 21. Alignment mark locations

| Symbol | <b>Χ (μm)</b> | Υ (μm) |

|--------|---------------|--------|

| S1     | -1916.1       | 45     |

| C1     | 1855.8        | 45     |

## 13.3 Bump locations

Table 22. Bump locations

All x/y coordinates represent the position of the center of each bump with respect to the center (x/y = 0) of the chip; see Figure 23.

| Symbol | Bump | <b>Χ (μm)</b> | <b>Υ (μm)</b> |            | Description                             |

|--------|------|---------------|---------------|------------|-----------------------------------------|

| SDAACK | 1    | -1022.67      | -436.5        | <u>[1]</u> | I <sup>2</sup> C-bus acknowledge output |

| SDAACK | 2    | -968.67       | -436.5        |            |                                         |

| SDAACK | 3    | -914.67       | -436.5        |            |                                         |

| SDA    | 4    | -712.17       | -436.5        | <u>[1]</u> | I <sup>2</sup> C-bus serial data input  |

| SDA    | 5    | -658.17       | -436.5        |            |                                         |

| SDA    | 6    | -604.17       | -436.5        |            |                                         |

| SCL    | 7    | -433.17       | -436.5        |            | I <sup>2</sup> C-bus serial clock input |

| SCL    | 8    | -379.17       | -436.5        |            |                                         |

| SCL    | 9    | -325.17       | -436.5        |            |                                         |

| CLK    | 10   | -173.52       | -436.5        |            | clock input/output                      |

## Universal LCD driver for low multiplex rates

**Table 22. Bump locations**All x/y coordinates represent the position of the center of each bump with respect to the center (x/y = 0) of the chip; see Figure 23.

| Symbol    | Bump | <b>Χ (μm)</b> | <b>Υ (μm)</b> | Description                                     |

|-----------|------|---------------|---------------|-------------------------------------------------|

| $V_{DD}$  | 11   | -61.47        | -436.5        | supply voltage                                  |

| $V_{DD}$  | 12   | -7.47         | -436.5        |                                                 |

| $V_{DD}$  | 13   | 46.53         | -436.5        |                                                 |

| SYNC      | 14   | 149.58        | -436.5        | cascade synchronization input/output            |

| OSC       | 15   | 262.08        | -436.5        | oscillator select                               |

| FF        | 16   | 345.78        | -436.5        | frame frequency select                          |

| A0        | 17   | 429.48        | -436.5        | subaddress input                                |

| A1        | 18   | 513.18        | -436.5        |                                                 |

| A2        | 19   | 596.88        | -436.5        |                                                 |

| SA0       | 20   | 680.58        | -436.5        | I <sup>2</sup> C-bus slave address input; bit 0 |

| $V_{SS}$  | 21   | 765.63        | -436.5        | ground supply voltage                           |

| $V_{SS}$  | 22   | 819.63        | -436.5        |                                                 |

| $V_{SS}$  | 23   | 873.63        | -436.5        |                                                 |

| $V_{LCD}$ | 24   | 979.83        | -436.5        | LCD supply voltage                              |

| $V_{LCD}$ | 25   | 1033.83       | -436.5        |                                                 |

| $V_{LCD}$ | 26   | 1087.83       | -436.5        |                                                 |

| BP2       | 27   | 1176.03       | -436.5        | LCD backplane output                            |

| BP0       | 28   | 1230.03       | -436.5        |                                                 |

| S0        | 29   | 1284.03       | -436.5        | LCD segment output                              |

| S1        | 30   | 1338.03       | -436.5        |                                                 |

| S2        | 31   | 1392.03       | -436.5        |                                                 |

| S3        | 32   | 1446.03       | -436.5        |                                                 |

| S4        | 33   | 1500.03       | -436.5        |                                                 |

| S5        | 34   | 1554.03       | -436.5        |                                                 |

| S6        | 35   | 1608.03       | -436.5        |                                                 |

| S7        | 36   | 1662.03       | -436.5        |                                                 |

| S8        | 37   | 1716.03       | -436.5        |                                                 |

| S9        | 38   | 1770.03       | -436.5        |                                                 |

| S10       | 39   | 1824.03       | -436.5        |                                                 |

| S11       | 40   | 1878.03       | -436.5        |                                                 |

| S12       | 41   | 1423.53       | 436.5         |                                                 |

| S13       | 42   | 1369.53       | 436.5         |                                                 |

| S14       | 43   | 1315.53       | 436.5         |                                                 |

| S15       | 44   | 1261.53       | 436.5         |                                                 |

| S16       | 45   | 1207.53       | 436.5         |                                                 |

| S17       | 46   | 1153.53       | 436.5         |                                                 |

| S18       | 47   | 1099.53       | 436.5         |                                                 |

|           |      |               |               |                                                 |

| S19       | 48   | 1045.53       | 436.5         |                                                 |

#### Universal LCD driver for low multiplex rates

**Table 22.** Bump locations All x/y coordinates represent the position of the center of each bump with respect to the center (x/y = 0) of the chip; see Figure 23.

| Symbol | Bump | <b>Χ (μm)</b> | <b>Υ (μm)</b> | Description        |

|--------|------|---------------|---------------|--------------------|

| S21    | 50   | 937.53        | 436.5         | LCD segment output |

| S22    | 51   | 883.53        | 436.5         |                    |

| S23    | 52   | 829.53        | 436.5         |                    |

| S24    | 53   | 714.06        | 436.5         |                    |

| S25    | 54   | 660.06        | 436.5         |                    |

| S26    | 55   | 606.06        | 436.5         |                    |

| S27    | 56   | 552.06        | 436.5         |                    |

| S28    | 57   | 498.06        | 436.5         |                    |

| S29    | 58   | 444.06        | 436.5         |                    |

| S30    | 59   | 390.06        | 436.5         |                    |

| S31    | 60   | 336.06        | 436.5         |                    |

| S32    | 61   | 282.06        | 436.5         |                    |

| S33    | 62   | 228.06        | 436.5         |                    |

| S34    | 63   | 112.59        | 436.5         |                    |

| S35    | 64   | 58.59         | 436.5         |                    |

| S36    | 65   | 4.59          | 436.5         |                    |

| S37    | 66   | -49.41        | 436.5         |                    |

| S38    | 67   | -103.41       | 436.5         |                    |

| S39    | 68   | -157.41       | 436.5         |                    |

| S40    | 69   | -211.41       | 436.5         |                    |

| S41    | 70   | -265.41       | 436.5         |                    |

| S42    | 71   | -319.41       | 436.5         |                    |

| S43    | 72   | -373.41       | 436.5         |                    |

| S44    | 73   | -427.41       | 436.5         |                    |

| S45    | 74   | -481.41       | 436.5         |                    |

| S46    | 75   | -596.88       | 436.5         |                    |

| S47    | 76   | -650.88       | 436.5         |                    |

| S48    | 77   | -704.88       | 436.5         |                    |

| S49    | 78   | -758.88       | 436.5         |                    |

| S50    | 79   | -812.88       | 436.5         |                    |

| S51    | 80   | -866.88       | 436.5         |                    |

| S52    | 81   | -920.88       | 436.5         |                    |

| S53    | 82   | -974.88       | 436.5         |                    |

| S54    | 83   | -1028.88      | 436.5         |                    |

| S55    | 84   | -1082.88      | 436.5         |                    |

| S56    | 85   | -1136.88      | 436.5         |                    |

| S57    | 86   | -1252.35      | 436.5         |                    |

| S58    | 87   | -1306.35      | 436.5         |                    |

| S59    | 88   | -1360.35      | 436.5         |                    |

#### Universal LCD driver for low multiplex rates

Table 22.

Bump locations

All x/y coordinates represent the position of the center of each bump with respect to the center

All x/y coordinates represent the position of the center of each bump with respect to the center (x/y = 0) of the chip; see Figure 23.

| Symbol | Bump | <b>Χ (μm)</b> | <b>Υ (μm)</b> |     | Description          |

|--------|------|---------------|---------------|-----|----------------------|

| S60    | 89   | -1414.35      | 436.5         |     | LCD segment output   |

| S61    | 90   | -1468.35      | 436.5         |     |                      |

| S62    | 91   | -1522.35      | 436.5         |     |                      |

| S63    | 92   | -1576.35      | 436.5         |     |                      |

| S64    | 93   | -1630.35      | 436.5         |     |                      |

| S65    | 94   | -1684.35      | 436.5         |     |                      |

| S66    | 95   | -1738.35      | 436.5         |     |                      |

| S67    | 96   | -1792.35      | 436.5         |     |                      |

| S68    | 97   | -1876.05      | -436.5        |     |                      |

| S69    | 98   | -1822.05      | -436.5        |     |                      |

| S70    | 99   | -1768.05      | -436.5        |     |                      |

| S71    | 100  | -1714.05      | -436.5        |     |                      |

| S72    | 101  | -1660.05      | -436.5        |     |                      |

| S73    | 102  | -1606.05      | -436.5        |     |                      |

| S74    | 103  | -1552.05      | -436.5        |     |                      |

| S75    | 104  | -1498.05      | -436.5        |     |                      |

| S76    | 105  | -1444.05      | -436.5        |     |                      |

| S77    | 106  | -1390.05      | -436.5        |     |                      |

| S78    | 107  | -1336.05      | -436.5        |     |                      |

| S79    | 108  | -1282.05      | -436.5        |     |                      |

| BP3    | 109  | -1228.05      | -436.5        |     | LCD backplane output |

| BP1    | 110  | -1174.05      | -436.5        |     |                      |

| D1     | -    | 1932.03       | -436.5        | [2] | dummy pad            |

| D2     | -    | 1909.53       | 436.5         |     |                      |

| D3     | -    | 1801.53       | 436.5         |     |                      |

| D4     | -    | 1693.53       | 436.5         |     |                      |

| D5     | -    | 1585.53       | 436.5         |     |                      |

| D6     | -    | 1477.53       | 436.5         |     |                      |

| D7     | -    | -1846.35      | 436.5         |     |                      |

| D8     | -    | -1953         | 436.5         |     |                      |

| D9     | -    | -1930.05      | -436.5        |     |                      |

|        |      |               |               |     |                      |

<sup>[1]</sup> For most applications SDA and SDAACK are shorted together; see Section 7.16.

<sup>[2]</sup> The dummy pads are connected to  $V_{\mbox{\scriptsize SS}}$  but are not tested.

#### Universal LCD driver for low multiplex rates

# 14. Bare die outline

Fig 23. Bare die outline of PCF85133

#### Universal LCD driver for low multiplex rates

# 15. Handling information

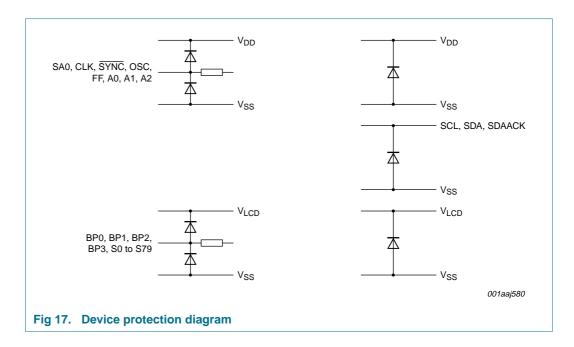

All input and output pins are protected against ElectroStatic Discharge (ESD) under normal handling. When handling Metal-Oxide Semiconductor (MOS) devices ensure that all normal precautions are taken as described in *JESD625-A*, *IEC 61340-5* or equivalent standards.

# 16. Packing information

#### Universal LCD driver for low multiplex rates

38 of 41

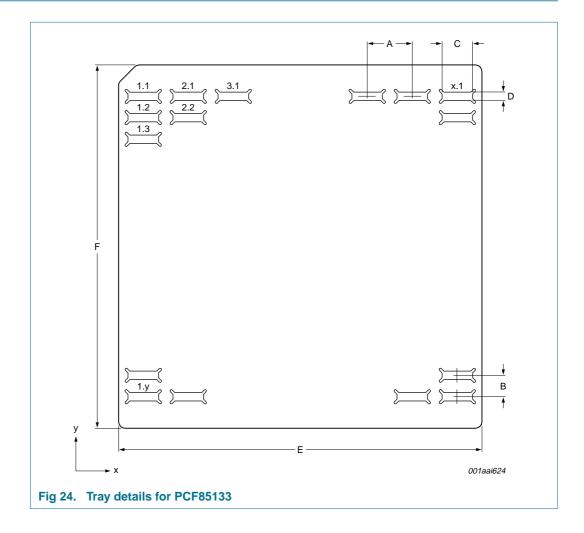

**Table 23.** Tray dimensions of PCF85133 tray *See Figure 24.*

| Symbol | Description                    | Value   |

|--------|--------------------------------|---------|

| Α      | pocket pitch in x direction    | 6.3 mm  |

| В      | pocket pitch in y direction    | 3 mm    |

| С      | pocket width in x direction    | 4.26 mm |

| D      | pocket width in y direction    | 1.17 mm |

| E      | tray width in x direction      | 50.8 mm |

| F      | tray width in y direction      | 50.8 mm |

| N      | number of pockets, x direction | 7       |

| M      | number of pockets, y direction | 15      |

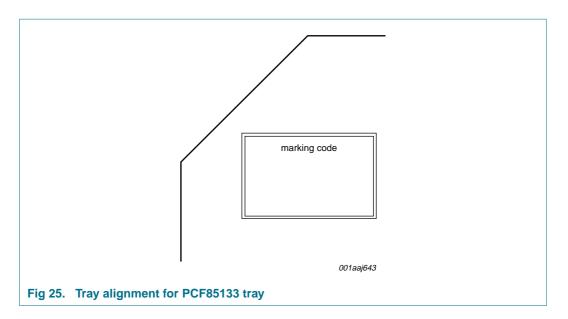

The orientation of the IC in a pocket is indicated by the position of the IC type name on the die surface with respect to the chamfer on the upper left corner of the tray (see <u>Figure 25</u>). Refer to the bump location diagram (<u>Figure 23</u>) for the orientation and position of the type name on the die surface.

#### Universal LCD driver for low multiplex rates

39 of 41

# 17. Abbreviations

Table 24. Abbreviations

| Acronym          | Description                             |

|------------------|-----------------------------------------|

| CMOS             | Complementary Metal-Oxide Semiconductor |

| COG              | Chip-On-Glass                           |

| DC               | Direct Current                          |

| HBM              | Human Body Model                        |

| I <sup>2</sup> C | Inter-Integrated Circuit                |

| IC               | Integrated Circuit                      |

| ITO              | Indium Tin Oxide                        |

| LCD              | Liquid Crystal Display                  |

| MM               | Machine Model                           |

| RAM              | Random Access Memory                    |