ISSUE 5

SATURN USER NETWORK INTERFACE

## PM5350

PMC PMC-Sierra, Inc.

## S/UNI-155-ULTRA

# SATURN USER NETWORK INTERFACE 155.52 & 51.84 MBIT/S

DATA SHEET

**ISSUE 5: JUNE 1998**

ISSUE 5

SATURN USER NETWORK INTERFACE

#### **PUBLIC REVISION HISTORY**

| Issue No | Date of issue | Details of Change                                        |

|----------|---------------|----------------------------------------------------------|

| 5        | June 1998     | Data Sheet Reformatted — No Change in Technical Content. |

|          |               | Generated R5 data sheet from PMC-969489, R7              |

| 4        | November 1997 | Eng Doc (7) revised.                                     |

| 3        | Dec 20, 1996  | Third Revision                                           |

| 2        | Oct 15, 1996  | Second Revision                                          |

| 1        | Sept 12, 1996 | Creation of Document                                     |

SATURN USER NETWORK INTERFACE

## **CONTENTS**

| 1 | FEAT  | URES1                                      |

|---|-------|--------------------------------------------|

| 2 | APPI  | _ICATIONS4                                 |

| 3 | REFI  | ERENCES                                    |

| 4 | APPI  | LICATION EXAMPLES6                         |

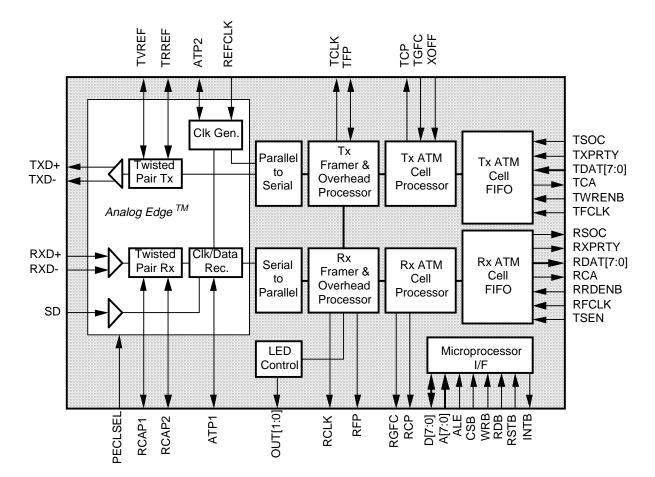

| 5 | BLO   | CK DIAGRAM7                                |

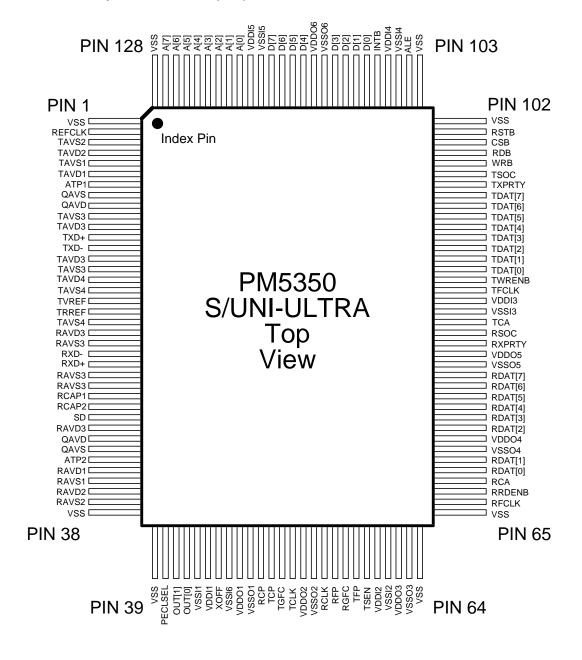

| 6 | PIN [ | DIAGRAM10                                  |

| 7 | PIN [ | DESCRIPTION                                |

|   | 7.1   | UTP-5 AND PECL RECEIVER27                  |

|   | 7.2   | CLOCK RECOVERY27                           |

|   | 7.3   | SERIAL TO PARALLEL CONVERTER               |

|   | 7.4   | RECEIVE SECTION OVERHEAD PROCESSOR         |

|   |       | 7.4.1 FRAMER                               |

|   |       | 7.4.2 DESCRAMBLE                           |

|   |       | 7.4.3 ERROR MONITOR                        |

|   |       | 7.4.4 LOSS OF SIGNAL                       |

|   |       | 7.4.5 LOSS OF FRAME                        |

|   | 7.5   | RECEIVE LINE OVERHEAD PROCESSOR            |

|   |       | 7.5.1 LINE REMOTE DEFECT INDICATION DETECT |

|   |       | 7.5.2 LINE AIS DETECT                      |

|   |       | 7.5.3 ERROR MONITOR                        |

|   | 7.6   | RECEIVE PATH OVERHEAD PROCESSOR            |

|   |       | 7.6.1 POINTER INTERPRETER                  |

P

ISSUE 5

|      | 7.6.2 ERROR MONITOR                         |

|------|---------------------------------------------|

| 7.7  | RECEIVE ATM CELL PROCESSOR                  |

|      | 7.7.1 CELL DELINEATION                      |

|      | 7.7.2 DESCRAMBLER                           |

|      | 7.7.3 CELL FILTER AND HCS VERIFICATION      |

|      | 7.7.4 PERFORMANCE MONITOR                   |

|      | 7.7.5 GFC EXTRACTION PORT                   |

|      | 7.7.6 RECEIVE FIFO                          |

| 7.8  | UTP-5 AND PECL TRANSMITTER                  |

| 7.9  | CLOCK SYNTHESIS                             |

| 7.10 | PARALLEL TO SERIAL CONVERTER                |

| 7.11 | TRANSMIT SECTION OVERHEAD PROCESSOR         |

|      | 7.11.1 LINE AIS INSERT                      |

|      | 7.11.2 BIP-8 INSERT                         |

|      | 7.11.3 FRAMING AND IDENTITY INSERT          |

|      | 7.11.4 SCRAMBLER                            |

| 7.12 | TRANSMIT LINE OVERHEAD PROCESSOR            |

|      | 7.12.1 BIP CALCULATE                        |

|      | 7.12.2 LINE REMOTE DEFECT INDICATION INSERT |

|      | 7.12.3 LINE FEBE INSERT                     |

| 7.13 | TRANSMIT PATH OVERHEAD PROCESSOR            |

|      | 7.13.1 POINTER GENERATOR                    |

|      | 7.13.2 BIP-8 CALCULATE                      |

| 960924 |      | ISSUE 5                         | SATURN USER NETWORK INTERFACE |

|--------|------|---------------------------------|-------------------------------|

|        |      | 7.13.3 FEBE CALCULATE           | 41                            |

|        |      | 7.13.4 SPE MULTIPLEXER          | 41                            |

|        | 7.14 | TRANSMIT ATM CELL PROCESSOR     | 42                            |

|        |      | 7.14.1 IDLE/UNASSIGNED CELL GEN | ERATOR43                      |

|        |      | 7.14.2 SCRAMBLER                | 43                            |

|        |      | 7.14.3 HCS GENERATOR            | 43                            |

|        |      | 7.14.4 GFC INSERTION PORT       | 43                            |

|        |      | 7.14.5 TRANSMIT FIFO            | 43                            |

|        | 7.15 | DROP SIDE INTERFACE             | 44                            |

|        |      | 7.15.1 RECEIVE INTERFACE        | 44                            |

|        |      | 7.15.2 TRANSMIT INTERFACE       | 45                            |

|        | 7.16 | PARALLEL OUTPUT PORT AND LED I  | DISPLAY CONTROLLER45          |

|        | 7.17 | MICROPROCESSOR INTERFACE        | 45                            |

| 8      | REGI | STER MEMORY MAP                 | 46                            |

|        | 8.1  | TEST MODE REGISTER MEMORY MA    | ۲۵                            |

|        | 8.2  | TEST MODE 0 DETAILS             |                               |

| 9      | OPE  | RATION                          |                               |

|        | 9.1  | OVERHEAD BYTE USAGE             |                               |

|        | 9.2  | CELL DATA STRUCTURE             |                               |

|        | 9.3  | PARALLEL OUTPUT PORT AND LED D  |                               |

|        |      | 9.3.1 DIRECT CONTROL PARALLEL   | OUTPUT PORT141                |

|        |      | 9.3.2 ALARM MONITOR             | 141                           |

|        |      | 9.3.3 TRAFFIC MONITOR           |                               |

| DATA SHEET |

|------------|

| PMC-960924 |

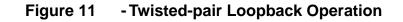

|    | 9.4    | LOOPBACK OPERATION142                                            |

|----|--------|------------------------------------------------------------------|

|    | 9.5    | BOARD DESIGN RECOMMENDATIONS                                     |

|    | 9.6    | POWER SUPPLIES SEQUENCING                                        |

|    | 9.7    | SELECTING BETWN TWISTED-PAIR AND PECL INTERFACES                 |

|    | 9.8    | INTERFACING TRANSMIT AND RECEIVE DATA LINES WITH<br>PECL DEVICES |

|    | 9.9    | INTERFACING TRANSMIT AND RECEIVE DATA LINES WITH UTP-5 CABLE     |

|    | 9.10   | CLOCKING OPTIONS                                                 |

|    | 9.11   | DROP SIDE RECEIVE INTERFACE                                      |

|    | 9.12   | DROP SIDE TRANSMIT INTERFACE                                     |

| 10 | ABSC   | DLUTE MAXIMUM RATINGS158                                         |

| 11 | D.C. 0 | CHARACTERISTICS                                                  |

| 12 | EXTE   | RNAL COMPONENTS                                                  |

| 13 | MICR   | OPROCESSOR INTERFACE TIMING CHARACTERISTICS 167                  |

| 14 | S/UN   | I-ULTRA TIMING CHARACTERISTICS                                   |

| 15 | ORD    | ERING AND THERMAL INFORMATION                                    |

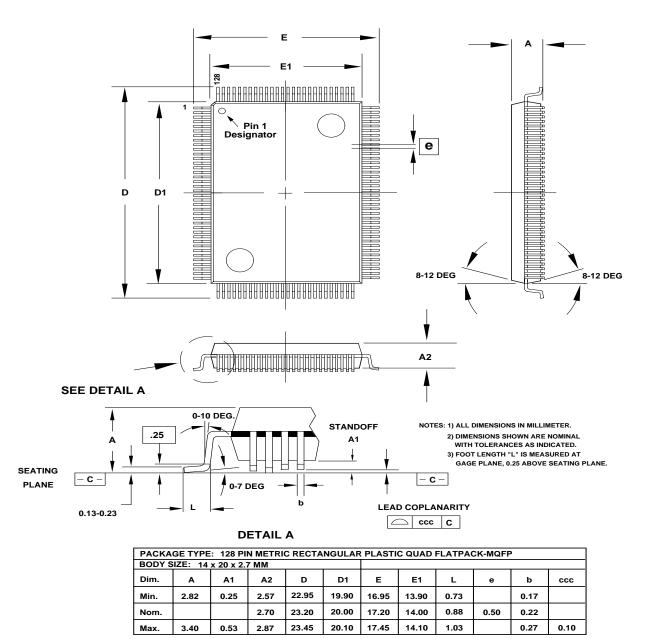

| 16 | MECH   | HANICAL INFORMATION181                                           |

PMC-Sierra, Inc.

## LIST OF REGISTERS

| REGISTER 0X00: S/UNI-ULTRA MASTER RESET AND IDENTITY / LOAD<br>METERS |

|-----------------------------------------------------------------------|

| REGISTER 0X01: S/UNI-ULTRA MASTER CONFIGURATION52                     |

| REGISTER 0X02: S/UNI-ULTRA MASTER INTERRUPT STATUS54                  |

| REGISTER 0X03: S/UNI-ULTRA MASTER MODE CONTROL56                      |

| REGISTER 0X04: S/UNI-ULTRA MASTER CLOCK MONITOR                       |

| REGISTER 0X05: S/UNI-ULTRA MASTER CONTROL                             |

| REGISTER 0X06: S/UNI-ULTRA CLOCK SYNTHESIS CONTROL AND STATUS         |

| REGISTER 0X08: S/UNI-ULTRA CLOCK RECOVERY CONTROL AND STATUS          |

| REGISTER 0X09: S/UNI-ULTRA CLOCK RECOVERY CONFIGURATION64             |

| REGISTER 0X0A: S/UNI-ULTRA LINE TRANSMITTER CONFIGURATION 165         |

| REGISTER 0X0B: S/UNI-ULTRA LINE TRANSMITTER CONFIGURATION 266         |

| REGISTER 0X0C: S/UNI-ULTRA LINE RECEIVER CONFIGURATION67              |

| REGISTER 0X10: RSOP CONTROL/INTERRUPT ENABLE                          |

| REGISTER 0X11: RSOP STATUS/INTERRUPT STATUS                           |

| REGISTER 0X12: RSOP SECTION BIP-8 LSB                                 |

| REGISTER 0X13: RSOP SECTION BIP-8 MSB                                 |

| REGISTER 0X14: TSOP CONTROL                                           |

| REGISTER 0X15: TSOP DIAGNOSTIC                                        |

| REGISTER 0X18: RLOP CONTROL/STATUS76                                  |

| REGISTER 0X19: RLOP INTERRUPT ENABLE/INTERRUPT STATUS77               |

| REGISTER 0X1A: RLOP LINE BIP-8/24 LSB79        |

|------------------------------------------------|

| REGISTER 0X1B: RLOP LINE BIP-8/2480            |

| REGISTER 0X1C: RLOP LINE BIP-8/24 MSB81        |

| REGISTER 0X1D: RLOP LINE FEBE LSB              |

| REGISTER 0X1E: RLOP LINE FEBE                  |

| REGISTER 0X1F: RLOP LINE FEBE MSB              |

| REGISTER 0X20: TLOP CONTROL                    |

| REGISTER 0X21: TLOP DIAGNOSTIC                 |

| REGISTER 0X30: RPOP STATUS/CONTROL             |

| REGISTER 0X31: RPOP INTERRUPT STATUS           |

| REGISTER 0X33: RPOP INTERRUPT ENABLE           |

| REGISTER 0X37: RPOP PATH SIGNAL LABEL          |

| REGISTER 0X38: RPOP PATH BIP-8 LSB92           |

| REGISTER 0X39: RPOP PATH BIP-8 MSB93           |

| REGISTER 0X3A: RPOP PATH FEBE LSB94            |

| REGISTER 0X3B: RPOP PATH FEBE MSB95            |

| REGISTER 0X3D: RPOP PATH BIP-8 CONFIGURATION96 |

| REGISTER 0X40: TPOP CONTROL/DIAGNOSTIC         |

| REGISTER 0X41: TPOP POINTER CONTROL            |

| REGISTER 0X45: TPOP ARBITRARY POINTER LSB      |

| REGISTER 0X46: TPOP ARBITRARY POINTER MSB101   |

| REGISTER 0X48: TPOP PATH SIGNAL LABEL          |

| REGISTER 0X49: TPOP PATH STATUS                |

P

| REGISTER 0X50: RACP CONTROL/STATUS                                |

|-------------------------------------------------------------------|

| REGISTER 0X51: RACP INTERRUPT ENABLE/STATUS                       |

| REGISTER 0X52: RACP MATCH HEADER PATTERN                          |

| REGISTER 0X53: RACP MATCH HEADER MASK109                          |

| REGISTER 0X54: RACP CORRECTABLE HCS ERROR COUNT                   |

| REGISTER 0X55: RACP UNCORRECTABLE HCS ERROR COUNT                 |

| REGISTER 0X56: RACP RECEIVE CELL COUNTER (LSB) 112                |

| REGISTER 0X57: RACP RECEIVE CELL COUNTER                          |

| REGISTER 0X58: RACP RECEIVE CELL COUNTER (MSB) 114                |

| REGISTER 0X59: RACP CONFIGURATION115                              |

| REGISTER 0X60: TACP CONTROL/STATUS                                |

| REGISTER 0X61: TACP IDLE/UNASSIGNED CELL HEADER PATTERN 119       |

| REGISTER 0X62: TACP IDLE/UNASSIGNED CELL PAYLOAD OCTET<br>PATTERN |

| REGISTER 0X63: TACP FIFO CONTROL121                               |

| REGISTER 0X64: TACP TRANSMIT CELL COUNTER (LSB)                   |

| REGISTER 0X65: TACP TRANSMIT CELL COUNTER                         |

| REGISTER 0X66: TACP TRANSMIT CELL COUNTER (MSB) 125               |

| REGISTER 0X67: TACP CONFIGURATION126                              |

| REGISTER 0X68: S/UNI-ULTRA POPC CONTROL                           |

| REGISTER 0X69: S/UNI-ULTRA POPC STROBE RATE 0                     |

| REGISTER 0X6A: S/UNI-ULTRA POPC STROBE RATE 1                     |

| REGISTER 0X80: MASTER TEST133                                     |

## **LIST OF FIGURES**

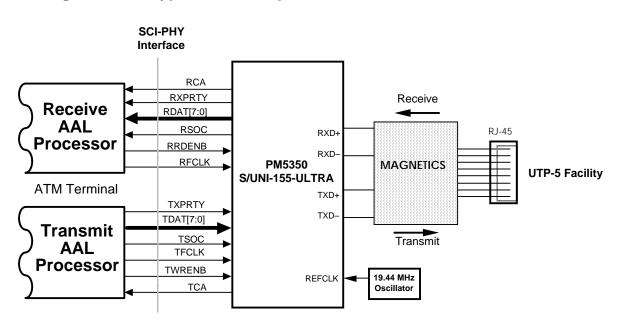

| FIGURE 1 - TYPICAL ATM ADAPTER UTP-5 INTERFACE                 |

|----------------------------------------------------------------|

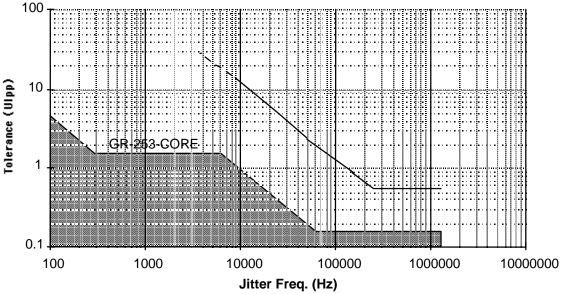

| FIGURE 2 - STS-3C/STM-1JITTER TOLERANCE                        |

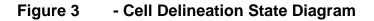

| FIGURE 3 - CELL DELINEATION STATE DIAGRAM                      |

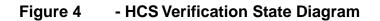

| FIGURE 4 - HCS VERIFICATION STATE DIAGRAM                      |

| FIGURE 5 - STS-3C/STM-1 DEFAULT TRANSPORT OVERHEAD VALUES 39   |

| FIGURE 6 - STS-1 DEFAULT TRANSPORT OVERHEAD VALUES40           |

| FIGURE 7 - DEFAULT PATH OVERHEAD VALUES42                      |

| FIGURE 8 - STS-3C (STM-1) OVERHEAD136                          |

| FIGURE 9 - STS-1 OVERHEAD                                      |

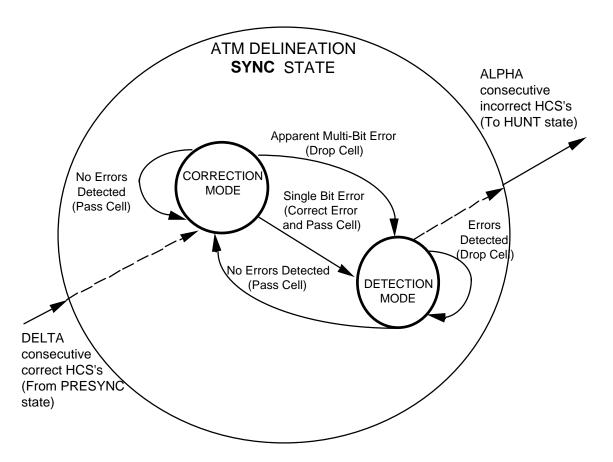

| FIGURE 10- DATA STRUCTURE                                      |

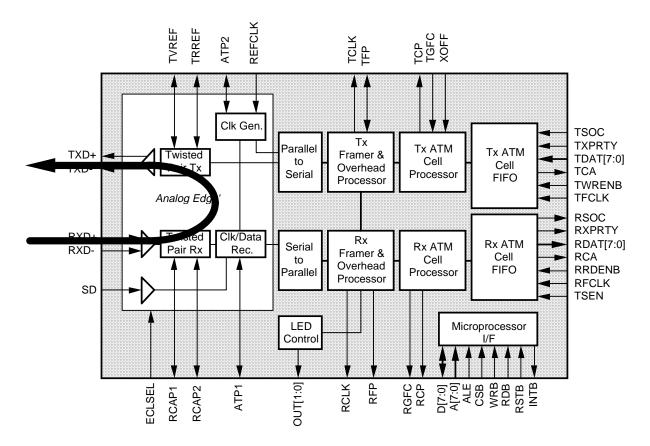

| FIGURE 11-TWISTED-PAIR LOOPBACK OPERATION                      |

| FIGURE 12- LINE LOOPBACK OPERATION144                          |

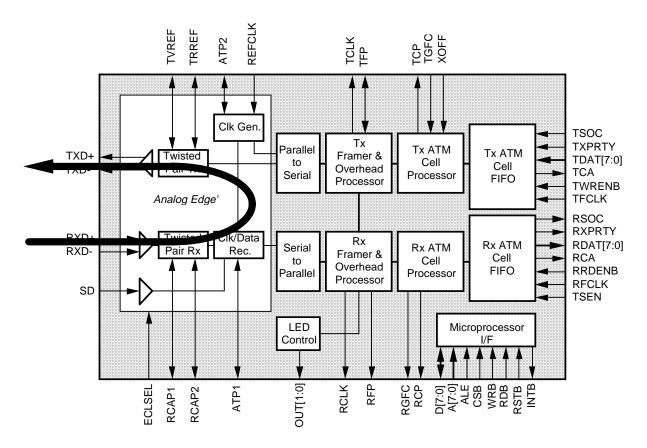

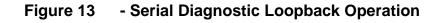

| FIGURE 13- SERIAL DIAGNOSTIC LOOPBACK OPERATION                |

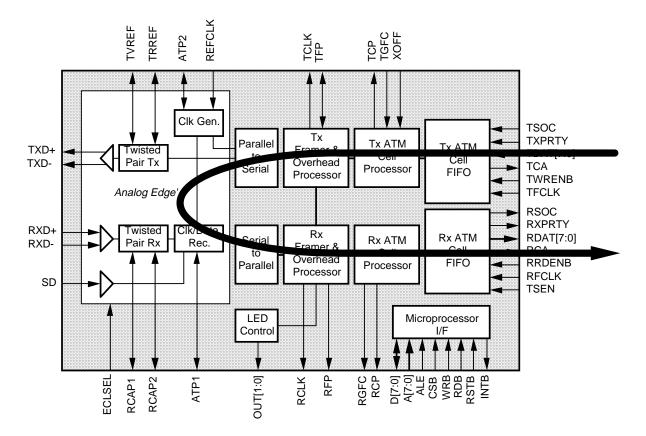

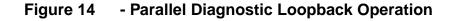

| FIGURE 14- PARALLEL DIAGNOSTIC LOOPBACK OPERATION146           |

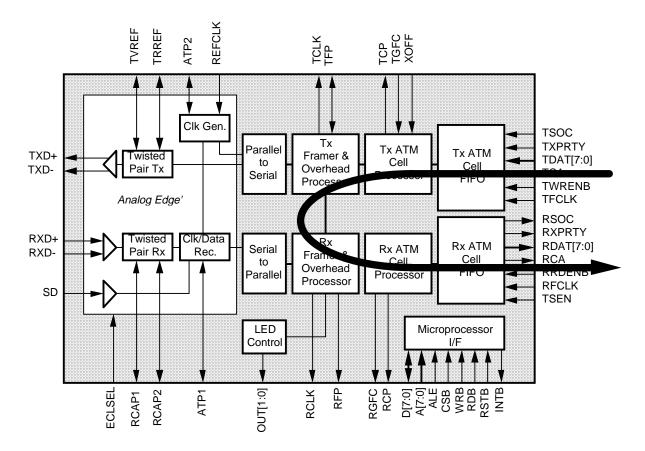

| FIGURE 15- INTERFACING TXD+/- TO PECL                          |

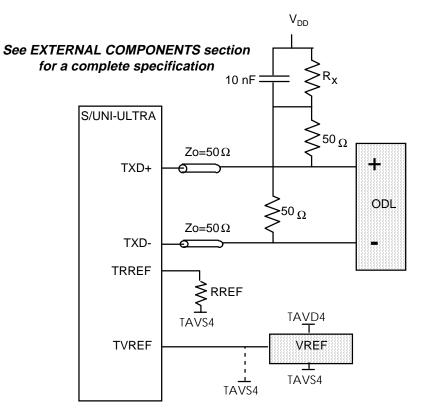

| FIGURE 16- INTERFACING WITH RXD+/- USING PECL (2 EXAMPLES) 150 |

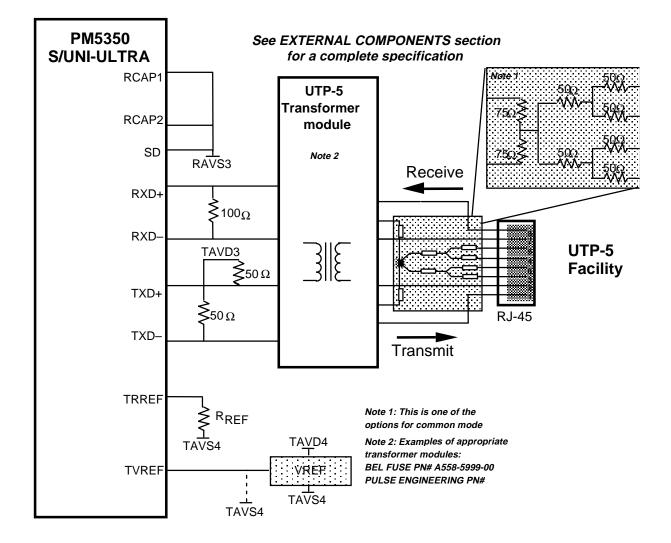

| FIGURE 17- INTERFACING TXD+/- AND RXD+/- WITH UTP-5152         |

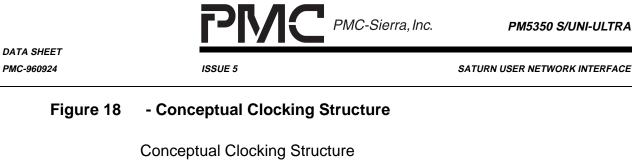

| FIGURE 18- CONCEPTUAL CLOCKING STRUCTURE                       |

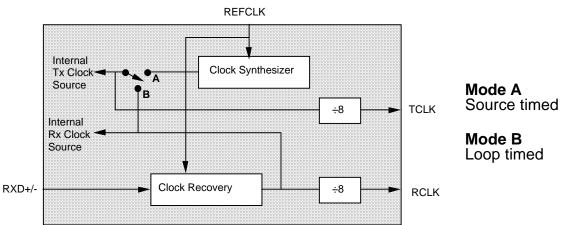

| FIGURE 19- RECEIVE FIFO EMPTY OPTION (RCALEVEL0=1)154          |

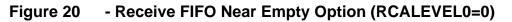

| FIGURE 20- RECEIVE FIFO NEAR EMPTY OPTION (RCALEVEL0=0)154     |

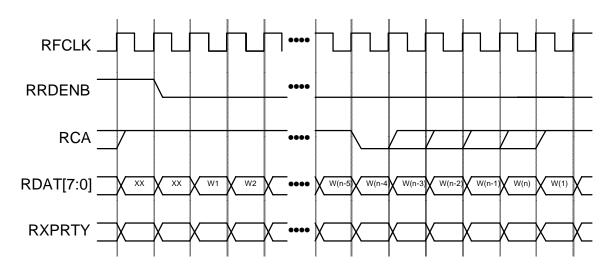

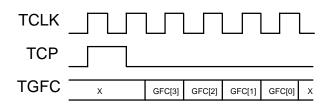

| FIGURE 21- RECEIVE GFC SERIAL LINK                             |

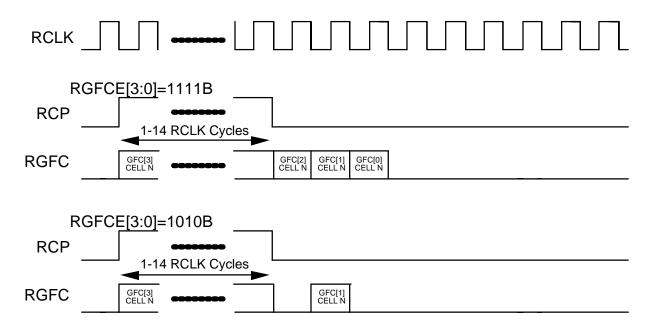

| FIGURE 22- TRANSMIT FIFO                                       |

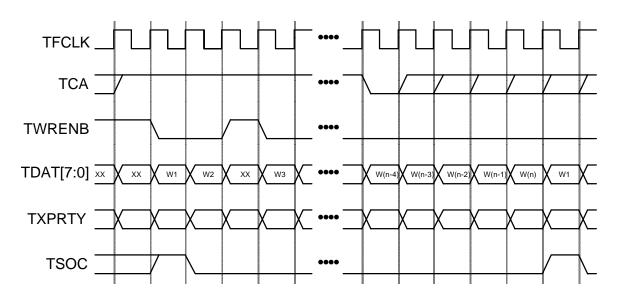

| FIGURE 23- TRANSMIT GFC SERIAL LINK                                     |

|-------------------------------------------------------------------------|

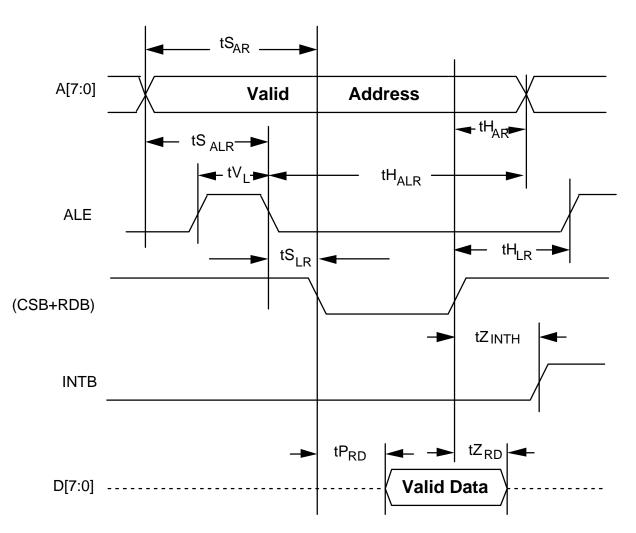

| FIGURE 24- MICROPROCESSOR INTERFACE READ TIMING168                      |

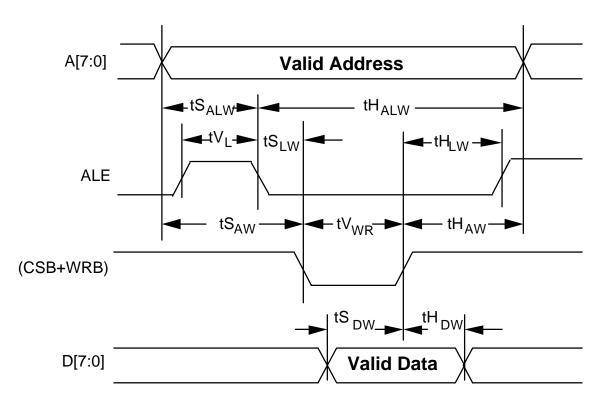

| FIGURE 25- MICROPROCESSOR INTERFACE WRITE TIMING                        |

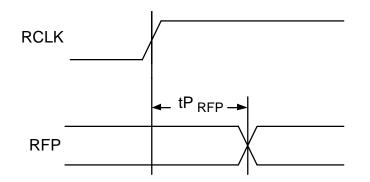

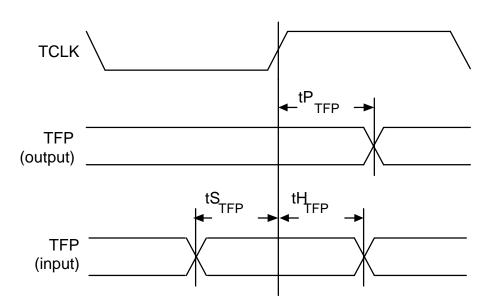

| FIGURE 26- RECEIVE FRAME PULSE OUTPUT TIMING                            |

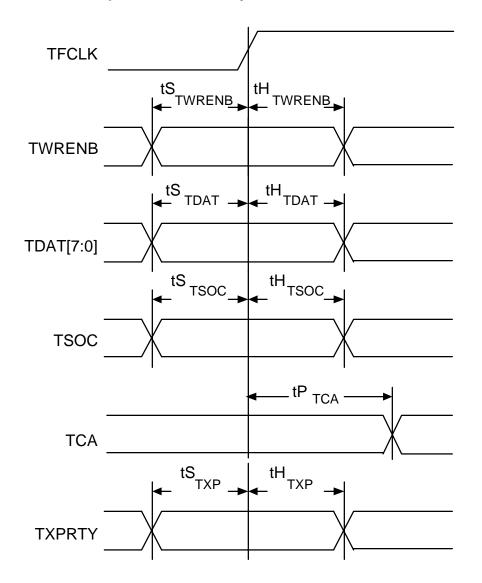

| FIGURE 27- LINE SIDE TRANSMIT INTERFACE TIMING                          |

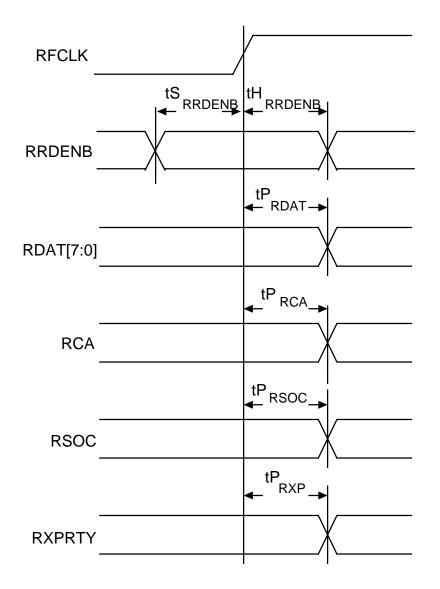

| FIGURE 28- DROP SIDE RECEIVE SYNCHRONOUS INTERFACE TIMING<br>(TSEN = 0) |

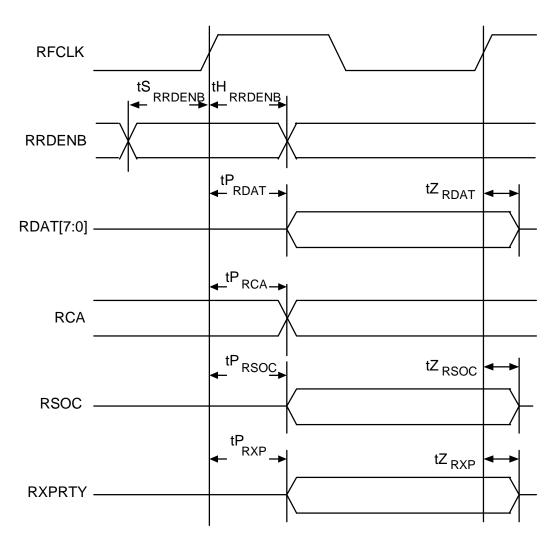

| FIGURE 29- DROP SIDE RECEIVE SYNCHRONOUS INTERFACE TIMING<br>(TSEN = 1) |

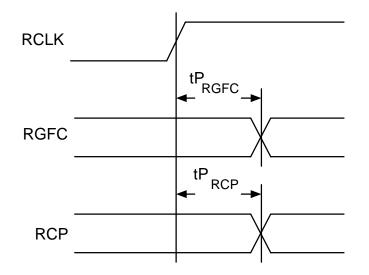

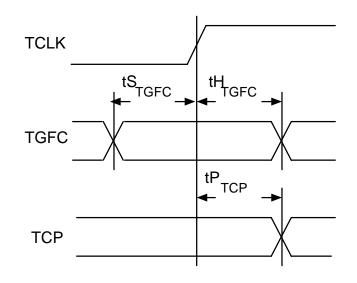

| FIGURE 30- GFC EXTRACT PORT TIMING                                      |

| FIGURE 31- DROP SIDE TRANSMIT SYNCHRONOUS INTERFACE177                  |

| FIGURE 32- GFC INSERT PORT TIMING178                                    |

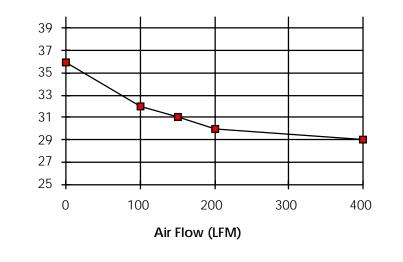

| FIGURE 33- THETA JA VS. AIR FLOW                                        |

ISSUE 5

#### LIST OF TABLES

| TABLE 1              | - MICROPROCESSOR INTERFACE READ ACCESS (FIGURE 24) .<br>    |

|----------------------|-------------------------------------------------------------|

| TABLE 2              | - MICROPROCESSOR INTERFACE WRITE ACCESS (FIGURE 25)<br>     |

| TABLE 3              | - LINE SIDE REFERENCE CLOCK171                              |

| TABLE 4              | - LINE SIDE RECEIVE INTERFACE (FIGURE 26)171                |

| TABLE 5              | - LINE SIDE TRANSMIT INTERFACE (FIGURE 27)                  |

|                      | - DROP SIDE RECEIVE SYNCHRONOUS INTERFACE (TSEN = 0)<br>28) |

| TABLE 7<br>(FIGURE 2 | - DROP SIDE RECEIVE SYNCHRONOUS INTERFACE (TSEN = 1)<br>29) |

| TABLE 8              | - GFC EXTRACT PORT (FIGURE 30)176                           |

| TABLE 9<br>31)       | - DROP SIDE TRANSMIT SYNCHRONOUS INTERFACE (FIGURE          |

| TABLE 10             | - GFC INSERT PORT (FIGURE 32)178                            |

| TABLE 11             | - S/UNI-ULTRA ORDERING INFORMATION                          |

| TABLE 12             | - S/UNI-ULTRA THERMAL INFORMATION                           |

ISSUE 5

SATURN USER NETWORK INTERFACE

#### FEATURES 1

- Single chip ATM User-Network Interface operating at 155.52 and 51.84 Mbit/s.

- Provides an Analog Edge Interface that can be selected to interface directly with Category-5 Unshielded Twisted Pair (UTP-5) or Shielded Twisted Pair cables, or to interface with Pseudo-ECL (PECL) optical data links (ODLs), using a minimum of passive components.

- Implements the ATM Forum User Network Interface Specification and the • ATM physical layer for Broadband ISDN according to CCITT Recommendation I.432.

- Processes duplex 155.52 Mbit/s STS-3c/STM-1 (direct interface to a twisted • pair cable or PECL interface to a PMD device) or 51.84 Mbit/s STS-1 (PECL interface to a PMD device only) data streams with on-chip clock and data recovery and clock synthesis.

- Performs clock recovery and clock synthesis using on-chip loop filters. •

- Provides Saturn Compliant Interface PHYsical layer (SCI-PHY™) FIFO buffers in both transmit and receive paths with parity support. Compatible with ATM Forum Utopia Level 1 specification.

- Inserts and extracts the generic flow control (GFC) bits via a simple serial interface and provides a transmit XOFF function to allow for local flow control.

- Provides a generic 8-bit microprocessor bus interface for configuration, control, and status monitoring.

- Low power, +5 Volt, CMOS technology.

- 128 pin high performance plastic quad flat pack (PQFP) 14 mm x 20 mm • package.

### The receiver section:

- Provides a serial interface at 155.52 or 51.84 Mbit/s.

- Adaptively equalizes the received differential signal.

SATURN USER NETWORK INTERFACE

- Recovers the clock and data; frames to the recovered data stream; descrambles the received data; interprets the received payload pointer (H1, H2); and extracts the STS-3c or STS-1 synchronous payload envelope (VC4) and path overhead.

- Extracts ATM cells from the synchronous payload envelope using ATM cell delineation and provides optional ATM cell payload descrambling, header check sequence (HCS) error detection and error correction, and idle/unassigned cell filtering.

- Provides a synchronous 8-bit wide, four cell FIFO buffer.

ISSUE 5

- Detects loss of signal (LOS), out of frame (OOF), loss of frame (LOF), line alarm indication signal (LAIS), line remote defect indication (RDI), loss of pointer (LOP), path alarm indication signal (PAIS), loss of cell delineation and path remote defect indication (PRDI).

- Counts received section BIP-8 (B1) errors, received line BIP-8/24 (B2) errors, line far end block errors (line FEBE), received path BIP-8 (B3) errors and path far end block errors (path FEBE).

- Counts received HCS errored cells that are discarded, received HCS errored cells that are corrected and passed on, and the total received cells passed on.

#### The transmitter section:

- Provides a serial interface at 155.52 or 51.84 Mbit/s.

- Provides a serial interface at 155.52 or 51.84 Mbit/s. Generates data of the correct amplitude and shape to directly interface with a signal transformer and transmit over a UTP-5 cable.

- Provides a synchronous 8-bit wide, four cell FIFO buffer.

- Provides idle/unassigned cell insertion, HCS generation/insertion, and ATM cell payload scrambling; Inserts ATM cells into the transmitted STS-3c (STM-1) or STS-1 synchronous payload envelope using H4 framing

- Generates the transmit payload pointer (H1, H2) and inserts the path overhead; scrambles the transmitted STS-3c (STM-1) or STS-1 stream and inserts framing bytes (A1, A2) and the identity byte (C1).

- Synthesizes the 155.52 MHz, 51.84 MHz transmit clock from a one-eighth frequency reference.

- Inserts path alarm indication signal (PAIS), path remote defect indication (RDI), line alarm indication signal (LAIS) and line RDI.

- Inserts path BIP-8 codes (B3), path far end block error (path FEBE) indications, line BIP-8/24 codes (B2), line far end block error (line FEBE) indications, section BIP-8 codes (B1) to allow performance monitoring at the far end.

- Allows forced insertion of all zeros data (after scrambling) or corruption of framing byte or section, line, or path BIP-8 codes for diagnostic purposes.

SATURN USER NETWORK INTERFACE

#### 2 **APPLICATIONS**

- ATM LANs over twisted pair cables (UTP-5) at155.52 Mbit/s •

- ATM LANs over optical fibers (using PECL ODLs) at either 155 Mbit/s or 51.84 Mbit/s

- Workstations and Personal Computer NIC Cards

- LAN switches and hubs •

- SONET or SDH compliant ATM User-Network Interfaces

SATURN USER NETWORK INTERFACE

#### 3 **REFERENCES**

- 1. CCITT Recommendation G.709 "Synchronous Multiplexing Structure", 1990.

- 2. CCITT Recommendation I.432, "B-ISDN User Network Interface Physical Interface Specification", June 1990.

- 3. Bell Communications Research SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 1, December 1994.

- 4. ATM Forum ATM User-Network Interface Specification, V3.1, September 1994

- 5. ATM Forum ATM Physical Medium Dependent Interface Specification for 155 Mbit/s over Twister Pair Cable, V1.0, September 1994

- 6. T1.105, American National Standard for Telecommunications Digital Hierarchy - Optical Interface Rates and Formats Specifications (SONET), 1991.

- 7. Telecommunications Industry Association (TIA), Commercial Building Telecommunications Wiring Standard, EIA/TIA-568.

ISSUE 5

SATURN USER NETWORK INTERFACE

#### **APPLICATION EXAMPLES** 4

The PM5350 S/UNI-ULTRA is typically used to implement the core of an ATM User Network Interface by which an ATM terminal is linked to an ATM switching system using SONET/SDH compatible transport.

The S/UNI-ULTRA finds application at either end of terminal to switch links or switch to switch links, typically in private network (LAN) applications. In this application, the S/UNI-ULTRA typically interfaces on its line side with line coupling transformers and baluns.

The S/UNI-ULTRA may be loop timed internally (the recovered clock is used in the transmit direction) or source timed (separate transmit and receive clocks). The drop side interfaces directly with ATM adaptation layer or ATM layer processors. The initial configuration and ongoing control and monitoring of the S/UNI-ULTRA is provided via a generic microprocessor interface. The S/UNI-ULTRA also supports a "hardware-only" operating mode where an external microprocessor is not required. This application is shown in Figure 1.

#### Figure 1 - Typical ATM Adapter UTP-5 Interface

PMC-Sierra, Inc.

ISSUE 5

SATURN USER NETWORK INTERFACE

#### Description

The PM5350 S/UNI-ULTRA Saturn User Network Interface is a monolithic integrated circuit that implements the SONET/SDH processing and ATM mapping functions of a 155 Mbit/s or 51Mbit/s ATM User Network Interface. It is fully compliant with both SONET and SDH requirements and ATM Forum UNI specifications.

The S/UNI-ULTRA is capable of directly interfacing with UTP-5 cable. At the receiver end, it performs adaptive equalization. It is fully compliant with the ATM Forum PMD Interface specifications for 155 Mb/s over twisted pair cable.

The S/UNI-ULTRA receives SONET/SDH frames via a bit serial interface, recovers clock and data, and processes section, line, and path overhead. It

PM5350 S/UNI-ULTRA

ISSUE 5

SATURN USER NETWORK INTERFACE

performs framing (A1, A2), descrambling, detects alarm conditions, and monitors section, line, and path bit interleaved parity (B1, B2, B3), accumulating error counts at each level for performance monitoring purposes. Line and path far end block error indications (M0 or M1, G1) are also accumulated. The S/UNI-ULTRA interprets the received payload pointers (H1, H2) and extracts the synchronous payload envelope which carries the received ATM cell payload.

The S/UNI-ULTRA frames to the ATM payload using cell delineation. HCS error correction is provided. Idle/unassigned cells may be dropped according to a programmable filter. Cells are also dropped upon detection of an uncorrectable header check sequence error. The ATM cell payloads are descrambled. Generic flow control (GFC) bits from error free cells are extracted and presented on a serial link for external processing.

Legitimate ATM cells are written to a four cell FIFO buffer. These cells are read from the FIFO using a synchronous 8 bit wide datapath interface with cell-based handshake. Counts of received ATM cell headers that are errored and uncorrectable, those that are errored and correctable and all passed cells are accumulated independently for performance monitoring purposes.

The S/UNI-ULTRA transmits SONET/SDH frames via a bit serial interface and formats section, line, and path overhead appropriately. It performs framing pattern insertion (A1, A2), scrambling, alarm signal insertion, and creates section, line, and path bit interleaved parity (B1, B2, B3) as required to allow performance monitoring at the far end. Line and path far end block error indications (M0 or M1, G1) are also inserted.

The S/UNI-ULTRA generates the payload pointer (H1, H2) and inserts the synchronous payload envelope which carries the ATM cell payload. It supports the insertion of a variety of errors into the transmit stream, such as framing pattern errors, bit interleaved parity errors, and illegal pointers, which are useful for system diagnostics.

ATM cells are written to an internal programmable-length 4-cell FIFO using a synchronous 8 bit wide datapath interface. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one cell or the XOFF input is asserted. Generic flow control (GFC) bits may be inserted downstream of the FIFO via a serial link so that all FIFO latency may be bypassed. A transmission off (XOFF) input is provided to allow the suspension of active ATM cell transmission independent of the FIFO fill state.

The S/UNI-ULTRA generates the header check sequence and scrambles the payload of the ATM cells. Payload scrambling can be disabled.

SATURN USER NETWORK INTERFACE

No line rate clocks are required directly by the S/UNI-ULTRA as it synthesizes the transmit clock and recovers the receive clock using a 19.44 MHz reference clock.

The S/UNI-ULTRA provides output control signals that can be used to command an LED display, making it easy to visually monitor either alarms, or the transmit and receive activity.

The S/UNI-ULTRA is configured, controlled and monitored via a generic 8-bit microprocessor bus interface. It is implemented in low power, +5 Volt CMOS technology. It has TTL and pseudo-ECL (PECL) compatible inputs and outputs and is packaged in a 128 pin PQFP package.

| <u>P</u> | M | IC | PMC-Sierra, |

|----------|---|----|-------------|

|          |   |    |             |

ISSUE 5

SATURN USER NETWORK INTERFACE

#### 6 PIN DIAGRAM

The S/UNI-ULTRA is packaged in an 128 pin PQFP package having a body size of 14 mm by 20 mm and a pin pitch of 0.50 mm.

Inc.

ISSUE 5

SATURN USER NETWORK INTERFACE

## 7 PIN DESCRIPTION

| Pin Name     | Туре                     | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                              |

|--------------|--------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PECLSEL      | TTL Input                | 40         | The PECL mode select (PECLSEL) is used to<br>configure the Analog Edge PMD interface for<br>either PECL or Twisted-pair. A TTL low<br>configures the interface for while a TTL high<br>configures the interface for PECL, enabling<br>direct interfacing with optical transceivers.                                   |

|              |                          |            | Refer to the OPERATION section for a detailed<br>description of Twisted-Pair mode and PECL<br>mode configurations. Different termination at<br>TXD+/- and RXD+/- are required depending on<br>the selected mode.                                                                                                      |

| RXD+<br>RXD- | Diff.<br>Analog<br>Input | 24<br>23   | The differential receiver inputs (RXD+/-) NRZ<br>data, from the balun/transformer module<br>interface to these pins when operating in<br>Twisted-pair mode (as configured via the<br>PECLSEL pin tied low), or from an optical data<br>link (ODL) when in PECL mode (as configured<br>via the PECLSEL pin tied high). |

|              |                          |            | RXD+/- are truly differential inputs offering<br>superior common-mode noise rejection. Refer<br>to the APPLICATIONS section of this<br>document for a description of the required<br>termination network.                                                                                                             |

| REFCLK       | TTL Input                | 2          | The reference clock input (REFCLK) must<br>provide a jitter-free 19.44 MHz reference clock.<br>It is used as the reference clock by both clock<br>recovery and clock synthesis circuits.                                                                                                                              |

PM5350 S/UNI-ULTRA

DATA SHEET PMC-960924

ISSUE 5

| Pin Name | Туре                              | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-----------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SD       | Single-<br>Ended<br>PECL<br>Input | 29         | The Signal Detect pin (SD) indicates the presence of valid receive signal power from the Optical Physical Medium Dependent Device when operating in PECL mode (as configured via the PECLSEL pin tied high). A PECL high indicates the presence of valid data and a PECL low indicates a loss of signal. It is mandatory that SD be terminated into the equivalent network that RXD+/- is terminated into. |

|          |                                   |            | When operated in Twisted-pair mode (as configured via the PECLSEL pin tied low), SD has no function and should be connected to the analog ground common to RAVS3.                                                                                                                                                                                                                                          |

| RCLK     | Output                            | 55         | The receive clock (RCLK) output provides a timing reference for the S/UNI-ULTRA receive outputs. RCLK is a divide by eight of the recovered line rate clock. RGFC, RCP, RFP and OUT[1] (when configured for alarm monitoring) are updated on the rising edge of RCLK.                                                                                                                                      |

| PMC-Sierra, Inc. |

|------------------|

|------------------|

ISSUE 5

| Pin Name         | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT[1]<br>OUT[0] | Output | 41<br>42   | The alarm/output port pins has three functions as selected by POPC control register bits.                                                                                                                                                                                                                                                                                                                      |

|                  |        |            | When configured to output alarms, the OUT[1]<br>output indicates a receive alarm (RALM<br>function) based on the state of the receive<br>framer. OUT[1] is low if no receive alarms are<br>active. OUT[1] is high if an alarm condition is<br>detected. OUT[1] is updated on the rising<br>edge of RCLK. In this operation mode OUT[0]<br>is used as a single bit parallel output port, as<br>described below. |

|                  |        |            | When configured as a parallel output port,<br>OUT[1] and OUT[0] can be used to control the<br>operation of external devices. The signal levels<br>on the output port are determined by register<br>bits.                                                                                                                                                                                                       |

|                  |        |            | When configured as a traffic indicator port,<br>OUT[1] indicates the receive traffic activity and<br>OUT[0] indicates the transmit traffic activity. In<br>this operation mode OUT[1] and OUT[0]<br>pulses high fom 100ms on cell receive and<br>transmit events and can be used to control an<br>LED display.                                                                                                 |

| RFP              | Output | 56         | The receive frame pulse (RFP) output, when<br>the framing alignment has been found (the<br>OOF register bit is logic 0), is an 8 kHz signal<br>derived from the receive line clock. RFP<br>pulses high for one RCLK cycle every 2430<br>RCLK cycles for STS-3c (STM-1) rate or every<br>810 RCLK cycles for STS-1 rate. RFP is<br>updated on the rising edge of RCLK.                                          |

ISSUE 5

| Pin Name     | Туре                      | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------|---------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXD+<br>TXD- | Diff.<br>Analog<br>Output | 12<br>13   | The transmit differential data/positive pulse<br>outputs (TXD+, TXD-) contain NRZ encoded<br>data. These outputs are open drain current<br>sinks which interface directly with the Twisted-<br>pair network or with an Optical Interface<br>Module requiring PECL levels.                                                                                                                                                                                                                                                                                            |

|              |                           |            | Refer to the APPLICATIONS section of this document for a description of the required termination network.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TFP          | I/O                       | 58         | The active high framing position (TFP) signal is<br>an 8 kHz timing marker for the transmitter. TFP<br>defaults to being an input and is used to align<br>the SONET/SDH transport frame generated by<br>the S/UNI-ULTRA device to a system<br>reference. TFP should be brought high for a<br>single TCLK period every 810 (STS-1) or 2430<br>(STS-3/STM-1) TCLK cycles, or a multiple<br>thereof. TFP may be tied low if such<br>synchronization is not required. TFP is<br>sampled on the rising edge of TCLK. TFP must<br>not be used as an input when loop-timed. |

|              |                           |            | When selected as an output through the interface configuration register, TFP pulses high for one TCLK cycle every 2430 TCLK cycles for STS-3c (STM-1) rate or every 810 TCLK cycles for STS-1 rate. TFP is updated on the rising edge of TCLK.                                                                                                                                                                                                                                                                                                                       |

ISSUE 5

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSEN     | Input | 59         | The tristate enable (TSEN) input selects the<br>configuration of the receive datapath<br>(RDAT[7:0], RXPRTY and RSOC). When<br>TSEN is tied high, RDAT[7:0] operates as a<br>tristate bus controlled by RRDENB. When<br>RRDENB is high upon RFCLK rising,<br>RDAT[7:0], RXPRTY and RSOC are tristated.<br>When RRDENB is low upon RFCLK rising,<br>RDAT[7:0], RXPRTY and RSOC are enabled.<br>When TSEN is tied low, RDAT[7:0], RXPRTY<br>and RSOC are always enabled, regardless of<br>the state of RRDENB.                                                                                                                                                                                                                                            |

| RFCLK    | Input | 66         | The receive read clock (RFCLK) is used to<br>read ATM cells from the receive FIFO. RFCLK<br>must cycle at a high enough rate to avoid FIFO<br>overflow. RRDENB is sampled using the rising<br>edge of RFCLK. RSOC, RDAT[7:0], RXPRTY<br>and RCA are updated on the rising edge of<br>RFCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RRDENB   | Input | 67         | The active low receive read enable input<br>(RRDENB) is used to initiate reads from the<br>receive FIFO. When sampled low using the<br>rising edge of RFCLK, a byte is read from the<br>internal synchronous FIFO and output on bus<br>RDAT[7:0] if one is available. When sampled<br>high using the rising edge of RFCLK, no read<br>is performed and RDAT[7:0] and RSOC are<br>tristated if the TSEN input is high. RRDENB<br>must operate in conjunction with RFCLK to<br>access the FIFO at a high enough<br>instantaneous rate as to avoid FIFO overflows.<br>The ATM layer device may deassert RRDENB<br>at anytime it is unable to accept another byte.<br>When the RCA signal is configured to be<br>deasserted with zero octets (as opposed to |

|          |       |            | deasserted with zero octets (as opposed to four) in the FIFO, the RCA signal identifies the valid octets.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

ISSUE 5

| Pin Name                                                                  | Туре               | Pin<br>No.                             | Function                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------------------------|--------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDAT[0]<br>RDAT[1]<br>RDAT[2]<br>RDAT[3]<br>RDAT[4]<br>RDAT[5]<br>RDAT[6] | Tristate<br>Output | 69<br>70<br>73<br>74<br>75<br>76<br>77 | The receive cell data (RDAT[7:0]) bus carries<br>the ATM cell octets that are read from the<br>receive FIFO. RDAT[7:0] is updated on the<br>rising edge of RFCLK and is tristated when not<br>valid if the TSEN input is high. The RDAT[7:0]<br>bus is always driven when TSEN is low,<br>regardless of the level of RRDENB.                                                    |

| RDAT[7]<br>RXPRTY                                                         | Tristate<br>Output | 78<br>81                               | The receive parity (RXPRTY) signal indicates<br>the parity of the RDAT[7:0] bus. Odd or even<br>parity selection can be made using a register.<br>RXPRTY is updated on the rising edge of<br>RFCLK and is tristated when not valid if the<br>TSEN input is high. RXPRTY is always driven<br>when TSEN is low, regardless of the level of<br>RRDENB.                             |

| RSOC                                                                      | Tristate<br>Output | 82                                     | The receive start of cell (RSOC) signal marks<br>the start of cell on the RDAT[7:0] bus. When<br>RSOC is high, the first octet of the cell is<br>present on the RDAT[7:0] stream. RSOC is<br>updated on the rising edge of RFCLK and is<br>tristated when not valid if the TSEN input is<br>high. RSOC is always driven when TSEN is<br>low, regardless of the level of RRDENB. |

| RCA                                                                       | Output             | 68                                     | The receive cell available (RCA) signal<br>indicates when a cell is available in the receive<br>FIFO. RCA can be configured to be<br>deasserted when either zero or four bytes<br>remain in the FIFO. RCA is updated on the<br>rising edge of RFCLK. The active polarity of<br>this signal is programmable and defaults to<br>active high.                                      |

ISSUE 5

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RGFC     | Output | 57         | The receive generic flow control (RGFC)<br>output presents the extracted GFC bits in a<br>serial stream. The four GFC bits are presented<br>for each received cell, with the RCP output<br>indicating the position of the most significant<br>bit. The updating of RGFC by particular GFC<br>bits may be disabled through the RACP<br>Configuration register. The serial link is forced<br>low if cell delineation is lost. RGFC is updated<br>on the rising edge of RCLK. |

| RCP      | Output | 49         | The receive cell pulse (RCP) indicates the location of the four GFC bits in the RGFC serial stream. RCP is coincident with the most significant GFC bit. RCP is updated on the rising edge of RCLK.                                                                                                                                                                                                                                                                        |

| TCLK     | Output | 52         | The transmit byte clock (TCLK) output provides<br>a timing reference for S/UNI-ULTRA transmit<br>outputs. TCLK is a divide by eight of the<br>synthesized line rate clock. TGFC, TCP and<br>TFP are sampled on the rising edge of TCLK.                                                                                                                                                                                                                                    |

| TFCLK    | Input  | 86         | The transmit write clock (TFCLK) is used to<br>write ATM cells to the four cell transmit FIFO.<br>A complete 53 octet cell must be written to the<br>FIFO before being inserted in the synchronous<br>payload envelope (SPE). Idle/unassigned cells<br>are inserted when a complete cell is not<br>available. TDAT[7:0], TXPRTY, TWRENB and<br>TSOC are sampled on the rising edge of<br>TFCLK. TCA is updated on the rising edge of<br>TFCLK.                             |

ISSUE 5

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|-------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDAT[0]  | Input | 88         | The transmit cell data (TDAT[7:0]) bus carries                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TDAT[1]  |       | 89         | the ATM cell octets that are written to the                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TDAT[2]  |       | 90         | transmit FIFO. TDAT[7:0] is sampled on the<br>rising edge of TFCLK and is considered valid                                                                                                                                                                                                                                                                                                                                                                                                        |

| TDAT[3]  |       | 91         | only when TWRENB is simultaneously                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TDAT[4]  |       | 92         | asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TDAT[5]  |       | 93         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TDAT[6]  |       | 94         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TDAT[7]  |       | 95         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TXPRTY   | Input | 96         | The transmit parity (TXPRTY) signal indicates<br>the parity of the TDAT[7:0] bus. Odd or even<br>parity selection can be made using a register<br>bit. TXPRTY is sampled on the rising edge of<br>TFCLK and is considered valid only when<br>TWRENB is simultaneously asserted.<br>A parity error is indicated by a status bit and a<br>maskable interrupt. Cells with parity errors are                                                                                                          |

|          |       |            | not filtered, so the TXPRTY input may be<br>unused.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TWRENB   | Input | 87         | The active low transmit write enable input<br>(TWRENB) is used to initiate writes to the<br>transmit FIFO. When sampled low using the<br>rising edge of TFCLK, the byte on TDAT[7:0] is<br>written into the transmit FIFO. When sampled<br>high using the rising edge of TFCLK, no write<br>is performed. A complete 53 octet cell must be<br>written to the transmit FIFO before it is<br>inserted into the SPE. Idle/unassigned cells<br>are inserted when a complete cell is not<br>available. |

| DATA SHEET |  |

|------------|--|

| PMC-960924 |  |

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TSOC     | Input  | 97         | The transmit start of cell (TSOC) signal marks<br>the start of cell on the TDAT[7:0] bus. When<br>TSOC is high, the first octet of the cell is<br>present on the TDAT[7:0] stream. It is not<br>necessary for TSOC to be present at each cell.<br>An interrupt may be generated if TSOC is high<br>during any byte other than the first byte. TSOC<br>is sampled on the rising edge of TFCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TCA      | Output | 83         | The transmit cell available (TCA) signal<br>indicates when a cell is available in the<br>transmit FIFO. When high, TCA indicates that<br>the transmit FIFO is not full and a complete<br>cell may be written in. When TCA goes low, it<br>indicates either that the transmit FIFO is near<br>full and can accept no more than four writes or<br>that the transmit FIFO is full. Selection is<br>made using a register bit in the TACP FIFO<br>Control register. To reduce FIFO latency, the<br>FIFO depth at which TCA indicates "full" can<br>be set to one, two, three or four cells by the<br>TACP FIFO Control register. If the<br>programmed depth is less than four, additional<br>cells may be written after TCA is deasserted.<br>TCA is updated on the rising edge of TFCLK.<br>The active polarity of this signal is<br>programmable and defaults to active high. |

| XOFF     | Input  | 45         | The transmit off (XOFF) input prevents the<br>insertion of cells from the transmit FIFO. If<br>XOFF is asserted high, the next cell<br>transmitted is an idle/unassigned cell<br>regardless of the number of cells in the FIFO.<br>Idle/unassigned cells are transmitted until<br>XOFF is deasserted. XOFF may be treated as<br>an asynchronous signal.<br>When the device in set in production test mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |        |            | (Master Test Register PMCTST bit set to logic<br>1) XOFF is used as the test vector clock<br>(VCLK) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

ISSUE 5

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TGFC     | Input  | 51         | The transmit generic flow control (TGFC) input<br>provides the ability to insert the GFC value.<br>The four TCLK periods following the TCP<br>output pulse contain the GFC value to be<br>inserted into the current cell. The GFC enable<br>bits of the TACP Configuration register enable<br>the insertion of each serial bit. By default, the<br>GFC values are the contents of the TACP<br>Idle/Unassigned Cell Header Control register<br>for idle/unassigned cells and the value<br>received from TDAT[7:0] for assigned cells.<br>TGFC is sampled on the rising edge of TCLK. |

| TCP      | Output | 50         | The transmit cell pulse (TCP) indicates where<br>the valid TGFC serial bits are expected. If TCP<br>is asserted high, the most significant GFC bit<br>is expected in the subsequent TCLK period.<br>TCP pulses high for one TCLK for every<br>transmitted cell six payload octets before the<br>first octet of the cell read from the transmit<br>FIFO, or the idle cell if the FIFO is empty. TCP<br>is updated on the rising edge of TCLK.                                                                                                                                        |

| TRREF    | Analog | 19         | The reference resistor (TRREF) input is<br>connected to an off-chip precision resistor<br>RREF to produce calibrated currents for the<br>TXD+/- outputs. The resistor should be<br>connected between TRREF and TAVS4.                                                                                                                                                                                                                                                                                                                                                               |

|          |        |            | Please refer to the APPLICATIONS and the EXTERNAL COMPONENTS sections of this document for a detailed RREF specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

ISSUE 5

| Pin Name       | Туре   | Pin<br>No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|--------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TVREF          | Analog | 18         | The reference voltage (TVREF) is optionally<br>used to produce calibrated currents for the<br>TXD +/- outputs. In order to meet tight<br>amplitude tolerances over process,<br>temperature and supply, a precise reference<br>voltage generator VREF is required. The other<br>terminal of the reference generator should be<br>connected to TAVS4. If this pin is unused, this<br>input should be connected to analog TAVS4.                                                           |

|                |        |            | Please refer to the APPLICATIONS and the EXTERNAL COMPONENTS sections of this document for a detailed VREF specification.                                                                                                                                                                                                                                                                                                                                                               |

| RCAP1<br>RCAP2 | Analog | 27<br>28   | The RCAP1 and RCAP2 pins should be connected to the RAVS3 analog ground.                                                                                                                                                                                                                                                                                                                                                                                                                |

| ATP1<br>ATP2   | Analog | 7<br>33    | Two analog test points (ATP1, ATP2) are<br>provided for production test purposes. These<br>pins must be connected to analog ground<br>during normal operation.                                                                                                                                                                                                                                                                                                                          |

| CSB            | Input  | 100        | The active low chip select (CSB) signal is low<br>during S/UNI-ULTRA register accesses. If CSB<br>is used, it must be held high while RSTB is low<br>to properly initialize the device. If CSB is not<br>required (i.e. register accesses are controlled<br>using the RDB and WRB signals only), CSB<br>must be connected to an inverted version of<br>the RSTB input to ensure proper device<br>initialization. CSB is a Schmitt triggered input<br>with an integral pull up resistor. |

| RDB            | Input  | 99         | The active low read enable (RDB) signal is low<br>during S/UNI-ULTRA register read accesses.<br>The S/UNI-ULTRA drives the D[7:0] bus with<br>the contents of the addressed register while<br>RDB and CSB are low.                                                                                                                                                                                                                                                                      |

ISSUE 5

| Pin Name | Туре  | Pin<br>No. | Function                                                                                                                                                                                                           |

|----------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WRB      | Input | 98         | The active low write strobe (WRB) signal is low<br>during a S/UNI-ULTRA register write accesses.<br>The D[7:0] bus contents are clocked into the<br>addressed register on the rising WRB edge<br>while CSB is low. |

| D[0]     | I/O   | 108        | The bidirectional data bus D[7:0] is used                                                                                                                                                                          |

| D[1]     |       | 109        | during S/UNI-ULTRA register read and write accesses.                                                                                                                                                               |

| D[2]     |       | 110        |                                                                                                                                                                                                                    |

| D[3]     |       | 111        |                                                                                                                                                                                                                    |

| D[4]     |       | 114        |                                                                                                                                                                                                                    |

| D[5]     |       | 115        |                                                                                                                                                                                                                    |

| D[6]     |       | 116        |                                                                                                                                                                                                                    |

| D[7]     |       | 117        |                                                                                                                                                                                                                    |

| A[0]     | Input | 120        | The address bus A[7:0] selects specific                                                                                                                                                                            |

| A[1]     |       | 121        | registers during S/UNI-ULTRA register accesses.                                                                                                                                                                    |

| A[2]     |       | 122        |                                                                                                                                                                                                                    |

| A[3]     |       | 123        |                                                                                                                                                                                                                    |

| A[4]     |       | 124        |                                                                                                                                                                                                                    |

| A[5]     |       | 125        |                                                                                                                                                                                                                    |

| A[6]     |       | 126        |                                                                                                                                                                                                                    |

| A[7]/TRS |       | 127        | The test register select (TRS) signal selects<br>between normal and test mode register<br>accesses. TRS is high during test mode<br>register accesses, and is low during normal<br>mode register accesses.         |

| RSTB     | Input | 101        | The active low reset (RSTB) signal provides an asynchronous S/UNI-ULTRA reset. RSTB is a Schmitt triggered input with an integral pull up resistor.                                                                |

PM5350 S/UNI-ULTRA

DATA SHEET PMC-960924

ISSUE 5

| Pin Name | Туре                     | Pin | Function                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                          | No. |                                                                                                                                                                                                                                                                                                                                                                                                      |

| ALE      | Input                    | 104 | The address latch enable (ALE) is active high<br>and latches the address bus A[7:0] when low.<br>When ALE is high, the internal address latches<br>are transparent. It allows the S/UNI-ULTRA to<br>interface to a multiplexed address/data bus.                                                                                                                                                     |

| INTB     | Open-<br>Drain<br>Output | 107 | The active low interrupt (INTB) signal goes low<br>when a S/UNI-ULTRA interrupt source is<br>active, and that source is unmasked. The<br>S/UNI-ULTRA may be enabled to report many<br>alarms or events via interrupts. INTB returns<br>high when the interrupt is acknowledged via an<br>appropriate register access. INTB is an open<br>drain output and must have an external pull-up<br>resistor. |

| VDDI1    | Power                    | 44  | The core power (VDDI1 - VDDI5) pins should                                                                                                                                                                                                                                                                                                                                                           |

| VDDI2    |                          | 60  | be connected to a well decoupled +5 V DC in common with VDDO.                                                                                                                                                                                                                                                                                                                                        |

| VDDI3    |                          | 85  |                                                                                                                                                                                                                                                                                                                                                                                                      |

| VDDI4    |                          | 106 |                                                                                                                                                                                                                                                                                                                                                                                                      |