Data Sheet, Version 4.0, June 07

# TDA5230 TDA5231 Universal Low Power ASK/FSK Single Conversion Multi-Channel Image-Reject Receiver with Digital Baseband Processing

Wireless Control Components

Never stop thinking.

Edition 2007-06-01 Published by Infineon Technologies AG, Am Campeon 1-12, 85579 Neubiberg, Germany © Infineon Technologies AG 2007. All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or the Infineon Technologies Companies and our Infineon Technologies Representatives worldwide (www.infineon.com).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# TDA5230 TDA5231

Universal Low Power ASK/FSK Single Conversion Multi-Channel Image-Reject Receiver with Digital Baseband Processing

Wireless Control Components

Never stop thinking.

#### TDA523x

#### Revision History: 2007-06-01

| Previous                                                                     | Version: | TDA5230 Preliminary Data Sheet V2.01                                                                                                                                                                                                                                                       |  |

|------------------------------------------------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PagePageSubjects (changes since previous revision)prev.currentversionversion |          |                                                                                                                                                                                                                                                                                            |  |

| all                                                                          | all      | Rework of all chapters<br>Product description enhanced by additional short form information<br>Functional description, explanations added, full SFR information in<br>each chapter<br>Reference: some characteristics added, FSK demodulator BW<br>changed to practical measurement method |  |

| Previous                 | s Version:                 | TDA523x Data Sheet V3.0                                                                                                                                   |

|--------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Page<br>prev.<br>version | Page<br>current<br>version | Subjects (changes since previous revision)                                                                                                                |

|                          | 4                          | IF MUX added in Chapter 1 Product Description, Chapter 2.4.8.1<br>IF Filter, and Dual: AIF0 and BIF0: Conf. A IF Buffer Amplifier<br>Enable               |

| 51                       | 51                         | Explanation for T <sub>ON</sub> and T <sub>OFF</sub> from Chapter 2.4.6.2 Constant<br>On/Off Time to Chapter 2.4.6.5 Permanent Wake Up Search<br>improved |

| 125                      | 127                        | Description Digital I/O pins corrected                                                                                                                    |

| 134                      | 135                        | Reset Value for register CMC0 corrected                                                                                                                   |

|                          | 163                        | Minimum SPM cycletime (T <sub>ON</sub> +T <sub>OFF</sub> ) specified                                                                                      |

| 4                        | 4                          | AEC Q100 added                                                                                                                                            |

|                          | 5                          | Order information added                                                                                                                                   |

| all                      | all                        | Spelling corrections                                                                                                                                      |

#### We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all? Your feedback will help us to continuously improve the quality of this document. Please send your proposal (including a reference to this document) to: sensors@infineon.com

| 1       | Product Description                                         | 4  |

|---------|-------------------------------------------------------------|----|

| 1.1     | Overview                                                    | 4  |

| 1.2     | Key Features                                                | 4  |

| 1.3     | Applications                                                | 4  |

| 1.4     | Order Information                                           | 5  |

| 1.5     | Target Application Frequencies for TDA5230 and TDA5231      | 5  |

| 1.6     | Major Key-Features of TDA5230 and TDA5231                   | 6  |

| 1.6.1   | Typical Application Circuit                                 | 6  |

| 1.6.2   | Baseband Processing                                         | 7  |

| 1.6.3   | Autonomous Self Polling                                     | 7  |

| 1.6.4   | Two Independent Receiver Configuration Sets                 | 8  |

| 1.6.5   | Multi-Channel PLL Receiver Supports up to 17 Subchannels    |    |

| 1.6.6   | Support Software and Evaluation Boards                      | 9  |

| 1.6.6.1 | The IAF TDA523x Configuration Tool                          | 9  |

| 1.6.6.2 | The TDA523x Explorer                                        | 10 |

| 1.6.6.3 | Evaluation Boards                                           | 10 |

| 2       | Functional Description                                      | 11 |

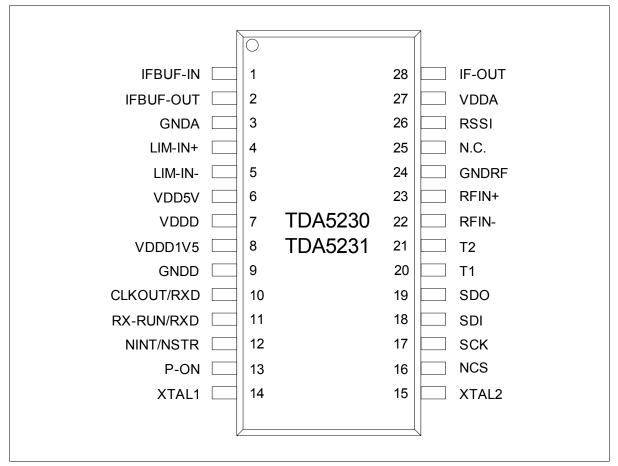

| 2.1     | Pin Configuration                                           | 11 |

| 2.2     | Pin Definition and Functions                                | 12 |

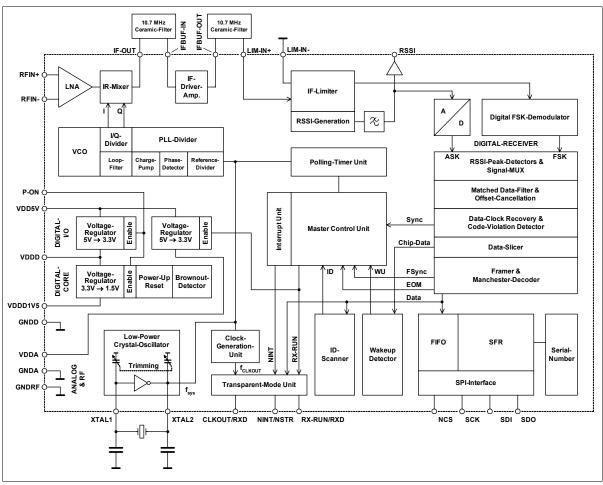

| 2.3     | Functional Block Diagram                                    | 16 |

| 2.4     | Functional Block Description                                | 16 |

| 2.4.1   | Power Supply                                                | 18 |

| 2.4.1.1 | Supply Current                                              | 19 |

| 2.4.2   | Chip Reset                                                  | 21 |

| 2.4.3   | System Clock                                                | 23 |

| 2.4.3.1 | Crystal Oscillator                                          | 23 |

| 2.4.3.2 | External Clock Generation Unit                              | 25 |

| 2.4.4   | RF-PLL Synthesizer                                          | 28 |

| 2.4.5   | Master Control Unit                                         | 33 |

| 2.4.5.1 | Overview                                                    | 33 |

| 2.4.5.2 | Run Mode Slave                                              | 35 |

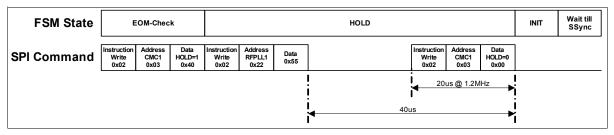

| 2.4.5.3 | HOLD Mode                                                   | 38 |

| 2.4.5.4 | SLEEP Mode                                                  | 38 |

| 2.4.5.5 | Self Polling Mode                                           | 39 |

| 2.4.5.6 |                                                             | 43 |

| 2.4.5.7 | Multi-channel in Self Polling Mode                          | 44 |

| 2.4.5.8 | Run Mode Self Polling                                       | 46 |

| 2.4.6   | Polling Timer Unit                                          | 50 |

| 2.4.6.1 | Self Polling Modes                                          |    |

| 2.4.6.2 | Constant On/Off Time                                        |    |

| 2.4.6.3 | Fast Fall Back To Sleep                                     | 54 |

| 2.4.6.4 | Mixed Mode (Constant On/Off Time & Fast Fall Back to Sleep) | 56 |

|         |                                                             |    |

| 2.4.6.5                                                                                                  | Permanent Wake Up Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 58                                                                                           |

|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2.4.6.6                                                                                                  | Active Idle Period Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59                                                                                           |

| 2.4.7                                                                                                    | RF Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 2.4.7.1                                                                                                  | RX-RUN/RXD Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 63                                                                                           |

| 2.4.8                                                                                                    | Functionality of the IF Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                           |

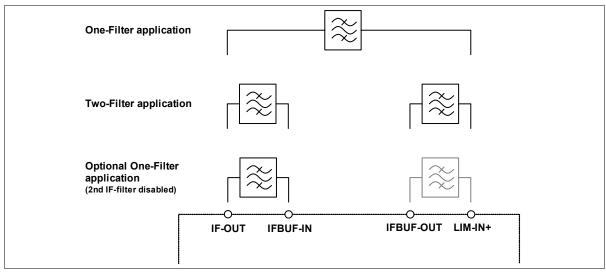

| 2.4.8.1                                                                                                  | IF Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 65                                                                                           |

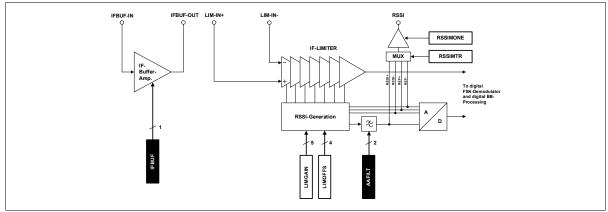

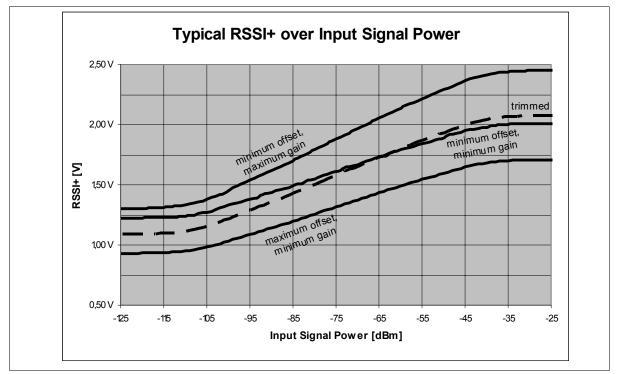

| 2.4.8.2                                                                                                  | Limiter, RSSI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 66                                                                                           |

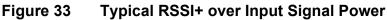

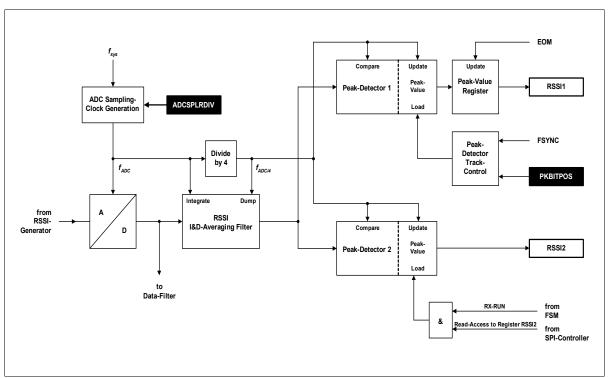

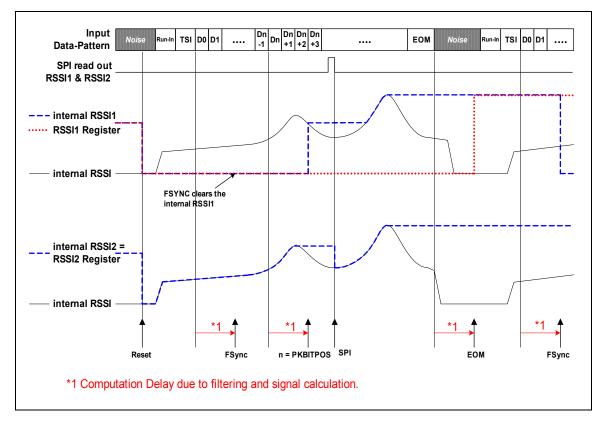

| 2.4.8.3                                                                                                  | RSSI Peak Detector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71                                                                                           |

| 2.4.9                                                                                                    | Digital Receiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75                                                                                           |

| 2.4.9.1                                                                                                  | Synchronization Search Time and Inter-Frame Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 75                                                                                           |

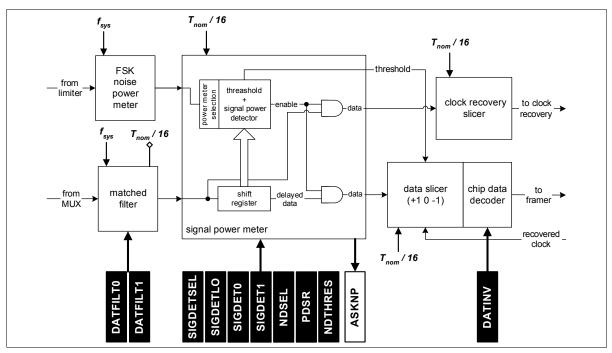

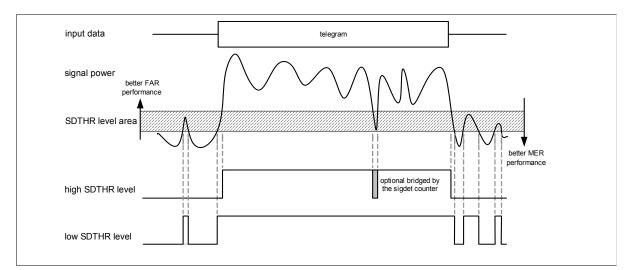

| 2.4.9.2                                                                                                  | Data Filter and Signal Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

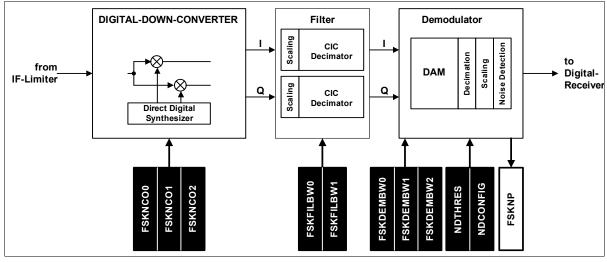

| 2.4.10                                                                                                   | Digital FSK Demodulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

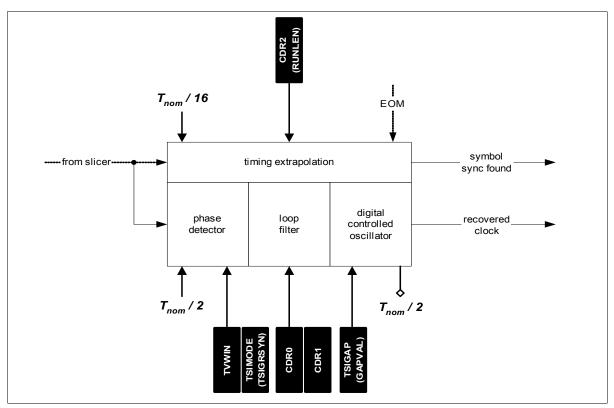

| 2.4.11                                                                                                   | Clock Recovery                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                              |

| 2.4.12                                                                                                   | Wake Up Generation Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                              |

| 2.4.13                                                                                                   | Frame Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

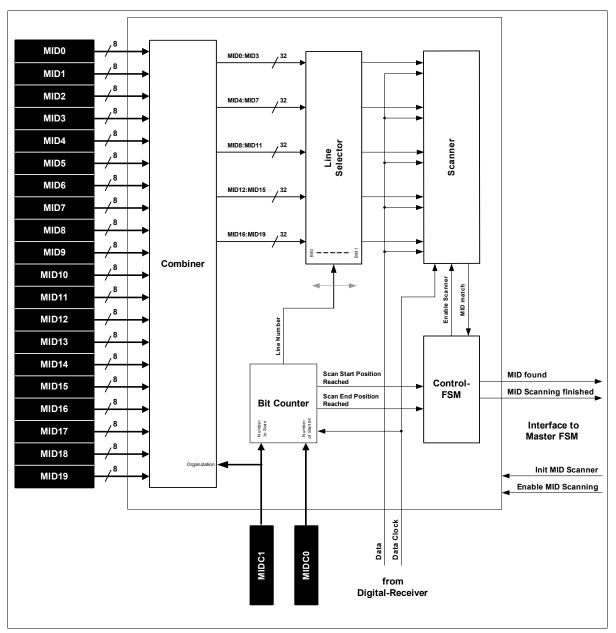

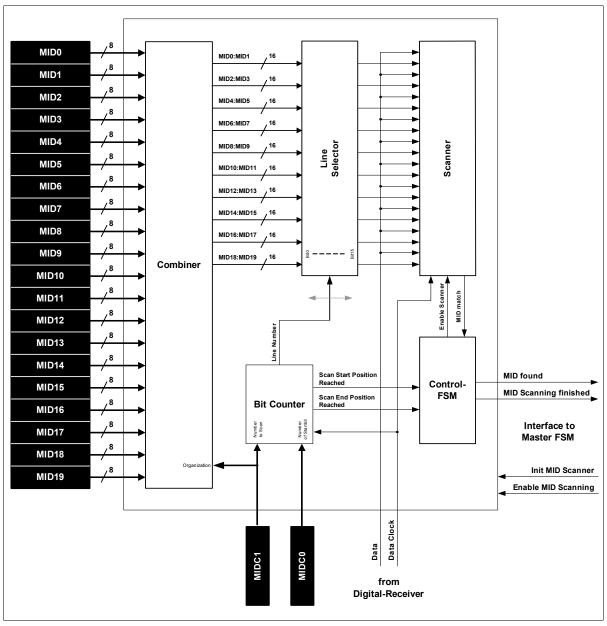

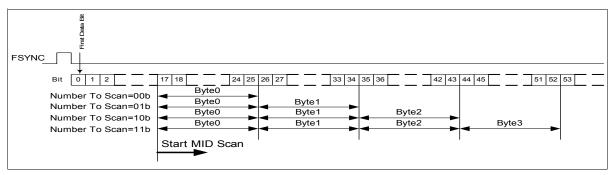

| 2.4.14                                                                                                   | Message-ID Scanning 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                              |

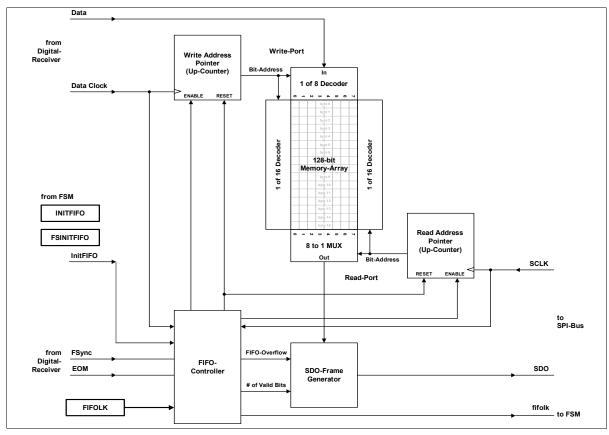

| 2.4.15                                                                                                   | Data FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 2.4.16                                                                                                   | Transparent Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                              |

| 2.4.17                                                                                                   | Interrupt Generation Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

| 2.4.18                                                                                                   | SPI Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                              |

| 2.4.19                                                                                                   | Chip Serial Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                              |

| 2.4.20                                                                                                   | Digital Input/Output Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                              |

|                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>Z</b> I                                                                                   |

| -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                              |

| 3                                                                                                        | Register Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28                                                                                           |

| -                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 28                                                                                           |

| 3                                                                                                        | Register Descriptions       1         Detailed register descriptions       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 28<br>35                                                                                     |

| <b>3</b><br>3.1                                                                                          | Register Descriptions       12         Detailed register descriptions       13         Specifications       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28<br>35<br>62                                                                               |

| <b>3</b><br>3.1<br><b>4</b>                                                                              | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28<br>35<br>62<br>62                                                                         |

| <b>3</b><br>3.1<br><b>4</b><br>4.1                                                                       | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28<br>35<br>62<br>62<br>62                                                                   |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1                                                                                                                                                                                                                                                                                                                                                                                                                 | 28<br>35<br>62<br>62<br>62<br>63                                                             |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1                                                              | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1                                                                                                                                                                                                                                                                                                                                                                           | 28<br>35<br>62<br>62<br>63<br>63                                                             |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         General       1                                                                                                                                                                                                                                                                                                                                                   | 28<br>35<br>62<br>62<br>63<br>63<br>63                                                       |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         RF Characteristics       1                                                                                                                                                                                                                                                                                                                                        | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>63                                                 |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions       11         Detailed register descriptions       14         Specifications       14         Electrical Data       14         Absolute Maximum Ratings       14         Operating Ratings       14         AC/DC Characteristics       14         RF Characteristics       14         IF Characteristics       14                                                                                                                                                                                                                                                                                            | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>63<br>64<br>66                                     |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         RF Characteristics       1         IF Characteristics       1         Limiter Characteristics       1                                                                                                                                                                                                                                                             | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>64<br>66<br>66                                     |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions11Detailed register descriptions14Specifications14Electrical Data14Absolute Maximum Ratings14Operating Ratings14AC/DC Characteristics14General14RF Characteristics14IF Characteristics14Limiter Characteristics14Crystal Oscillator Characteristics14                                                                                                                                                                                                                                                                                                                                                             | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>63<br>64<br>66<br>66<br>67                         |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2                                                     | Register Descriptions11Detailed register descriptions14Specifications14Electrical Data14Absolute Maximum Ratings14Operating Ratings14AC/DC Characteristics14General14RF Characteristics14IF Characteristics14Limiter Characteristics14Crystal Oscillator Characteristics14Digital Inputs/Outputs14                                                                                                                                                                                                                                                                                                                                     | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>63<br>64<br>66<br>66<br>67<br>67                   |

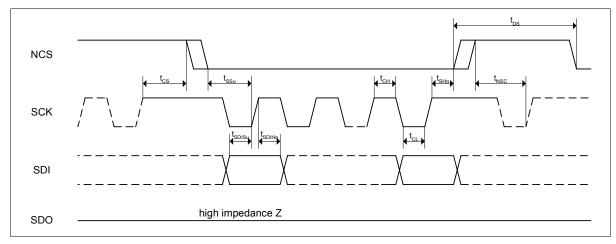

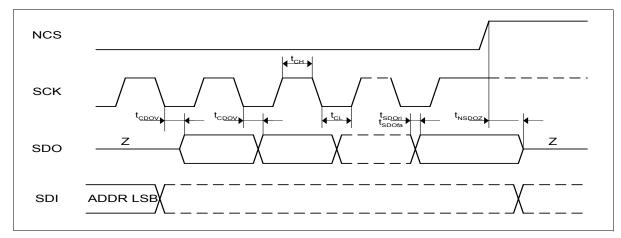

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3                                            | Register Descriptions1Detailed register descriptions1Specifications1Electrical Data1Absolute Maximum Ratings1Operating Ratings1AC/DC Characteristics1General1RF Characteristics1IF Characteristics1Limiter Characteristics1Crystal Oscillator Characteristics1Digital Inputs/Outputs1Timing SPI-Bus1                                                                                                                                                                                                                                                                                                                                   | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>64<br>66<br>66<br>67<br>67<br>68                   |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3                                            | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         General       1         RF Characteristics       1         IF Characteristics       1         Limiter Characteristics       1         Digital Inputs/Outputs       1         Timing SPI-Bus       1                                                                                                                                                               | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>64<br>66<br>67<br>67<br>67<br>68<br>75             |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.2.1                            | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         General       1         IF Characteristics       1         Limiter Characteristics       1         Crystal Oscillator Characteristics       1         Digital Inputs/Outputs       1         Timing SPI-Bus       1         Timing Diagrams       1         Serial Input Timing       1                                                                           | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>64<br>66<br>67<br>67<br>68<br>75<br>75             |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.3                                   | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         General       1         RF Characteristics       1         IF Characteristics       1         Limiter Characteristics       1         Digital Inputs/Outputs       1         Timing Diagrams       1         Serial Input Timing       1         Serial Output Timing       1                                                                                     | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>63<br>64<br>66<br>67<br>67<br>68<br>75<br>75       |

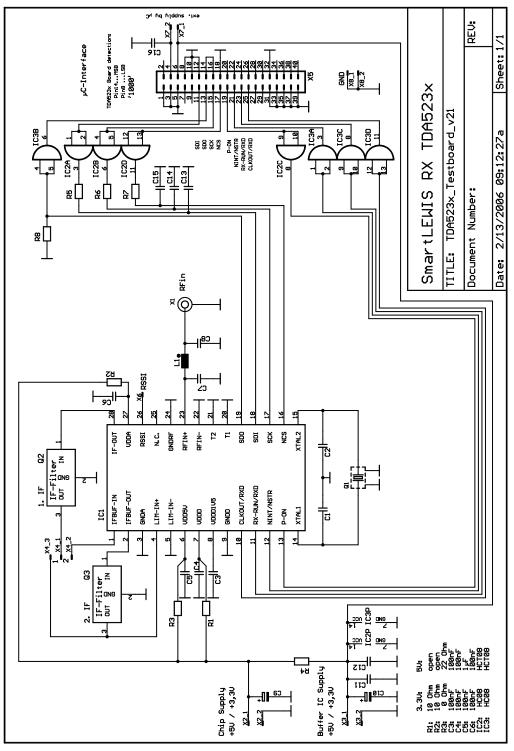

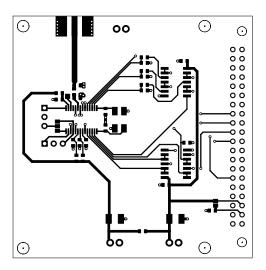

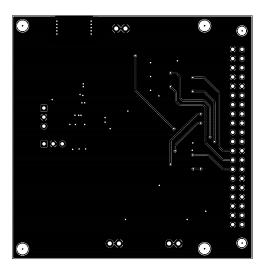

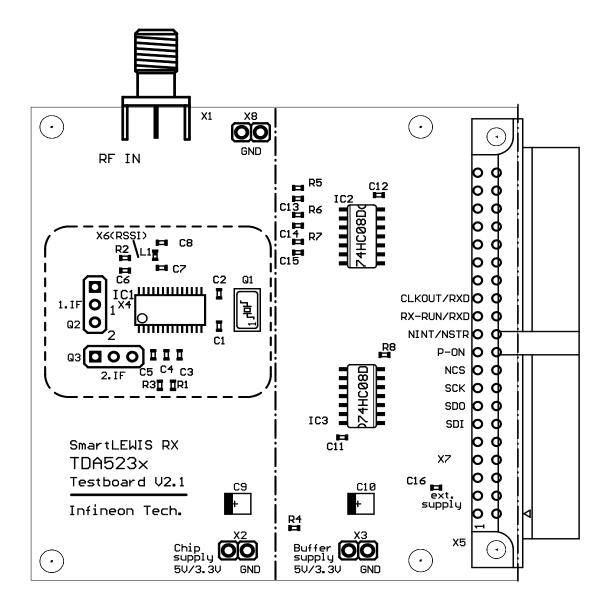

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.3<br>4.2.2<br>4.2.1<br>4.2.2<br>4.3 | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         General       1         RF Characteristics       1         IF Characteristics       1         Limiter Characteristics       1         Digital Inputs/Outputs       1         Timing SPI-Bus       1         Timing Diagrams       1         Serial Output Timing       1         Serial Output Timing       1         Test Circuit, Evaluation Board V2.1       1 | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>64<br>66<br>67<br>67<br>67<br>75<br>75<br>75<br>75 |

| <b>3</b><br>3.1<br><b>4</b><br>4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.3                                   | Register Descriptions       1         Detailed register descriptions       1         Specifications       1         Electrical Data       1         Absolute Maximum Ratings       1         Operating Ratings       1         AC/DC Characteristics       1         General       1         RF Characteristics       1         Limiter Characteristics       1         Digital Inputs/Outputs       1         Timing SPI-Bus       1         Timing Diagrams       1         Serial Input Timing       1         Test Circuit, Evaluation Board V2.1       1                                                                          | 28<br>35<br>62<br>62<br>63<br>63<br>63<br>63<br>64<br>66<br>67<br>67<br>68<br>75<br>75       |

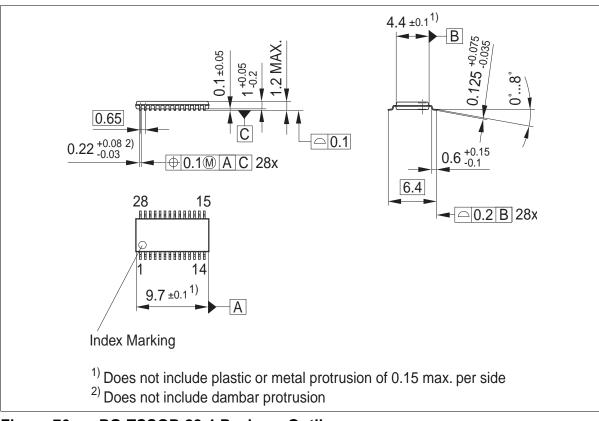

| 5 | Package Outlines | 81  |

|---|------------------|-----|

| - |                  | • • |

# 1 **Product Description**

#### 1.1 Overview

The TDA523x is a family of universal, highly sensitive, low-power single-chip ASK/FSK superheterodyne image-reject-receivers for Manchester-coded data signals in the ISM bands between 302..320 MHz, 433..450 MHz and 865..870 MHz. The chips include fully-integrated digital baseband data processing and produce clean data output via SPI, thus significantly reducing the load on the host processor and standby power consumption.

The TDA523x family of chips offers a high level of integration and needs only few external components for application deployment.

The TDA523x is able to run in several autonomous self-polling and wake-up modes, scanning the received signal for usable data. Interrupts can be initiated based on various criteria, such as the received bit pattern to wake up the host processor. Received data can be scanned for certain message contents (IDs) and is stored in a FIFO data buffer, accessible via the SPI host interface.

The TDA523x is able to scan and receive from different sources with up to two different independent parameter configuration sets. Configurations can differ in modulation ASK/FSK, data rate, wake up criterion, protocol, etc. Additionally, multichannel applications are supported by scanning of up to 3 RF channels in the same band.

The TDA523x is fully programmable to facilitate quick time to market.

#### 1.2 Key Features

- Fully integrated ASK/FSK RF Data Receiver with data FIFO and SPI host interface

- High input sensitivity: e.g. typically -108dBm at 2kbit data rate (see Specifications)

- Autonomous wake-up and Self-Polling features allow different modulation for wake-up and data

- Two parallel parameter sets for scanning and receiving from different sources

- Reduces significantly host processing power, system standby power consumption

- Fully integrated Multichannel PLL Synthesizer support up to 17 sub-channels

- Image Reject mixer prevents interferences on mirror frequency

- IF Filter Multiplexer allows IF bandwidth switching

- IF-Limiting Amplifier with RSSI-Output accessible via dedicated pin or register

- Data Framer with versatile Frame Synchronization capability

- Message Contents (ID) scanning

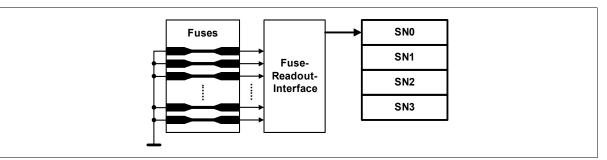

- Unique Serial-Number, accessible via SPI

- Crystal-Oscillator with on chip Fine-Tuning, Clock-Output with configurable Prescaler

- Supply Voltage Range 3.0 V to 3.6 V and 4.5 V to 5.5 V

- Package PG-TSSOP-28-1

- Operating Temperature Range -40 to +105°C

- Qualified according automotive AEC-Q100

- Evaluation boards, reference designs, and free PC configuration and evaluation tools available

#### 1.3 Applications

- Tire Pressure Monitoring Systems

- Remote Keyless Entry Systems

- Remote Control Systems

# 1.4 Order Information

| Туре    | Ordering Code | Package      |

|---------|---------------|--------------|

| TDA5230 | Q62705K 791   | PG-TSSOP28-1 |

| TDA5231 | SP000202847   | PG-TSSOP28-1 |

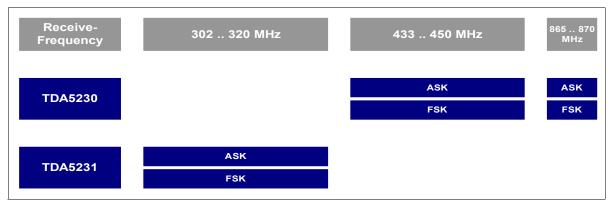

### 1.5 Target Application Frequencies for TDA5230 and TDA5231

The TDA523x family of receivers cover a wide range of commonly used receive frequencies within the three major ISM-bands used in TPMS, RKE/PKE and remote control system applications.

The TDA5230 covers operation in the 433..450 MHz and 865..868 MHz ISM bands. The TDA5231 covers complementary operation in the 302..320 MHz ISM-band.

Figure 1 identifies the capabilities of the TDA5230 and TDA5231 within the three different frequency bands.

Figure 1 Application Frequencies for TDA5230 and TDA5231

Color underlayed text within this document highlights differences in the operation between the TDA5230 (Lo-Side LO-Injection) and TDA5231 (Hi-Side LO-Injection).

# 1.6 Major Key-Features of TDA5230 and TDA5231

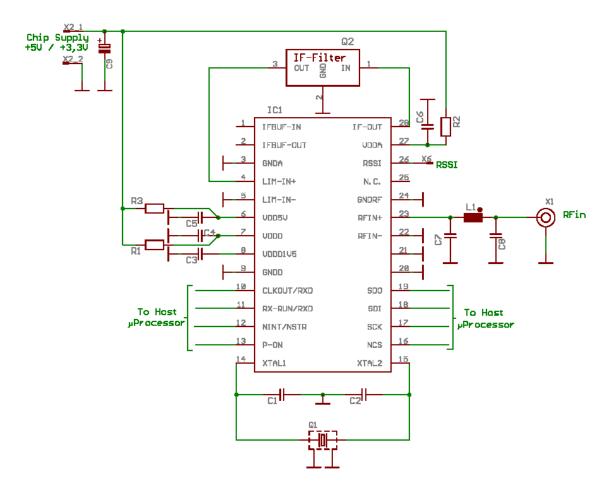

# 1.6.1 Typical Application Circuit

#### Figure 2 Typical Application Circuit

The TDA523x requires only view external components.

In noise and EMC sensitive applications usage of an input SAW filter plus additional matching circuitry is recommended.

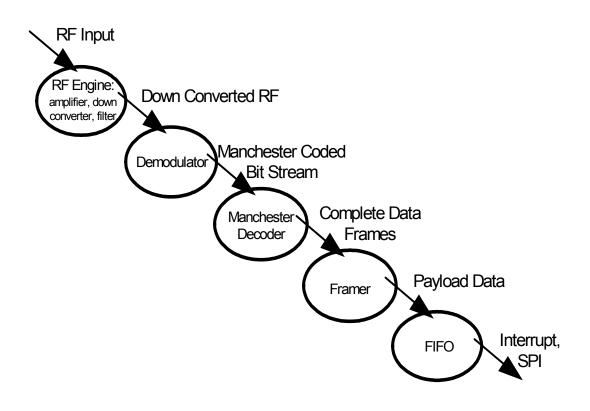

# 1.6.2 Baseband Processing

TDA523x has integrated all means to process incoming ASK or FSK modulated Manchester-coded bit streams, and convert them into pure data, which can be read out via SPI by the host processor.

#### Figure 3 Internal Data Processing Flow

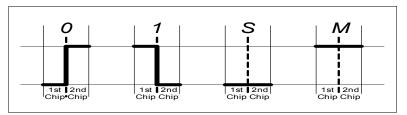

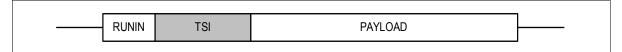

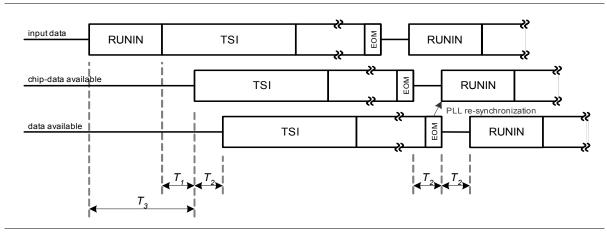

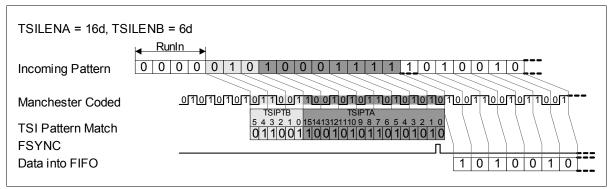

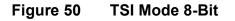

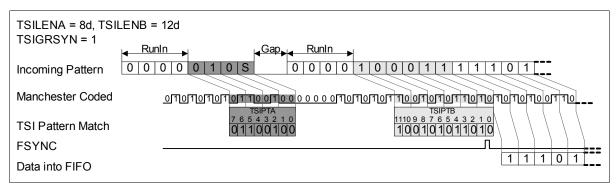

The Manchester-coded bit stream is decoded by the Manchester Decoder into a bit stream containing the wake-up pattern, the TSI (Telegram Start Identifier) and the payload. The Framer separates the payload and stores it in the FIFO. An interrupt is generated and data can be read from the FIFO by the host processor via SPI.

# 1.6.3 Autonomous Self Polling

The TDA523x offers a fully autonomous Self Polling Mode, in which the RF input signal is scanned for valid data signals base on programmable timing. The host processor is not burdened with this task, so its full processing power is available for other tasks, or the host processor may stay in a power save, or sleep mode. When valid data has been

received, the host processor is alerted by an interrupt, and the data payload is available from the FIFO. Invalid signals are ignored.

The TDA523x offers different programmable scanning modes, and criteria to identify valid wake up patterns, TSIs, and payloads.

Selectable Wake-Up Criteria include detection of a valid data rate, a random Manchester-coded pattern, a chain of equal Manchester-coded bits, or a specific pattern.

Before initiating an interrupt also the TSI must match up to a programmed pattern; optionally the data stream may be scanned for up to 16 bytes of a Message Identifier.

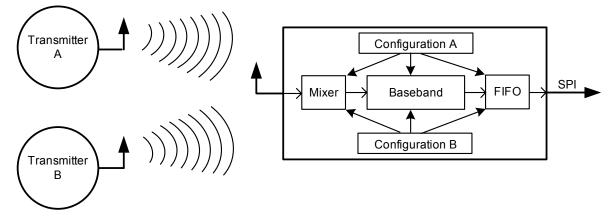

# **1.6.4** Two Independent Receiver Configuration Sets

#### Figure 4 TDA523x Two Independent Receiver Configurations (simplified)

TDA523x has two switchable register sets, allowing scans based on up to two different configurations from different transmitters. Transmissions may differ in sub-channel, modulation, wake-up criterion, data rate, TSI, message identifier, packet length, etc.

In Self Polling Mode configurations are switched autonomously; in Slave Mode, configurations are switched by changing a single register bit.

# 1.6.5 Multi-Channel PLL Receiver Supports up to 17 Subchannels

TDA523x supports up to 17 subchannels: 1 center channel, 8 channels above, and 8 channels below the center channel frequency. The frequencies for the channels are fixed and depend on the system frequency and the selected band. Additional information is provided in chapter **"RF-PLL Synthesizer" on Page 28**.

In Self Polling Mode up to 3 Channels per Receiver Configuration may be scanned automatically.

# **1.6.6 Support Software and Evaluation Boards**

The TDA523x includes free downloadable support software.

# 1.6.6.1 The IAF TDA523x Configuration Tool

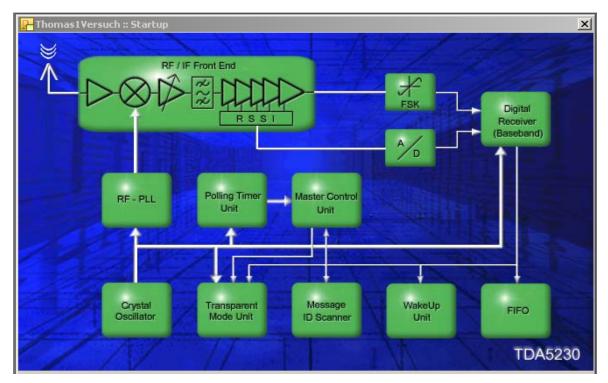

# Figure 5 IAF TDA523x Configuration Tool

The IAF TDA523x Configuration Tool offers simple configuration of all register settings. The resulting configuration file may be directly used and downloaded with the TDA523x Explorer or the configuration content may be copied into the target application software.

# 1.6.6.2 The TDA523x Explorer

| Configuration Ru | n Explore About               |                                       |

|------------------|-------------------------------|---------------------------------------|

|                  |                               |                                       |

| File             | No File Selected              |                                       |

| Configure        |                               | (infineon                             |

| Reset Chip       |                               |                                       |

|                  | Control                       |                                       |

| Read Register    | Addr Data<br>0x 0x            | Read                                  |

| Write Register   | 0x 0x                         | Write                                 |

|                  |                               | Andreas Schroeck                      |

| SPI Log          |                               |                                       |

| Clear Log 🔽      | Execute Verification Transfer |                                       |

|                  |                               | Address<br>0x<br>Data<br>0x<br>Update |

| Sleep Mode       |                               | USB In-Active                         |

#### Figure 6 TDA523x Explorer

The TDA523x Explorer works with the TDA523x Evaluation Boards. It allows application solutions to be created and checked via a USB connection from a standard PC. The Explorer allows the user to write registers, read out the data FIFO and related registers.

# 1.6.6.3 Evaluation Boards

Various Evaluation Boards are available or in development.

All Evaluation Boards have a USB interface to connect to a standard PC and are supported by the TDA523x Explorer.

# 2 Functional Description

# 2.1 Pin Configuration

# Figure 7 Pin Configuration

# 2.2 Pin Definition and Functions

# Table 1Pin Definition and Function

| Pin<br>No. | Symbol    |                                                                                                                                 | Function                          |

|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

| 1          | IFBUF-IN  | IFBUF-IN<br>GNDA<br>LIM-IN+<br>GNDA<br>LIM-IN-<br>GNDA<br>GNDA<br>LIM-IN-<br>GNDA<br>GNDA<br>LIM-IN-<br>GNDA<br>LIM-IN-<br>GNDA | Input of IF Buffer<br>Amplifier   |

| 2          | IFBUF-OUT | VDDA VDDA<br>IFBUF-OUT                                                                                                          | Output of IF Buffer<br>Amplifier  |

| 3          | GNDA      |                                                                                                                                 | Analog Ground                     |

| 4          | LIM-IN+   | see schematic of Pin 1                                                                                                          | IF Limiter Input                  |

| 5          | LIM-IN-   | see schematic of Pin 1                                                                                                          | Complementary IF<br>Limiter Input |

| 6          | VDD5V     |                                                                                                                                 | Supply 5 V                        |

| 7          | VDDD      | VDD5V<br>VReg<br>GNDD<br>VDDD                                                                                                   | Digital Supply 3.3 V              |

| 8          | VDDD1V5   | VDDD<br>VDDD<br>GNDD<br>VDD1V5                                                                                                  | Digital Supply 1.5 V              |

| 9          | GNDD      |                                                                                                                                 | Digital Ground                    |

| Pin<br>No. | Symbol     |                                                             | Function                                                       |

|------------|------------|-------------------------------------------------------------|----------------------------------------------------------------|

| 10         | CLKOUT/RXD |                                                             | Programmable Clock<br>Output and alternative<br>RX Data Output |

| 11         | RX-RUN/RXD |                                                             | Run Mode Output<br>signal and alternative<br>RX Data Output    |

| 12         | NINT/NSTR  |                                                             | Interrupt Output and<br>alternative RX Data<br>Strobe Output   |

| 13         | P-ON       | P_ON<br>GNDD<br>GNDD<br>GNDD<br>GNDD<br>GNDD                | Power On                                                       |

| 14         | XTAL1      |                                                             | Crystal Oscillator                                             |

| 15         | XTAL2      | VDDD<br>VDDD<br>VDDD<br>VDDD<br>VDDD<br>VDDD<br>VDDD<br>VDD | Crystal Oscillator                                             |

| Pin<br>No. | Symbol |                                                                           | Function                   |

|------------|--------|---------------------------------------------------------------------------|----------------------------|

| 16         | NCS    | NCS<br>GNDD<br>GNDD<br>VDD5V VDDD<br>VDDD<br>VDDD<br>VDDD<br>VDDD<br>VDDD | SPI Chip Select            |

| 17         | SCK    | VDD5V VDDD<br>sck                                                         | SPI Clock                  |

| 18         | SDI    | SDI SDI GNDD GNDD                                                         | SPI Serial Data Input      |

| 19         | SDO    |                                                                           | SPI Serial Data Output     |

| 20         | T1     |                                                                           | Connect to Digital Ground  |

| 21         | T2     |                                                                           | Connect to RF Ground       |

| 22         | RFIN-  | RFIN-                                                                     | Complementary LNA<br>Input |

| 23         | RFIN+  |                                                                           | LNA Input                  |

| 24         | GNDRF  |                                                                           | RF Ground                  |

| 25         | N.C.   |                                                                           | Do not connect             |

| Pin<br>No. | Symbol |                               | Function            |

|------------|--------|-------------------------------|---------------------|

| 26         | RSSI   |                               | RSSI Output         |

| 27         | VDDA   | UDD5V<br>VReg<br>GNDA<br>VDDA | Analog Supply 3.3 V |

| 28         | IF-OUT | VDDA VDDA<br>IF-OUT           | Mixer IF Output     |

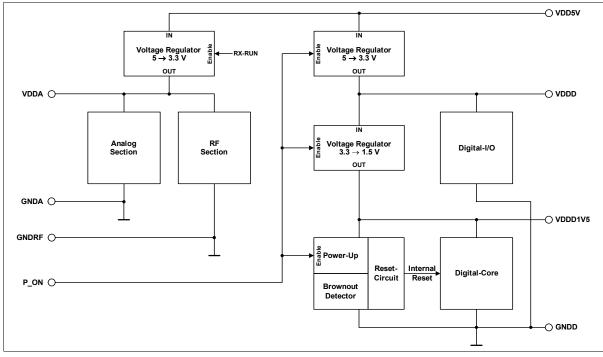

Figure 8 Functional Block Diagram

# 2.4 Functional Block Description

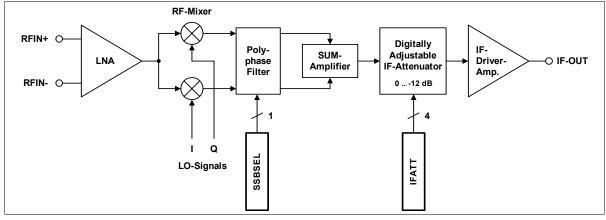

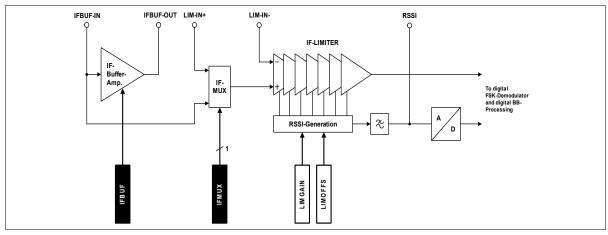

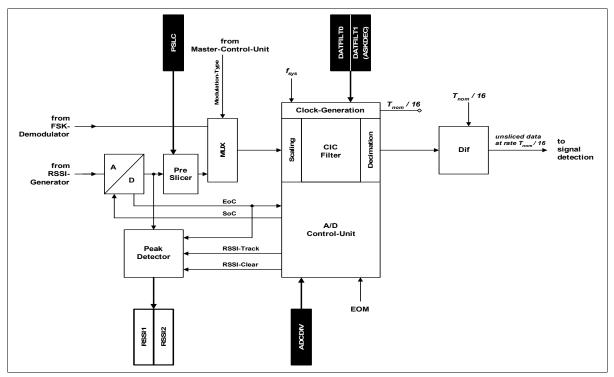

The RF frontend of the chip contains an LNA followed by an Image Reject Mixer that converts the incoming RF-signal down to IF with adjustable gain from RFIN to IF-OUT. Channel selection is achieved by up to two external ceramic IF filters, which narrow the channel bandwidth. The multistage amplifier performs the limitation of the IF signal and generation of the RSSI signal. The limited IF signal at its output drives the input of the digital FSK Demodulator. The gain and offset of the generated RSSI signal can be digitally adjusted. An A/D converter acts as an interface from the analog RSSI signal path to the Digital Receiver.

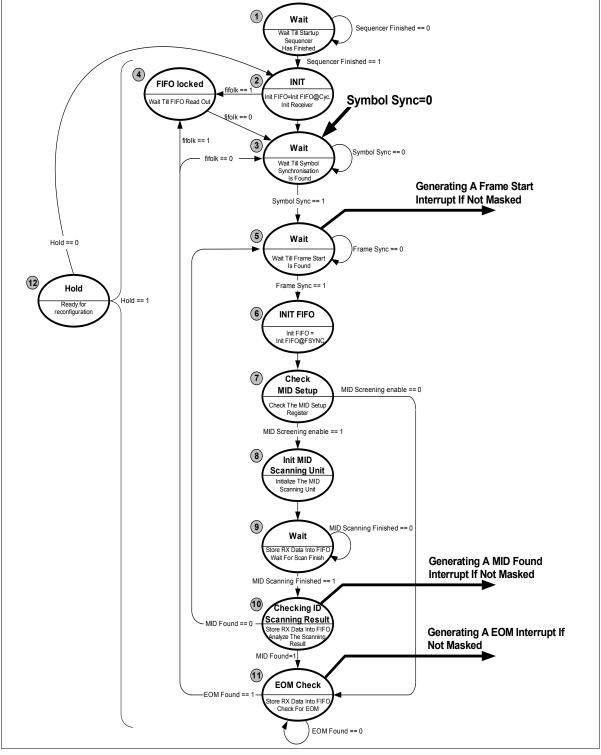

The Digital Receiver performs data filtering, offset cancellation and Manchester decoding of the received signals after they are demodulated. The chip also offers a

flexible and configurable frame synchronisation and Message ID scanning feature, supported by special function registers. Received data of an accepted message is stored in a FIFO and can be read out via the SPI interface.

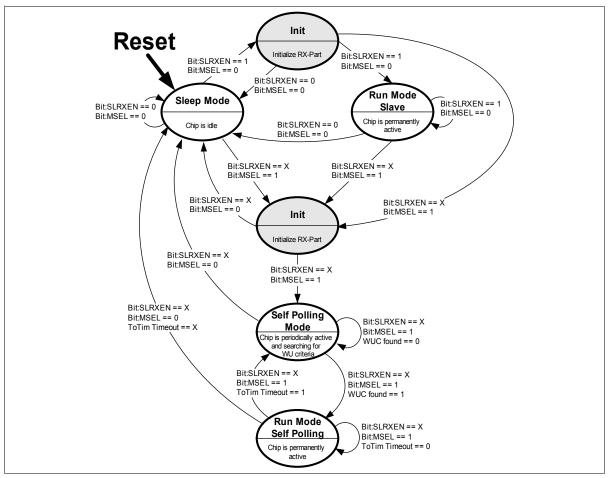

A master control unit (MCU), implemented as a finite state machine and a Polling Timer Unit control all actions of the device and can be configured via Special Function Registers (SFRs). Various self-polling modes can be set up to achieve a maximum of autonomous receiver operation. The Transparent Mode Unit defines the functionality of the pins CLKOUT/RXD, NINT/NSTR and RX-RUN/RXD.

A fully integrated multi-channel PLLdrives the LO ports of the Image-Reject-Mixer. Within a selected operational frequency band multiple channels are accessible by utilizing the same reference crystal-frequency. The reference clock of the PLL and the digital section are provided by a pierce type crystal oscillator that offers on chip fine-tuning to trim out crystal tolerances. A programmable Clock Generation Unit divides the system clock by a programmable ratio and drives the CLKOUT/RXD pin.

On chip voltage regulators generate the required internal supply voltages and allow the IC to be operated at supply voltages between 3 V to 3.6 V and 4.5 V to 5.5 V. The digital supply of the chip is monitored by a brown out detector and is equipped with a built-in reset generator. Every device contains a unique serial number, which can be read out via the SPI Interface.

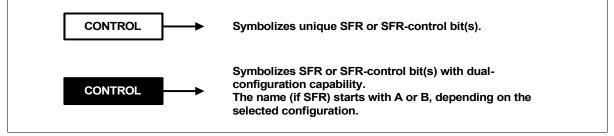

# **Special Function Register and Control Bit Symbols**

#### Figure 9 SFR Symbolism

The register names, addresses, and control bits for each function are listed in a table at the end of this section. Functional descriptions of all registers are provided in **Chapter 3 Register Descriptions**.

# 2.4.1 Power Supply

The chip may be operated within a 5 V or a 3.3 V environment.

#### Figure 10 Power Supply

For operation within a 5 V environment, the chip is supplied via the pin VDD5V. In this configuration a 5 to 3.3 V voltage regulator supplies the analog/RF-section (only active in Run Modes) and a second 5 to 3.3 V voltage regulator supplies the digital I/O-pads.

When operating within a 3.3 V environment, the pins VDD5V, VDDA and VDDD must be supplied. The 5 to 3.3 V voltage regulators are inactive in this configuration.

The internal digital core is supplied by an additional 3.3 to 1.5 V regulator.

The regulators for the digital section are controlled by the signal at the P\_ON (Power On). A low signal at P\_ON disables all regulators and sets the IC into Power Down Mode. A low to high transition at P\_ON enables the regulators for the digital section and initiates a power on reset. The regulator for the analog section is controlled by the Master Control Unit and is active only when the RF-section is active (RX-RUN = high).

P\_ON can be used to initiate a reset. The required negative pulse time  $t_{P_ON}$  is specified in **Chapter 4 Specifications**.

To provide data integrity within the digital units, a brown out detector monitors the digital supply and a detected voltage drop of VDDD below approximately 2.45 V initiates a reset.

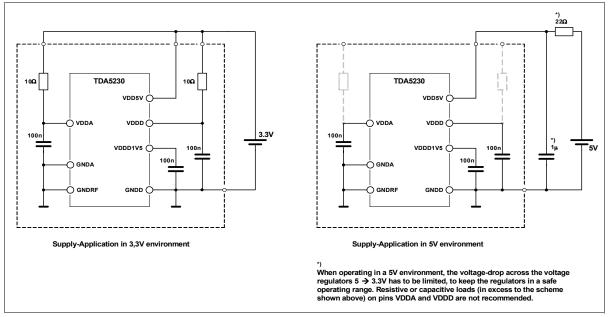

Figure 11 illustrates a typical power supply application for a 3.3 V and a 5 V environment.

Figure 11 Supply Modes

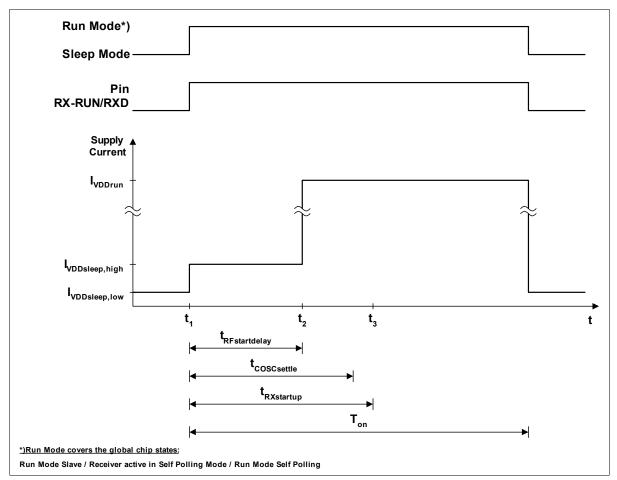

# 2.4.1.1 Supply Current

In Sleep Mode, the Master Control Unit switches the crystal oscillator into Low Power Mode (all internal load capacitors are disconnected) to minimize power consumption.

Whenever the chip leaves the Sleep Mode ( $t_1$ ), the crystal oscillator resumes operation in High Precision Mode and requires  $t_{COSCsettle}$  to settle at the trimmed frequency. At  $t_2$ the analog signal path (RF and IF section) and the RF-PLL are activated. At  $t_3$  the chip is ready to receive data. The chip requires  $t_{RXstartup}$  from leaving Sleep Mode and until the receiver is ready to receive data.

A transient supply current peak may occur at  $t_1$ , depending on the selected trimming capacitance. The average supply current drawn between during  $t_{\text{RFstartupdelay}}$  is  $I_{\text{VDDsleep}, high}$ .

Figure 12 Supply Current Ramp Up/Down

If the IF buffer amplifier or the clock-generation feature (CLKOUT/RXD pin active) is activated, the respective currents must be added.

# 2.4.2 Chip Reset

Power down and power on are controlled by the P\_ON pin. A low at this pin keeps the IC in Power Down Mode. All voltage regulators and the internal biasing are switched off. A high at the P\_ON pin activates the appropriate voltage regulators and the internal biasing of the chip. A power up reset is generated at the same time.

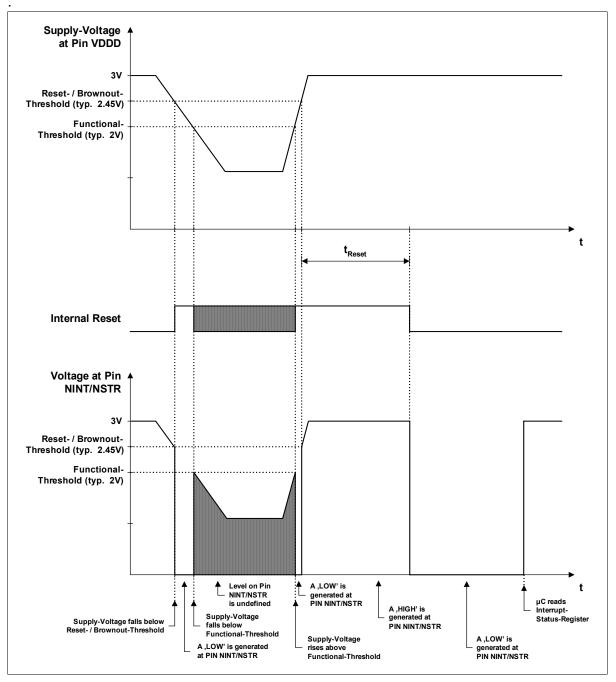

Figure 13 Reset Behavior

A second source that can trigger a reset is a brown out event. Whenever the integrated brown out detector measures a voltage drop below the brown-out threshold on the digital supply, the integrity of the stored data and configuration can no longer be guaranteed; thus, a reset is generated. While the supply voltage stays between the brown out and the functional threshold of the chip, the NINT/NSTR pin is forced to low. When the supply voltage drops below the functional threshold, the levels of all digital output pins (e.g. NINT/NSTR) are undefined.

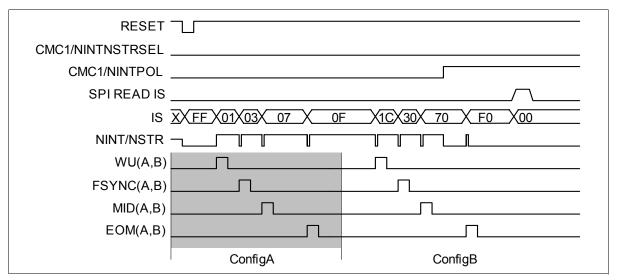

When the supply voltage rises above the brown out threshold, the IC generates a high pulse at NINT/NSTR and remains in the reset state for the duration of  $t_{Reset}$ . When the IC leaves the reset state, the Interrupt Status register (IS) is set to FF<sub>hex</sub> and the NINT/NSTR pin is forced to low. Now, the IC starts operation in the Sleep Mode, ready to receive commands via the SPI interface. The NINT/NSTR pin will go high, when the Interrupt Status register is read the first time.

# 2.4.3 System Clock

# 2.4.3.1 Crystal Oscillator

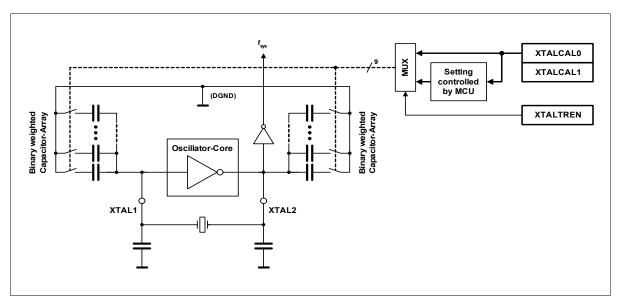

The reference clock for the Digital and the RF Section is generated by a pierce-type crystal oscillator. Adjustable internal load capacitors are provided that allow the tolerances of the crystal, external load capacitors and the IC itself to be trimmed out. These capacitors are built of binary weighted C-banks and are connected in parallel to the external load capacitors. The internal capacitors are controlled by the crystal oscillator calibration data register (XTALCAL). An automatic amplitude regulation allows the oscillator to operate with minimal current consumption.

All trim capacitors are disconnected in Sleep Mode (this minimizes current consumption). Whenever the TDA523x switches from Sleep Mode to Run Modes, the Master Control Unit reads out the XTALCAL0 and XTALCAL1 registers and connects the selected trim capacitors to the crystal. A modification of XTALCAL0 or XTALCAL1 registers in Run Modes does not immediately alter the setting of the activated trim capacitors unless the SFR control bit XTALTREN, is set.

Figure 14 Crystal Oscillator

# **Crystal Selection:**

The recommended crystal type and manufacturer is listed in the **Bill of Materials** in the Evaluation Board section of this Data Sheet. This crystal has been released by Infineon as well by the crystal manufacturer for optimal operation with TDA523x.

If additional crystal types are released, this information will be published on the related TDA523x product page at www.infineon.com.

The crystal frequency is calculated:

```

For TDA5230 (Lo Side LO Injection)

```

$f_{svs} = A^*(f_{RF} - 10.7MHz)/64$

For TDA5231 (Hi Side LO Injection

f<sub>svs</sub>=A\*(f<sub>RF</sub>+10.7MHz)/64

Values for A depend on the frequency band: 302...320MHz...A=3 (TDA5231), 433...450MHz...A=2, 865...870MHz...A=1 (TDA5230)

# The crystal frequency is automatically calculated by the IAF TDA523x Configuration Tool.

#### **Recommended Trimming Procedure**

- Set the TDA523x to SLEEP mode

- Set the registers XTCAL0 and XTCAL1 to the expected nominal values

- Set the TDA523x to Slave Mode Run

- Set the register bit XTALTREN in register CMC1

- Wait for 0.5ms minimum

- Trim the oscillator by increasing and decreasing the values of XTALCAL0/1

- Never change the trim capacitor size by more than 1 pF!

- When the Oscillator is trimmed, reset the XALTREN bit

- Set the TDA523x to SLEEP mode

- Add the settings of XTCAL0/1 to the configuration. It must be set after every power up or brown out!

#### **Using the High Precision Mode**

As discussed earlier, the TDA523x allows to the crystal oscillator to be trimmed by the use of internal trim capacitors. It is also possible to use the trim functionality to compensate temperature drift of crystals.

During Run Mode (always when the receiver is active) the capacitors are automatically connected and the oscillator is used in the High Precision Mode.

On entering Sleep Mode, the capacitors are automatically disconnected to save power.

If the High Precision Mode is also required for Sleep Mode, the automatic disconnection of trim capacitors can be avoided by setting XALTREN to 1 (enable XTAL trim).

#### Setting of XALTREN has to be changed only in Run-Mode!

# CMC1: Chip Mode Control Register 1

| ADDR: 0x03          |  | Reset Value: 0x00                                                               |  |

|---------------------|--|---------------------------------------------------------------------------------|--|

| Bit R/W Description |  | •                                                                               |  |

| 4                   |  | XTALTREN: XTAL Trim Enable<br>0: Trimming is disabled<br>1: Trimming is enabled |  |

# XTALCAL0: Trim XTAL frequency, coarse

| ADDR: 0x61 |     |                                                | Reset Value: 0x10 |

|------------|-----|------------------------------------------------|-------------------|

| Bit        | R/W | Description                                    |                   |

| 4          | W   | XTAL_SW_COARSE_4: Connect trim capacitor: 16 p | ρF                |

| 3          | W   | XTAL_SW_COARSE_3: Connect trim capacitor: 8 pl | =                 |

| 2          | W   | XTAL_SW_COARSE_2: Connect trim capacitor: 4 pl | =                 |

| 1          | W   | XTAL_SW_COARSE_1: Connect trim capacitor: 2 pl | =                 |

| 0          | W   | XTAL_SW_COARSE_0: Connect trim capacitor: 1 pl | =                 |

# XTALCAL1: Trim XTAL frequency, fine

| ADDR: 0x62 |     |                                                 | Reset Value: 0x00 |

|------------|-----|-------------------------------------------------|-------------------|

| Bit        | R/W | Description                                     |                   |

| 3          | W   | XTAL_SW_FINE_3: Connect trim capacitor: 500 fF  |                   |

| 2          | W   | XTAL_SW_FINE_2: Connect trim capacitor: 250 fF  |                   |

| 1          | W   | XTAL_SW_FINE_1: Connect trim capacitor: 125 fF  |                   |

| 0          | W   | XTAL_SW_FINE_0: Connect trim capacitor: 62.5 fF |                   |

# 2.4.3.2 External Clock Generation Unit

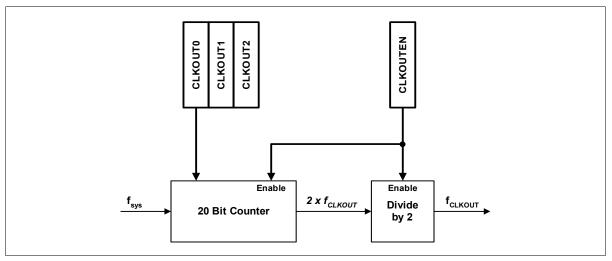

The chip provides a programmable clock signal at the CLKOUT/RXD pin that is derived from the internal system clock. To save power, this unit can be disabled by the SFR CLKOUTEN bit. The Clock Generation Unit divides the internal clock by an adjustable factor down to the desired CLKOUT frequency. The 20-bit wide division factor, stored in the CLOCKOUT0, CLOCKOUT1 and CLOCKOUT2 registers, allows a CLKOUT-frequency to be generated down to approximately 10 Hz. The 1:2 divider following the 20-bit counter creates the final CLKOUT signal with 50% duty cycle.

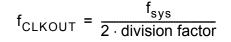

The resulting CLKOUT frequency can be calculated by:

### Figure 15 External Clock Generation Unit

The maximum CLKOUT frequency is limited by the driver capability of the CLKOUT/RXD pin and depends on the external load connected to this pin. Please be aware that large loads and/or high clock frequencies at this pin may interfere with the receiver and reduce performance.

After Reset the CLKOUT/RXD pin is activated and the division factor initialized to 7 (equals 1 MHz for  $f_{svs}$  of 14 MHz).

A higher clock output frequency than 1 MHz is not recommended.

# CMC0: Chip Mode Control Register 0

| ADDR: 0x02 |     | 02                                                                           | Reset Value: 0x40 |

|------------|-----|------------------------------------------------------------------------------|-------------------|

| Bit        | R/W | Description                                                                  |                   |

| 6          | W   | CLKOUTEN: CLKOUT enable<br>0: Disable<br>1: Enable programmable clock output |                   |

# CLKOUT0: Clock Divider Register 0

| ADDR: 0x13 |     | Reset Value: 0x07                                                                                                               |  |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------|--|

| Bit        | R/W | Description                                                                                                                     |  |

| 7:0        | W   | CLKOUT0: Clock Out Divider: Bit 7Bit 0 (LSB)<br>Min: 0 00 01h = Clock divided by 2<br>Max: 0 00 00h = Clock divided by (2^20)*2 |  |

# CLKOUT1: Clock Divider Register 1

| ADDR: 0x14 |     | 4                                                                                                                          | Reset Value: 0x00 |

|------------|-----|----------------------------------------------------------------------------------------------------------------------------|-------------------|

| Bit        | R/W | Description                                                                                                                |                   |

| 7:0        | W   | CLKOUT1: Clock Out Divider: Bit 15Bit 8<br>Min: 0 00 01h = Clock divided by 2<br>Max: 0 00 00h = Clock divided by (2^20)*2 |                   |

# CLKOUT2: Clock Divider Register 2

| ADDR: 0x15 |     | Reset Value: 0x00                                                                                                                 |   |

|------------|-----|-----------------------------------------------------------------------------------------------------------------------------------|---|

| Bit        | R/W | Description                                                                                                                       | 1 |

| 3:0        | W   | CLKOUT2: Clock Out Divider: Bit 19 (MSB)Bit 16<br>Min: 0 00 01h = Clock divided by 2<br>Max: 0 00 00h = Clock divided by (2^20)*2 |   |

# TDA523x

#### **Functional Description**

# 2.4.4 **RF-PLL Synthesizer**

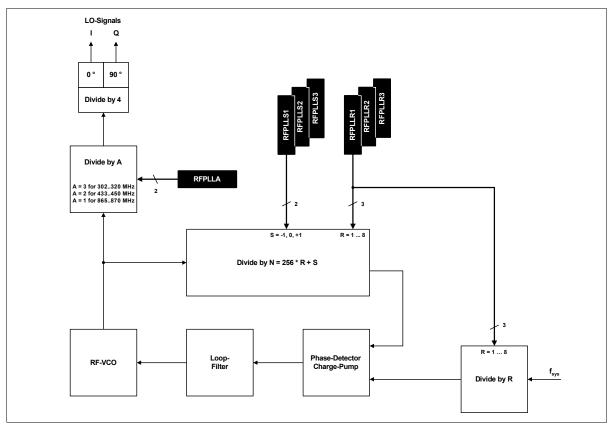

The Phase Locked Loop RF synthesizer consists of a VCO, programmable divider chains, a phase detector, a charge pump and a loop filter. The on chip VCO includes a spiral-inductor and varactors. The loop filter is also fully integrated on chip. The VCO signal is fed to both the programmable synthesizer divider chain and to a programmable RF divider. This RF divider allows selection between three operational frequency bands and drives a fixed divider by four, which generates the quadrature LO signals for the Image Reject Mixer.

Figure 16 RF PLL

Selection of a distinct operational frequency band is done via the SFR control bits RFPLLA. The overall division factor of the PLL-loop is determined by the content of the SFR control bits RFPLLRx and RFPLLSx, which control a programmable tri-modulus divider and a reference frequency divider. Depending on the configuration of the multichannel feature, the effective source of the control bits RFPLLRx can either be RFPLLR1, RFPLLR2 or RFPLLR3 and the source of the control bits RFPLLSx can be either RFPLLS1, RFPLLS2 or RFPLLS3.

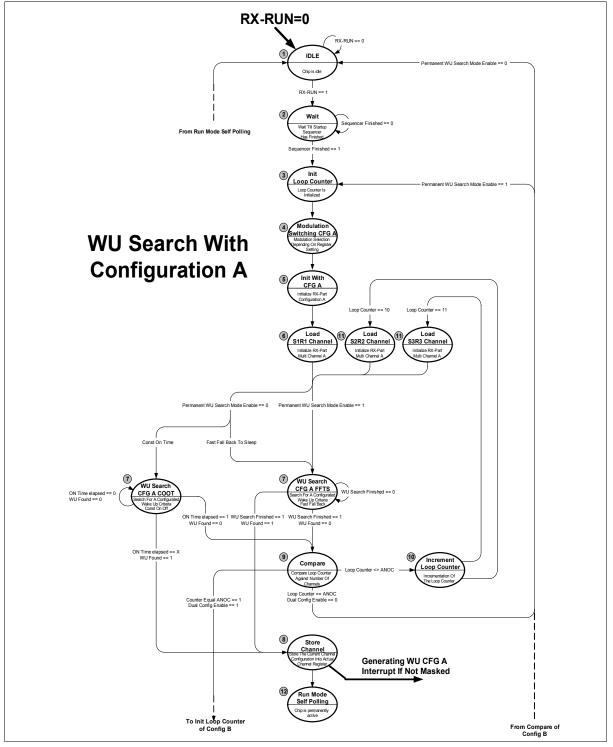

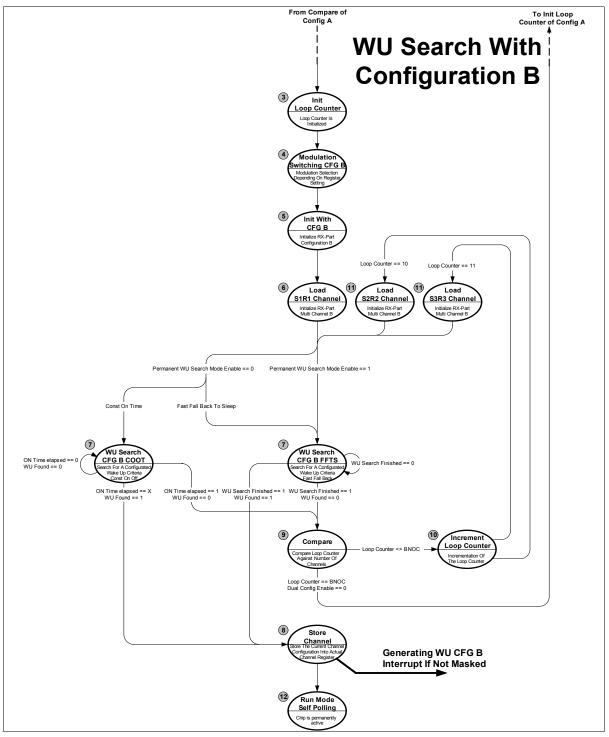

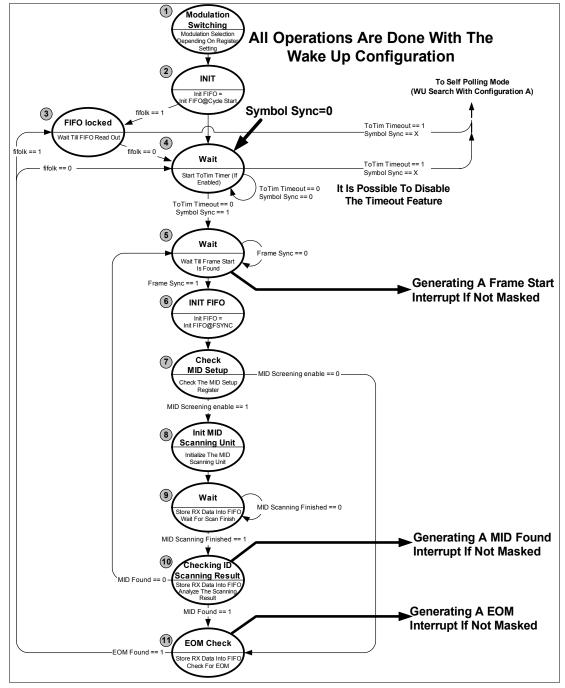

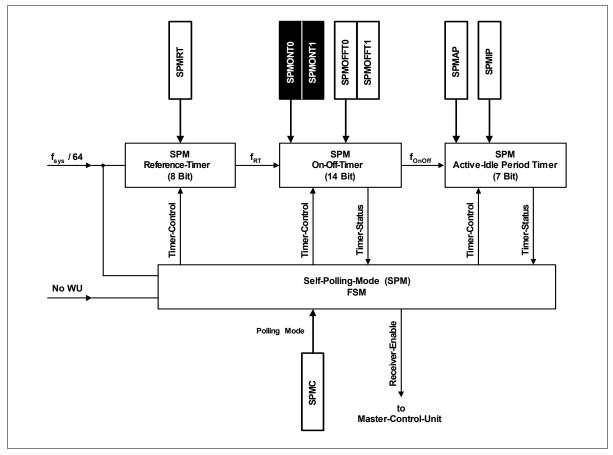

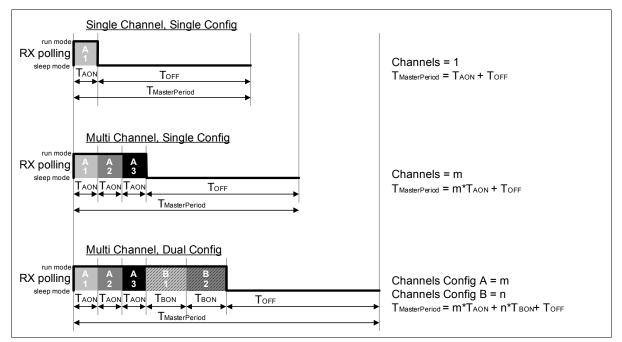

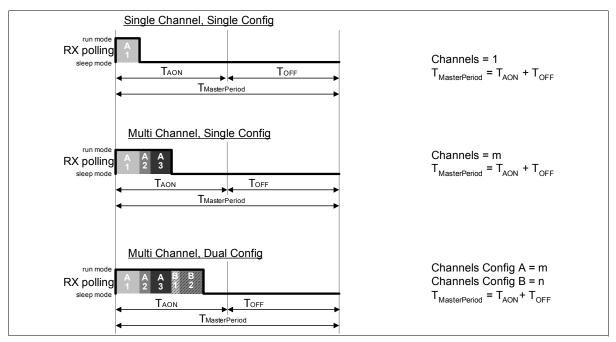

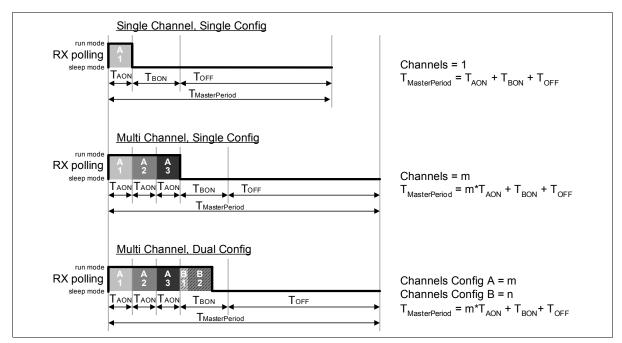

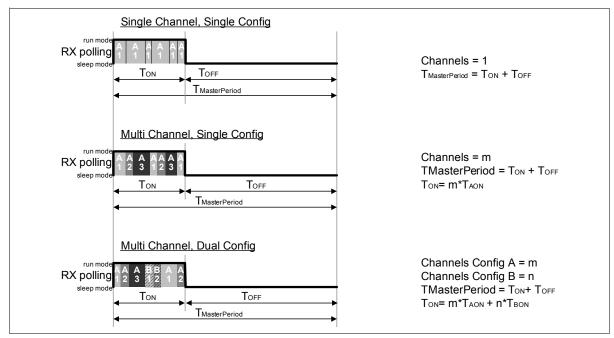

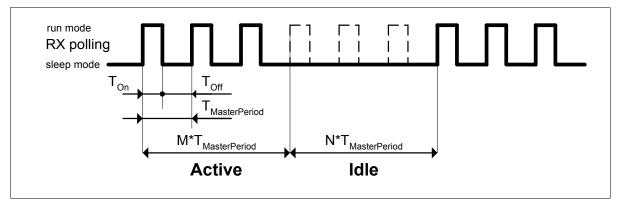

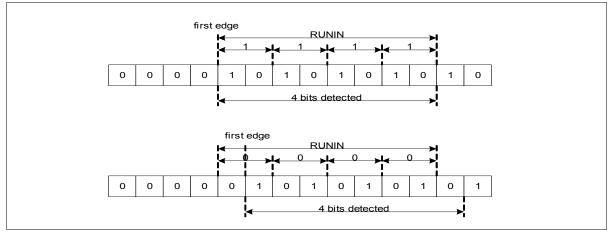

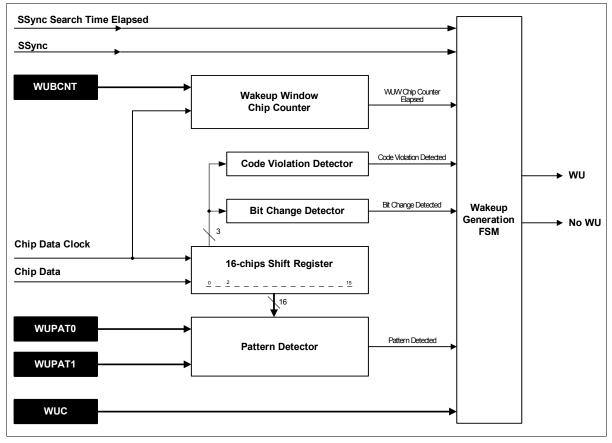

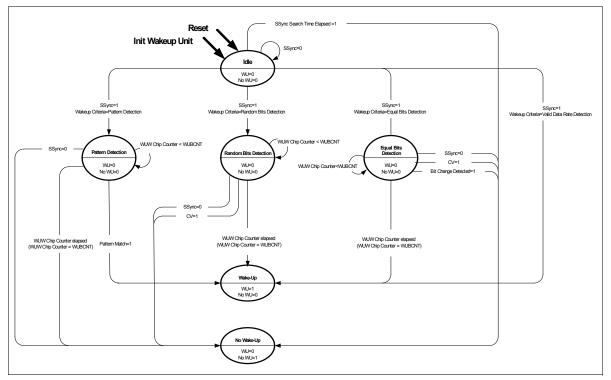

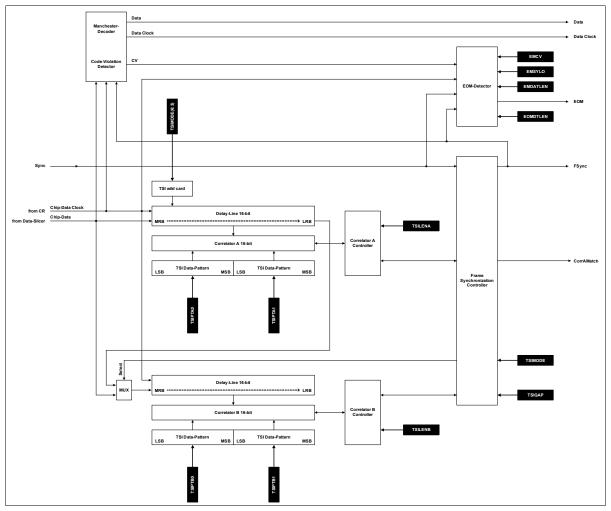

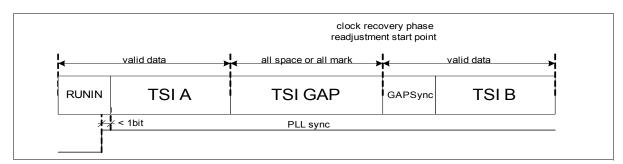

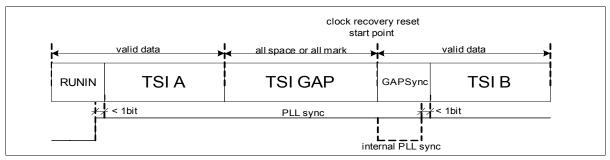

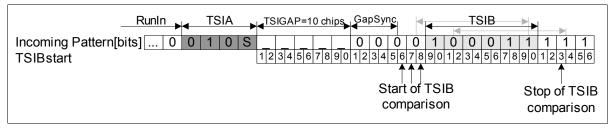

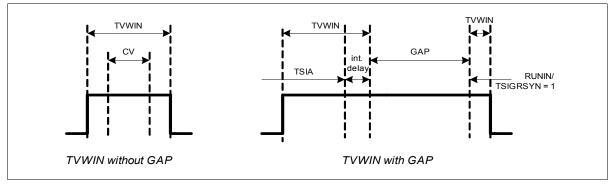

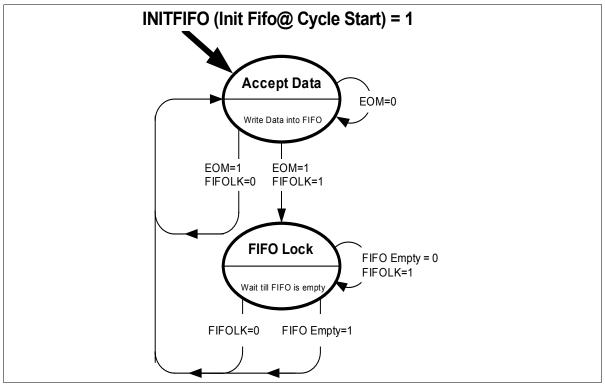

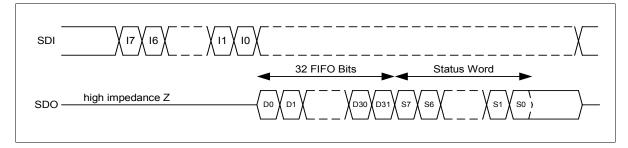

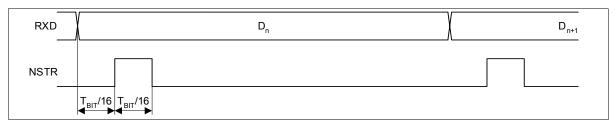

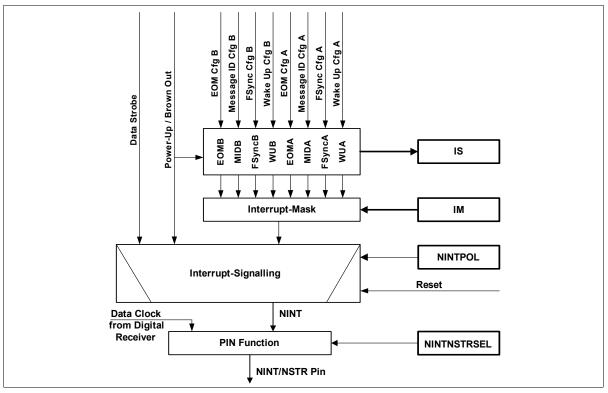

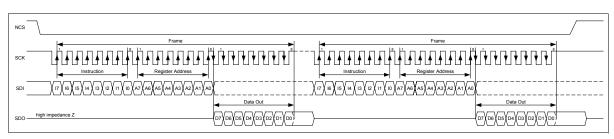

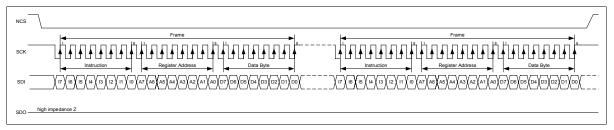

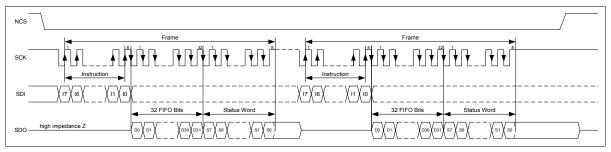

Based on the tri-modulus divider concept, up to 17 distinct channels<sup>1)</sup> are accessible within the selected operational frequency band by utilizing the same reference crystal frequency. The selected LO-frequency is described by the formula: