# RD15LD74AP, RD15LD74ANP, RD15LD74AT

8-bit D-type Flip-Flop Driver (with Clear)

REJ03D0894-0300 Rev.3.00 Feb 29, 2008

# Description

RD15LD74AP, RD15LD74ANP, RD15LD74AT have eight D-type flip-flop drivers and high voltage NMOS output (open drain output) in a 20 pin package. Each bit, there are a common clear and clock input. The input signal is output with the rising edge of clock signals. The voltage of maximum 15 V can be impressed to the drain-source voltage.

# Features

- Application of amusement equipment.

- Output voltage :  $V_{DS}$  (max) = 15 V

- Output current :  $I_{DS}$  (max) = 200 mA (par pin)

- Supply voltage range : 3.0 to 5.5 V

- Operating temperature range : -20 to +85 °C

- Quiescent supply current : 5 µA max.

- Low input current :  $1 \mu A max$ .

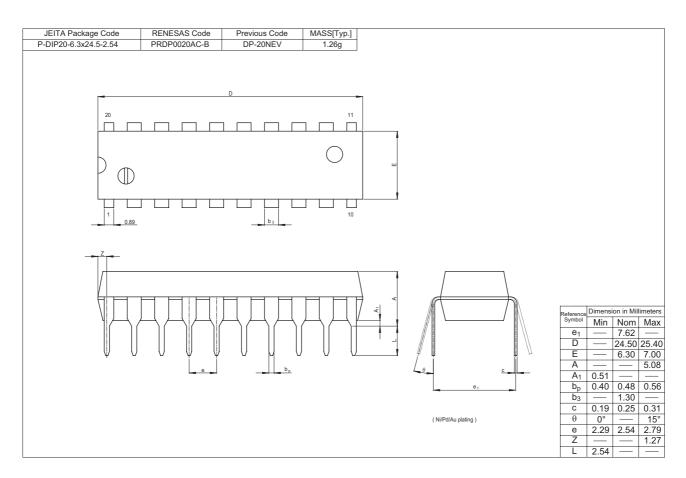

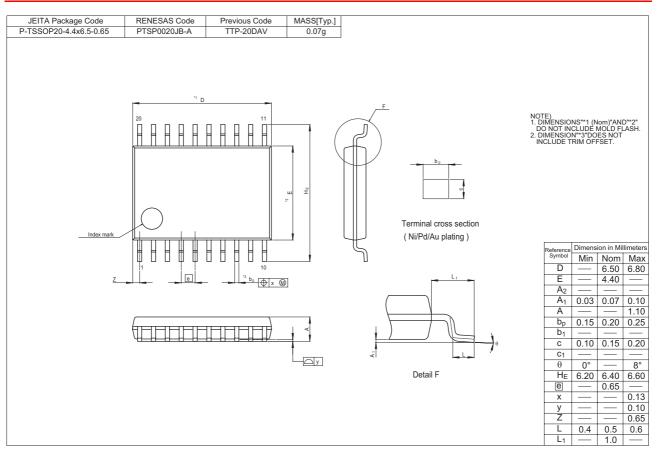

- Ordering Information

| Part Name     | Package Type | Package Code<br>(Previous Code) | Package<br>Abbreviation | Packing Abbreviation<br>(Quantity) | Surface<br>Treatment |

|---------------|--------------|---------------------------------|-------------------------|------------------------------------|----------------------|

| RD15LD74APT0  | SDIP-20 pin  | PRDP0020BA-A<br>(20P4B)         | Р                       | T (1,125 pcs/box)                  | 0 (Sn-Cu)            |

| RD15LD74ANPT0 | DILP-20 pin  | PRDP0020AC-B<br>(DP-20NEV)      | Р                       | T (1,000 pcs/box)                  | 0 (Ni/Pd/Au)         |

| RD15LD74ATH0  | TSSOP-20 pin | PTSP0020JB-A<br>(TTP-20DAV)     | Т                       | H (2,000 pcs/reel)                 | 0 (Ni/Pd/Au)         |

Note: Please consult the sales office for the above package availability.

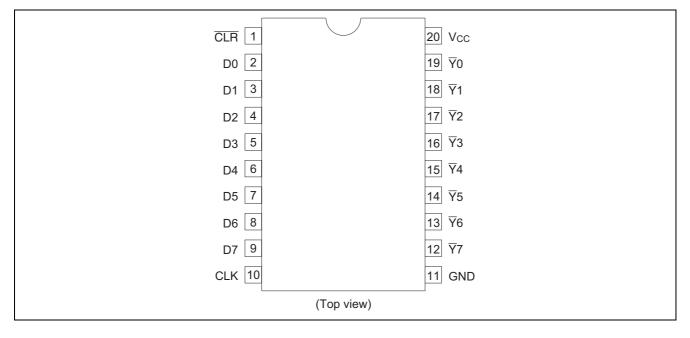

# **Pin Arrangement**

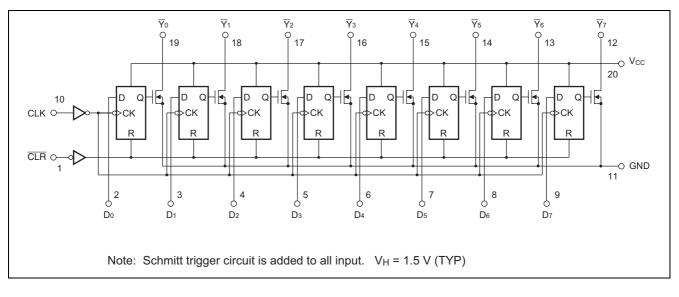

# Logic Diagram

# **Function Table**

|     | Output        |   |                |

|-----|---------------|---|----------------|

| CLR | CLK           | D | Ϋ́             |

| L   | Х             | Х | Z              |

| Н   | $\uparrow$    | L | Z              |

| Н   | $\uparrow$    | н | L              |

| Н   | L             | Х | Y <sub>0</sub> |

| Н   | $\rightarrow$ | Х | Y <sub>0</sub> |

H : High level

- L : Low level

- X : Immaterial

- Z : High Impedance

- $\uparrow$  : Low to High transition

- $\downarrow$  : High to Low transition

$Y_0$  : Level of  $\overline{Y}$  before the indicated steady input conditions were established.

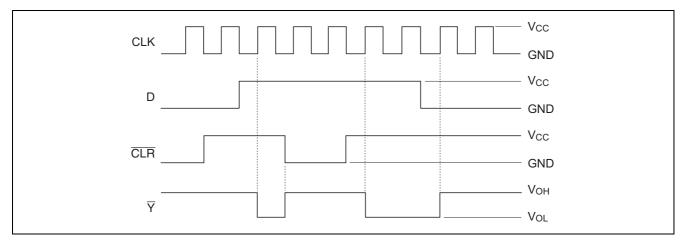

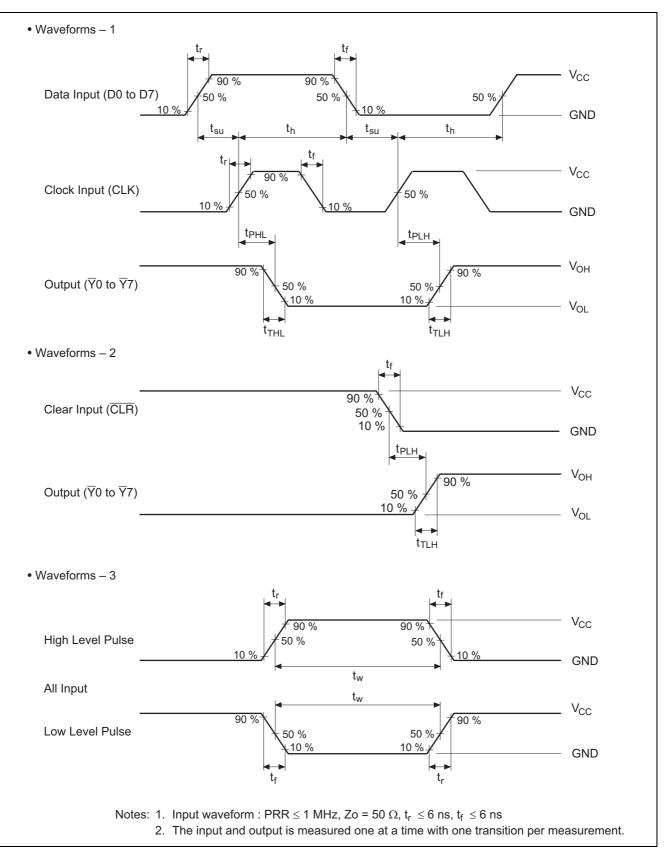

# **Timing Figure**

# **Absolute Maximum Ratings**

| Item Symbol                                |                 | Ratings          | Unit | Conditions         |                           |  |

|--------------------------------------------|-----------------|------------------|------|--------------------|---------------------------|--|

| Supply voltage                             | V <sub>CC</sub> | 6.5              | V    |                    |                           |  |

| Input voltage                              | VI              | –0.5 to $V_{CC}$ | V    |                    |                           |  |

| Output voltage                             | V <sub>DS</sub> | –0.5 to 15       | V    | Output : "Z" (off) |                           |  |

| Output current                             | I <sub>DS</sub> | 200              | mA   | Output : "on       | ", Current of one circuit |  |

|                                            |                 | 1.47             |      | SDIP               | Ta = 25°C                 |  |

| Maximum power<br>dissipation <sup>*1</sup> | PT              | 1.38             | W    | DILP               |                           |  |

| uissipation                                |                 | 0.76             |      | TSSOP              | Base implementation       |  |

| Storage temperature                        | Tstg            | -55 to +125      | °C   |                    |                           |  |

Note: The absolute maximum ratings are values which must not individually be exceeded, and furthermore no two of which may be realized at the same time.

1. The maximum package power dissipation was calculated using a junction temperature of 150°C

# **Recommended Operating Conditions**

| ltem                                                                              | Symbol                          | Ratings |                 | Unit     | Conditions         |                                |  |

|-----------------------------------------------------------------------------------|---------------------------------|---------|-----------------|----------|--------------------|--------------------------------|--|

| Supply voltage                                                                    | V <sub>CC</sub>                 | 3.0     | 5.5             | V        |                    |                                |  |

| Input voltage                                                                     | VI                              | 0       | V <sub>CC</sub> | V        |                    |                                |  |

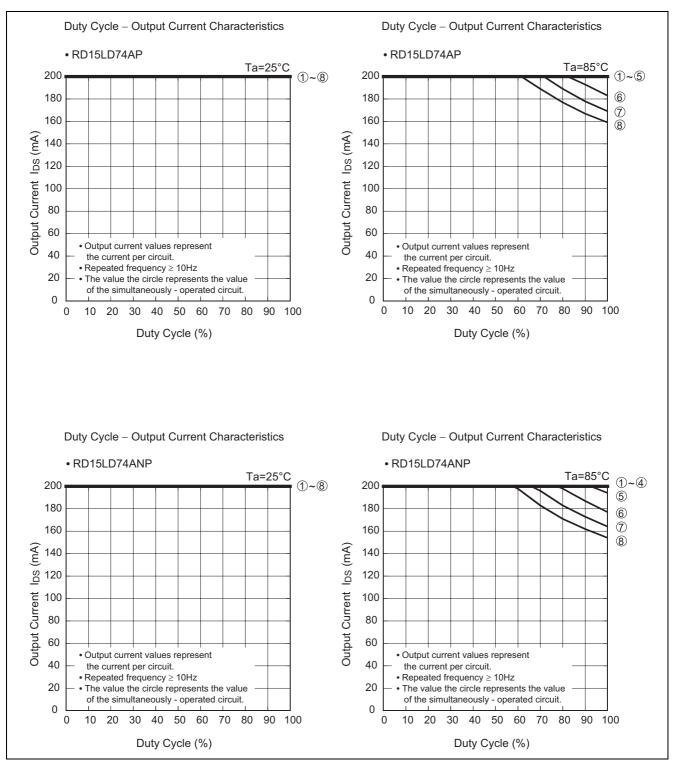

| Output voltage                                                                    | $V_{DS}$                        | 0       | 15              | V        | Output "Z"         | Output "Z" (off)               |  |

| Output current<br>(Current of an one circuit,<br>when eight circuit<br>operation) | I <sub>DS</sub>                 | 0       | 200             | mA       | SDIP               | Duty cycle $\leq 60\%$         |  |

|                                                                                   |                                 | 0       | 150             |          | JUIF               | Duty cycle ≤ 100%              |  |

|                                                                                   |                                 | 0       | 200             | mA<br>mA | DILP               | Duty cycle $\leq 55\%$         |  |

|                                                                                   |                                 | 0       | 140             |          | DILF               | Duty cycle ≤ 100%              |  |

|                                                                                   |                                 | 0       | 200             |          | TSSOP              | Duty cycle ≤ 25%               |  |

|                                                                                   |                                 | 0       | 105             |          | 1330F              | Duty cycle ≤ 100%              |  |

| Input rise / fall time                                                            | t <sub>r</sub> , t <sub>f</sub> | 0       | 500             | ns       | $V_{\rm CC} = 3.0$ | V <sub>CC</sub> = 3.0 V, 4.5 V |  |

| Operating temperature                                                             | Та                              | -20     | 85              | ۵°       |                    |                                |  |

Note: Unused or floating inputs must be held high or low.

# **Electrical Characteristics**

$(Ta = -20 \text{ to } +85^{\circ}C)$

| ltom                     | Symbol          | VCC (V)    | Ratings               |       |                       | Unit | Conditions                             |     |    |                        |

|--------------------------|-----------------|------------|-----------------------|-------|-----------------------|------|----------------------------------------|-----|----|------------------------|

| ltem                     |                 |            | Min                   | Тур   | Max                   | Unit | Conditions                             |     |    |                        |

|                          | Vih             | 3.0 to 3.6 | V <sub>CC</sub> ×0.84 | _     | —                     | V    |                                        |     |    |                        |

|                          |                 | 4.5 to 5.5 | V <sub>CC</sub> ×0.76 |       | _                     |      |                                        |     |    |                        |

| Input voltage            | Ma              | 3.0 to 3.6 | —                     |       | V <sub>CC</sub> ×0.16 | V    |                                        |     |    |                        |

|                          | VIL             | 4.5 to 5.5 | —                     | _     | V <sub>CC</sub> ×0.24 | V    |                                        |     |    |                        |

| Output voltage           | V <sub>DS</sub> | 3.0 to 3.6 | —                     | 0.30  | 0.45                  |      | I <sub>DS</sub> = 100 mA               |     |    |                        |

|                          |                 | 4.5 to 5.5 | —                     | 0.25  | 0.38                  | V    |                                        |     |    |                        |

|                          |                 | 3.0 to 3.6 | —                     | 0.60  | 0.90                  |      | I <sub>DS</sub> = 200 mA               |     |    |                        |

|                          |                 | 4.5 to 5.5 | —                     | 0.51  | 0.77                  |      |                                        |     |    |                        |

| "H" input current        | I <sub>IH</sub> | 3.0 to 5.5 | —                     | 0.005 | 1.0                   | μΑ   | $V_I = V_{CC}$                         |     |    |                        |

| "L" input current        | IIL             | 3.0 to 5.5 | —                     | 0.005 | -1.0                  | μΑ   | $V_1 = 0 V$                            |     |    |                        |

| Quiescent supply current | Icc             | 5.5        | _                     | 0.005 | 5.0                   | μA   | All output "Z" (off)                   |     |    |                        |

|                          |                 |            |                       |       |                       |      | $V_I = V_{CC}$ or GND                  |     |    |                        |

|                          |                 | 5.5        | —                     | 0.005 | 5.0                   |      | All output "on", $V_I = V_{CC}$ or GND |     |    |                        |

| Output off state         | I <sub>DS</sub> | 5.0        | 5.0                   | 5.0   | 5.0                   | _    | 0.002                                  | 5.0 | μA | V <sub>DS</sub> = 12 V |

| leak current             | טי              |            |                       | 0.002 | 0.0                   | μΛ   | VD2 - 12 V                             |     |    |                        |

| Output on resister       | R <sub>DS</sub> | 4.5        | —                     | 2.5   | 3.8                   | Ω    | I <sub>DS</sub> = 100 mA               |     |    |                        |

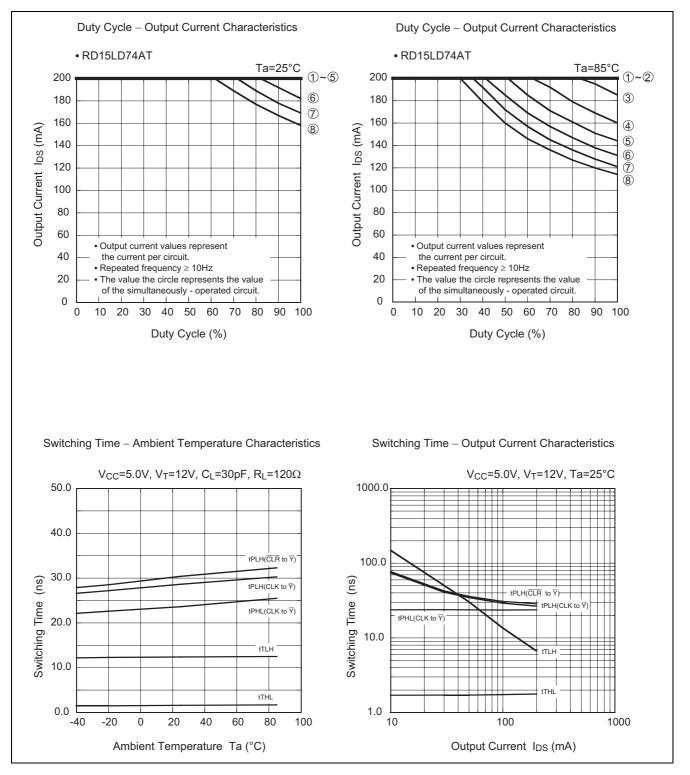

# Switching Characteristics

| ltem              | Symbol           | VCC (V)     | Ratings |     | Unit   | Conditions                                            |  |

|-------------------|------------------|-------------|---------|-----|--------|-------------------------------------------------------|--|

| nem               |                  | VCC (V)     | Min     | Max | Unit   | Conditions                                            |  |

| Maximum clock     | f <sub>max</sub> | $3.3\pm0.3$ | —       | 15  | MHz    |                                                       |  |

| frequency         |                  | $5.0\pm0.5$ | —       | 20  | IVITIZ |                                                       |  |

| Propagation delay | t                | $3.3\pm0.3$ | 1.0     | 65  | ns     | CLK, $\overline{\text{CLR}}$ to $\overline{\text{Y}}$ |  |

| time              | t <sub>PLH</sub> | $5.0\pm0.5$ | 1.0     | 50  | 115    |                                                       |  |

| Propagation delay | +                | $3.3\pm0.3$ | 1.0     | 60  | 20     |                                                       |  |

| time              | t <sub>PHL</sub> | $5.0\pm0.5$ | 1.0     | 45  | ns     | CLK to $\overline{Y}$                                 |  |

| Setup time        | t <sub>su</sub>  | $3.3\pm0.3$ | 25      | —   | ns     | D to CLK                                              |  |

|                   |                  | $5.0\pm0.5$ | 20      | —   | 115    |                                                       |  |

| Hold time         | t <sub>h</sub>   | $3.3\pm0.3$ | 3       | —   | - ns   | CLK to D                                              |  |

|                   |                  | $5.0\pm0.5$ | 3       | —   | 115    |                                                       |  |

| Pulse width       | t <sub>W</sub>   | $3.3\pm0.3$ | 50      | —   | ns     | CLK, CLR                                              |  |

| Puise width       |                  | $5.0\pm0.5$ | 40      | —   | 115    |                                                       |  |

| Output rise time  | t <sub>TLH</sub> | $3.3\pm0.3$ | —       | 30  | ns     | Ϋ́                                                    |  |

|                   |                  | $5.0\pm0.5$ | —       | 20  | 115    | I                                                     |  |

| Output fall time  | t <sub>THL</sub> | $3.3\pm0.3$ | —       | 10  | nc     | Ϋ́                                                    |  |

|                   |                  | $5.0\pm0.5$ | —       | 5   | ns     | 1                                                     |  |

$(Ta = -20 \text{ to } +85^{\circ}\text{C}, \text{ CL} = 30 \text{ pF}, \text{ tr} = \text{tf} = 6 \text{ ns})$

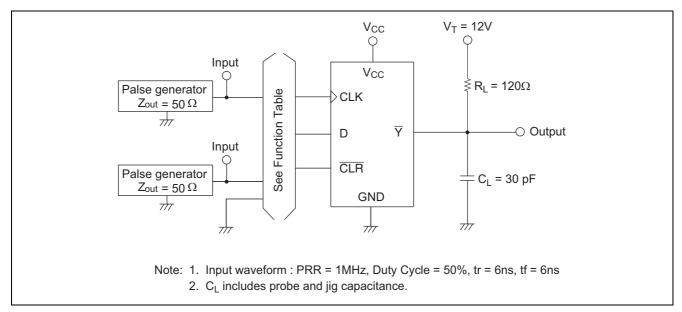

# **Test Circuit**

# Waveforms

### **Application Data**

### **Application Data**

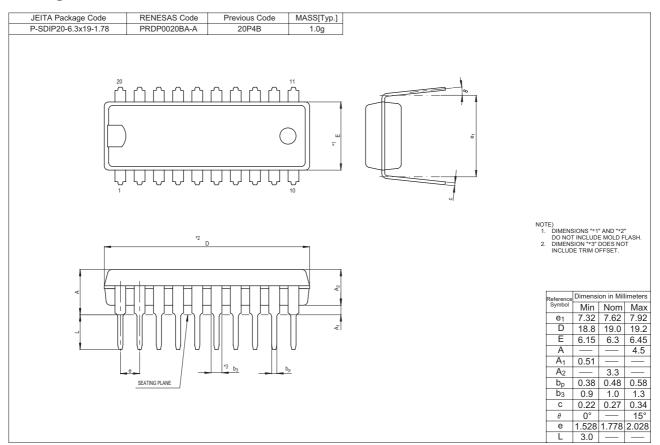

## Package Dimensions

RENESAS

### RD15LD74AP, RD15LD74ANP, RD15LD74AT

# RenesasTechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Benesas lechnology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

Pines

This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warranties or representations with respect to the accuracy or completeness of the information in this document.

But not infinited to, product data. diagrams, charts, programs, algorithms, and application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulation.

All information in this document, included in this document for the purpose of military application scuch as the development of weapons of mass and regulations, and proceedures required by such laws and regulations.

All information included in this document such as product data, diagrams, charts, programs, algorithms, and application carcuit examples, is current as of the date this document, when exporting the products or the technology described herein, you should follow the applicable export control laws and regulations.

Renesas has used reasonable care in compiling the information in this document, but Renesas assumes no liability whatsoever for any damages incurred as a set exception of protein ting from the date this document. Dut Renesas asproaces for description and the date dispersively and the information in this document. Dut Renesas assumes no liability whatsoever for any damages incurred as a set evention of the set of t

### **RENESAS SALES OFFICES**

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K. Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd. Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd. 7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

Renesas Technology Taiwan Co., Ltd. 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

# Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510

http://www.renesas.com