# RF109

## 2400 MHz Digital Spread Spectrum Transceiver

The RF109, a fully integrated transceiver device, provides the transmit, receive, and frequency synthesis functions for 2400 MHz digital spread spectrum systems operating in the 2400–2483.5 MHz portion of the ISM (Industrial, Scientific, Medical) band. The device has a direct conversion architecture that minimizes circuit complexity and cost.

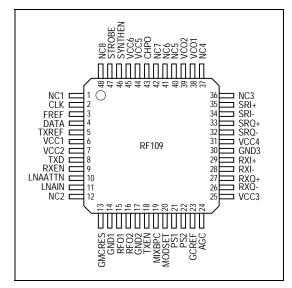

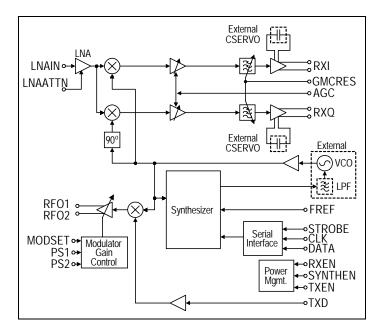

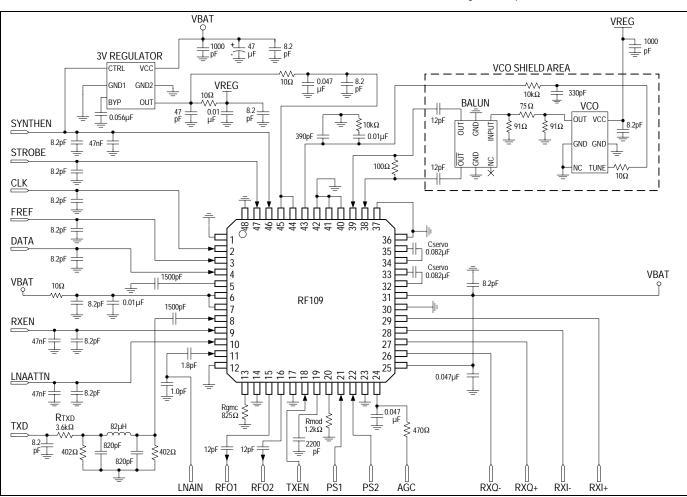

The receive path of the RF109 provides complete RF-to-baseband I/Q demodulation, including an LNA, double-balanced quadrature mixers, fully integrated baseband filters, and baseband variable-gain amplifiers. The transmit path is a variable-gain direct conversion modulator. Figure 1 shows the RF109's pin signals. Figure 2 shows the RF109 block diagram.

The RF109 generates the Local Oscillator (LO) frequencies using a Phase Lock Loop (PLL) frequency synthesizer and an external 2.4 GHz Voltage Controlled Oscillator (VCO). The PLL provides a full frequency range of 2392.2–2505.6 MHz.

The RF109 features low-voltage operation (3.0–4.5V) for low power consumption. A complete RF system solution for 2.4 GHz cordless telephone applications can be constructed with the RF109, a power amplifier, a differential 2.4 GHz frequency source and a Transmit/Receive (T/R) switch.

Figure 1. RF109 Pin Signals

## Features

- Low power dissipation

- Fast settling from standby mode to active mode

- Separate enable lines for transmit, receive, and synthesizer

- 64 programmable channels with 1.8 MHz channel spacing

- 3-battery-cell operation

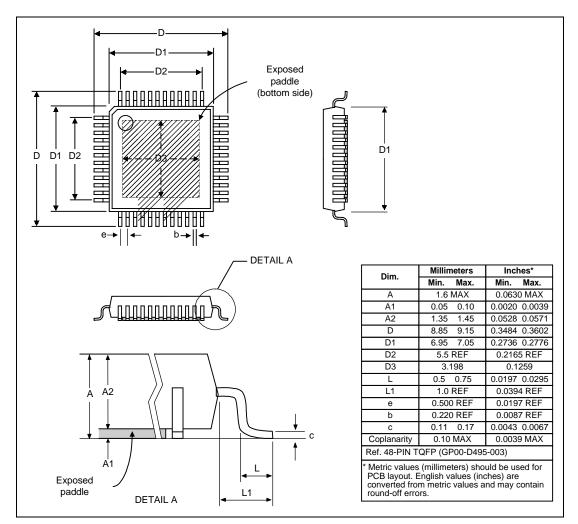

- 48-pin TQFP package with exposed paddle (refer to Figure 6)

### Receiver

- LNA/Quadrature mixer from RF down to baseband

- Selectable LNA gain

- Integrated baseband filter with external bandwidth adjustment

- Receiver baseband amplifier with automatic gain control

- Direct conversion with differential baseband outputs

- Low system noise figure (9.0 dB typical)

- Large dynamic range (89 dB typical)

- Transmitter

- Variable gain modulator

- Mixer for baseband-to-RF modulation

- Differential TX inputs and outputs

- Selectable transmitter output levels for high, medium, and low power modes

## **Applications**

- Digital Spread Spectrum (DSS) cordless telephone

- Direct sequence spread spectrum systems

- Frequency hopping spread spectrum systems

- Wireless LANs

- Wireless modems

- · Wireless security

- Inventory control systems

Figure 2. RF109 Block Diagram

## **Technical Description**

## Receive Path\_

The LNA provides two gain levels for coarse Automatic Gain Control (AGC), which are selected via the LNAATTN control. The signal is down-converted to In-phase and Quadraturephase (I/Q) baseband signals using a matched pair of mixers and the LO.

The receive baseband bandwidth has a bandpass characteristic. The I/Q baseband signals are internally low-pass and high-pass filtered to attenuate out-of-channel signals and to remove DC components. The low-pass cutoff is determined by the GmC filters and is set by the  $R_{gmc}$  resistor connected to pin 13. The high-pass cutoff is set by the value of the  $C_{servo}$  capacitors connected between pins 32–33, and pins 34–35.

The baseband high-pass cutoff frequency should be set much lower than the low-pass cutoff frequency or else the servo loop will become unstable.

The optimum receive bandwidth values are:

A matched pair of VGAs provide fine AGC. The differential I/Q baseband signals are DC-coupled to the RXI+, RXI-, RXQ+, and RXQ- outputs, respectively.

## Transmit Path\_

The transmit path consists of an amplifier and a mixer. The mixer modulates the LO with baseband data supplied to pin 8.

The transmit RF outputs from the RF109 are differential and matched for a  $100\Omega$  differential load. If a single-ended connection is required, then the unused output must be suitably terminated by a  $50\Omega$  resistor (as shown in Figure 5).

The transmit output power is determined by the output power control inputs, PS1 (pin 21) and PS2 (pin 22), and by the value of Rmod (connected to pin 20). Rmod sets the bias current into the modulator which is then multiplied by a factor set by the state of PS1 and PS2. PS1 and PS2 input programming is given in the Transmitter Section of Table 3.

## LO Generation \_

The LO is generated by a programmable PLL frequency synthesizer and a 2.4 GHz external VCO. Synthesizer performance parameters are determined by the loop filter, the external reference oscillator, the sensitivity and phase noise of the VCO, and the frequency synthesizer programming.

The RF109 requires differential inputs for VCO1 (pin 38) and VCO2 (pin 39). The typical differential input level is 200 mVp-p. A BALUN transformer, shown in Figure 5, is used to generate differential signals from a single-ended VCO output.

## Synthesizer Programming\_

The frequency synthesizer block is comprised of a divide-by-3 counter (D), 9.6 MHz reference frequency (FREF) source, a fixed reference divider of 16 (R), 16/17 prescaler (M), a fixed counter of 83 (N), a programmable counter of 64 (A),an external loop filter, and a 2.4 GHz external VCO.

The synthesizer can be programmed to cover 64 channels (channel spacing = 1.8 MHz) from 2392.2 MHz to 2505.6 MHz Table 1).

The LO frequency is given by the following equation:

$$f_{LO} = (D) \times (FREF/R) \times ((M \times N) + (A + 1))$$

, where N > A.

Example:

$f_{LO} = 3 \times (9.6 \text{ MHz} / 16) \times ((16 \times 83) + 7) = 2403.0 \text{ MHz}$  $f_{LO} = 3 \times (9.6 \text{ MHz} / 16) \times ((16 \times 83) + 46) = 2473.2 \text{ MHz}$

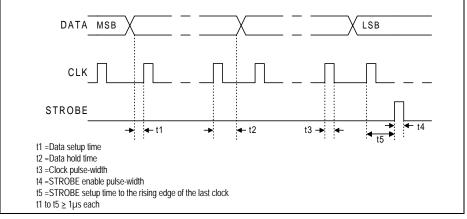

**Data Format.** The synthesizer is programmed with a halfduplex 3-wire serial interface. The three signals are DATA, CLK, and STROBE. Each rising edge of the CLK signal shifts one bit of the data into a shift register. When the STROBE input is toggled from low to high, the data latched in the shift register is transferred to the A counter. The data format is as follows:

| MSB | S7 | S6 | S5 | S4 | S3 | S2 | S1 | S0 | LSB |

|-----|----|----|----|----|----|----|----|----|-----|

| -   |    |    |    |    |    |    |    |    |     |

The timing relationship is shown in Figure 4. Programming bits S0 to S5, used for the A counter, are defined in Table 1. Bits S6 and S7 are reserved.

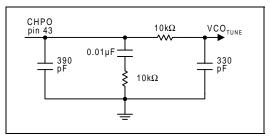

**Synthesizer Loop Filter.** A typical loop filter design is shown below in Figure 3. The loop bandwidth is approximately 5 kHz with a nominal phase margin of 45 degrees for a VCO sensitivity of 60 MHz/V.

Figure 3. Typical Loop Filter

## Power Management\_

Independent power-up/power-down control of the transmit path, receive path, and frequency synthesizer is provided by the TXEN, RXEN and SYNTHEN controls, respectively. When all of the functions are powered down, the current drain from the voltage supply (Vcc) is at a minimum.

Figure 4. Timing Diagram

| Synth. Channel No. (A) | Frequency (MHz) | S5 | S4 | S3 | S2 | S1 | S0 |

|------------------------|-----------------|----|----|----|----|----|----|

| 0                      | 2392.2          | 0  | 0  | 0  | 0  | 0  | 0  |

| 1                      | 2394.0          | 0  | 0  | 0  | 0  | 0  | 1  |

| 2                      | 2395.8          | 0  | 0  | 0  | 0  | 1  | 0  |

|                        |                 | :  | :  | :  | :  | :  | :  |

| 6                      | 2403.0          | 0  | 0  | 0  | 1  | 1  | 0  |

| 7                      | 2404.8          | 0  | 0  | 0  | 1  | 1  | 1  |

| 8                      | 2406.6          | 0  | 0  | 1  | 0  | 0  | 0  |

|                        | :               | :  | :  | ÷  | :  | ÷  | :  |

| 25                     | 2437.2          | 0  | 1  | 1  | 0  | 0  | 1  |

| 26                     | 2439.0          | 0  | 1  | 1  | 0  | 1  | 0  |

| 27                     | 2440.8          | 0  | 1  | 1  | 0  | 1  | 1  |

|                        |                 | :  | :  | ÷  | :  | ÷  | :  |

| 45                     | 2473.2          | 1  | 0  | 1  | 1  | 0  | 1  |

| 46                     | 2475.0          | 1  | 0  | 1  | 1  | 1  | 0  |

| 47                     | 2476.8          | 1  | 0  | 1  | 1  | 1  | 1  |

| :                      |                 | :  | :  | ÷  | :  | ÷  | :  |

| 61                     | 2502.0          | 1  | 1  | 1  | 1  | 0  | 1  |

| 62                     | 2503.8          | 1  | 1  | 1  | 1  | 1  | 0  |

| 63                     | 2505.6          | 1  | 1  | 1  | 1  | 1  | 1  |

## Table 1. Swallow Counter Data Input

## Recommendations on Layout and Implementation \_

A typical applications schematic is shown in Figure 5.

Decouple all Vcc pins as close as possible to the supply pin.

All ground pins should have minimum trace inductance to ground. If a ground plane cannot be provided right at the pins, the vias to the ground plane should be placed as close to the pins as possible. There should be one via for each ground pin. If the ground plane is at the bottom layer, it is recommended to have two vias in parallel for each ground pin.

Connect all no connect (NC) pins to the ground.

VCC1 (pin 6), VCC2 (pin 7), VCC3 (pin 25), and VCC4 (pin 31) should be connected to the common Vcc supply through individual decoupling networks.

RTXD should be chosen to provide a typical baseband spread spectrum signal level of 0.10 Vp-p, to the TXD pin (pin 8).

The routing of the trace to pin 3 (FREF) is very important to minimize the coupling of the reference clock (9.6 MHz) into the

LO. The FREF trace should be well isolated from all other traces, preferably by grounded strips on either side of the trace.

All traces from the VCO to pins 38 and 39 should be as short as possible with a characteristic impedance of 50  $\Omega.$

## Exposed Paddle Soldering

The RF109 48-pin TQFP package has an exposed (metal) paddle on the bottom. The footprint dimensions of the exposed paddle are shown in Figure 6. The printed circuit board should provide through hole connections to the ground plane to ground the exposed paddle. The solder mask opening should have the same size as the exposed paddle. All relevant manufacturing considerations for this type of package should be taken into account.

## ESD Sensitivity\_

The RF109 is a static-sensitive electronic device. Do not operate or store near strong electrostatic fields. Take proper Electrostatic Discharge (ESD) precautions.

Figure 5. Typical Application Diagram – RF109

## Interface Description

| Pin      | Signal       | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |              |                  | Digital Signals <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                         |

| 18       | TXEN         | Input            | Transmit Enable. Switches on/off bias power to the transmitter circuitry.<br>1: Tx on<br>0: Tx off                                                                                                                                                                                                                                                                                   |

| 9        | RXEN         | Input            | Receive Enable. Switches on/off bias power to the receiver circuitry.<br>1: Rx on<br>0: Rx off                                                                                                                                                                                                                                                                                       |

| 46       | SYNTHEN      | Input            | Synthesizer Enable. Switches on/off bias power to the synthesizer circuitry.<br>1: Synthesizer on<br>0: Synthesizer off                                                                                                                                                                                                                                                              |

| 21<br>22 | PS1<br>PS2   | Input<br>Input   | Transmit Power. These two control bits select the PA output power.<br>PS1=0, PS2=0: High (-8 dBm typical, single-ended)<br>PS1=0, PS2=1: Medium (-18 dBm typical, single-ended)<br>PS1=1, PS2=0: Low (-26.5 dBm typical, single-ended)<br>PS1=1, PS2=1: Undefined                                                                                                                    |

| 10       | LNAATTN      | Input            | LNA Attenuator. This control signal toggles the LNA gain between the low gain state and the high gain state.<br>1: Low gain, attenuator enabled<br>0: High gain, attenuator disabled                                                                                                                                                                                                 |

| 3        | FREF         | Input            | <b>Reference Oscillator.</b> This digital input clock signal is used to provide the reference frequency for the synthesizer. A 9.6 MHz clock provides channel spacing of 1.8 MHz (see Table 1).                                                                                                                                                                                      |

| 2        | CLK          | Input            | Synthesizer Programming Clock. This is the clock input signal used to serially shift the synthesizer data bits into the synthesizer input register. The rising edge of CLK is used to load each data bit.                                                                                                                                                                            |

| 4        | DATA         | Input            | Synthesizer Programming Data. This is the serial data input bit stream used to program the synthesizer. Data bits are shifted from MSB first to LSB. The DATA bit is loaded into the synthesizer input register on the rising edge of the CLK signal.                                                                                                                                |

| 47       | STROBE       | Input            | Synthesizer Programming Strobe. This signal is used to transfer the synthesizer data bits from the input register to the pulse swallow counter, after all of the data bits have been shifted in. The data is transferred on the rising edge of the STROBE signal.                                                                                                                    |

|          |              |                  | Analog Signals                                                                                                                                                                                                                                                                                                                                                                       |

| 8        | TXD          | Input            | <b>Transmit Data.</b> This input signal is used as the modulating signal. TXD is a single-ended, 1.2 Mbps NRZ signal from the baseband modem. The TXD signal shall be filtered first if any data/spectral shaping is desired. A resistor divider should be used to provide the desired signal level at the TXD input of the RF109.                                                   |

| 5        | TXREF        | Input            | Tx Reference. This is the reference for the TXD input. It is AC-coupled to ground.                                                                                                                                                                                                                                                                                                   |

| 23       | GCREF        | Input            | Gain Control Reference. This is the reference for the gain control input. It is connected to ground.                                                                                                                                                                                                                                                                                 |

| 28<br>29 | RXI-<br>RXI+ | Output<br>Output | <b>Received In-Phase Signal Negative, Received In-Phase Signal Positive.</b> This differential signal pair is the in-phase portion of the baseband output of the receiver. The differential output signal level is typically 0.5 Vp-p, within the AGC operating range of 1.35–1.9 V.                                                                                                 |

| 26<br>27 | RXQ-<br>RXQ+ | Output<br>Output | <b>Received Quadrature Signal Negative, Received Quadrature Signal Positive.</b> This differential signal pair is the quadrature portion of the baseband output of the receiver. The differential output signal level is typically 0.5 Vp-p, within the AGC operating range of 1.35–1.9 V.                                                                                           |

| 24       | AGC          | Input            | Auto Gain Control. This analog input signal is used to control the gain of the baseband VGAs in the receiver. This signal is generated by the baseband ASIC as part of the AGC control loop. An increase in the AGC voltage decreases the baseband VGA gain. The control loop provides a typical receive baseband differential signal of 0.5 Vp-p over the VAGC range of 1.35–1.9 V. |

| 38<br>39 | VCO1<br>VCO2 | Input<br>Input   | Voltage Controlled Oscillator. This differential input provides the local oscillator signal from an external VCO to the RF109 mixers. An external BALUN may be used to convert a single-ended external VCO signal to the differential signals, VCO1 and VCO2, required by the RF109. The differential input signal level required is typically 200 mVp-p.                            |

| 43       | CHPO         | Output           | Charge Pump Output. This output signal is used to control the external 2.4 GHz VCO. The CHPO current is typically ±250 µA.                                                                                                                                                                                                                                                           |

| 11       | LNAIN        | Input            | <b>RF Input.</b> This is the received RF input signal that is routed to the LNA of the RF109. This pin should be externally matched to 50 $\Omega$ . The received signal must be AC coupled into LNAIN with a 12 pF series capacitor.                                                                                                                                                |

| 15<br>16 | RFO1<br>RFO2 | Output           | <b>RF Output.</b> These are the differential transmit output signals from the RF109. The single-ended output impedance is 50 $\Omega$ . The RF output signals are internally AC-coupled. The unused signal should be terminated to ground through a 50 $\Omega$ resistor.                                                                                                            |

## Table 2. RF109 Pin Signal Description (1 of 2)

| Pin                                 | Signal                                                                                                            | Туре         | Description                                                      |  |  |  |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------------------------------|--|--|--|

|                                     | Miscellaneous                                                                                                     |              |                                                                  |  |  |  |

| 20                                  | 20 MODSET — Modulator Gain Setting. Transmit modulator gain can be adjusted by the resistor connected to the pin. |              |                                                                  |  |  |  |

| 13                                  | GMCRES                                                                                                            | _            | GMC resistor to set the cutoff frequency of the baseband filter. |  |  |  |

| 19                                  | MIXBPC                                                                                                            | _            | Mixer bias bypass capacitor.                                     |  |  |  |

| 32<br>33                            | SRQ-<br>SRQ+                                                                                                      | -            | Q channel DC offset cancellation servo capacitor connections.    |  |  |  |

| 34<br>35                            | SRI-<br>SRI+                                                                                                      | -            | I channel DC offset cancellation servo capacitor connections.    |  |  |  |

| 1, 12, 36, 37,<br>40, 41, 42,<br>48 | NC                                                                                                                | _            | No Connect. It is recommended to connect these pins to ground.   |  |  |  |

|                                     |                                                                                                                   |              | Power Supply Terminals                                           |  |  |  |

| 6                                   | VCC1                                                                                                              | Supply       | Positive supply terminal.                                        |  |  |  |

| 7                                   | VCC2                                                                                                              | Supply       | Positive supply terminal.                                        |  |  |  |

| 25                                  | VCC3                                                                                                              | Supply       | Positive supply terminal.                                        |  |  |  |

| 31                                  | VCC4                                                                                                              | Supply       | Positive supply terminal.                                        |  |  |  |

| 44                                  | VCC5                                                                                                              | Supply       | Positive supply terminal.                                        |  |  |  |

| 45                                  | VCC6                                                                                                              | Supply       | Positive supply terminal.                                        |  |  |  |

| 14, 17, 30                          | GND                                                                                                               | Supply       | Power supply ground terminal.                                    |  |  |  |

| Notes:<br>1. All digital s          | gnals are CMC                                                                                                     | )S compatibl | e.                                                               |  |  |  |

## Table 2. RF109 Pin Signal Description (2 of 2)

RF109

## Specifications

| Parameter                                                                                                                                    | Min  | Typical                      | Мах       | Units |

|----------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------------|-----------|-------|

| Receiver Section                                                                                                                             |      |                              |           |       |

| RX voltage gain:<br>LNA high-gain mode (LNAATTN = 0)<br>GC = 1.35 V<br>GC = 1.65 V<br>GC = 1.9 V                                             | 94.5 | 100<br>76<br>37              | 105.5     | dB    |

| LNA gain step delta Gain LNAATTN = 0/1                                                                                                       |      | 27                           |           | dB    |

| RX gain variation vs. frequency $2400 \text{ MHz} < f_{LO} < 2483.5 \text{ MHz}$                                                             | -1.5 | 0.5                          | 2.0       | dB    |

| RX SSB noise figure: High-gain mode, GC = 1.35 V                                                                                             |      | 9                            |           | dB    |

| RX input IP3: LNA high-gain mode, GC = 1.9 V<br>LNA low-gain mode, GC = 1.9 V                                                                |      | -33<br>-3                    |           | dBm   |

| RX input P1dB: LNA high-gain mode (LNAATTN = 0)<br>GC = 1.35 V<br>GC = 1.65 V<br>GC = 1.9 V<br>LNA low-gain mode (LNAATTN = 1)<br>GC = 1.9 V |      | -90.5<br>-65<br>-36<br>-10   |           | dBm   |

| I/Q phase imbalance                                                                                                                          |      |                              | ±7        | deg   |

| I/Q amplitude imbalance                                                                                                                      |      |                              | 3         | dB    |

| Input high voltage, LNAATTN, RXEN VIH                                                                                                        | 1.9  |                              |           | V     |

| Input low voltage, LNAATTN, RXEN VIL                                                                                                         |      |                              | 0.75      |       |

| Input high current, RXEN IIH                                                                                                                 |      | 125                          | 200       | μA    |

| Input low current , RXEN IIL                                                                                                                 | -10  |                              | 10        |       |

| Input high current, LNAATTN IIH                                                                                                              |      |                              | 60        | μA    |

| Input low current, LNAATTN IIL                                                                                                               | -10  |                              |           |       |

| GC lin                                                                                                                                       | -500 |                              | 500       | μA    |

| Baseband amplifier gain control range (GC = 1.35–1.9 V)                                                                                      |      | 63                           |           | dB    |

| GC input voltage range                                                                                                                       | 1.35 | 1.65                         | 1.9       | V     |

| Baseband amplifier gain control sensitivity<br>GC = 1.35–1.9 V<br>GC = 1.35 V<br>GC = 1.65 V<br>GC = 1.90 V                                  |      | 0.14<br>0.01<br>0.15<br>0.13 | 0.17      | dB/mV |

| RX P1dB @ 3.9 MHz offset LNA high gain, GC=1.9V                                                                                              |      | -24                          |           | dBm   |

| Baseband output load capacitance                                                                                                             |      | 20                           | 50        | pF    |

| Baseband LPF 3 dB bandwidth (Rgmc = 825 $\Omega$ )                                                                                           | 650  | 820                          | 970       | kHz   |

| Baseband selectivity @ 3.9 MHz                                                                                                               | 60   | 70                           |           | dB    |

| Baseband common mode output                                                                                                                  | 1.0  | Vcc – 1.55                   | Vcc - 1.0 | V     |

| Baseband I,Q DC offset                                                                                                                       |      |                              | 25        | mV    |

| RXI, RXQ DC and gain settle time <sup>(2)</sup> from initial RXEN input at TDD rate > 250 Hz                                                 |      | 50                           | 100       | μs    |

| Baseband HPF 3dB bandwidth (servo capacitors = 82 nF)                                                                                        | 13   | 22                           | 29        | kHz   |

| Baseband output voltage swing (peak differential)                                                                                            |      | 250                          |           | mVp   |

| Baseband output SNR (GC = 1.9 V)                                                                                                             |      | 31                           |           | dB    |

## Table 3. Electrical Specifications<sup>(1)</sup> (1 of 3)

Note: TA = 25°C, VCC = 3.6 V, fLO= 2449.8 MHz

| Parameter                                                                                               | Min     | Typical           | Мах    | Units            |

|---------------------------------------------------------------------------------------------------------|---------|-------------------|--------|------------------|

| Transmitter Section                                                                                     | on      |                   |        |                  |

| Gain variation vs. frequency 2400 MHz < fLO < 2483.5 MHz                                                |         | 0.5               | 1.5    | dB               |

| Peak-envelope output power (single-ended): <sup>(3)</sup>                                               |         |                   |        |                  |

| High power mode (PS1 = 0, PS2 = 0)<br>Medium power mode (PS1 = 0, PS2 = 1)                              | -10.5   | -8.0<br>-18       | -5.0   | dBm              |

| Low power mode (PS1 = 1, PS2 = 0)<br>Undefined mode (PS1 = 1, PS2 = 1)                                  |         | -26.5<br>not used |        |                  |

| IM3 (TXD input signal 2 tones each 60 mVpp)                                                             |         | -35               |        | dBc              |

| LO suppression relative to peak                                                                         |         | -25               | -15    | dBc              |

| TXD input impedance                                                                                     |         | 10                |        | kΩ               |

| TXD input peak-to-peak baseband spread spectrum signal for specified output peak envelope power         |         | 100               |        | mV <sub>pp</sub> |

| TXD input bandwidth                                                                                     |         | 80                |        | MHz              |

| TXD to RF settle time to within spec value from TXEN                                                    |         |                   | 50     | μs               |

| Input high voltage, PS1, PS2, TXEN VIH<br>Input low voltage, PS1, PS2, TXEN VIL                         | 1.9     |                   | 0.75   | V                |

| Input high current, PS1, PS2, TXEN IIH<br>Input Iow current, PS1, PS2, TXEN IIL                         | -10     |                   | 60     | μΑ               |

| Input high current TXEN IIH<br>Input low current TXEN IIL                                               | -10     |                   | 100    | μΑ               |

| Frequency Synthesizer                                                                                   | Section |                   |        |                  |

| Synthesizer frequency range                                                                             | 2392.2  |                   | 2505.6 | MHz              |

| Differential LO input power across VCO1 and VCO2                                                        | -17     | -13               | -9     | dBm              |

| Input reference frequency, FREF                                                                         |         | 9.6               |        | MHz              |

| Frequency step, Fs                                                                                      |         | 1800              |        | kHz              |

| Comparison frequency (600 kHz) spur level                                                               |         |                   | -60    | dBc              |

| Input high voltage, STROBE, CLK, DATA, SYNTHEN VIH<br>Input low voltage, STROBE, CLK, DATA, SYNTHEN VIL | 1.9     |                   | 0.75   | V                |

| Input high current, STROBE, CLK, DATA IIH<br>Input low current, STROBE, CLK, DATA IIL                   | -10     |                   | 40     | μA               |

| Input high current, SYNTHEN IIH<br>Input low current, SYNTHEN IIL                                       | -10     |                   | 100    | μA               |

| Input high voltage, FREF VIH<br>Input low voltage, FREF VIL                                             | 1.9     |                   | 0.75   | V                |

| Input high current, FREF IIH<br>Input low current, FREF IIL                                             | -10     |                   | 100    | μA               |

| Charge-pump output current                                                                              |         | ±250              |        | μA               |

| Output short-circuit current CHPO                                                                       |         |                   | 1.0    | mA               |

| Table 3. | Electrical | Specifications | (2 of 3) |

|----------|------------|----------------|----------|

|----------|------------|----------------|----------|

| Table 3. | Electrical | Specifications | (3 of 3) |

|----------|------------|----------------|----------|

|----------|------------|----------------|----------|

| Parameter                                                                                        | Min                     | Typical        | Max | Units          |  |  |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------|----------------|-----|----------------|--|--|--|--|

| Power Supply                                                                                     |                         |                |     |                |  |  |  |  |

| Total supply current:                                                                            |                         |                |     |                |  |  |  |  |

| RX mode (RXEN, SYNTHEN = 1)                                                                      | 67                      | 89             | 111 | mA             |  |  |  |  |

| TX + SYNTH supply current: <sup>(3)</sup> High power mode<br>Medium power mode<br>Low power mode | 31                      | 41<br>33<br>31 | 51  | mA<br>mA<br>mA |  |  |  |  |

| Synth mode (SYNTHEN = 1)<br>Sleep mode (RXEN, TXEN, SYNTHEN, LNAATTN = 0)                        |                         | 25<br>5        | 100 | mΑ<br>μΑ       |  |  |  |  |

| Power supply range <sup>(1)</sup>                                                                | 3.0                     | 3.6            | 4.5 | VDC            |  |  |  |  |

| Notes:                                                                                           |                         |                |     |                |  |  |  |  |

| 1. The specifications in Table 3 are guaranteed at a supply voltage of 3.6 VI                    | DC, and TA = 25°C.      |                |     |                |  |  |  |  |

| 2. Gain settled to within 90% of final value, DC settled to within 10% of desir                  | ed signal's final value |                |     |                |  |  |  |  |

| 3. TXD input signal 120 mVpp, 300 kHz sinusoidal at pin 8, Rmod = 1.2 k $\Omega$ .               |                         |                |     |                |  |  |  |  |

## Table 4. Absolute Maximum Ratings

| Parameter                          | Min  | Мах | Unit |  |  |  |  |

|------------------------------------|------|-----|------|--|--|--|--|

| Supply voltage (Vcc) <sup>1</sup>  | -0.3 | 5   | V    |  |  |  |  |

| Input voltage range <sup>1</sup>   | -0.3 | VCC | V    |  |  |  |  |

| Power dissipation                  |      | 700 | mW   |  |  |  |  |

| LNA input power                    |      | +5  | dBm  |  |  |  |  |

| Operating temperature range (TA)   | -10  | 70  | °C   |  |  |  |  |

| Storage temperature                | -40  | 125 | °C   |  |  |  |  |

| Notes:                             |      |     |      |  |  |  |  |

| 1. Voltages are referenced to GND. |      |     |      |  |  |  |  |

## **Device Dimensions**

RF109 device dimensions are shown below in Figure 6.

Figure 6. RF109 Device Dimensions

Copyright © 2000, Conexant Systems, Inc. All Rights Reserved.

Information in this document is provided in connection with Conexant Systems, Inc. ("Conexant") products. These materials are provided by Conexant as a service to its customers and may be used for informational purposes only. Conexant assumes no responsibility for errors or omissions in these materials. Conexant may make changes to specifications and product descriptions at any time, without notice. Conexant makes no commitment to update the information contained herein. Conexant shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Conexant's Terms and Conditions of Sale for such products, Conexant assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF CONEXANT PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Conexant further does not warrant the accuracy or completeness of the information, text, graphics or other items contained within these materials. Conexant shall not be liable for any special, indirect, incidental, or consequential damages, including without limitation, lost revenues or lost profits, which may result from the use of these materials.

Conexant products are not intended for use in medical, life saving or life sustaining applications. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Conexant, the Conexant C symbol, and "What's Next in Communications Technologies". Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

### Further Information:

literature@conexant.com 1-800-854-8099 (North America) 33-14-906-3980 (International)

Web Site www.conexant.com

### World Headquarters

Conexant Systems, Inc. 4311 Jamboree Road, P.O. Box C Newport Beach, CA 92658-8902 Phone: (949) 483-4600 Fax: (949) 483-6375

**U.S. Florida/South America** Phone: (727) 799-8406 Fax: (727) 799-8306

U.S. Los Angeles Phone: (805) 376-0559 Fax: (805) 376-8180

U.S. Mid-Atlantic Phone: (215) 244-6784 Fax: (215) 244-9292

**U.S. North Central** Phone: (630) 773-3454 Fax: (630) 773-3907

U.S. Northeast Phone: (978) 692-7660 Fax: (978) 692-8185

U.S. Northwest/Pacific West Phone: (408) 249-9696 Fax: (408) 249-7113

U.S. South Central Phone: (972) 733-0723 Fax: (972) 407-0639

**СО N E X A N T**<sup>™</sup>

What's next in communications technologies™

U.S. Southeast Phone: (919) 858-9110 Fax: (919) 858-8669

**U.S. Southwest** Phone: (949) 483-9119 Fax: (949) 483-9090

APAC Headquarters

Conexant Systems Singapore, Pte. Ltd. 1 Kim Seng Promenade Great World City #09-01 East Tower Singapore 237994 Phone: (65) 737 7355 Fax: (65) 737 9077

Australia

Phone: (61 2) 9869 4088 Fax: (61 2) 9869 4077

China Phone: (86)

Phone: (86 2) 6361 2515 Fax: (86 2) 6361 2516

#### Hong Kong

Phone: (852) 2 827 0181 Fax: (852) 2 827 6488

### India

Phone: (91 11) 692 4780 Fax: (91 11) 692 4712

### Korea - Seoul Office

Phone: (82 2) 565 2880 Fax: (82 2) 565 1440

Korea - Taegu Office Phone: (82 53) 745 2880 Fax: (82 53) 745 1440

### Europe Headquarters

Conexant Systems France Les Taissounieres B1 1681 Route des Dolines BP 283 06905 Sophia Antipolis Cedex France Phone: (33 1) 41 44 36 50 Fax: (33 1) 93 00 33 03

### **Europe Central**

Phone: (49 89) 829 1320 Fax: (49 89) 834 2734

Europe Mediterranean

Phone: (39 02) 9317 9911 Fax (39 02) 9317 9913

### Europe North

Phone: (44 1344) 486 444 Fax: (44 1344) 486 555

### Europe South

Phone: (33 1) 41 44 36 50 Fax: (33 1) 41 44 36 90

### Middle East Headquarters

Conexant Systems Commercial (Israel) Ltd. P.O. Box 12660 Herzlia 46733 Israel Phone: (972 9) 952 4064 Fax: (972 9) 951 3924

### Japan Headquarters

Conexant Systems Japan Co., Ltd. Shimomoto Building 1-46-3 Hatsudai, Shibuya-ku Tokyo, 151-0061 Japan Phone: (81 3) 5371 1567 Fax: (81 3) 5371 1501

### Taiwan Headquarters

Conexant Systems, Taiwan Co., Ltd. Room 2808 International Trade Building 333 Keelung Road, Section 1 Taipei 110 Taiwan, ROC Phone: (886 2) 2720 0282 Fax: (886 2) 2757 6760