# RL56CSMV/3 and RL56CSM/3

AnyPort™ Multi-Service Access Processor Hardware Interface Description

Information provided by Conexant Systems, Inc. is believed to be accurate and reliable. However, no responsibility is assumed by Conexant for its use, nor any infringement of patents, copyrights, or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights or copyright of Conexant other than for circuitry embodied in Conexant products. Conexant reserves the right to change circuitry at any time without notice. This document is subject to change without notice.

Conexant products are not designed or intended for use in life support appliances, devices, or systems where malfunction of a Conexant product can reasonably be expected to result in personal injury or death. Conexant customers using or selling Conexant products for use in such applications do so at their own risk and agree to fully indemnify Conexant for any damages resulting from such improper use or sale.

K56flex is a trademark of Conexant Systems, Inc. and Lucent Technologies.

Conexant, the Conexant C symbol, "What's Next in Communications Technologies", AnyPort, and MNP EC are trademarks of Conexant Systems, Inc.

ARM is a trademark of ARM Ltd.

Product names or services listed in this publication are for identification purposes only, and may be trademarks or registered trademarks of third parties [their respective companies]. All other marks mentioned herein are the property of their respective [holders] owners.

©1999, Conexant Systems, Inc. All Rights Reserved

## **Table of Contents**

| 1. | INTR                            | ODUCTION                                                                                                                                                                                                                                                                         | 1-1                                                  |

|----|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|    | 1.1<br>1.2<br>1.3               | SUMMARY FEATURES TECHNICAL OVERVIEW  1.3.1 General Description  1.3.2 Digital Data Pump (DDP)  1.3.3 ARM Microcontroller (MCU)  1.3.4 Access Processor Operation  1.3.5 Access Processor Firmware  1.3.6 Supported Interfaces                                                    | 1-2<br>                                              |

| 2. | TECH                            | HNICAL SPECIFICATIONS                                                                                                                                                                                                                                                            | 2-1                                                  |

|    | 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | ESTABLISHING DATA MODEM CONNECTIONS                                                                                                                                                                                                                                              |                                                      |

|    | 2.6                             | LOW POWER SLEEP MODE                                                                                                                                                                                                                                                             |                                                      |

| 3. | HAR                             | DWARE INTERFACE                                                                                                                                                                                                                                                                  |                                                      |

|    | 3.1<br>3.2                      | HARDWARE SIGNALS  ELECTRICAL AND ENVIRONMENTAL SPECIFICATIONS  3.2.1 Operating Conditions and Absolute Maximum Ratings  3.2.2 Current and Power Requirements                                                                                                                     | 3-15<br>3-15                                         |

|    | 3.3                             | 3.2.3 Thermal Characteristics                                                                                                                                                                                                                                                    | 3-17<br>3-19<br>3-19                                 |

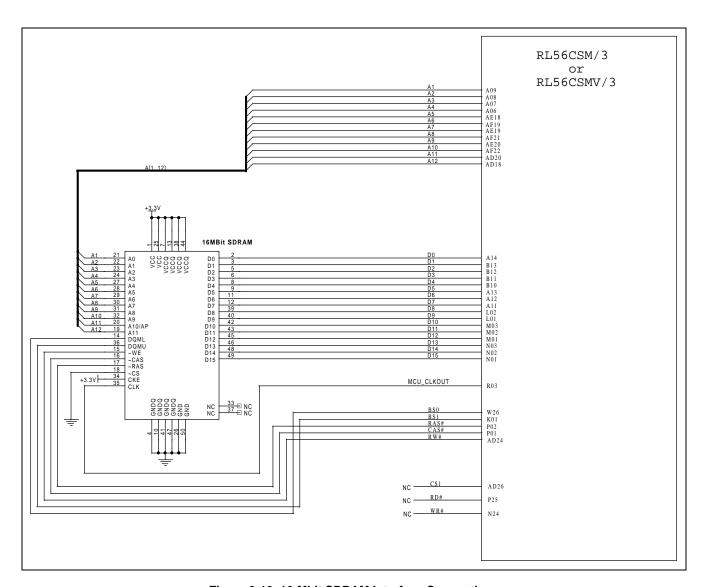

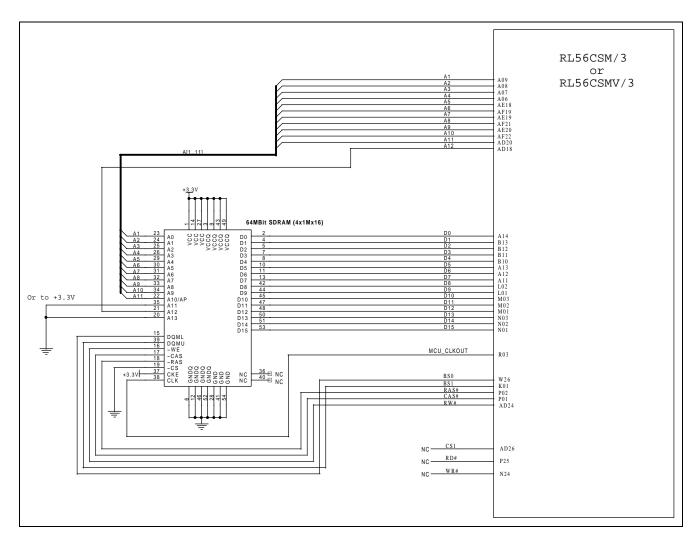

|    | 3.4                             | 3.3.3 Oscillator Waveform Requirements  SDRAM INTERFACE CONNECTIONS  3.4.1 16-Mbit SDRAM Interface  3.4.2 64-Mbit SDRAM Interface                                                                                                                                                | 3-22<br>3-22                                         |

| 4. | HOS                             | T INTERFACE                                                                                                                                                                                                                                                                      | <b>4-</b> 1                                          |

|    | 4.1<br>4.2                      | REGISTERS AND FIFO                                                                                                                                                                                                                                                               | 4-3<br>4-4<br>4-7<br>4-7<br>4-7                      |

| 5. | DESI                            | GN CONSIDERATIONS                                                                                                                                                                                                                                                                | 5-1                                                  |

|    | 5.1                             | PC BOARD LAYOUT GUIDELINES  5.1.1 General Principles  5.1.2 Component Placement  5.1.3 Signal Routing  5.1.4 Power  5.1.5 Ground Planes  5.1.6 Clock Oscillator Circuit  5.1.7 EMI Considerations for Standalone Modem Design  5.1.8 Optional Configurations  5.1.9 DDP Specific | 5-1<br>5-1<br>5-2<br>5-2<br>5-2<br>5-3<br>5-3<br>5-3 |

### RL56CSMV/3 and RL56CSM/3 Hardware Interface Description

| 5.2 | OSCIL             | LATOR SPECIFICATIONS     | 5-4 |

|-----|-------------------|--------------------------|-----|

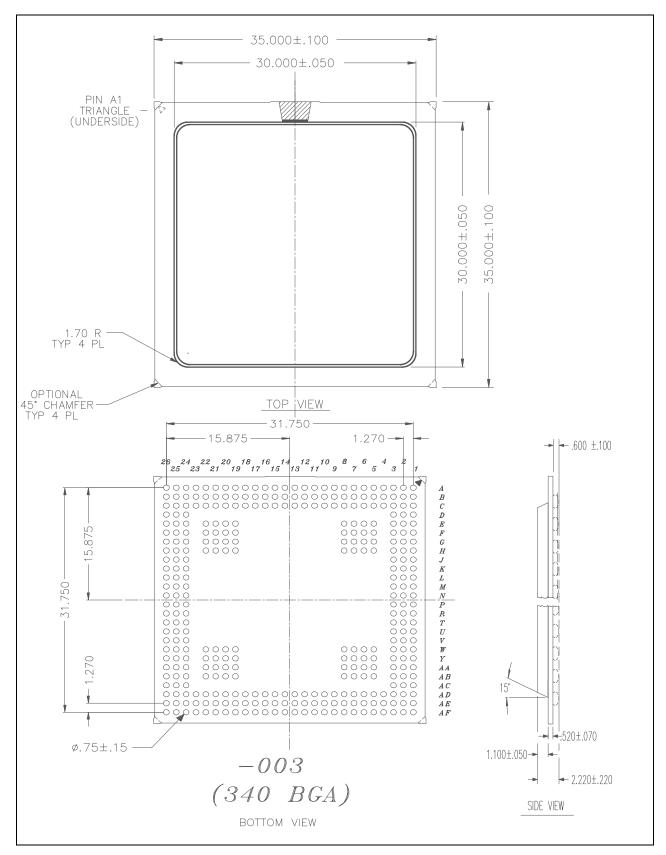

| 5.3 | PACK/             | AGE DIMENSIONS           | 5-6 |

| 5.4 | PLAS <sub>1</sub> | TIC BGA HANDLING AND USE | 5-8 |

|     | 5.4.1             | Handling                 | 5-8 |

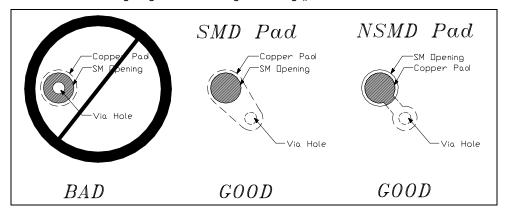

|     |                   | Circuit Card Design      |     |

|     | 5.4.3             | Solder Reflowing         | 5-8 |

|     | 5.4.4             | Inspection               | 5-9 |

|     | 5.4.5             | Rework and Removal       | 5-9 |

|     | 5.4.6             | Moisture                 | 5-9 |

|     | 547               | References               | 5-9 |

## **List of Figures**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-4                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Figure 3-1. RL56CSMV/3 Hardware Interface Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |

| Figure 3-2. RL56CSMV/3 340-Pin BGA Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                 |

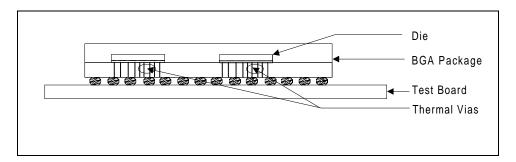

| Figure 3-3. Multi Die Ball Grid Array Package                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                 |

| Figure 3-4. Package Internal Heat Removal Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3-17                                                                            |

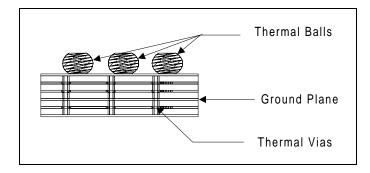

| Figure 3-5. Connecting BGA Thermal Balls to Motherboard Ground Plane by Using Thermal Vias                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-17                                                                            |

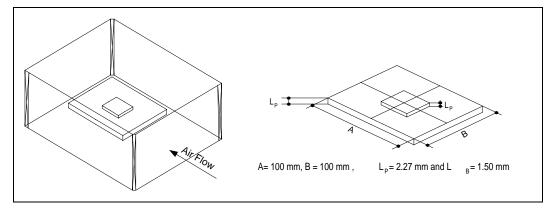

| Figure 3-6. Test Performance Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3-18                                                                            |

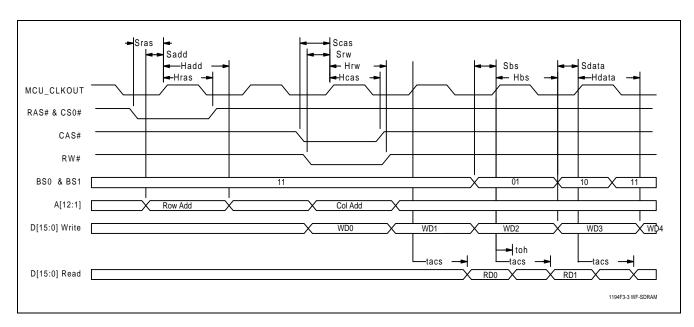

| Figure 3-7. SDRAM Interface Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-19                                                                            |

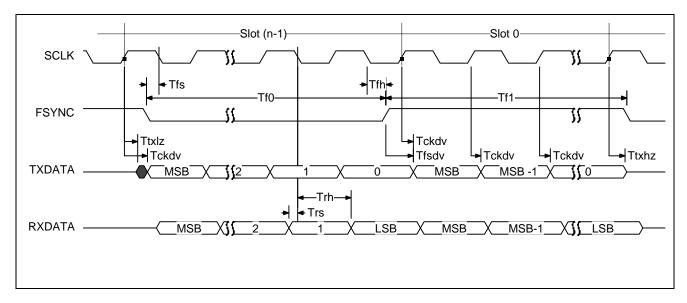

| Figure 3-8. TDM Bus Timing Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                 |

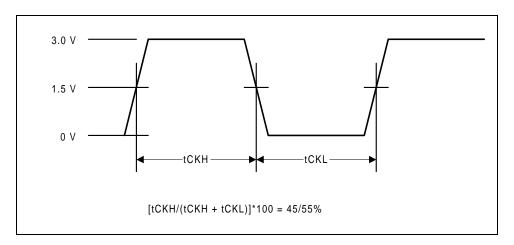

| Figure 3-9. Oscillator Waveform Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                 |

| Figure 3-10. 16-Mbit SDRAM Interface Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

| Figure 3-11. 64-Mbit SDRAM Interface Connections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                 |

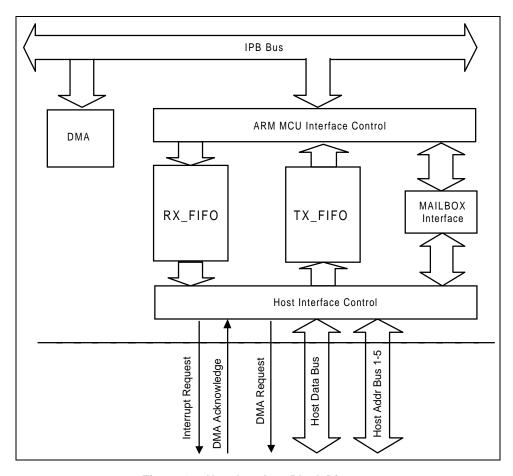

| Figure 4-1. Host Interface Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                 |

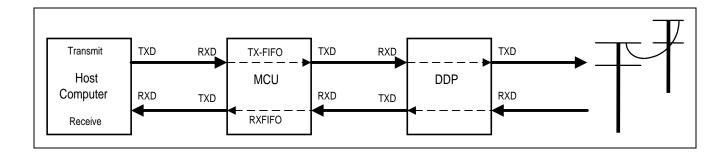

| Figure 4-2. Reference Direction For Modem Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                 |

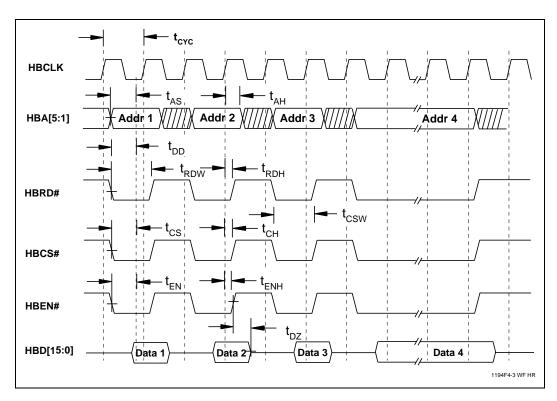

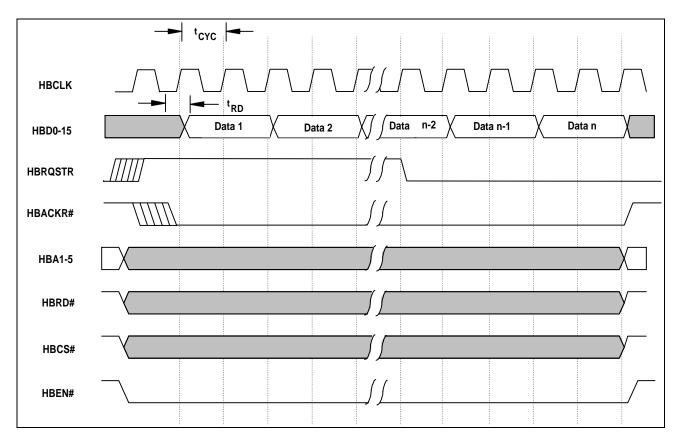

| Figure 4-3. Waveforms - Host Read                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                 |

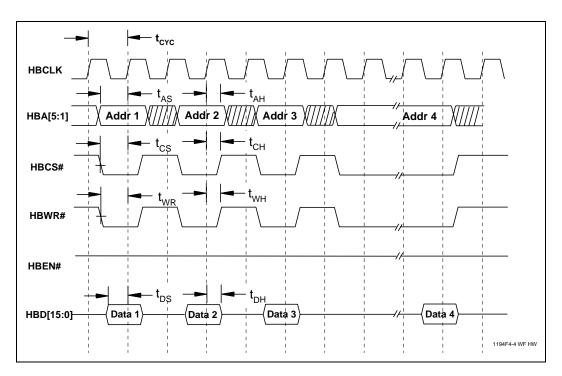

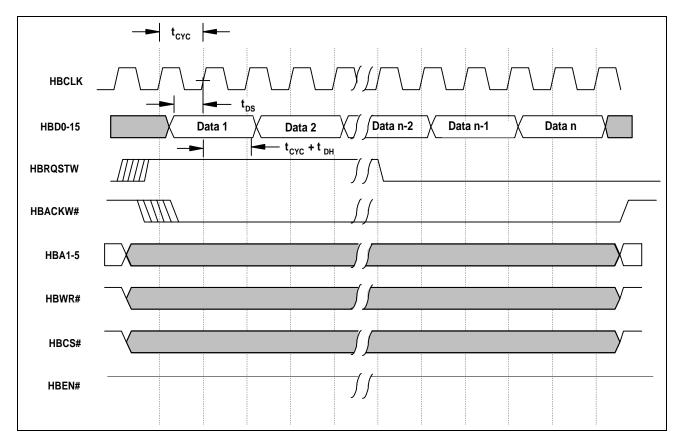

| Figure 4-4. Waveforms - Host Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                 |

| Figure 4-5. Host DMA Demand Mode Read, DMAMODE = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                 |

| Figure 4-6. Host DMA Demand Mode Write, DMAMODE = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                 |

| Figure 5-1. Package Dimensions - 340-Pin BGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                 |

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                 |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                 |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-4                                                                             |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-4<br>1-5                                                                      |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-4<br>1-5<br>3-4                                                               |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-2<br>1-5<br>3-2<br>3-6                                                        |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-5<br>3-4<br>3-6<br>3-6                                                        |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                 |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                 |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1-4<br>1-5<br>3-4<br>3-6<br>3-13<br>3-14<br>3-15                                |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel.  Table 1-3. Typical SDRAMs                                                                                                                                                                                                                                                                                                                                                                                                                             | 1-4<br>1-5<br>3-4<br>3-6<br>3-13<br>3-14<br>3-15                                |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel  Table 1-3. Typical SDRAMs  Table 3-1. RL56CSMV/3 Pin Signals by Pin Location  Table 3-2. RL56CSMV/3 Pin Signals by Interface.  Table 3-3. RL56CSMV/3 Signal Definitions.  Table 3-4. I/O Type Descriptions.  Table 3-5. Digital Electrical Characteristics  Table 3-6. Operating Conditions.  Table 3-7. Absolute Maximum Ratings.  Table 3-8. Current and Power Requirements                                                                          | 1-4<br>1-5<br>3-4<br>3-6<br>3-13<br>3-14<br>3-15<br>3-15                        |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel  Table 1-3. Typical SDRAMs  Table 3-1. RL56CSMV/3 Pin Signals by Pin Location  Table 3-2. RL56CSMV/3 Pin Signals by Interface.  Table 3-3. RL56CSMV/3 Signal Definitions.  Table 3-4. I/O Type Descriptions.  Table 3-5. Digital Electrical Characteristics  Table 3-6. Operating Conditions.  Table 3-7. Absolute Maximum Ratings.  Table 3-8. Current and Power Requirements  Table 3-9. Thermal Characteristics                                      | 3-4<br>3-6<br>3-13<br>3-13<br>3-14<br>3-15<br>3-16<br>3-16                      |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel  Table 1-3. Typical SDRAMs  Table 3-1. RL56CSMV/3 Pin Signals by Pin Location  Table 3-2. RL56CSMV/3 Pin Signals by Interface.  Table 3-3. RL56CSMV/3 Signal Definitions.  Table 3-4. I/O Type Descriptions.  Table 3-5. Digital Electrical Characteristics  Table 3-6. Operating Conditions.  Table 3-7. Absolute Maximum Ratings.  Table 3-8. Current and Power Requirements  Table 3-9. Thermal Characteristics  Table 3-10. SDRAM Interface Timing. | 1-4<br>1-5<br>3-4<br>3-6<br>3-13<br>3-14<br>3-15<br>3-16<br>3-16                |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-4 1-5 1-6 3-6 3-6 3-13 3-14 3-15 3-16 3-16 3-16 3-16 3-19 3-16 3-19 3-19 3-19 |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel Table 1-3. Typical SDRAMs                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-4 1-5 1-6 3-4 3-6 3-16 3-16 3-16 3-16 3-16 3-16 3-16                          |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1-4 1-5 3-4 3-6 3-15 3-15 3-16 3-16 3-20 4-2                                    |

| Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions.  Table 1-2. Logical Channel vs. Physical Channel Table 1-3. Typical SDRAMs                                                                                                                                                                                                                                                                                                                                                                                                                               | 1-4 1-5 1-6 3-4 3-6 3-15 3-15 3-16 3-16 3-16 3-16 4-7 4-8                       |

## **Document Revision Record**

#### Changes Incorporated in Revision 6

- 1. Figure 1-1: Revised SDRAM box.

- 2. Table 1-3: Added SDRAM part numbers.

- 3. Figure 1-1: Revised SDRAM box.

- 4. Table 3-3: Revised x\_SCLK I/O type.

- 5. Table 3-4: Added Itpu/Ot2 I/O type.

- 6. Table 3-5: Revised Output Voltage Low and Output Voltage High Test Conditions.

- 7. Section 3.4: Added.

#### Changes Incorporated in Revision 5

- 8. Throughout: Replaced VCC with VDD.

- Throughout: Replaced VGG5V with VGG.

- 10. Figure 1-1: Corrected x\_SCLK label.

- 11. Figure 3-1: Corrected RW# label and added CLK label.

- 12. Section 3.2: Added section headings and reorganized.

- 13. Table 3-1: Corrected RW# label.

- 14. Table 3-2: Corrected RW# label.

- 15. Table 3-3: Corrected MCU\_TEST# I/O type to Itpu and corrected RW# label.

- 16. Table 3-4: Updated C<sub>IN</sub> from 7 pF to 8pF.

- 17. Table 3-5: Added new table.

- 18. Table 3-8: Added power requirements for RL56CSMV/3.

- 19. Section 3.2.3: Revised thermal characteristics.

- 20. Section 3.3: Replaced Table 3-10 and Figure 3-3.

- 21. Table 3-11: Added notes.

- 22. Table 4-2: Added notes.

- 23. Table 3-3: Added notes.

- 24. Table 3-6: Revised.

- 25. Table 3-9: Replaced VDD in Limits with VGG, revised maximum Supply Voltage to 4.0 V, added Latch-up Current @ 125 °C.

- 26. Table 3-10: Revised.

- 27. Figure 3-3: Revised.

- 28. Section 3.2.3: Revised NOTES.

- 29. Table 4-2: Corrected t<sub>CS</sub> Symbol.

- 30. Figure 4-3: Revised.

- 31. Figure 4-4: Revised.

- 32. Table 5-1: Revised.

- 33. Table 5-2: Revised.

#### **Changes Incorporated in Revision 4**

- Added RL56CSMV/3 Voice enabled part to the AnyPort family.

- 2. Added Table 3-10, SDRAM Interface Timing and Figure 3-3. SDRAM Interface Timing

- 3. Added Figure 3-5, Oscillator Waveform Requirements.

- 4. Updated and corrected Figure 3-1, RL56CSMV/3 Hardware Interface Signals.

- 5. Renamed Channel Signal Names to match Logical Channels, as follows:

Old "A\_name" changed to "C\_name", old "B\_name" changed to "A\_name", old "C\_name" changed to "B\_name".

NOTE: This is a Signal Name change only. There is no functional change to device operation.

| Ball  | Old Name  | New Name  | Ball | Old Name  | New Name  | Ball | Old Name  | New Name  |

|-------|-----------|-----------|------|-----------|-----------|------|-----------|-----------|

| AC26  | A_SCLK    | C_SCLK    | G26  | B_SCLK    | A_SCLK    | F01  | C_SCLK    | B_SCLK    |

| AB25  | A_FSYNC   | C_FSYNC   | H26  | B_FSYNC   | A_FSYNC   | E01  | C_FSYNC   | B_FSYNC   |

| AD25  | A_RXDATA  | C_RXDATA  | K26  | B_RXDATA  | A_RXDATA  | C01  | C_RXDATA  | B_RXDATA  |

| A C25 | A_TXDATA  | C_TXDATA  | L26  | B_TXDATA  | A_TXDATA  | B01  | C_TXDATA  | B_TXDATA  |

| V 26  | A_PLLVDD  | C_PLLVDD  | C16  | B_PLLVDD  | A_PLLVDD  | G03  | C_PLLVDD  | B_PLLVDD  |

| AD16  | A_PLLGND  | C_PLLGND  | N25  | B_PLLGND  | A_PLLGND  | C09  | C_PLLGND  | B_PLLGND  |

| P26   | A_EYEXY   | C_EYEXY   | A19  | B_EYEXY   | A_EYEXY   | L03  | C_EYEXY   | B_EYEXY   |

| AA25  | A_EYESYNC | C_EYESYNC | F26  | B_EYESYNC | A_EYESYNC | G01  | C_EYESYNC | B_EYESYNC |

| Y 24  | A_EYECLK# | C_EYECLK# | E26  | B_EYECLK# | A_EYECLK# | H01  | C_EYECLK# | B_EYECLK# |

| U25   | A_TSAEN#  | C_TSAEN#  | A23  | B_TSAEN#  | A_TSAEN#  | J02  | C_TSAEN#  | B_TSAEN#  |

| R26   | A_XCLK    | C_XCLK    | A20  | B_XCLK    | A_XCLK    | C07  | C_XCLK    | B_XCLK    |

| R25   | A_YCLK    | C_YCLK    | A21  | B_YCLK    | A_YCLK    | C06  | C_YCLK    | B_YCLK    |

- 6. Updated Table 1-2, Logical Channel vs. Physical Channel.

- 7. Added Table 3-4, I/O Type Descriptions.

- 8. Updated Table 3-5, Digital Electrical Characteristics.

- 9. Updated Section 5.1.6, Clock Oscillator Circuit.

This page is intentionally blank.

#### 1. INTRODUCTION

#### 1.1 SUMMARY

The RL56CSMV/3 and RL56CSM/3 are members of the CONEXANT™ AnyPort™ family of multi-service access processors, and provide a complete solution to the transport of multiple media types between circuit-switched remote access and a variety of back-end networks. AnyPort processors are ideally suited for the network infrastructures resulting from the convergence of voice and data networking, addressing new requirements such as Voice and Fax over packet networks, ISDN and Cellular Data, while maintaining support of traditional PSTN Data/Fax needs.

**Note:** In this document, RL56CSMV/3 and CSMV/3 refer to both RL56CSMV/3 and RL56CSM/3 except as noted. Any reference to voice applies only to the RL56CSMV/3.

The CSMV/3 transcends existing modem solutions by providing a complete system solution for multi-service remote access. The combined DSP/RISC architecture provides an ideal engine to run CONEXANT's extensive suite of field-proven modulations, echo cancellers, voice coders, and communications protocols. In addition, performing functions such as T.38, V.120, async to sync HDLC conversion for PPP, V.110, and synchronous HDLC for PPP on ISDN connections, in the access processor allows system designers to reduce system overhead and increase scalability.

The CSMV/3 is a low-power system providing three communication channels in a single package. Powerful and downloadable DSP-based data pumps employ on-chip SRAM to allow upgrades to future voice and communication modulation schemes. An advanced RISC microcontroller manages three data pumps simultaneously. An innovative host interface to the Multi-Service Access Processor system uses a shared SDRAM memory to increase data throughput while reducing system cost and space. A programmable time slot selection feature provides direct digital connection to a T1/E1/PRI framing device.

A 35mm BGA package houses the CSMV/3 with extra balls available for thermal vias to minimize heat. A built-in phase lock loop (PLL) minimizes board noise while easing design. A quick-wake, sleep mode further reduces the power of this +3.3V access processor system.

This Hardware Interface Description describes the modem hardware capabilities. AT commands and S registers are defined in the AT Command Reference Manual (Order No. 1195). Additional information is described in the Software Interface Description (Order No. 1148) and the RL56DDP Modem Designer's Guide (Order No. 1141).

Model/Order/Part Numbers Supported Functions Part Number (340-Pin BGA) **Marketing Model Number** Data Fax Voice R7138-94 RL56CSM/3 Yes Yes Νo RL56CSMV/3 R7178-24 Yes Yes Yes

Table 1-1. RL56CSMV/3 and RL56CSM/3 Models and Functions

#### 1.2 FEATURES

#### Generic

- · Three access channels in one package

- +3.3V operation with +5V tolerant inputs

- Downloadable controller firmware and data pump code

- · Advanced RISC Machines (ARM) architecture

- · Low-power sleep mode with quick wake

- Glueless interface to Bt8370 T1/E1/PRI framer with time slot selection

- Built-in phase lock loop (PLL)

#### Signaling

- · DTMF detection and generation

- Multi frequency tone support for legacy network equipment (R1 and R2)

#### Data

- · Data modem modes

- PSTN: ITU-T V.90, K56flex, K56Plus, V.34 (33.6 kbps), V.FC, V.32 bis, V.32, V.22 bis, V.22A/B, V.23, and V.21; Bell 212A and 103

- ISDN: 64/56 kbps ISDN Basic Rate Interface B Channel HDLC control, or data pass-through mode for HDLC processing elsewhere in the central site system

- Internal error correction and data compression (ECC)

- V.42 LAPM, MNP 2-4, and MNP 10EC

- V.42 bis and MNP 5 data compression

- Async/sync HDLC conversion

- V.120 ISDN data

- V.110 cellular data

- LAP-B X.75

#### Voice (RL56CSMV/3 only)

- · Baseline configuration:

- G.723.1 and G.723.1 Annex A

- $-\,$  G.711  $\mu\text{-law}$  and A-law

- G.729 Annex A and Annex B

- G.168 128 ms Network Echo Canceller

- Patented robust jitter buffer

- Voice API using Mailbox Messages

#### FAX

- Fax modem send and receive rates up to 14400 bps

- V.17, V.33, V.29, V.27 ter, and V.21 channel 2

- Group 3, T.30 protocol and Class 1, 2 supported

- T.38 real-time fax protocol

#### Communications software-compatible AT command set

#### 1.3 TECHNICAL OVERVIEW

#### 1.3.1 General Description

The CSMV/3 provides the processing core for three channels of a central site Remote Access Server supporting high speed T1/E1/PRI digital lines. The OEM adds two oscillators, SDRAM, and discrete components to complete the Multi-Service Access Processor system.

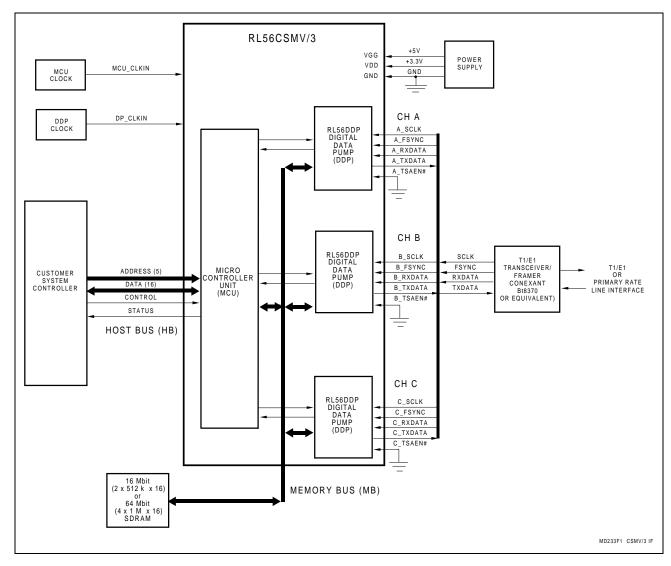

The access processor includes a full-featured, self-contained data/fax/Voice modem solution shown in Figure 1-1. Data modem handshake, fax modem protocol, voice codecs, and ISDN data connection functions are supported and controlled through the AT command set.

#### 1.3.2 Digital Data Pump (DDP)

The DDP is a +3.3V CONEXANT data pump supporting PSTN data/fax modem operation, ISDN B Channel call termination mode, and voice coding/decoding. The DDP executes internal code including downloadable modules from on-chip memory.

Digital data transfers serially between the T1/E1 framer device and the DDP at a data rate up to 8.192 Mbps. The T1/E1 framing device provides a strobe signal and the DDP TSA logic detects where the data for the channel starts in the serial TDM data stream using a programmable counter. The DDP performs PCM  $\mu$ -law or A-law conversion and synchronizes with an external network clock.

#### 1.3.3 ARM Microcontroller (MCU)

The ARM MCU performs the command processing and interfaces to the central site system controller via a 16-bit parallel host interface. Two 64-word deep FIFOs are used for improved data throughput between the access processor and system controller. This single powerful RISC processor controls three separate channels. A SDRAM loader is available to support download from the central site system controller on startup, if desired.

#### 1.3.4 Access Processor Operation

In data modem modes, each channel can independently connect to PSTN data modems at rates up to 56 kbps or ISDN terminal adapters at rates up to 64 kbps. A downloadable architecture allows for software download. For PSTN modems, complete handshake and data rate negotiations are performed. By optimizing the modem configuration for line conditions, the DDP can connect at the highest data rate that the channel can support from 56 kbps to 300 bps with automatic fallback. Automode operation in V.34 is provided in accordance with PN3320 and in V.32 bis in accordance with PN2330. All tone and pattern detection functions required by the applicable ITU or Bell standard are supported. Asynchronous to synchronous conversion is supported inside the controller to ease PPP processing in PSTN data mode.

When the remote end is an ISDN terminal adapter, the CSMV/3 provides HDLC control including HDLC Flag generation/detection, bit stuffing/extraction, and CRC generation/checking. V.120, V.110, and LAP-B X.75 are also supported. V.120 is a standard for encapsulating asynchronous data communications traffic into ISDN data streams.

In fax modem mode, the CSMV/3 supports Group 3 facsimile send and receive speeds of 14400, 12000, 9600, 7200, 4800, and 2400 bps. Fax modem modes support T.30 fax requirements. Fax data transmission and reception performed by the access processor are controlled and monitored through the EIA-578 Class 1 and Class 2 command interface. Both transmit and receive fax data are buffered within the access processor.

In Voice mode, the CSMV/3 encodes PCM audio data from the line into Real-Time Protocol (RTP) packets for the Host, and decodes RTP packets from the Host, to output PCM audio data to the line. In Voice mode, DTMF digits can be detected and transmitted, and a Voice Activity Detector can be enabled.

#### 1.3.5 Access Processor Firmware

Access processor firmware performs processing of general modem control, command sets, error correction and data compression, fax class 1 and class 2, voice coding and decoding (optional), and central site system controller interface functions.

The firmware is provided in object code form for executing from external SDRAM after download on startup using the ROM-coded Boot Loader. Equipment designers can add their own functions in firmware using commonly available development tools and the C programming language.

Figure 1-1. System Implementation Example Block Diagram

**Note:** Table 1-2 shows the DDP (physical) channel corresponding to the logical channel number programmed in the mailbox messages. The logical channel corresponds to the physical channel as follows: 0 = A, 1 = B, and 2 = C.

Table 1-2. Logical Channel vs. Physical Channel

| Logical Channel   | Corresponding Physical Channel |

|-------------------|--------------------------------|

| Logical Channel 0 | Physical Channel A             |

| Logical Channel 1 | Physical Channel B             |

| Logical Channel 2 | Physical Channel C             |

#### 1.3.6 Supported Interfaces

#### **Parallel Host Bus Interface**

The interface signals are: 16 bidirectional data lines (HBD0-HBD15), five address input lines (HBA1-HBA5), and six control lines (HBCS#, HBRD#, HBWR#, HBEN#, HBACKR#, and HBACKW#). Refer to the Software Interface Description (Order No. 1148) for FIFO and Mailbox description.

#### T1/E1 Transceiver Interface

The 4-line interface to the OEM-supplied T1/E1 Transceiver consists of the SCLK, FSYNC, and RXDATA inputs and the TXDATA output. The T1/E1 Transceiver interface timing is described in Section 3.2.3.

#### **SDRAM Interface**

The CSMV/3 provides address, data, and control lines to connect to a 16 Mbit (2 x 512 k x 16) or 64 Mbit (4 x 1 M x 16) Synchronous Dynamic RAM (SDRAM) meeting the Intel PC100 Specification. Typical SDRAMs that meet CSMV/3 requirements are listed in Table 1-3.

Table 1-3. Typical SDRAMs

| Manufacturer   | Part Number          |  |  |  |  |  |  |  |

|----------------|----------------------|--|--|--|--|--|--|--|

| 16-Mbit SDRAMs |                      |  |  |  |  |  |  |  |

| NEC            | UPD4516161AG5-A80    |  |  |  |  |  |  |  |

|                | UPD4516161AG5-A10    |  |  |  |  |  |  |  |

|                | UPD4516161AG5-A10B   |  |  |  |  |  |  |  |

| Hyundai        | HY57V161610CTC-8     |  |  |  |  |  |  |  |

|                | HY57V161610CTC-10P   |  |  |  |  |  |  |  |

|                | HY57V161610CTC-10S   |  |  |  |  |  |  |  |

| Fujitsu        | MB81F161622B -60     |  |  |  |  |  |  |  |

|                | MB81F161622B-70      |  |  |  |  |  |  |  |

|                | MB81F161622B-80      |  |  |  |  |  |  |  |

| Micron         | MT48LC1M16A1-TG-7SE  |  |  |  |  |  |  |  |

|                | 64-Mbit SDRAMs       |  |  |  |  |  |  |  |

| NEC            | UPD4564163G5-A10-9JF |  |  |  |  |  |  |  |

| Mitsubishi     | M2V64S40BTP          |  |  |  |  |  |  |  |

This page is intentionally blank.

#### 2. TECHNICAL SPECIFICATIONS

#### 2.1 ESTABLISHING DATA MODEM CONNECTIONS

In a typical application, the "system controller" processes all aspects of PSTN connection call setup, including off-hook signaling, sending dial digits, call progress detection, and ring detection for both T1/E1 lines and ISDN D-Channel control.

After a PSTN connection is established by the system controller, the system controller issues the ATA command to the CSMV/3 to start the Answer Handshake Sequence, or the ATD command to start the Originate Handshake Sequence.

#### **Modem Handshaking Protocol**

If a handshake is not completed within the time specified in the S7 register after the ATD or ATA command is issued, the modem aborts the handshake attempt.

#### **Answer Tone Detection**

Answer tone can be detected over the frequency range of 2100 ± 40 Hz in ITU-T modes and 2225 ± 40 Hz in Bell modes.

#### **Billing Protection**

When the modem goes off-hook to answer an incoming call, both transmission and reception of data are prevented for 2 seconds (data modem) or 4 seconds (fax adaptive answer) to comply with the billing delay requirement.

#### **Connection Speeds and CODEC Selection**

The modem functions as a data modem when the +FCLASS=0 command is active.

Line connection can be selected using the +MS command in accordance with the draft PN-3320 standard presented to the TR30-4 committee (which is a candidate for the definition of V.25 ter at the ITU). The +MS command selects modulation, enables/disables automode, selects minimum and maximum line speeds, and selects μ-Law or A-Law codec.

The +MS command is described in the AT Command Reference Manual (Order No. 1195).

#### Multi-frequency (MF) Tone Generation and Detection

Multi-frequency (MF) tone generation and detection is supported by the +VTS, +CTD, +PTF, and +QTR commands.

The +VTS, +CTD, +PTF, and +QTR commands are described in the AT Command Reference Manual (Order No. 1195).

#### 2.2 DATA MODE

Data mode exists when a connection has been established between modems and all handshaking has been completed.

#### **Speed Buffering (Normal Mode)**

Speed buffering allows a DTE to send data to, and receive data from, a modem at a speed different than the line speed. The modem supports speed buffering at all line speeds.

#### **Flow Control**

**DTE-to-Modem Flow Control.** Refer to the Software Interface Description (Order No. 1148).

#### **Escape Sequence Detection**

The "+++" escape sequence can be used to return control to the command mode from the data mode. Escape sequence detection is disabled by an S2 register value greater than 127, (or use &D2 and DTR drop - see S25 register, AT Command Reference Manual, Order No. 1195). Refer to the Software Interface Description (Order No. 1148).

#### **BREAK Generation and Detection**

Refer to the Software Interface Description (Order No. 1148).

#### **Telephone Line Monitoring**

**GSTN Cleardown (V.90, K56flex, V.34, V.32 bis, V.32).** Upon receiving GSTN Cleardown from the remote modem in a non-error correcting mode, the modem cleanly terminates the call.

#### Fall Forward/Fallback (V.34/V.32 bis/V.32)

During initial handshake, the modem will fallback to the optimal line connection within V.34/V.32 bis/V.32 mode depending upon signal quality if automode is enabled by the +MS or N1 command.

When connected in V.34/V.32 bis/V.32 mode, the modem will fall forward or fallback to the optimal line speed within the current modulation depending upon signal quality if fall forward/fallback is enabled by the %E2 command.

#### Retrain

The modem may lose synchronization with the received line signal under poor line conditions. If this occurs, retraining may be initiated to attempt recovery depending on the type of connection.

The modem initiates a retrain if line quality becomes unacceptable if enabled by the %E command. The modem continues to retrain until an acceptable connection is achieved, or until 30 seconds elapse resulting in line disconnect.

#### **Programmable Inactivity Timer**

The modem disconnects from the line if data is not sent or received for a specified length of time. In normal or error-correction mode, this inactivity timer is reset when data is received from either the DTE or from the line. This timer can be set to a value between 0 and 2550 seconds by using register S30. A value of 0 disables the inactivity timer.

#### 2.3 ERROR CORRECTION AND DATA COMPRESSION

#### V.42 Error Correction

V.42 supports two methods of error correction: LAPM and, as a fallback, MNP 4. The modem provides a detection and negotiation technique for determining and establishing the best method of error correction between two modems.

#### **MNP 2-4 Error Correction**

MNP 2-4 is a data link protocol that uses error correction algorithms to ensure data integrity. Supporting stream mode, the modem sends data frames in varying lengths depending on the amount of time between characters coming from the DTE.

#### V.42 bis Data Compression

V.42 bis data compression mode, enabled by the %Cn command or S46 register, operates when a LAPM or MNP 10EC connection is established.

The V.42 bis data compression employs a "string learning" algorithm in which a string of characters from the DTE is encoded as a fixed length codeword. Two 2k-byte dictionaries are used to store the strings. These dictionaries are dynamically updated during normal operation.

#### **MNP 5 Data Compression**

MNP 5 data compression mode, enabled by the %Cn command, operates during an MNP connection.

In MNP 5, the modem increases its throughput by compressing data into tokens before transmitting it to the remote modem, and by decompressing encoded received data before sending it to the DTE.

#### 2.4 FAX OPERATION

Facsimile functions operate in response to fax class 1 commands when +FCLASS=1 or in response to fax class 2 commands when +FCLASS=2.

In the fax mode, the on-line behavior of the modem is different from the data (non-fax) mode. After dialing, modem operation is controlled by fax commands. Other AT commands are still valid but may operate differently than in data modem mode.

Calling tone is generated in accordance with T.30.

#### 2.5 DIAGNOSTICS

#### 2.5.1 Commanded Tests

Diagnostics are performed in response to &T commands, per V.54.

Remote Digital Loopback (RDL) (&T6 Command). Data from the local DTE is sent to the remote modem which loops the data back to the local DTE.

Remote Digital Loopback with Self Test (&T7 Command). An internally generated pattern is sent from the local modem to the remote modem, which loops the data back to the local modem.

**Local Digital Loopback (&T3 Command).** When local digital loop is requested by the local DTE, two data paths are set up in the local modem. Data from the local DTE is looped back to the local DTE (path 1) and data received from the remote modem is looped back to the remote modem (path 2).

#### 2.5.2 DDP Test

Following an SDRAM download, the ROM-coded Boot Loader jumps to the starting address of the MCU firmware, and the MCU firmware will try to configure the DDPs. If any DDP does not configure correctly, that channel is reported as "down", and AT commands that require access to the DDP (e.g., ATD, ATA, ATH, or ATZ) will respond with ERROR.

#### 2.6 LOW POWER SLEEP MODE

**Sleep Mode Entry.** The DDPs enter the low power sleep mode when no line connection exists and no datapump activity occurs for the period of time specified in the S24 register. All DDP circuits are turned off in order to consume reduced power while being able to immediately wake up and resume normal operation.

**Wake-up.** When the Host requests a channel to be active, the MCU will wake-up the datapump for that channel. The wake-up process is transparent to the host.

This page is intentionally blank.

### 3. HARDWARE INTERFACE

#### 3.1 HARDWARE SIGNALS

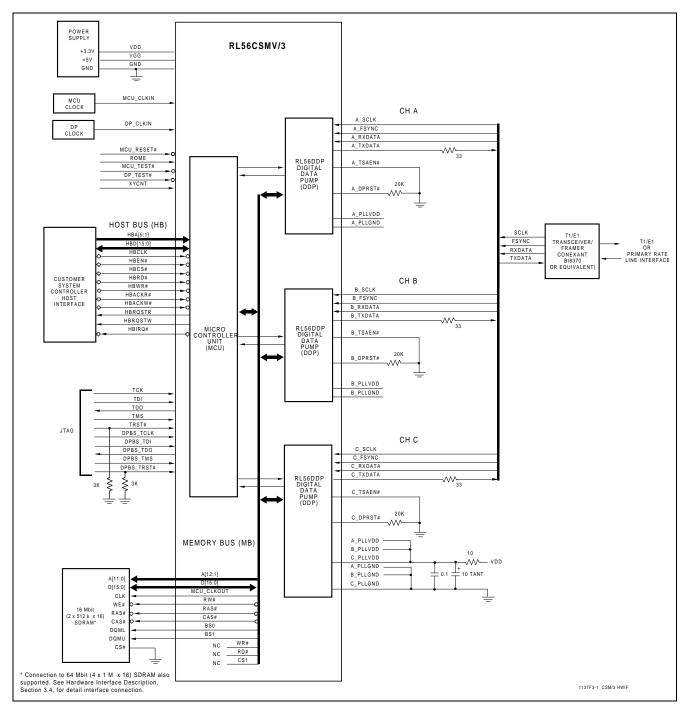

The RL56CSMV/3 interface is illustrated in Figure 3-1.

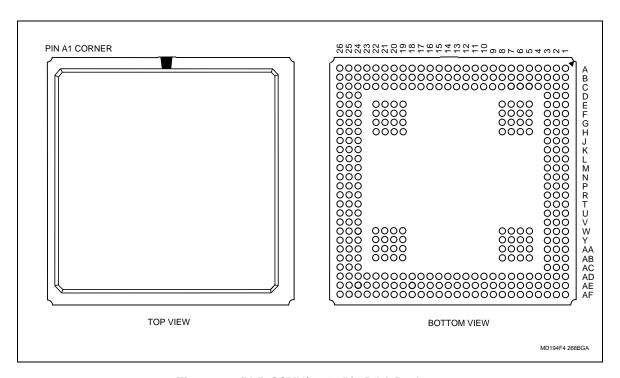

The RL56CSMV/3 BGA pin (ball) locations are shown in Figure 3-2.

The RL56CSMV/3 pin signals by pin location are listed in Table 3-1.

The RL56CSMV/3 pin signals by interface are listed in Table 3-2.

The RL56CSMV/3 hardware interface signals are defined in Table 3-3.

Hardware interface signal I/O types are described in Table 3-4.

Digital electrical characteristics for the hardware interface signals are listed in Table 3-5.

Figure 3-1. RL56CSMV/3 Hardware Interface Signals

Figure 3-2. RL56CSMV/3 340-Pin BGA Package

Table 3-1. RL56CSMV/3 Pin Signals by Pin Location

| Table<br>Col. |              | 1                      |                 |            | 2          |        |            | 3         |       |            | 4          |             |  |

|---------------|--------------|------------------------|-----------------|------------|------------|--------|------------|-----------|-------|------------|------------|-------------|--|

| Table<br>Row  | Loc.         | Signal                 | I/F             | Loc.       | Signal     | I/F    | Loc.       | Signal    | I/F   | Loc.       | Signal     | I/F         |  |

| 1             | A01          | C_DPRST#               | GND thru<br>20K | B25        | B_DPRXCLK  | TEST   | F03        | VDD       | 3.3V  | K25        | A_DPTXCLK  | TEST        |  |

| 2             | A02          | A_DPRST#               | GND thru<br>20K | B26        | RESERVED   |        | F05        | RESERVED  |       | K26        | A_RXDATA   | CH A        |  |

| 3             | A03          | B_DPRST#               | GND thru<br>20K | C01        | B_RXDATA   | СН В   | F06        | GND       | GND   | L01        | D9         | MB          |  |

| 4             | A04          | VGG                    | 5V              | C02        | RESERVED   |        | F07        | GND       | GND   | L02        | D8         | MB          |  |

| 5             | A05          | B_DPCS                 | TEST            | C03        | RESERVED   |        | F08        | GND       | GND   | L03        | B_EYEXY    | CH B        |  |

| 6             | A06          | A4                     | MB              | C04        | RESERVED   |        | F19        | GND       | GND   | L24        | XYCNT      | TEST        |  |

| 7             | A07          | А3                     | MB              | C05        | VDD        | 3.3V   | F20        | GND       | GND   | L25        | RESERVED   |             |  |

| 8             | A08          | A2                     | MB              | C06        | B_YCLK     | CH B   | F21        | GND       | GND   | L26        | A_TXDATA   | CH A        |  |

| 9             | A09          | A1                     | MB              | C07        | B_XCLK     | CH B   | F22        | RESERVED  |       | M01        | D12        | MB          |  |

| 10            | A10          | Α0                     | MB              | C08        | B_DSPRST   | TEST   | F24        | DP_TEST#  | TEST  | M02        | D11        | MB          |  |

| 11            | A11          | D7                     | MB              | C09        | B_PLLGND   | СНВ    | F25        | RESERVED  |       | M03        | D10        | MB          |  |

| 12            | A12          | D6                     | MB              | C10        | RESERVED   |        | F26        | A_EYESYNC | CH A  | M24        | VDD        | 3.3V        |  |

| 13            | A13          | D5                     | MB              | C11        | DPBS_TRST# | JTAG   | G01        | B_EYESYNC | CH B  | M25        | A_DPCS     | TEST        |  |

| 14            | A 14         | D0                     | MB              | C12        | VDD        | 3.3V   | G02        | RESERVED  |       | M26        | A_DSPRST   | TEST        |  |

| 15            | A15          | DP CLKIN               | SYS             | C13        | B_DPINT    | TEST   | G03        | B PLLVDD  | CH B  | N01        | D15        | MB          |  |

| 16            | A16          | RESERVED               |                 | C14        | RESERVED   |        | G05        | RESERVED  |       | N02        | D14        | MB          |  |

| 17            | A17          | A_DPINT                | TEST            | C15        | VDD        | 3.3V   | G06        | GND       | GND   | N03        | D13        | MB          |  |

| 18            | A18          | A_DSPINT               | TEST            | C16        | A_PLLVDD   | CH A   | G07        | GND       | GND   | N24        | WR#        | MB          |  |

| 19            | A19          | A_EYEXY                | CH A            | C17        | RESERVED   |        | G08        | GND       | GND   | N25        | A_PLLGND   | CH A        |  |

| 20            | A 20         | A_XCLK                 | CH A            | C18        | RESERVED   |        | G19        | GND       | GND   | N26        | DPBS_TCLK  | JTAG        |  |

| 21            | A 21         | A_YCLK                 | CH A            | C19        | RESERVED   |        | G20        | GND       | GND   | P01        | CAS#       | MB          |  |

| 22            | A 22         | RESERVED               | 01174           | C20        | RESERVED   |        | G21        | GND       | GND   | P02        | RAS#       | MB          |  |

| 23            | A 23         | A_TSAEN#               | CH A            | C21        | RESERVED   |        | G22        | RESERVED  | GIID  | P03        | MCU_CLKIN  | SYS         |  |

| 24            | A 24         | RESERVED               | OHA             | C22        | RESERVED   |        | G24        | RESERVED  |       | P24        | C_DSPINT   | TEST        |  |

| 25            | A 25         | RESERVED               | +               | C23        | A_DPTXD    | TEST   | G25        | RESERVED  |       | P25        | RD#        | MB          |  |

| 26            | A 26         | RESERVED               |                 | C24        | VDD VDD    | 3.3V   | G26        | A_SCLK    | CH A  | P26        | C_EYEXY    | CH C        |  |

| 27            | B 01         | B_TXDATA               | СН В            | C25        | RESERVED   | J. J V | H01        | B_EYECLK# | CH B  | R01        | PA5        | NA NA       |  |

| 28            | B02          | RESERVED               | OHB             | C26        | RESERVED   |        | H02        | RESERVED  | OIID  | R02        | RESERVED   | INA         |  |

| 29            | B 03         | RESERVED               |                 | D01        | RESERVED   |        | H03        | B_DSPINT  | TEST  | R03        | MCU_CLKOUT | MB          |  |

| 30            | B 04         | RESERVED               |                 | D02        | RESERVED   |        | H05        | RESERVED  | 1201  | R24        | C_DPTXCLK  | TEST        |  |

| 31            | B 04         | RESERVED               |                 | D02        | RESERVED   |        | H06        | GND       | GND   | R25        | C_YCLK     | CH C        |  |

| 32            | B 06         | RESERVED               |                 | D03        | VDD        | 3.3V   | H07        | GND       | GND   | R26        | C_XCLK     | CH C        |  |

| 33            | B 07         | C_DPEXRST              | TEST            | D24        | A 21       | MB     | H08        | GND       | GND   | T01        | PA3        | NA NA       |  |

| 34            |              |                        |                 |            |            | IVID   | H19        | GND       |       | T02        | PE4        |             |  |

| 35            | B 08<br>B 09 | A_DPEXRST<br>B_DPEXRST | TEST<br>TEST    | D26<br>E01 | RESERVED   | СПВ    | H19<br>H20 | GND       | GND   | T02        | VDD        | NA<br>3.3V  |  |

| 36            | B 10         | D4                     |                 |            | B_FSYNC    | CH B   |            | GND       | GND   | T24        | C DPINT    | TEST        |  |

|               |              |                        | MB              | E02        | RESERVED   |        | H21        |           | GND   | -          | <u> </u>   |             |  |

| 37            | B11          | D3                     | MB<br>MB        | E03        | RESERVED   |        | H22        | RESERVED  | 2 01/ | T25<br>T26 | VDD        | 3.3V        |  |

|               | B12          |                        |                 | E05        | RESERVED   |        | H24        | VDD       | 3.3V  |            | VDD        | 3.3V        |  |

| 39            | B13          | D1                     | MB              | E06        | RESERVED   |        | H25        | RESERVED  | 0     | U01        | PA7        | NA          |  |

| 40            | B14          | C_DPRXD                | TEST            | E07        | RESERVED   |        | H26        | A_FSYNC   | CH A  | U02        | PE0        | NA<br>2.207 |  |

| 41            | B15          | RESERVED               |                 | E08        | RESERVED   |        | J01        | RESERVED  | OUD   | U03        | VDD        | 3.3V        |  |

| 42            | B16          | RESERVED               |                 | E19        | RESERVED   |        | J02        | B_TSAEN#  | CH B  | U24        | VGG        | 5V          |  |

| 43            | B17          | RESERVED               | TF 67           | E20        | RESERVED   |        | J03        | VDD       | 3.3V  | U25        | C_TSAEN#   | CH C        |  |

| 44            | B18          | A_DPRXD                | TEST            | E21        | RESERVED   |        | J24        | RESERVED  |       | U26        | RESERVED   | 1           |  |

| 45            | B19          | RESERVED               |                 | E22        | RESERVED   |        | J25        | RESERVED  |       | V01        | PE6        | NA          |  |

| 46            | B 20         | RESERVED               |                 | E 24       | RESERVED   |        | J26        | RESERVED  |       | V02        | PE2        | NA          |  |

| 47            | B 21         | RESERVED               |                 | E 25       | RESERVED   |        | K01        | BS1       | MB    | V03        | RESERVED   | 1           |  |

| 48            | B 22         | B_DPRXD                | TEST            | E 26       | A_EYECLK#  | CH A   | K 02       | DPBS_TDO  | JTAG  | V24        | C_DPRXCLK  | TEST        |  |

| 49            | B 23         | B_DPTXD                | TEST            | F01        | B_SCLK     | CH B   | K 03       | VDD       | 3.3V  | V25        | C_DPTXD    | TEST        |  |

| 50            | B 24         | B DPTXCLK              | TEST            | F02        | RESERVED   | 1      | K24        | A_DPRXCLK | TEST  | V26        | C_PLLVDD   | CH C        |  |

Table 3-1. RL56CSMV/3 Pin Signals by Pin Location (Cont'd)

| Table<br>Col. |              | 5          |          | 6              |                 |          | 7            |            |          | 8                                               |        |     |

|---------------|--------------|------------|----------|----------------|-----------------|----------|--------------|------------|----------|-------------------------------------------------|--------|-----|

| Table<br>Row  | Loc.         | Signal     | I/F      | Loc.           | Signal          | I/F      | Loc.         | Signal     | I/F      | Loc.                                            | Signal | I/F |

| 1             | W01          | PA4        | NA       | AB20           | RESERVED        |          | AE13         | HBA1       | HB       |                                                 |        |     |

| 2             | W02          | PA6        | NA       | AB21           | RESERVED        |          | AE 14        | HBCS#      | HB       |                                                 |        |     |

| 3             | W03          | VDD        | 3.3V     | AB22           | RESERVED        |          | AE15         | HBWR#      | НВ       |                                                 |        |     |

| 4             | W05          | GND        | GND      | AB24           | RESERVED        |          | AE16         | HBCLK      | НВ       |                                                 |        |     |

| 5             | W06          | GND        | GND      | AB25           | C_FSYNC         | CH C     | AE17         | HBEN#      | НВ       |                                                 |        |     |

| 6             | W07          | GND        | GND      | AB26           | CS3             | MB       | AE18         | A5         | MB       |                                                 |        |     |

| 7             | W08          | GND        | GND      | AC01           | TRST#           | JTAG     | AE19         | A7         | MB       |                                                 |        |     |

| 8             | W19          | GND        | GND      | AC02           | PF3             | NA       | AE20         | A9         | MB       |                                                 |        |     |

| 9             | W20          | GND        | GND      | AC03           | VDD             | 3.3V     | AE21         | A13        | MB       |                                                 |        |     |

| 10            | W21          | GND        | GND      | AC24           | CS0             | MB       | AE22         | VDD        | 3.3V     |                                                 |        |     |

| 11            | W22          | RESERVED   |          | AC25           | C_TXDATA        | CH C     | AE23         | RESERVED   |          |                                                 |        |     |

| 12            | W 24         | MCU_RESET# | SYS      | AC26           | C_SCLK          | CH C     | AE 24        | A14        | MB       |                                                 |        |     |

| 13            | W25          | ROME       | SYS      | AD01           | PF7             | NA       | AE 25        | A22        | MB       |                                                 |        |     |

| 14            | W26          | BS0        | MB       | AD02           | TMS             | JTAG     | AE26         | A24        | MB       |                                                 |        |     |

| 15            | Y 01         | PE1        | NA       | AD03           | VDD             | 3.3V     | AF01         | PF4        | NA       |                                                 |        |     |

| 16            | Y 02         | PE3        | NA       | AD04           | VDD             | 3.3V     | AF02         | PF6        | NA       |                                                 |        |     |

| 17            | Y 03         | VDD        | 3.3V     | AD 05          | VDD             | 3.3V     | AF03         | TDI        | JTAG     |                                                 |        |     |

| 18            | Y 05         | GND        | GND      | AD 06          | VDD             | 3.3V     | AF04         | HBACKR#    | НВ       |                                                 |        |     |

| 19            | Y 06         | GND        | GND      | AD07           | VDD             | 3.3V     | AF05         | HBACKW#    | НВ       |                                                 |        |     |

| 20            | Y 07         | GND        | GND      | AD08           | VDD             | 3.3V     | AF06         | HBD0       | НВ       |                                                 |        |     |

| 21            | Y 08         | GND        | GND      | AD 09          | VDD             | 3.3V     | AF07         | HBD2       | HB       |                                                 |        |     |

| 22            | Y19          | GND        | GND      | AD10           | VDD             | 3.3V     | AF08         | HBD3       | HB       |                                                 |        |     |

| 23            | Y 20         | GND        | GND      | AD11           | VDD             | 3.3V     | AF09         | HBD10      | HB       |                                                 |        |     |

| 24            | Y 21         | GND        | GND      | AD12           | HBD14           | HB       | AF10         | HBD8       | HB       |                                                 |        |     |

| 25            | Y 22         | RESERVED   | OND      | AD12           | HBA2            | HB       | AF11         | HBD5       | НВ       |                                                 |        |     |

| 26            | Y 24         | C_EYECLK#  | CH C     | AD13           | HBA5            | HB       | AF12         | HBD13      | HB       |                                                 |        |     |

| 27            | Y 25         | MCU_TEST#  | SYS      | AD15           | DPBS_TDI        | JTAG     | AF13         | HBD11      | НВ       |                                                 |        |     |

| 28            | Y 26         | CS4        | MB       | AD16           | C_PLLGND        | CH C     | AF14         | HBA3       | HB       |                                                 |        |     |

| 29            | AA01         | PE5        | NA NA    | AD17           | C_DSPRST        | TEST     | AF15         | HBA4       | НВ       |                                                 |        |     |

| 30            | AA02         | PE7        | NA NA    | AD17           | A12             | MB       | AF16         | HBRD#      | НВ       |                                                 |        |     |

| 31            | AA03         | VDD        | 3.3V     | AD19           | C_DPCS          | TEST     | AF17         | RESERVED   | 110      |                                                 |        |     |

| 32            | AA05         | GND        | GND      | AD19           | A11             | MB       | AF18         | HBIRQ#     | НВ       |                                                 |        |     |

| 33            | AA06         | GND        | GND      | AD20           | A16             | MB       | AF19         | A6         | MB       |                                                 |        |     |

| 34            | AA07         | GND        | GND      | AD21           | A15             | MB       | AF20         | DPBS_TMS   | JTAG     |                                                 |        |     |

| 35            | AA08         | GND        | GND      | AD23           | A20             | MB       | AF21         | A8         | MB       |                                                 |        |     |

| 36            | AA19         | GND        | GND      | AD23           | RW#             | MB       | AF22         | A10        | MB       |                                                 |        |     |

| 37            | AA19<br>AA20 | GND        | GND      | AD 24<br>AD 25 | C_RXDATA        | CH C     | AF23         | A10        |          |                                                 |        |     |

| 38            | AA20<br>AA21 | GND        | GND      | AD 26          | C_RXDATA<br>CS1 | MB       | AF23<br>AF24 | A17<br>A19 | MB<br>MB | l <del>  </del>                                 |        | -   |

| 39            | AA21<br>AA22 | RESERVED   | GND      | AE01           | PF5             | NA<br>NA | AF24<br>AF25 | A19<br>A18 | MB       | <del>   </del>                                  |        | -   |

|               |              | 1          | E\/      |                |                 |          | 4            |            |          | <del>   </del>                                  |        | -   |

| 40            | AA24         | VGG        | 5V       | AE02           | TDO             | JTAG     | AF26         | A23        | MB       |                                                 |        | -   |

| 41            | AA25         | C_EYESYNC  | CH C     | AE03           | TCK             | JTAG     | ╂            |            |          |                                                 |        | -   |

| 42            | AA26         | CS2        | MB       | AE04           | HBRQSTR         | HB       | ╂——          | 1          |          | <del>                                    </del> |        | -   |

| 43            | AB01         | PF0        | NA<br>NA | AE05           | HBRQSTW         | HB       | ╂——          | 1          |          | <del>                                    </del> |        | -   |

| 44            | AB02         | PF2        | NA<br>NA | AE06           | HBD1            | HB       | <b>∦</b> ——  |            |          |                                                 |        |     |

| 45            | AB03         | PF1        | NA OND   | AE07           | HBD9            | HB       | <b>I</b> ——  | -          |          |                                                 |        |     |

| 46            | AB05         | GND        | GND      | AE08           | HBD4            | HB       | <b>I</b> ——  | -          |          |                                                 |        |     |

| 47            | AB06         | GND        | GND      | AE09           | HBD6            | HB       | <b>↓</b>     | 1          |          |                                                 |        |     |

| 48            | AB07         | GND        | GND      | AE10           | HBD7            | HB       | <b>↓</b>     |            |          |                                                 |        |     |

| 49            | AB08         | GND        | GND      | AE11           | HBD12           | HB       | <b>↓</b>     |            |          |                                                 |        |     |

| 50            | AB19         | RESERVED   | 1        | AE12           | HBD15           | HB       | II           | Ì          |          |                                                 |        |     |

Table 3-2. RL56CSMV/3 Pin Signals by Interface