## Dual Single-Phase PWM Controller for CPU Core/GFX Power Supply

### **General Description**

The RT8167A is a dual single-phase synchronous Buck PWM controller with integrated gate drivers, compliant with Intel VR12/IMVP7 specification. A serial VID (SVID) interface is built-in in the RT8167A to communicate with Intel VR12/IMVP7 compliant CPU. The integrated differential remote output voltage sensing function and built-in high accuracy DAC achieve accurate output voltage regulation.

The RT8167A supports VR12/ IMVP7 compatible power management states and VID on-the-fly function. The RT8167A operates in two power management states including DEM in PS2 and Forced-CCM in PS1/PS0. Richtek's proprietary G-NAVP<sup>TM</sup> (Green Native AVP) makes AVP (Active Voltage Positioning) design easier and more robust. By utilizing the G-NAVP<sup>TM</sup> topology, DEM and CCM efficiency can be improved.

The RT8167A integrates high accuracy ADC for platform setting functions, such as no-load offset or over current level. Individual VR ready output signals are provided for both CORE VR and GFX VR. The IC also features complete fault protection functions, including over voltage, under voltage, negative voltage, over current and under voltage lockout. The RT8167A is available in a WQFN-48L 6x6 small foot print package.

### **Marking Information**

RT8167A GQW YMDNN RT8167AGQW : Product Number YMDNN : Date Code

### Features

- G-NAVP<sup>™</sup> (Green Native Active Voltage Positioning) Topology

- Dual Output Controller with Two Built-in Gate Drivers

- Serial VID Interface

- 0.5% DAC Accuracy

- Differential Remote Output Voltage Sensing

- Built-in ADC for Platform Programming

- Diode Emulation Mode (DEM) at Light Load Condition

- Droop Enable/Disable

- Fast Transient Response

- VR12/IMVP7 Compatible Power Management States

- VR Ready Indicator

- Thermal Throttling Indicator

- Current Monitor Output

- Switching Frequency up to 1MHz per Phase

- Protection : OVP, UVP, NVP, OCP, UVLO

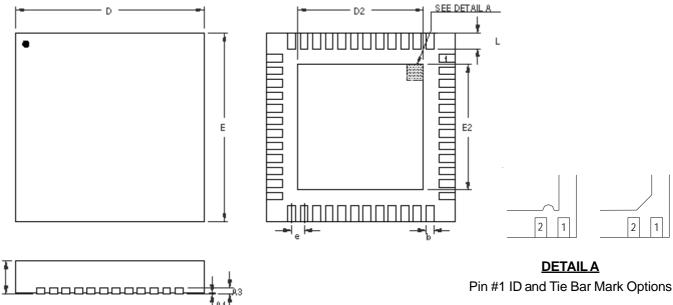

- Small 48-Lead WQFN Package

- RoHS Compliant and Halogen Free

### Applications

- VR12 / IMVP7 Intel CPU Core Supply

- AVP Step-down Converter

- Notebook/ Netbook/ Desktop Computer CPU Core Supply

## Ordering Information

Package Type QW : WQFN-48L 6x6 (W-Type)

Lead Plating System G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- ▶ RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

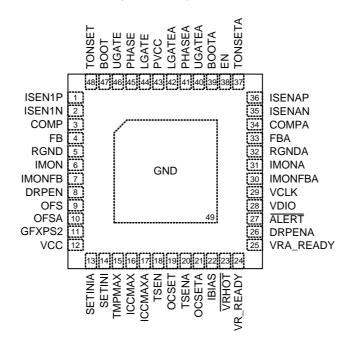

### **Pin Configurations**

(TOP VIEW)

WQFN-48L 6x6

### **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                                                                                                                                               |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

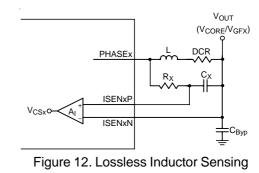

| 1       | ISEN1P   | Positive Current Sense Input of CORE VR                                                                                                                                                                                                                                                                    |

| 2       | ISEN1N   | Negative Current Sense Input of CORE VR                                                                                                                                                                                                                                                                    |

| 3       | COMP     | CORE VR Compensation. This pin is the output node of the error amplifier.                                                                                                                                                                                                                                  |

| 4       | FB       | CORE VR Feedback. This is the negative input node of the error amplifier.                                                                                                                                                                                                                                  |

| 5       | RGND     | Return Ground for CORE VR. This pin is the negative input for differential remote voltage sensing.                                                                                                                                                                                                         |

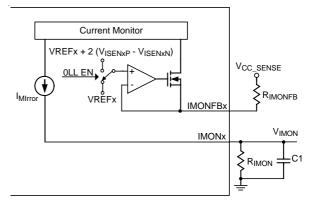

| 6       | IMON     | Current Monitor Output of CORE VR. The output voltage $V_{IMON}$ of this pin is proportional to the output current. For digital output current reporting, detailed $V_{IMON}$ is generated by built-in ADC.                                                                                                |

| 7       | IMONFB   | This pin is used to externally set the current monitor output gain of CORE VR. Connect this pin with one resistor $R_{IMONFB}$ to CORE VCC_SENSE while IMON pin is connected to ground with another resistor, $R_{IMON}$ . The current monitor output gain can be set by the ratio of these two resistors. |

| 8       | DRPEN    | Droop Enable Mode Setting of CORE VR. An internal $80\mu$ A current source is connected to the DRPEN pin and flows out of this pin for $10\mu$ s. Connect this pin to V <sub>CC</sub> to enable droop function. Connect this pin to GND to disable droop function.                                         |

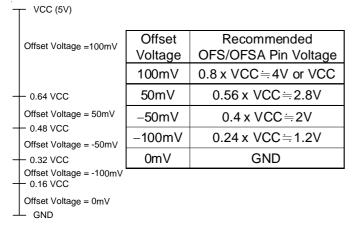

| 9       | OFS      | Output Voltage No-Load Offset Setting of CORE VR. Connect to a resistive voltage divider from V <sub>CC</sub> to GND to set the pin voltage V <sub>OFS</sub> for offset setting. Connect this pin to GND for no offset setting.                                                                            |

| 10      | OFSA     | Output Voltage No-Load Offset Setting of GFX VR. Connect to a resistive voltage divider from V <sub>CC</sub> to GND to set the pin voltage V <sub>OFSA</sub> for offset setting. Connect this pin to GND for no offset setting.                                                                            |

| Pin No. | Pin Name  | Pin Function                                                                                                                                                                                                                                                                                                            |

|---------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11      | GFXPS2    | Forced DEM Enable Setting of GFX VR. Connect to $V_{CC}$ for forced-DEM setting and connect to GND for following SVID power state command.                                                                                                                                                                              |

| 12      | VCC       | $5V$ Power Supply Input of Controller. Bypass this pin to GND with a $1\mu F$ or greater ceramic capacitor.                                                                                                                                                                                                             |

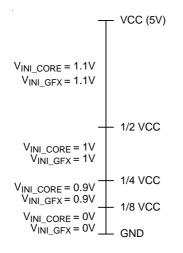

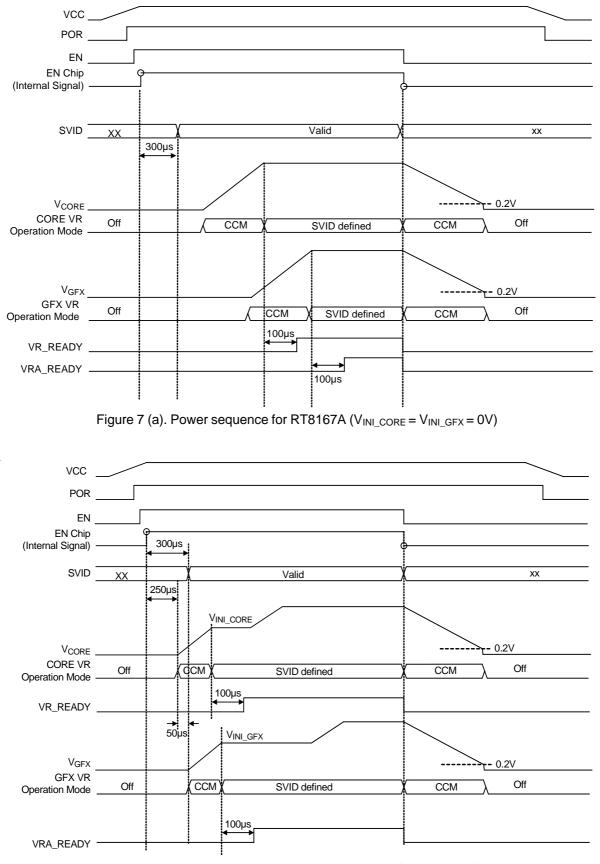

| 13      | SETINIA   | Initial Startup Voltage V <sub>INI_GFX</sub> Setting of GFX VR. Connect to a resistive voltage divider from V <sub>CC</sub> to GND to set the pin voltage V <sub>SETINIA</sub> for GFX VR initial startup voltage V <sub>INI_GFX</sub> setting. Connect this pin to GND for 0V V <sub>INI_GFX</sub> setting.            |

| 14      | SETINI    | Initial Startup Voltage V <sub>INI_CORE</sub> Setting of CORE VR. Connect to a resistive voltage divider from V <sub>CC</sub> to GND to set the pin voltage V <sub>SETINI</sub> for CORE VR initial startup voltage V <sub>INI_CORE</sub> setting. Connect this pin to GND for 0V V <sub>INI_CORE</sub> setting.        |

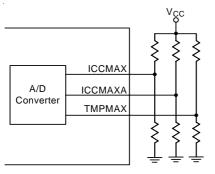

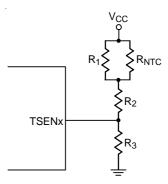

| 15      | ТМРМАХ    | Maximum Temperature Setting of CORE VR. Connect to a resistive voltage divider from V <sub>CC</sub> to GND to set the pin voltage V <sub>TMPMAX</sub> for TMPMAX setting.                                                                                                                                               |

| 16      | ICCMAX    | Maximum Current Setting of CORE VR. Connect to a resistive voltage divider from V <sub>CC</sub> to GND to set the pin voltage V <sub>ICCMAX</sub> for ICCMAX setting.                                                                                                                                                   |

| 17      | ICCMAXA   | Maximum Current Setting of GFX VR. Connect to a resistive voltage divider from $V_{CC}$ to GND to set the pin voltage $V_{ICCMAXA}$ for ICCMAXA setting.                                                                                                                                                                |

| 18      | TSEN      | Thermal Monitor Sense Pin of CORE VR.                                                                                                                                                                                                                                                                                   |

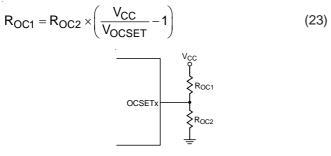

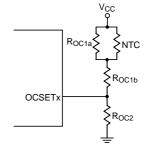

| 19      | OCSET     | Over Current Protection Setting of CORE VR. Connect to a resistive voltage divider from $V_{CC}$ to GND to set the pin voltage $V_{OCSET}$ from 0 to 3.3V for CORE VR over current protection threshold.                                                                                                                |

| 20      | TSENA     | Thermal Monitor Sense Pin of GFX VR.                                                                                                                                                                                                                                                                                    |

| 21      | OCSETA    | Over Current Protection Setting of GFX VR. Connect to a resistive voltage divider from $V_{CC}$ to GND to adjust the pin voltage $V_{OCSETA}$ from 0 to 3.3V for GFX VR over current protection threshold.                                                                                                              |

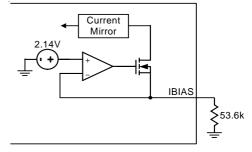

| 22      | IBIAS     | Internal bias current setting. Connect a 53.6k $\Omega$ resistor from IBIAS pin to GND.                                                                                                                                                                                                                                 |

| 23      | VRHOT     | Thermal Monitor Output (Active Low). Connect a pull high resistor from VRHOT pin to 1.05V.                                                                                                                                                                                                                              |

| 24      | VR_READY  | Voltage Ready Indicator of CORE VR. Connect a pull high resistor from VR_READY pin to 1.05V.                                                                                                                                                                                                                            |

| 25      | VRA_READY | Voltage Ready Indicator GFX VR. Connect a pull high resistor from VRA_READY pin to 1.05V.                                                                                                                                                                                                                               |

| 26      | DRPENA    | Droop Enable Mode Setting of GFX VR. An internal $80\mu$ A current source is connected to DRPENA pin and flows out of this pin for $10\mu$ s. Connect this pin to V <sub>CC</sub> to enable droop function. Connect this pin to GND to disable droop function.                                                          |

| 27      | ALERT     | SVID Alert Pin (Active Low). Connect a 75 $\Omega$ resistor from ALERT pin to 1.05V.                                                                                                                                                                                                                                    |

| 28      | VDIO      | Controller and CPU Data Transmission Interface. Connecting a $64.9\Omega$ resistor between VDIO pin to 1.05V.                                                                                                                                                                                                           |

| 29      | VCLK      | Synchronous Clock from the CPU. Connect a $64.9\Omega$ resistor from VCLK pin to 1.05V.                                                                                                                                                                                                                                 |

| 30      | IMONFBA   | This pin is used to externally set the current monitor output gain of GFX VR. Connect this pin with one resistor R <sub>IMONFBA</sub> to GFX VCC_SENSE while IMON pin is connected to ground with another resistor R <sub>IMONA</sub> . The current monitor output gain can be set by the ratio of these two resistors. |

| 31      | IMONA     | Current Monitor Output of GFX VR. The output voltage VIMONA of this pin is proportional to the output current. For digital output current reporting, detailed VIMONA is generated by built-in ADC.                                                                                                                      |

| Pin No.          | Pin Name | Pin Function                                                                                                                                                                                                                                                     |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 32               | RGNDA    | Return Ground for GFX VR. This pin is the negative input for differential remote voltage sensing.                                                                                                                                                                |

| 33               | FBA      | GFX VR Feedback. This is the negative input node of the error amplifier.                                                                                                                                                                                         |

| 34               | COMPA    | GFX VR Compensation. This pin is the output node of the error amplifier.                                                                                                                                                                                         |

| 35               | ISENAN   | Negative Current Sense Input of GFX VR.                                                                                                                                                                                                                          |

| 36               | ISENAP   | Positive Current Sense Input of GFX VR.                                                                                                                                                                                                                          |

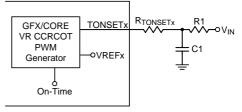

| 37               | TONSETA  | On-Time Setting of GFX VR. Connect this pin to VIN with one resistor.                                                                                                                                                                                            |

| 38               | EN       | Chip Enable (Active High).                                                                                                                                                                                                                                       |

| 39               | ΒΟΟΤΑ    | Bootstrap Flying Capacitor Connection for GFX VR. This pin powers the high side MOSFET drivers. Connect this pin to PHASEA with an external ceramic capacitor.                                                                                                   |

| 40               | UGATEA   | High Side MOSFET Floating Gate Driver Output for GFX VR. Connect this pin to the gate of high side MOSFET.                                                                                                                                                       |

| 41               | PHASEA   | Switching Node Connection for GFX VR. PHASEA is also the zero cross detect input for GFX VR. Connect this pin to the high side MOSFET sources together with the low side MOSFET drains and the inductor.                                                         |

| 42               | LGATEA   | Synchronous-Rectifier Gate Driver Output of GFX VR. Connect this pin to the gate of low side MOSFET.                                                                                                                                                             |

| 43               | PVCC     | 5V Power Supply of Driver. Bypass this pin to GND with a $1\mu F$ or greater ceramic capacitor.                                                                                                                                                                  |

| 44               | LGATE    | Synchronous-Rectifier Gate Driver Output of CORE VR. Connect this pin to the gate of low side MOSFET.                                                                                                                                                            |

| 45               | PHASE    | Switching Node Connection for CORE VR. PHASE is the internal lower supply rail for the UGATE. PHASE is also the zero cross detect input for CORE VR. Connect this pin to the high side MOSFET sources together with the low side MOSFET drains and the inductor. |

| 46               | UGATE    | High Side MOSFET Floating Gate Driver Output for CORE VR. Connect this pin to the gate of high side MOSFET.                                                                                                                                                      |

| 47               | BOOT     | Bootstrap Flying Capacitor Connection for CORE VR. This pin powers the high side MOSFET drivers. Connect this pin to PHASE with an external ceramic capacitor.                                                                                                   |

| 48               | TONSET   | On-Time Setting of CORE VR. Connect this pin to VIN with one resistor.                                                                                                                                                                                           |

| 49 (Exposed pad) | GND      | Ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum power dissipation.                                                                                                                                                      |

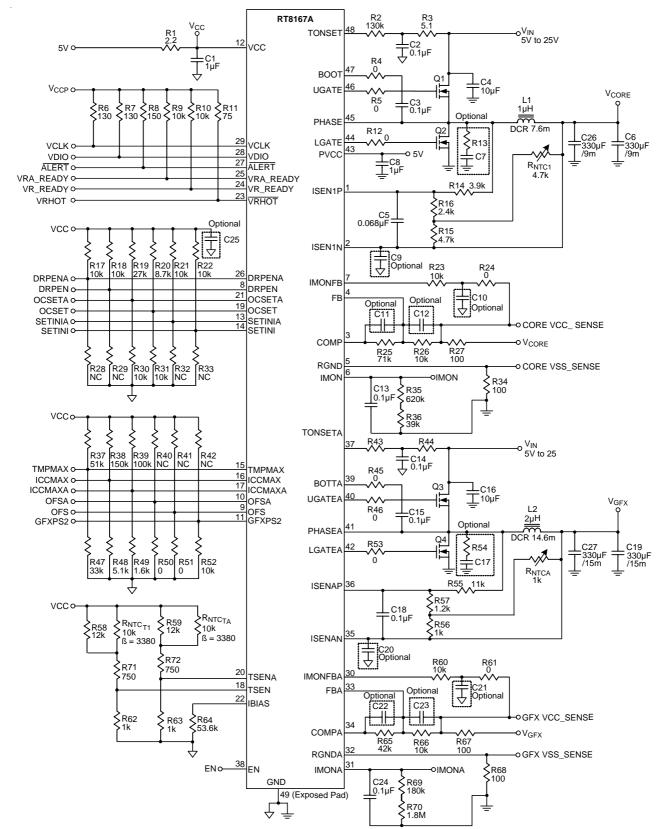

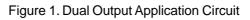

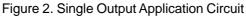

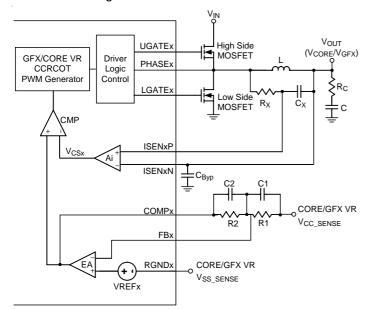

### **Typical Application Circuit**

### RICHTEK

| Copyright ©2012 Richtek Technology Corporation. All rights reserved. | <b>RICHTEK</b> is a registered trademark of Richtek Technology Corporation. |      |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------|------|

| www.richtek.com                                                      | DS8167A-00 January 2                                                        | 2012 |

| 6                                                                    |                                                                             |      |

### **Function Block Diagram**

| VID7         VID6         VID5         VID4         VID3         VID2         VID1         VID0         H1         H0         VDAC Voltage           0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                 | r    | Table 1. IMVP//VR12 Compliant VID Table |      |      |      |      |      |      |    |    |              |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------|------|------|------|------|------|------|----|----|--------------|--|--|

| 0         0         0         0         0         1         0         1         0.250           0         0         0         0         0         0         1         1         0         2         0.255           0         0         0         0         0         0         1         1         0         3         0.260           0         0         0         0         1         0         1         0         3         0.260           0         0         0         0         1         0         1         0         3         0.260           0         0         0         0         1         1         0         7         0.280           0         0         0         0         1         1         0         7         0.280           0         0         0         1         0         1         0         1         0         7         0.280           0         0         0         1         0         1         0         1         0         1         0         1         0         0         0.300           0                                                                                                                                                                                  | VID7 | VID6                                    | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | H1 | HO | VDAC Voltage |  |  |

| 0         0         0         0         1         0         0         2         0.255           0         0         0         0         0         0         1         1         0         3         0.260           0         0         0         0         0         1         0         1         0         3         0.260           0         0         0         0         0         1         0         0         4         0.285           0         0         0         0         1         1         0         0         6         0.275           0         0         0         0         1         1         0         0         6         0.275           0         0         0         1         0         0         0         0.280           0         0         0         1         0         0         0         0         0         0.285           0         0         0         1         1         1         1         0         0         0         0         0         0         0.285           0         0         0                                                                                                                                                                                  | 0    | 0                                       | 0    | 0    | 0    | 0    | 0    | 0    | 0  | 0  | 0.000        |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0    | 0                                       | 0    | 0    | 0    | 0    | 0    | 1    | 0  | 1  | 0.250        |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0    | 0                                       | 0    | 0    | 0    | 0    | 1    | 0    | 0  | 2  | 0.255        |  |  |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0    | 0                                       | 0    | 0    | 0    | 0    | 1    | 1    | 0  | 3  | 0.260        |  |  |

| 0         0         0         0         1         1         0         0         6         0.275           0         0         0         0         0         0         1         1         1         0         7         0.280           0         0         0         0         1         0         0         0         0         8         0.285           0         0         0         0         1         0         0         1         0         9         0.290           0         0         0         0         1         0         1         0         9         0.295           0         0         0         0         1         1         0         0         0         A         0.295           0         0         0         0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>0</td> <td>4</td> <td>0.265</td>                               | 0    | 0                                       | 0    | 0    | 0    | 1    | 0    | 0    | 0  | 4  | 0.265        |  |  |

| 0         0         0         0         1         1         1         0         7         0.280           0         0         0         0         1         0         0         0         0         8         0.285           0         0         0         0         1         0         0         1         0         9         0.290           0         0         0         0         1         0         1         0         9         0.290           0         0         0         0         1         0         1         0         0         0         A         0.295           0         0         0         0         1         1         0         0         0         A         0.295           0         0         0         0         1         1         0         0         0         0         0         0         0         0         0         0         0         1         1         0         0         0         1         1         1         1         0         0         0         0         0         0         0         0         1 <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>1</td> <td>0</td> <td>5</td> <td>0.270</td>                               | 0    | 0                                       | 0    | 0    | 0    | 1    | 0    | 1    | 0  | 5  | 0.270        |  |  |

| 0         0         0         0         0         0         0         0         8         0.285           0         0         0         0         1         0         0         1         0         9         0.290           0         0         0         0         1         0         1         0         1         0         0         A         0.295           0         0         0         0         0         1         0         1         1         0         0         A         0.295           0         0         0         0         0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0                                                                                                                                                    | 0    | 0                                       | 0    | 0    | 0    | 1    | 1    | 0    | 0  | 6  | 0.275        |  |  |

| 0         0         0         1         0         1         0         1         0         1         0         1         0         0         A         0.295           0         0         0         0         0         1         0         1         0         0         A         0.295           0         0         0         0         0         1         1         0         0         A         0.295           0         0         0         0         1         1         0         1         0         B         0.300           0         0         0         0         1         1         1         0         0         0         0.305           0         0         0         1         1         1         1         0         0         0.305           0         0         0         1         1         1         1         0         0         0.3225           0         0         0         1         0         0         1         1         0         0.3335           0         0         0         1         0         0                                                                                                                                                                            | 0    | 0                                       | 0    | 0    | 0    | 1    | 1    | 1    | 0  | 7  | 0.280        |  |  |

| 0         0         0         0         1         0         1         0         A         0.295           0         0         0         0         1         0         1         1         0         B         0.300           0         0         0         0         1         1         0         0         0         C         0.305           0         0         0         0         1         1         0         1         0         D         0.310           0         0         0         0         1         1         1         0         0         C         0.305           0         0         0         0         1         1         1         0         D         0.315           0         0         0         1         1         1         0         0.320           0         0         1         0         0         0         1         1         1         1         0.3325           0         0         1         0         0         1         1         1         1         1         1         0.3355           0                                                                                                                                                                                | 0    | 0                                       | 0    | 0    | 1    | 0    | 0    | 0    | 0  | 8  | 0.285        |  |  |

| 0         0         0         0         1         1         0         B         0.300           0         0         0         0         1         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>0</td> <td>1</td> <td>0</td> <td>9</td> <td>0.290</td> | 0    | 0                                       | 0    | 0    | 1    | 0    | 0    | 1    | 0  | 9  | 0.290        |  |  |

| 0         0         0         0         1         1         0         0         0         C         0.305           0         0         0         0         1         1         0         1         0         D         0.310           0         0         0         0         1         1         1         0         0         E         0.310           0         0         0         0         1         1         1         0         0         E         0.315           0         0         0         0         1         1         1         1         0         F         0.320           0         0         1         0         0         0         1         1         0         0.335           0         0         1         0         0         1         1         1         0.335           0         0         1         0         0         1         1         1         1         0.335           0         0         1         0         1         1         0         1         1         1         1         1         1                                                                                                                                                                              | 0    | 0                                       | 0    | 0    | 1    | 0    | 1    | 0    | 0  | А  | 0.295        |  |  |

| 0         0         0         0         1         1         0         1         0         D         0.310           0         0         0         0         1         1         1         0         0         E         0.315           0         0         0         0         1         1         1         1         0         0         E         0.315           0         0         0         0         1         1         1         1         0         F         0.320           0         0         0         1         0         0         0         1         1         0         0.325           0         0         1         0         0         0         1         1         1         0.330           0         0         1         0         0         1         1         1         1         1         0.330           0         0         1         0         0         1         1         1         1         1         1         0.330           0         0         1         0         1         0         1         1                                                                                                                                                                              | 0    | 0                                       | 0    | 0    | 1    | 0    | 1    | 1    | 0  | В  | 0.300        |  |  |

| 0         0         0         1         1         1         0         0         E         0.315           0         0         0         0         1         1         1         1         0         F         0.320           0         0         0         1         0         0         0         1         0         0.325           0         0         0         1         0         0         0         1         1         0         0.325           0         0         0         1         0         0         1         1         1         0.330           0         0         0         1         0         0         1         1         1         0.335           0         0         0         1         0         1         1         1         1         0.335           0         0         0         1         0         1         1         1         1         0.345           0         0         1         1         0         1         1         1         1         1         0.355           0         0         0                                                                                                                                                                                  | 0    | 0                                       | 0    | 0    | 1    | 1    | 0    | 0    | 0  | С  | 0.305        |  |  |

| 0         0         0         1         1         1         1         0         F         0.320           0         0         0         1         0         0         0         0         1         0         0.325           0         0         0         1         0         0         0         0         1         1         1         1         0.325           0         0         0         1         0         0         0         1         1         1         0         0.335           0         0         0         1         0         0         1         1         1         1         0.330           0         0         0         1         0         1         0         1         1         1         1         0.335           0         0         1         0         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>1</td> <td>0</td> <td>1</td> <td>0</td> <td>D</td> <td>0.310</td>                               | 0    | 0                                       | 0    | 0    | 1    | 1    | 0    | 1    | 0  | D  | 0.310        |  |  |

| 0         0         0         1         0         0         0         0         1         0         0.325           0         0         0         1         0         0         0         1         1         1         0.330           0         0         0         1         0         0         1         0         1         1         1         0.330           0         0         0         1         0         0         1         0         1         2         0.335           0         0         0         1         0         1         0         1         1         1         2         0.335           0         0         1         0         1         1         1         1         1         1         3         0.340           0         0         1         0         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1 <td>0</td> <td>0</td> <td>0</td> <td>0</td> <td>1</td> <td>1</td> <td>1</td> <td>0</td> <td>0</td> <td>E</td> <td>0.315</td>                               | 0    | 0                                       | 0    | 0    | 1    | 1    | 1    | 0    | 0  | E  | 0.315        |  |  |

| 0         0         0         1         0         0         0         1         1         1         0.330           0         0         0         1         0         0         1         0         1         2         0.335           0         0         0         1         0         1         1         1         2         0.335           0         0         0         1         0         1         1         1         2         0.335           0         0         0         1         0         1         1         1         3         0.340           0         0         0         1         0         1         1         1         3         0.340           0         0         0         1         0         1         0         1         1         1         1         1         1         3         0.345           0         0         1         1         0         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1         1                                                                                                                                                                          | 0    | 0                                       | 0    | 0    | 1    | 1    | 1    | 1    | 0  | F  | 0.320        |  |  |

| 0         0         1         0         1         0         1         2         0.335           0         0         0         1         0         0         1         1         3         0.340           0         0         0         1         0         1         0         1         1         3         0.340           0         0         0         1         0         1         0         1         1         3         0.340           0         0         0         1         0         1         0         1         4         0.345           0         0         0         1         0         1         1         5         0.350           0         0         0         1         0         1         1         1         7         0.360           0         0         1         1         0         1         1         1         1         1         1         1         1         1         3         0.365           0         0         1         1         0         1         1         1         1         1         1                                                                                                                                                                              | 0    | 0                                       | 0    | 1    | 0    | 0    | 0    | 0    | 1  | 0  | 0.325        |  |  |

| 0         0         0         1         0         0         1         1         1         3         0.340           0         0         0         1         0         1         0         0         1         4         0.345           0         0         0         1         0         1         0         1         4         0.345           0         0         0         1         0         1         0         1         4         0.345           0         0         0         1         0         1         0         1         5         0.350           0         0         0         1         0         1         1         7         0.360           0         0         0         1         1         0         1         1         7         0.360           0         0         1         1         0         0         1         8         0.365           0         0         0         1         1         0         1         1         9         0.370           0         0         0         1         1         0                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 0    | 0    | 0    | 1    | 1  | 1  | 0.330        |  |  |

| 0         0         0         1         0         1         0         1         4         0.345           0         0         0         1         0         1         0         1         1         5         0.350           0         0         0         1         0         1         1         1         5         0.350           0         0         0         1         0         1         1         0         1         6         0.355           0         0         0         1         0         1         1         7         0.360           0         0         0         1         1         0         0         1         8         0.365           0         0         0         1         1         0         0         1         8         0.365           0         0         0         1         1         0         1         1         9         0.370           0         0         0         1         1         0         1         1         8         0.375           0         0         0         1         1                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 0    | 0    | 1    | 0    | 1  | 2  | 0.335        |  |  |

| 0         0         0         1         0         1         0         1         1         5         0.350           0         0         0         1         0         1         1         0         1         6         0.355           0         0         0         1         0         1         1         1         1         6         0.355           0         0         0         1         1         1         1         1         7         0.360           0         0         0         1         1         0         0         1         8         0.365           0         0         0         1         1         0         0         1         8         0.365           0         0         0         1         1         0         1         1         9         0.370           0         0         0         1         1         0         1         1         8         0.380           0         0         0         1         1         1         1         1         1         1         1         0         0.385                                                                                                                                                                                    | 0    | 0                                       | 0    | 1    | 0    | 0    | 1    | 1    | 1  | 3  | 0.340        |  |  |

| 0         0         0         1         0         1         1         0         1         6         0.355           0         0         0         1         0         1         1         1         1         7         0.360           0         0         0         1         1         0         0         0         1         7         0.360           0         0         0         1         1         0         0         0         1         7         0.360           0         0         0         1         1         0         0         1         1         9         0.365           0         0         0         1         1         0         1         1         9         0.370           0         0         0         1         1         0         1         1         A         0.375           0         0         0         1         1         0         1         1         B         0.380           0         0         1         1         1         1         1         D         0.395           0         0                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 0    | 1    | 0    | 0    | 1  | 4  | 0.345        |  |  |

| 0         0         1         0         1         1         1         1         7         0.360           0         0         0         1         1         0         0         0         1         8         0.365           0         0         0         1         1         0         0         1         1         9         0.370           0         0         0         1         1         0         0         1         1         9         0.370           0         0         0         1         1         0         1         0         1         1         9         0.370           0         0         0         1         1         0         1         0         1         A         0.375           0         0         0         1         1         0         1         1         B         0.380           0         0         1         1         1         0         1         C         0.395           0         0         1         1         1         1         1         1         D         0.395           0                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 0    | 1    | 0    | 1    | 1  | 5  | 0.350        |  |  |

| 0         0         0         1         1         0         0         0         1         8         0.365           0         0         0         1         1         0         0         1         1         9         0.370           0         0         0         1         1         0         1         0         1         1         9         0.370           0         0         0         1         1         0         1         0         1         A         0.375           0         0         0         1         1         0         1         1         A         0.375           0         0         0         1         1         0         1         1         B         0.380           0         0         0         1         1         1         0         1         C         0.385           0         0         0         1         1         1         1         D         0.390           0         0         0         1         1         1         1         1         E         0.395           0         0                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 0    | 1    | 1    | 0    | 1  | 6  | 0.355        |  |  |

| 0         0         0         1         1         0         0         1         1         9         0.370           0         0         0         1         1         0         1         0         1         1         9         0.370           0         0         0         1         1         0         1         0         1         A         0.375           0         0         0         1         1         0         1         1         A         0.375           0         0         0         1         1         0         1         1         B         0.380           0         0         0         1         1         0         1         B         0.380           0         0         0         1         1         1         0         1         C         0.385           0         0         0         1         1         1         1         1         D         0.395           0         0         0         1         1         1         1         1         F         0.400           0         0         0                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 0    | 1    | 1    | 1    | 1  | 7  | 0.360        |  |  |

| 0         0         0         1         1         0         1         0         1         A         0.375           0         0         0         1         1         0         1         1         B         0.380           0         0         0         1         1         0         1         1         B         0.380           0         0         0         1         1         1         0         1         C         0.385           0         0         0         1         1         1         0         1         D         0.390           0         0         0         1         1         1         0         1         E         0.395           0         0         0         1         1         1         1         E         0.395           0         0         0         1         1         1         1         F         0.400           0         0         1         1         1         1         1         F         0.405           0         0         1         0         0         0         0         1                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 1    | 0    | 0    | 0    | 1  | 8  | 0.365        |  |  |

| 0         0         0         1         1         0         1         1         1         B         0.380           0         0         0         1         1         1         0         0         1         C         0.380           0         0         0         1         1         1         0         0         1         C         0.385           0         0         0         1         1         1         0         1         D         0.390           0         0         0         1         1         1         0         1         E         0.395           0         0         0         1         1         1         1         E         0.395           0         0         0         1         1         1         1         F         0.400           0         0         1         0         0         0         2         0         0.405           0         0         1         0         0         0         1         2         1         0.410                                                                                                                                                                                                                                                | 0    | 0                                       | 0    | 1    | 1    | 0    | 0    | 1    | 1  | 9  | 0.370        |  |  |

| 0         0         0         1         1         1         0         0         1         C         0.385           0         0         0         1         1         1         0         1         1         D         0.385           0         0         0         1         1         1         0         1         1         D         0.390           0         0         0         1         1         1         0         1         E         0.395           0         0         0         1         1         1         1         E         0.395           0         0         0         1         1         1         1         E         0.395           0         0         0         1         1         1         1         F         0.400           0         0         1         0         0         0         0         2         0         0.405           0         0         1         0         0         0         1         2         1         0.410                                                                                                                                                                                                                                                | 0    | 0                                       | 0    | 1    | 1    | 0    | 1    | 0    | 1  | A  | 0.375        |  |  |

| 0         0         0         1         1         1         0         1         1         D         0.390           0         0         0         1         1         1         0         1         1         D         0.390           0         0         0         1         1         1         0         1         E         0.395           0         0         0         1         1         1         1         F         0.400           0         0         1         0         0         0         0         2         0         0.405           0         0         1         0         0         0         0         1         2         1         0.410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0    | 0                                       | 0    | 1    | 1    | 0    | 1    | 1    | 1  | В  | 0.380        |  |  |

| 0         0         0         1         1         1         0         1         E         0.395           0         0         0         1         1         1         1         1         F         0.400           0         0         1         0         0         0         2         0         0.405           0         0         1         0         0         0         1         2         1         0.410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0    | 0                                       | 0    | 1    | 1    | 1    | 0    | 0    | 1  | С  | 0.385        |  |  |

| 0         0         0         1         1         1         1         1         F         0.400           0         0         1         0         0         0         0         2         0         0.405           0         0         1         0         0         0         0         1         2         1         0.410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 1    | 1    | 0    | 1    | 1  | D  | 0.390        |  |  |

| 0         0         1         0         0         0         0         0         2         0         0.405           0         0         1         0         0         0         0         1         2         1         0.410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0    | 0                                       | 0    | 1    | 1    | 1    | 1    | 0    | 1  | E  | 0.395        |  |  |

| 0 0 1 0 0 0 0 1 2 1 0.410                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0    | 0                                       | 0    | 1    | 1    | 1    | 1    | 1    | 1  | F  | 0.400        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | 0                                       | 1    | 0    | 0    | 0    | 0    | 0    | 2  | 0  | 0.405        |  |  |

| 0 0 1 0 0 0 1 0 2 2 0.415                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0    | 0                                       | 1    | 0    | 0    | 0    | 0    | 1    | 2  | 1  | 0.410        |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0    | 0                                       | 1    | 0    | 0    | 0    | 1    | 0    | 2  | 2  | 0.415        |  |  |

#### Table 1. IMVP7/VR12 Compliant VID Table

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | H1 | H0 | DAC Voltage |

|------|------|------|------|------|------|------|------|----|----|-------------|

| 0    | 0    | 1    | 0    | 0    | 0    | 1    | 1    | 2  | 3  | 0.420       |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 0    | 2  | 4  | 0.425       |

| 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 2  | 5  | 0.430       |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 0    | 2  | 6  | 0.435       |

| 0    | 0    | 1    | 0    | 0    | 1    | 1    | 1    | 2  | 7  | 0.440       |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 0    | 2  | 8  | 0.445       |

| 0    | 0    | 1    | 0    | 1    | 0    | 0    | 1    | 2  | 9  | 0.450       |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 0    | 2  | А  | 0.455       |

| 0    | 0    | 1    | 0    | 1    | 0    | 1    | 1    | 2  | В  | 0.460       |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 0    | 2  | С  | 0.465       |

| 0    | 0    | 1    | 0    | 1    | 1    | 0    | 1    | 2  | D  | 0.470       |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 0    | 2  | E  | 0.475       |

| 0    | 0    | 1    | 0    | 1    | 1    | 1    | 1    | 2  | F  | 0.480       |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 0    | 3  | 0  | 0.485       |

| 0    | 0    | 1    | 1    | 0    | 0    | 0    | 1    | 3  | 1  | 0.490       |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 0    | 3  | 2  | 0.495       |

| 0    | 0    | 1    | 1    | 0    | 0    | 1    | 1    | 3  | 3  | 0.500       |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 0    | 3  | 4  | 0.505       |

| 0    | 0    | 1    | 1    | 0    | 1    | 0    | 1    | 3  | 5  | 0.510       |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 0    | 3  | 6  | 0.515       |

| 0    | 0    | 1    | 1    | 0    | 1    | 1    | 1    | 3  | 7  | 0.520       |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 3  | 8  | 0.525       |

| 0    | 0    | 1    | 1    | 1    | 0    | 0    | 1    | 3  | 9  | 0.530       |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 3  | А  | 0.535       |

| 0    | 0    | 1    | 1    | 1    | 0    | 1    | 1    | 3  | В  | 0.540       |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 3  | С  | 0.545       |

| 0    | 0    | 1    | 1    | 1    | 1    | 0    | 1    | 3  | D  | 0.550       |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 0    | 3  | E  | 0.555       |

| 0    | 0    | 1    | 1    | 1    | 1    | 1    | 1    | 3  | F  | 0.560       |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 0    | 4  | 0  | 0.565       |

| 0    | 1    | 0    | 0    | 0    | 0    | 0    | 1    | 4  | 1  | 0.570       |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 0    | 4  | 2  | 0.575       |

| 0    | 1    | 0    | 0    | 0    | 0    | 1    | 1    | 4  | 3  | 0.580       |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 0    | 4  | 4  | 0.585       |

| 0    | 1    | 0    | 0    | 0    | 1    | 0    | 1    | 4  | 5  | 0.590       |

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | H1 | H0 | DAC Voltage |

|------|------|------|------|------|------|------|------|----|----|-------------|

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 0    | 4  | 6  | 0.595       |

| 0    | 1    | 0    | 0    | 0    | 1    | 1    | 1    | 4  | 7  | 0.600       |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 0    | 4  | 8  | 0.605       |

| 0    | 1    | 0    | 0    | 1    | 0    | 0    | 1    | 4  | 9  | 0.610       |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 4  | А  | 0.615       |

| 0    | 1    | 0    | 0    | 1    | 0    | 1    | 1    | 4  | В  | 0.620       |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 4  | С  | 0.625       |

| 0    | 1    | 0    | 0    | 1    | 1    | 0    | 1    | 4  | D  | 0.630       |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 4  | E  | 0.635       |

| 0    | 1    | 0    | 0    | 1    | 1    | 1    | 1    | 4  | F  | 0.640       |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 0    | 5  | 0  | 0.645       |

| 0    | 1    | 0    | 1    | 0    | 0    | 0    | 1    | 5  | 1  | 0.650       |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 0    | 5  | 2  | 0.655       |

| 0    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | 5  | 3  | 0.660       |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 0    | 5  | 4  | 0.665       |

| 0    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | 5  | 5  | 0.670       |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 0    | 5  | 6  | 0.675       |

| 0    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | 5  | 7  | 0.680       |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 0    | 5  | 8  | 0.685       |

| 0    | 1    | 0    | 1    | 1    | 0    | 0    | 1    | 5  | 9  | 0.690       |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 0    | 5  | А  | 0.695       |

| 0    | 1    | 0    | 1    | 1    | 0    | 1    | 1    | 5  | В  | 0.700       |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 0    | 5  | С  | 0.705       |

| 0    | 1    | 0    | 1    | 1    | 1    | 0    | 1    | 5  | D  | 0.710       |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | 5  | Е  | 0.715       |

| 0    | 1    | 0    | 1    | 1    | 1    | 1    | 1    | 5  | F  | 0.720       |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 6  | 0  | 0.725       |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 1    | 6  | 1  | 0.730       |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 0    | 6  | 2  | 0.735       |

| 0    | 1    | 1    | 0    | 0    | 0    | 1    | 1    | 6  | 3  | 0.740       |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 0    | 6  | 4  | 0.745       |

| 0    | 1    | 1    | 0    | 0    | 1    | 0    | 1    | 6  | 5  | 0.750       |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 0    | 6  | 6  | 0.755       |

| 0    | 1    | 1    | 0    | 0    | 1    | 1    | 1    | 6  | 7  | 0.760       |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 0    | 6  | 8  | 0.765       |

| 0    | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 6  | 9  | 0.770       |

# RT8167A

| VID7 | VID6 | VID5 | VID4 | VID3 | VID2 | VID1 | VID0 | H1 | H0 | DAC Voltage |

|------|------|------|------|------|------|------|------|----|----|-------------|

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 6  | A  | 0.775       |

| 0    | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 6  | В  | 0.780       |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 0    | 6  | С  | 0.785       |

| 0    | 1    | 1    | 0    | 1    | 1    | 0    | 1    | 6  | D  | 0.790       |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 0    | 6  | E  | 0.795       |

| 0    | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 6  | F  | 0.800       |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    | 7  | 0  | 0.805       |

| 0    | 1    | 1    | 1    | 0    | 0    | 0    | 1    | 7  | 1  | 0.810       |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 0    | 7  | 2  | 0.815       |

| 0    | 1    | 1    | 1    | 0    | 0    | 1    | 1    | 7  | 3  | 0.820       |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 0    | 7  | 4  | 0.825       |

| 0    | 1    | 1    | 1    | 0    | 1    | 0    | 1    | 7  | 5  | 0.830       |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 0    | 7  | 6  | 0.835       |

| 0    | 1    | 1    | 1    | 0    | 1    | 1    | 1    | 7  | 7  | 0.840       |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 0    | 7  | 8  | 0.845       |

| 0    | 1    | 1    | 1    | 1    | 0    | 0    | 1    | 7  | 9  | 0.850       |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 0    | 7  | А  | 0.855       |

| 0    | 1    | 1    | 1    | 1    | 0    | 1    | 1    | 7  | В  | 0.860       |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 0    | 7  | С  | 0.865       |

| 0    | 1    | 1    | 1    | 1    | 1    | 0    | 1    | 7  | D  | 0.870       |

| 0    | 1    | 1    | 1    | 1    | 1    | 1    | 0    | 7  | Е  | 0.875       |