# 1

# **PRODUCT OVERVIEW**

### **SAM8 PRODUCT FAMILY**

Samsung's SAM8 family of 8-bit single-chip CMOS microcontrollers offers a fast and efficient CPU with a wide range of integrated peripherals, in various mask-programmable ROM sizes. Analog its major CPU features are:

- Efficient register-oriented architecture

- Selectable CPU clock sources

- Idle and Stop power-down mode release by interrupt

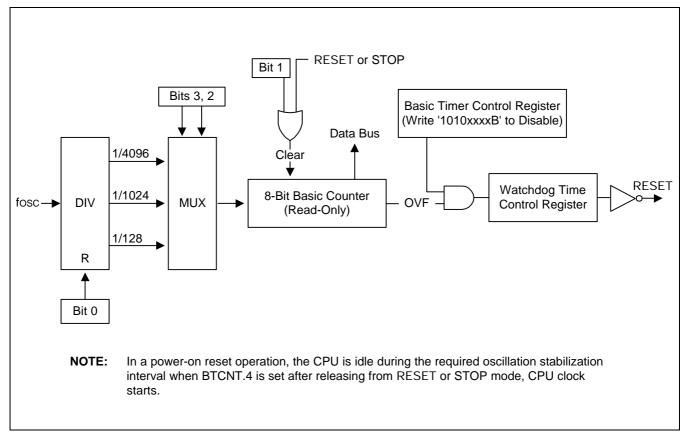

- Built-in basic timer with watchdog function

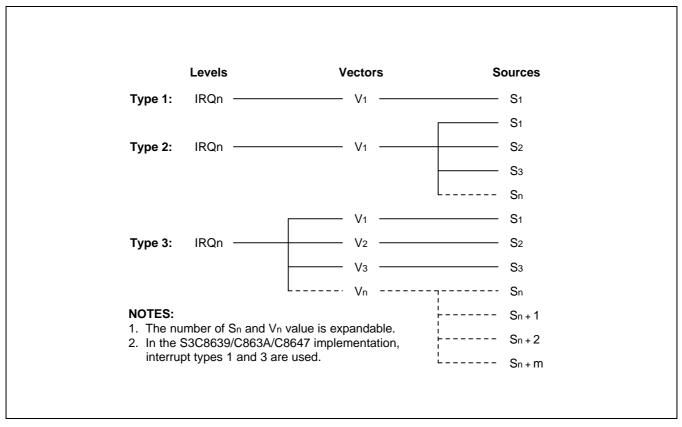

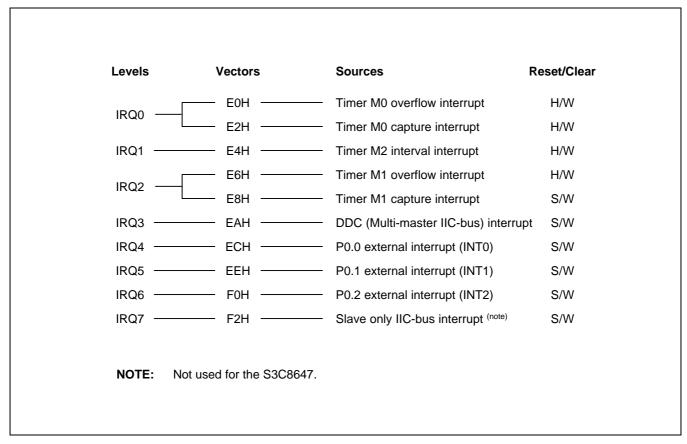

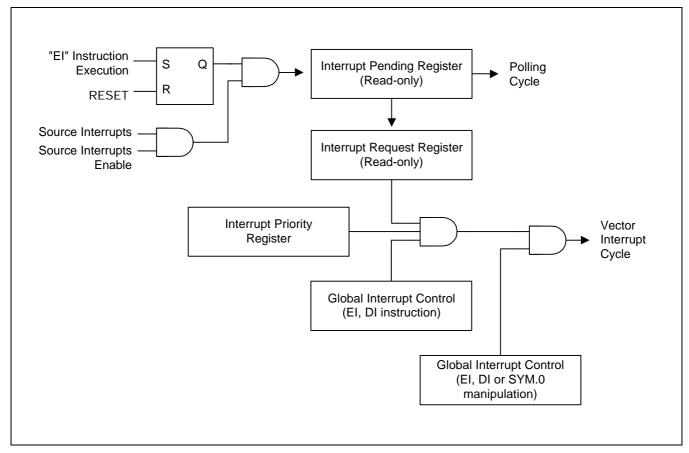

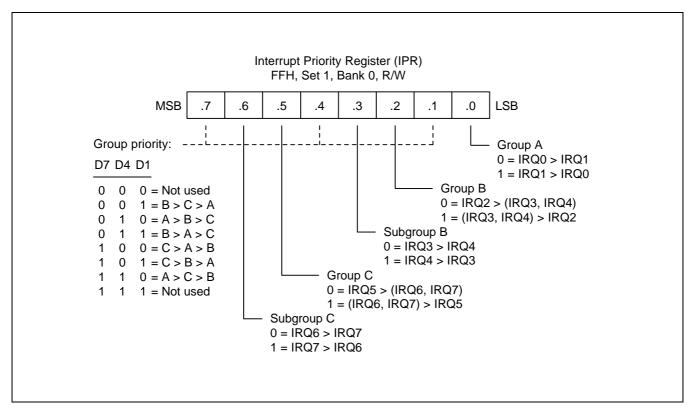

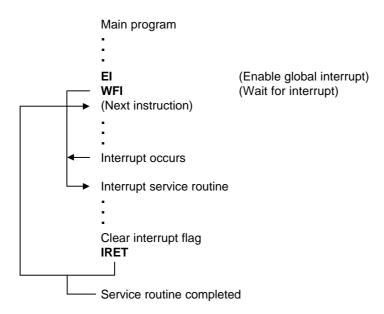

The sophisticated interrupt structure recognizes up to eight interrupt levels. Each level can have one or more interrupt sources and vectors. Fast interrupt processing (within a minimum of four CPU clocks) can be assigned to specific interrupt levels.

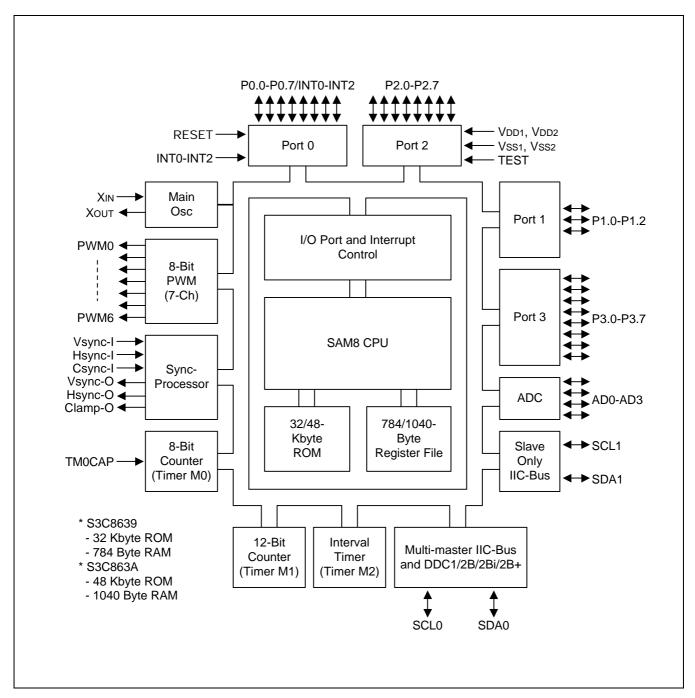

### S3C8639/C863A/P863A MICROCONTROLLERS

S3C8639/C863A/P863A single-chip 8-bit microcontrollers are based on the powerful SAM8 CPU architecture. The internal register file is logically expanded to increase the on-chip register space. S3C8639/C863A/P863A contain 32/48 Kbytes of on-chip program ROM.

In line with Samsung's modular design approach, the following peripherals are integrated with the SAM8 core:

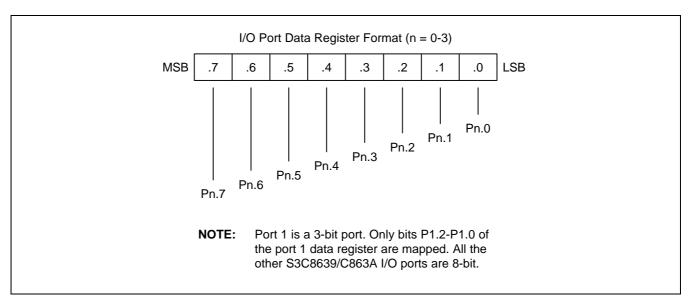

- Four programmable I/O ports (total 27 pins)

- One 8-bit basic timer for oscillation stabilization and watchdog functions

- One 8-bit general-purpose timer/counter with selectable clock sources

- One interval timer

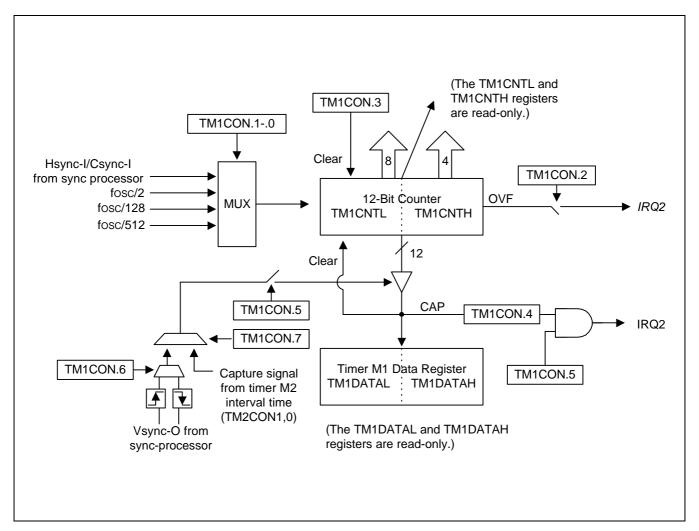

- One 12-bit counter with selectable clock sources, including Hsync or Csync input

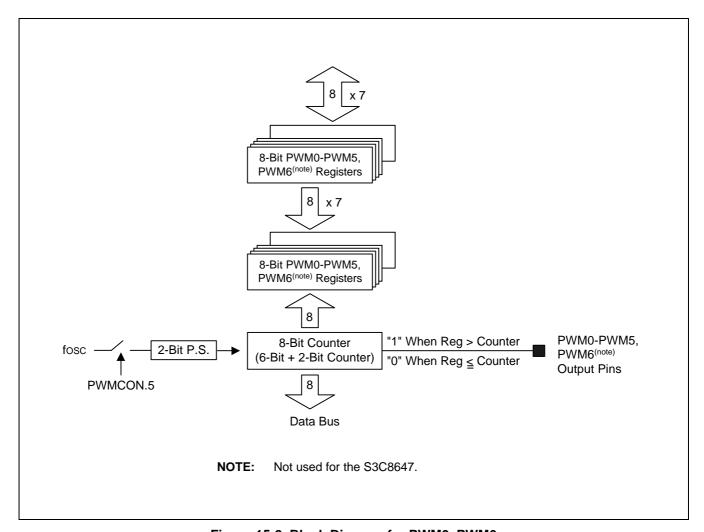

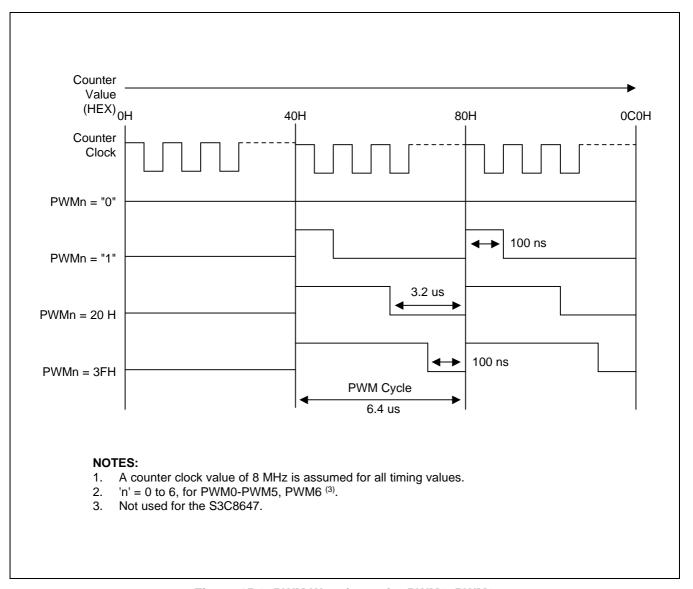

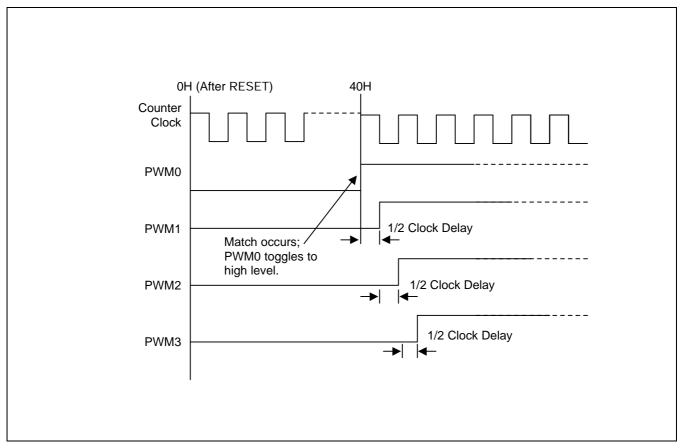

- PWM block with seven 8-bit PWM circuits

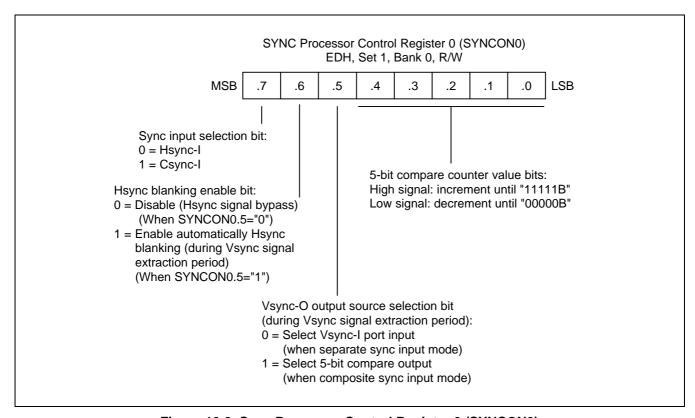

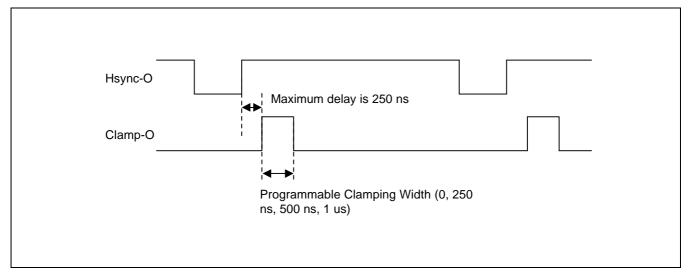

- Sync processor block (for Vsync and Hsync I/O, Csync input, and Clamp signal output)

- DDC Multi-master and slave-only IIC-Bus

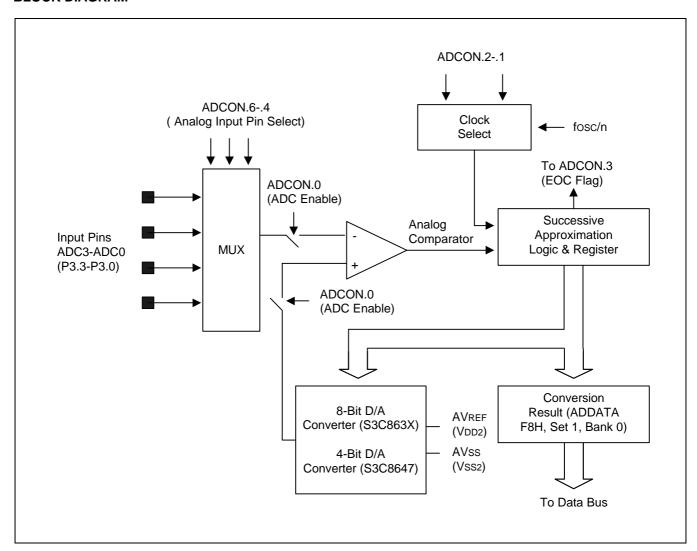

- 4-channel A/D converter (8-bit resolution)

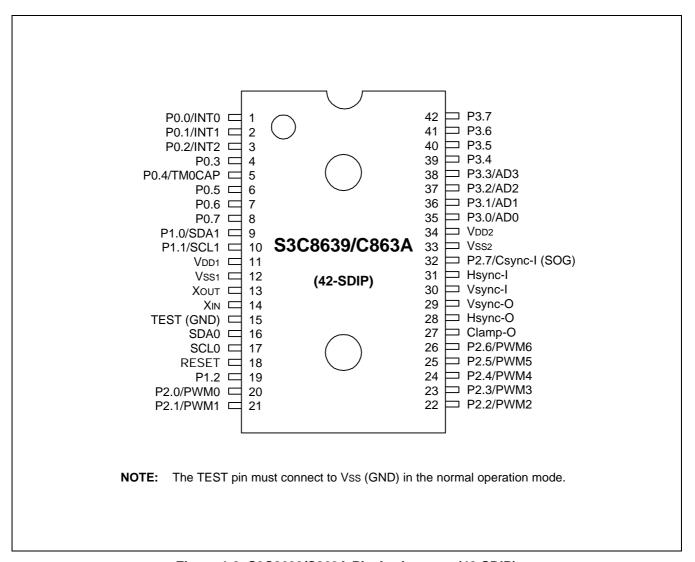

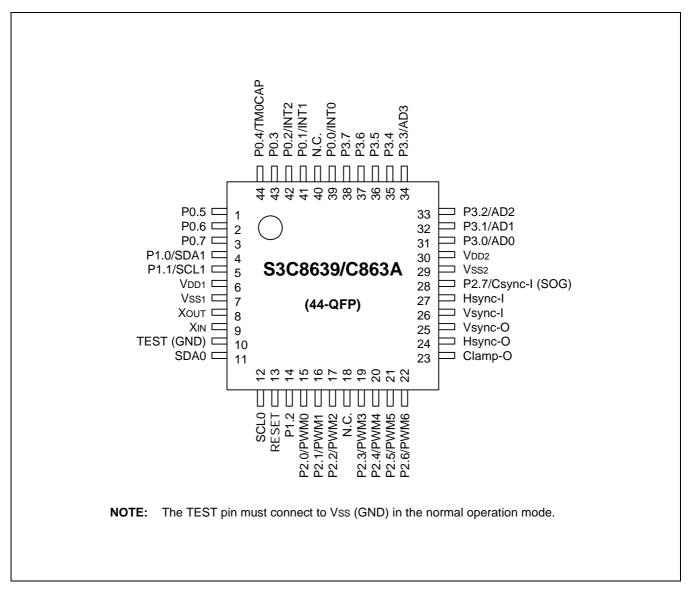

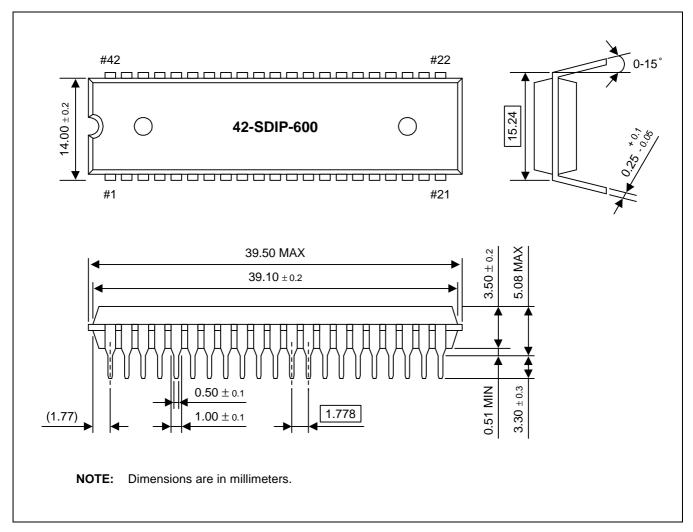

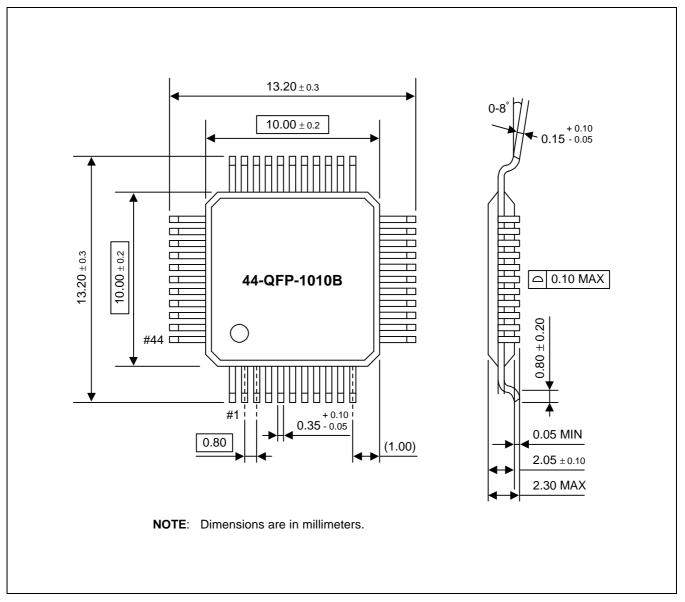

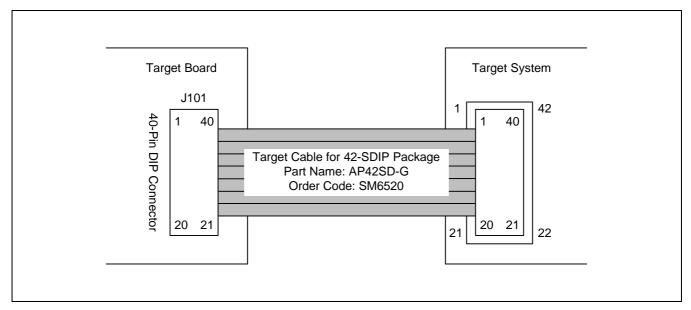

S3C8639/C863A/P863A are a versatile microcontrollers which are ideal for use in multi-sync monitors or in general-purpose applications that require sophisticated timer/counter, PWM, sync signal processing, A/D converter, and multi-master IIC-bus support with DDC. They are available in a 42-pin SDIP or a 44-pin QFP package.

### **OTP**

S3C8639/C863A microcontrollers are also available in OTP (One Time Programmable) version named, S3P863A. S3P863A microcontroller has an on-chip 48-Kbyte one-time-programmable EPROM instead of masked ROM. S3P863A is comparable to S3C8639/C863A, both in function and pin configuration except its ROM size.

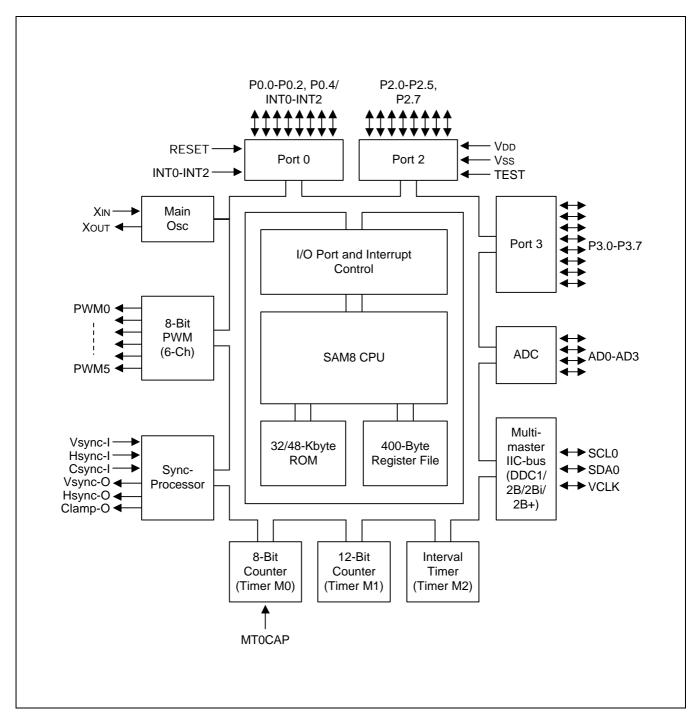

### S3C8647/F8647 MICROCONTROLLERS

S3C8647/F8647 single-chip 8-bit microcontrollers are based on the powerful SAM8 CPU architecture. The internal register file is logically expanded to increase the on-chip register space.

S3C8647/F8647 contain 24 Kbytes of on-chip program ROM.

In line with Samsung's modular design approach, the following peripherals are integrated with the SAM8 core:

- Three programmable I/O ports (total 19 pins)

- One 8-bit basic timer for oscillation stabilization and watchdog functions

- One 8-bit general-purpose timer/counter with selectable clock sources

- One interval timer

- One 12-bit counter with selectable clock sources, including Hsync or Csync input

- PWM block with six 8-bit PWM circuits

- Sync processor block (for Vsync and Hsync I/O, Csync input, and Clamp signal output)

- DDC Multi-master IIC-Bus

- 4-channel A/D converter (4-bit resolution)

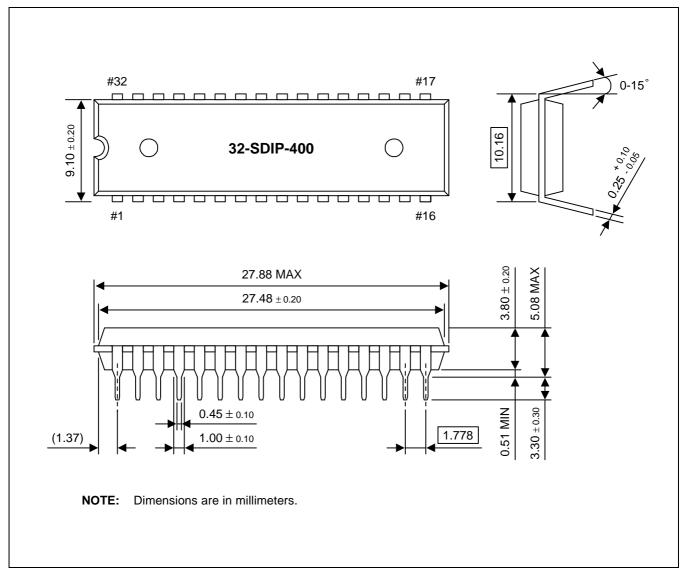

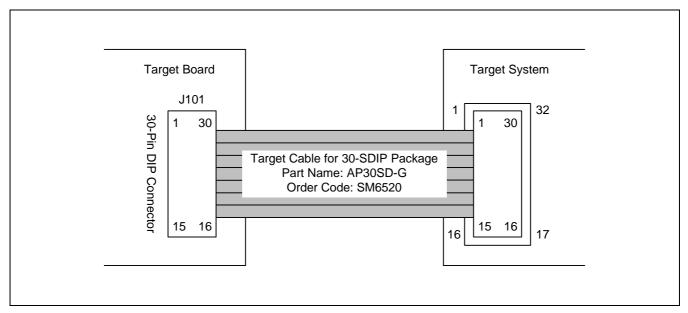

S3C8647/F8647 are a versatile microcontrollers which are ideal for use in multi-sync monitors or in general-purpose applications that require sophisticated timer/counter, PWM, sync signal processing, A/D converter, and multi-master IIC-bus support with DDC. They are available in a 32-pin SDIP/SOP package.

### **FLASH**

S3C8647 microcontroller is also available in Flash version named, S3F8647. S3F8647 microcontroller has an on-chip 24-Kbyte flash cells instead of masked ROM. S3F8647 is comparable to S3C8647, both in function and pin configuration.

### **FEATURES**

### **CPU**

SAM88RC CPU core

### Memory

S3C8639: 32-Kbyte program memory (ROM) S3C863A: 48-Kbyte program memory (ROM) S3C8647: 24-Kbyte program memory (ROM)

S3C8639: 784-byte general-purpose register area

S3C863A: 1040-byte general-purpose

register area

S3C8647: 400-byte general-purpose

register area

### Instruction Set

- 78 instructions

- IDLE and STOP instructions added for power-down modes

### **Instruction Execution Time**

Minimum 333 ns (with 12 MHz CPU clock)

### Interrupts

- Ten (nine)\* interrupt sources/vectors (S3C8647)\*

- Eight (seven)\* interrupt level (S3C8647)\*

- · Fast interrupt feature

### General I/O

S3C863X: four I/O ports (total 27pins)

S3C8647: three I/O ports (total 19pins)

### **8-Bit Basic Timer**

- Programmable timer for oscillation stabilization interval control or watchdog timer function

- Three selective internal clock frequencies

### **Timer/Counters**

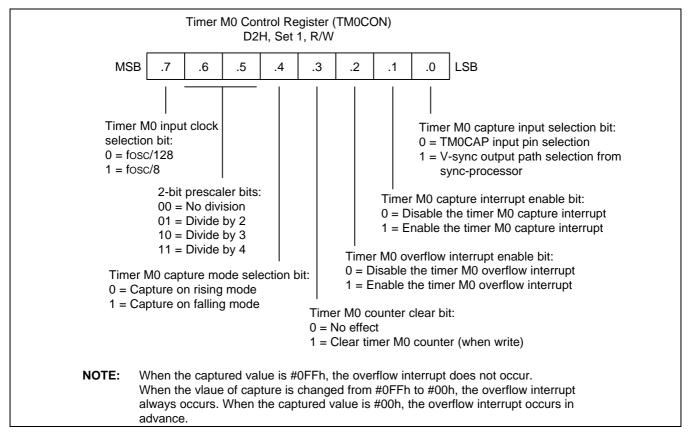

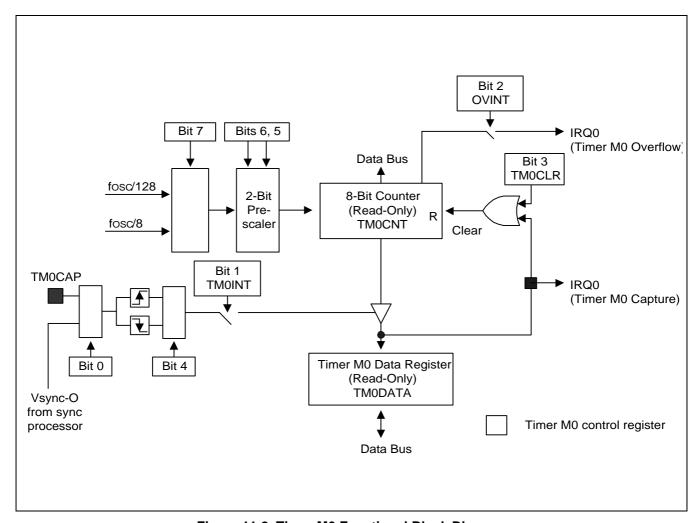

- One 8-bit Timer/Counter with several clock sources (Capture mode)

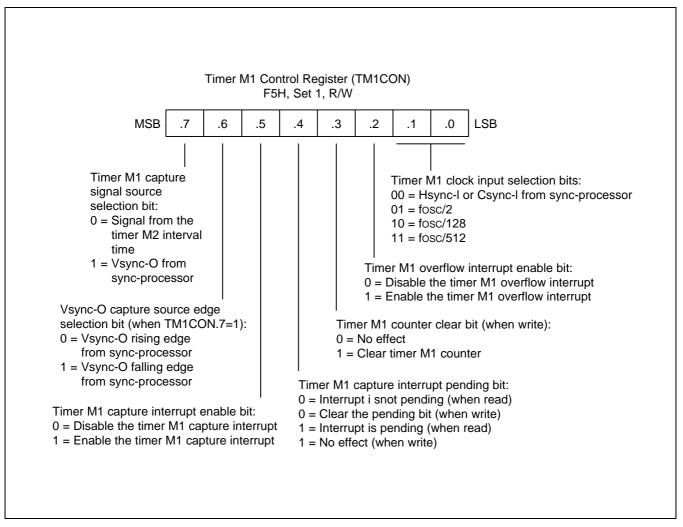

- One 12-bit Counter with H-/C-sync and several clock sources

- One Interval Timer

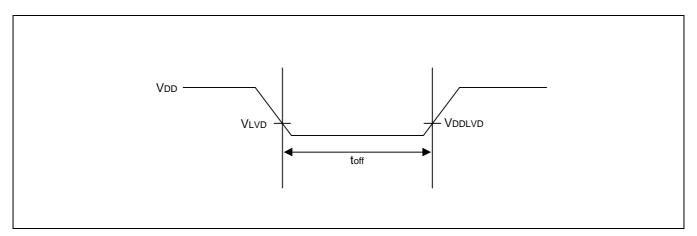

### Low Voltage Detector (LVD & POR)

### **Pulse Width Modulator (PWM)**

8-bit PWM: 7(6)\*-Ch (S3C8647)\*

(6-bit basic frame with 2-bit extension)

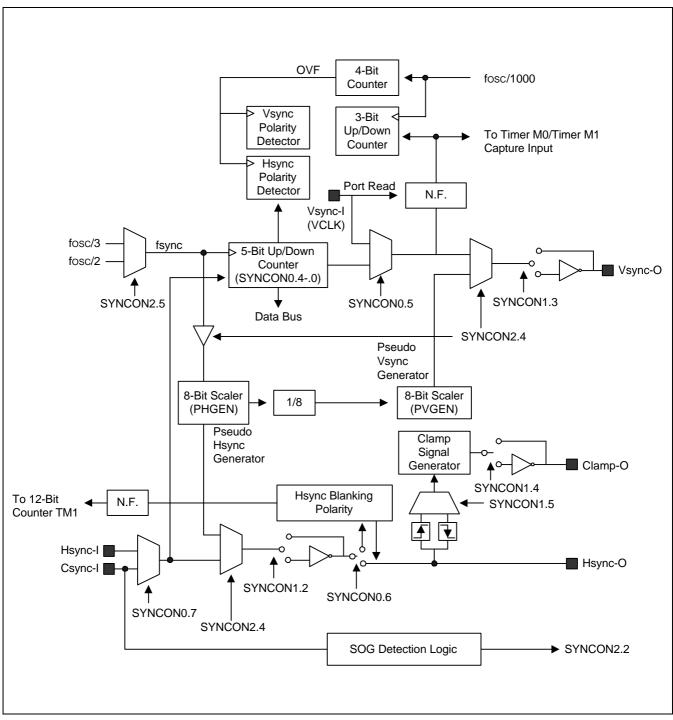

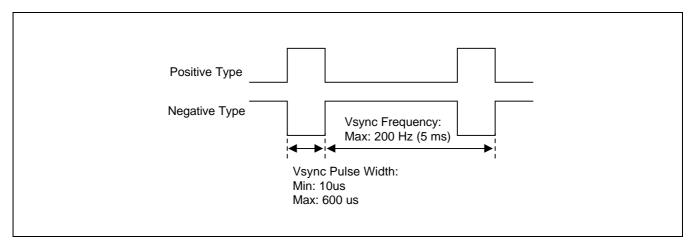

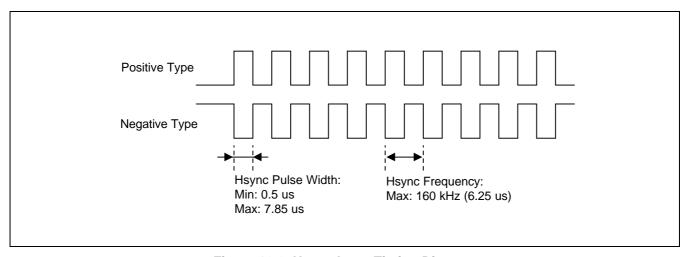

### **Sync-Processor Block**

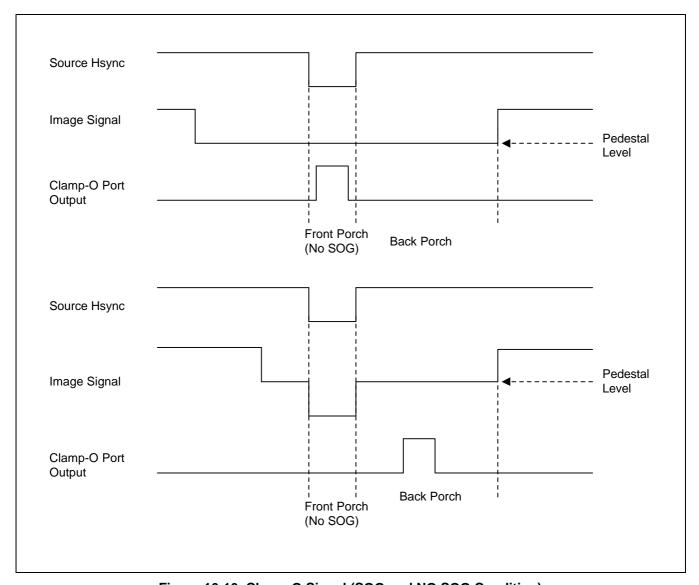

- Vsync-I, Hsync-I, Csync-I input and Vsync-O, Hsync-O, Clamp-O output pins

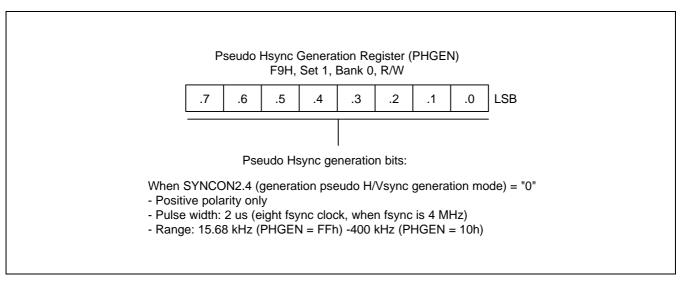

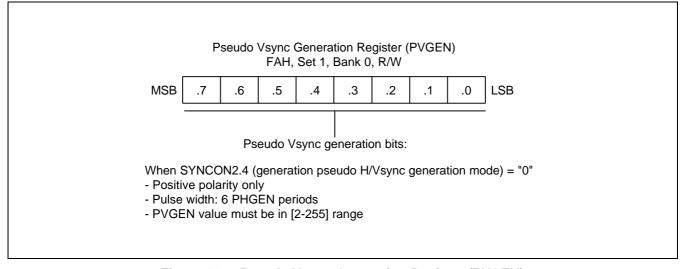

- Programmable Pseudo sync signal generation

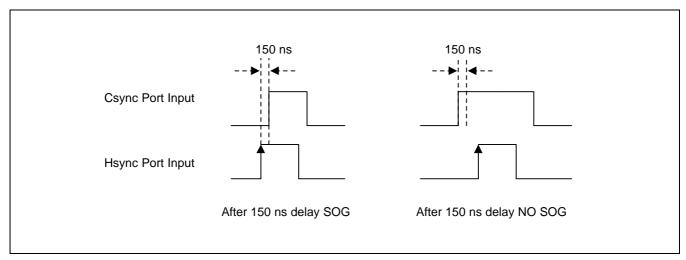

- Auto SOG detection

- Auto H-/V-sync polarity detection

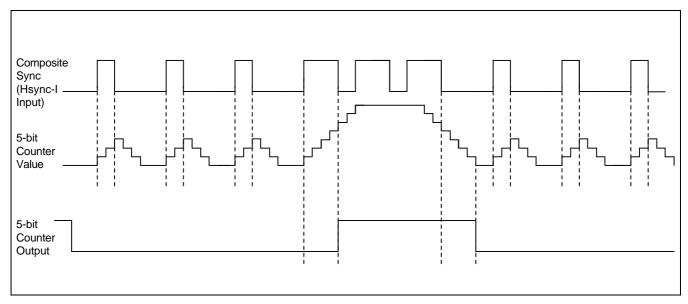

- Composite sync detection

### **DDC Multi-Master IIC-Bus 1-Ch**

- Serial Peripheral Interface

- Support for Display Data Channel (DDC1/DDC2B/DDC2Bi/DDC2B+)

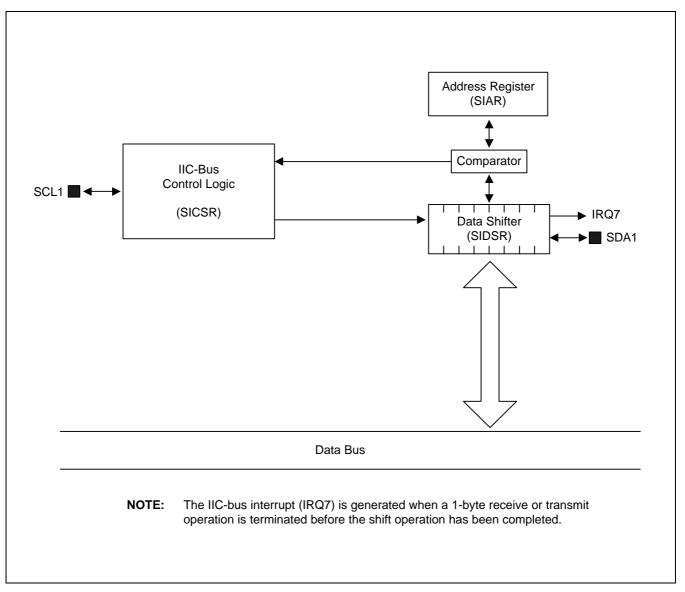

### Slave Only IIC-Bus 1-Ch (Only S3C863X)

· Serial Peripheral Interface

### A/D Converter

4-channel; 8(4)\*-bit resolution (S3C8647)\*

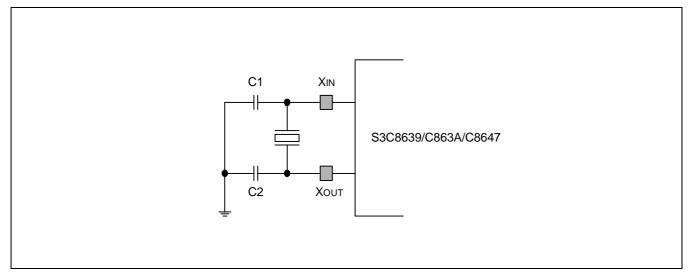

### **Oscillator Frequency**

- 8 MHz to 12 MHz crystal operation

- Internal Max. 12 MHz CPU clock

### **Operating Temperature Range**

− 40 °C to + 85 °C

### **Operating Voltage Range**

• 3.0(4.0)\* V to 5.5 V (S3C8647)\*

### **Package Types**

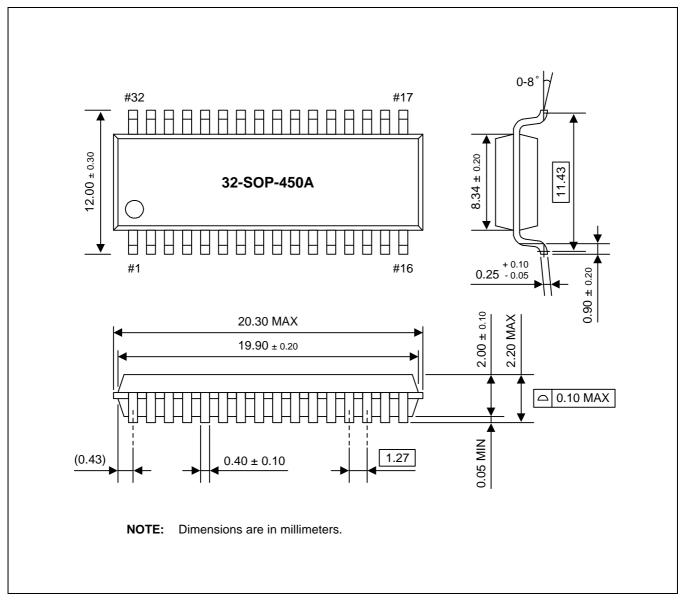

S3C863X: 42-pin SDIP, 44-pin QFP S3C8647: 32-pin SDIP, 32-pin SOP

### **BLOCK DIAGRAM**

Figure 1-1. Block Diagram (S3C863X)

Figure 1-2. Block Diagram (S3C8647)

### **PIN ASSIGNMENTS**

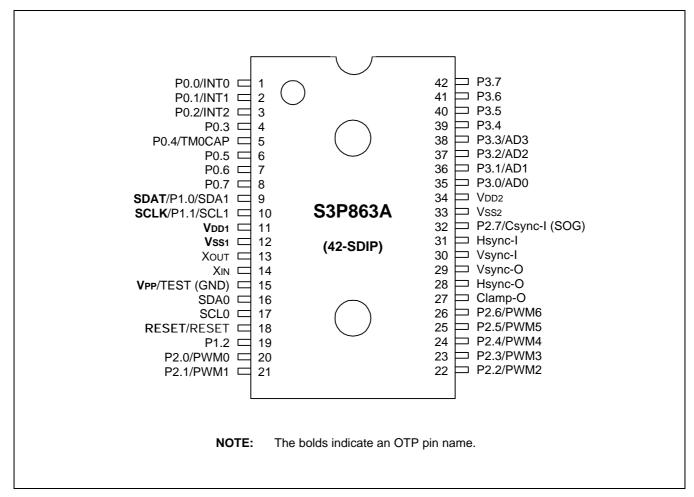

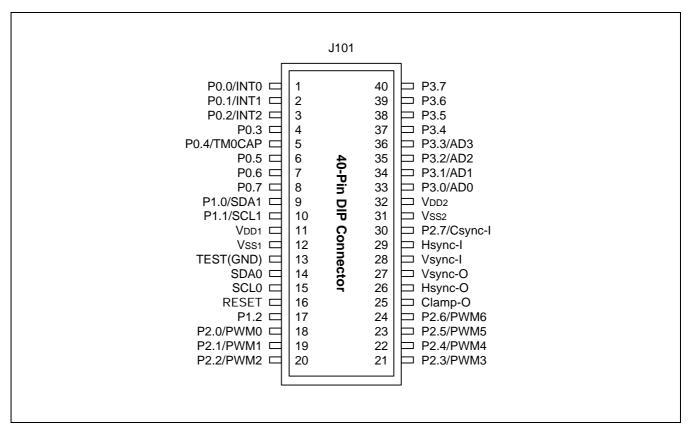

Figure 1-3. S3C8639/C863A Pin Assignment (42-SDIP)

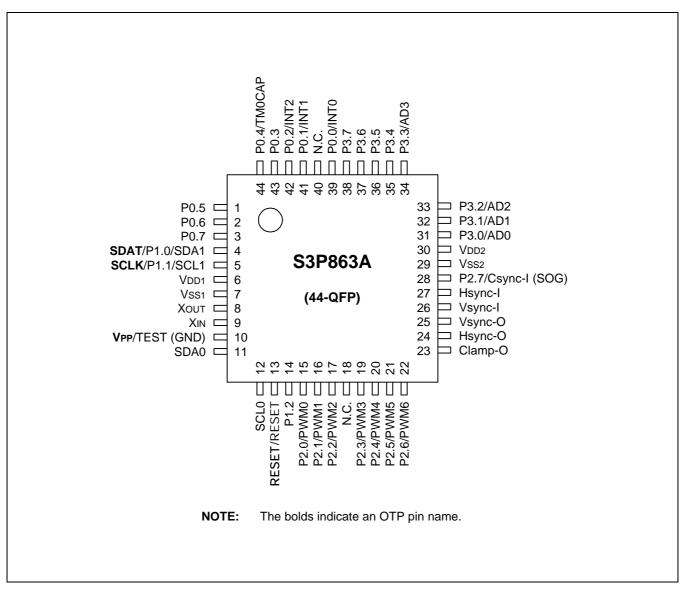

Figure 1-4. S3C8639/C863A Pin Assignment (44-QFP)

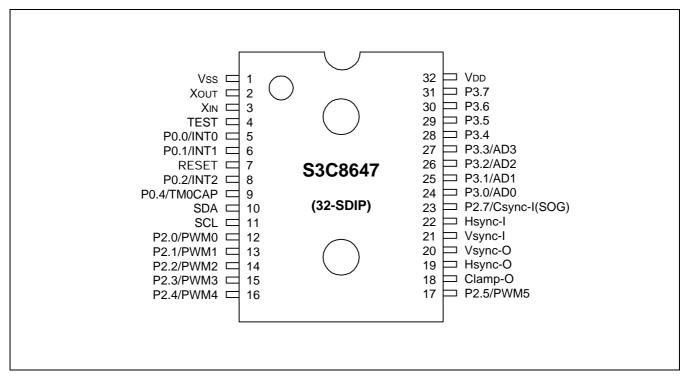

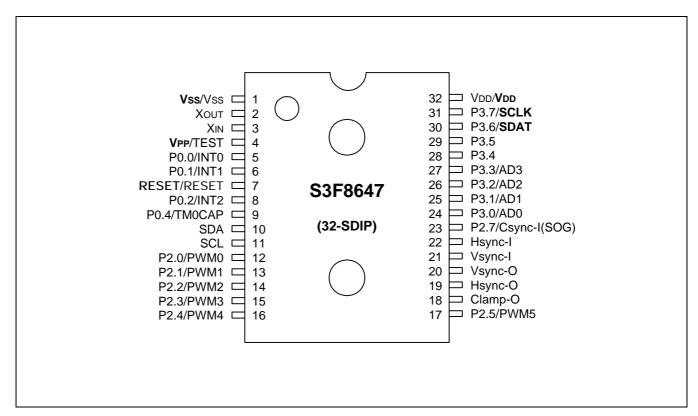

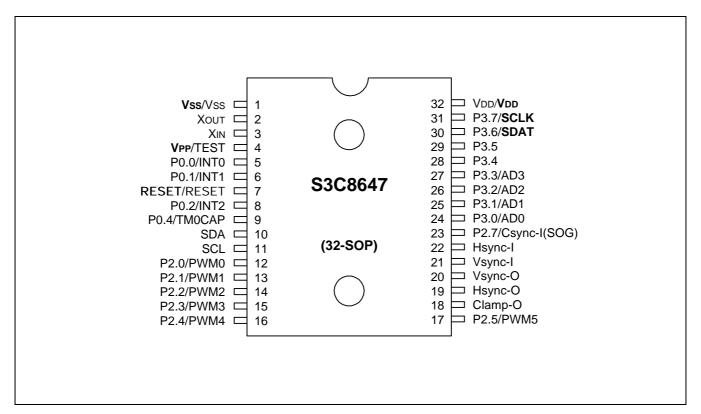

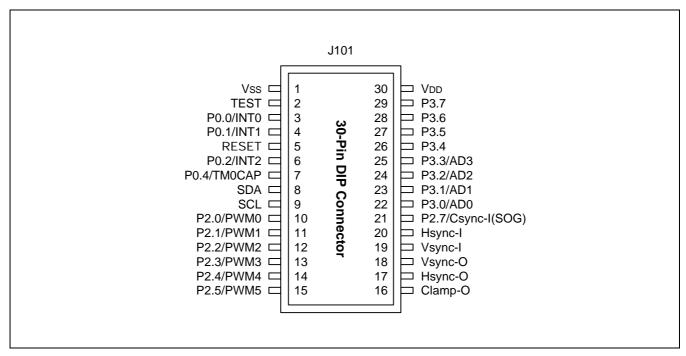

Figure 1-5. S3C8647 Pin Assignment (32-SDIP)

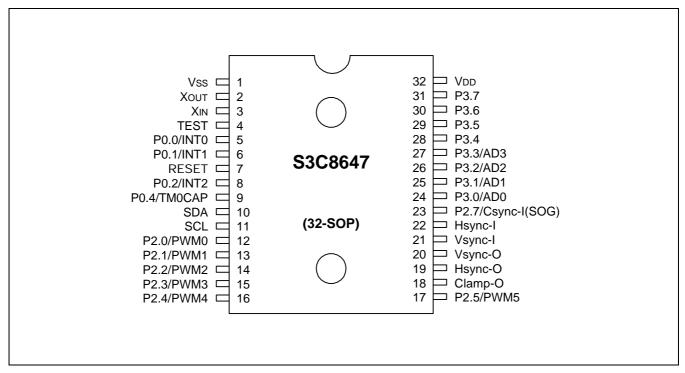

Figure 1-6. S3C8647 Pin Assignment (32-SOP)

# **PIN DESCRIPTIONS**

Table 1-1. S3C8639/C863A Pin Descriptions

|                                                                                           | Tuble 1 1. 000000/0000A1 iii Descriptions |                                                                                                                                                                                                         |                                               |                                              |                                                                 |  |

|-------------------------------------------------------------------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------|-----------------------------------------------------------------|--|

| Pin<br>Names                                                                              | Pin<br>Type                               | Pin<br>Description                                                                                                                                                                                      | Circuit<br>Type                               | SDIP Pin<br>Numbers                          | Shared Functions                                                |  |

| P0.0<br>P0.1<br>P0.2<br>P0.3 (note)<br>P0.4<br>P0.5 (note)<br>P0.6 (note)<br>P0.7 (note)  | I/O                                       | General-purpose, 8-bit I/O port. Shared functions include three external interrupt inputs and I/O for timer M0. Selective configuration of port 0 pins to input or output mode is supported.            | D-1<br>D-1<br>D-1<br>D-1<br>D-1<br>D-1<br>D-1 | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8         | INT0<br>INT1<br>INT2<br>TM0CAP                                  |  |

| P1.0 (note)<br>P1.1 (note)<br>P1.2 (note)                                                 | I/O                                       | General-purpose, 8-bit I/O port. Selective configuration is available for port 1 pins to input, push-pull output, n-channel open-drain mode, or IIC-bus clock and data I/O.                             | E-1<br>E-1<br>E-1                             | 9<br>10<br>19                                | SDA1<br>SCL1                                                    |  |

| P2.0<br>P2.1<br>P2.2<br>P2.3<br>P2.4<br>P2.5<br>P2.6 (note)<br>P2.7                       | I/O                                       | General-purpose, 8-bit I/O port Selective configuration of port 2 pins to input or output mode is supported. The port 2 pin circuits are designed to push-pull PWM output and Csync (SOG) signal input. | D-1<br>D-1<br>D-1<br>E-1<br>E-1<br>E-1<br>D-1 | 20<br>21<br>22<br>23<br>24<br>25<br>26<br>32 | PWM0<br>PWM1<br>PWM2<br>PWM3<br>PWM4<br>PWM5<br>PWM6<br>Csync-I |  |

| P3.0–P3.3<br>P3.4–P3.7                                                                    | I/O                                       | General-purpose, 8-bit I/O port Selective configuration port 3 pins to input or output mode is supported. Multiplexed for alternative use as A/D converter inputs AD0–AD3.                              | E-1<br>E                                      | 35–38<br>39–42                               | AD0-AD3                                                         |  |

| Hsync-I<br>Vsync-I<br>Clamp-O<br>Hsync-O<br>Vsync-O<br>SDA0<br>SCL0                       | <br>  0<br>  0<br> /0<br> /0              | The pins are sync processor signal I/O and IIC-bus clock and data I/O.                                                                                                                                  | A-3<br>A-3<br>A<br>A<br>A<br>G-3<br>G-3       | 31<br>30<br>27<br>28<br>29<br>16<br>17       | -                                                               |  |

| V <sub>DD1</sub> , V <sub>SS1</sub> (note),<br>V <sub>DD2</sub> , V <sub>SS2</sub> (note) | _                                         | Power pins                                                                                                                                                                                              | _<br>_                                        | 11, 12<br>34, 33                             | _                                                               |  |

| X <sub>IN</sub> , X <sub>OUT</sub>                                                        | -                                         | System clock I/O pins                                                                                                                                                                                   | _                                             | 14, 13                                       | _                                                               |  |

| RESET                                                                                     | I                                         | System RESET pin                                                                                                                                                                                        | В                                             | 18                                           | _                                                               |  |

| TEST                                                                                      | I                                         | Factory test pin input <b>0 V: Normal operation</b> , 5 V: Factory test mode                                                                                                                            | _                                             | 15                                           | _                                                               |  |

NOTE: Not used in S3C8647.

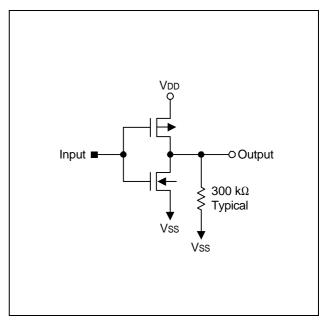

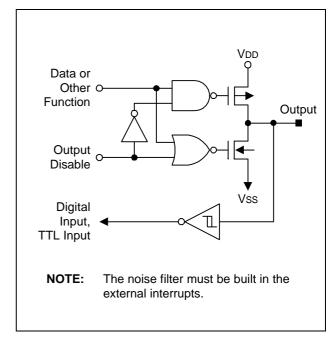

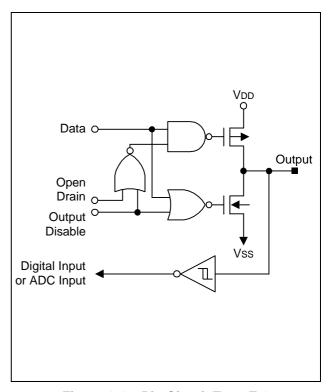

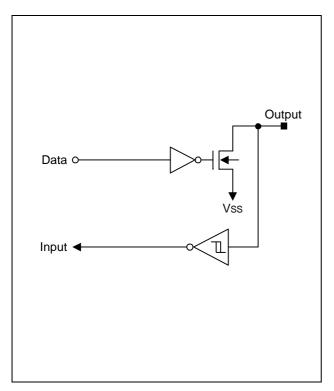

### **PIN CIRCUITS DIAGRAM**

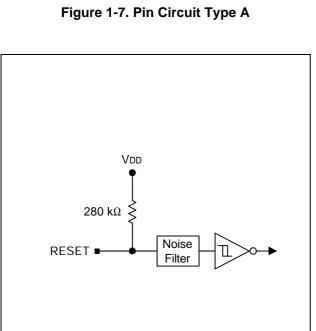

Figure 1-9. Pin Circuit Type B (RESET)

Figure 1-8. Pin Circuit Type A-3

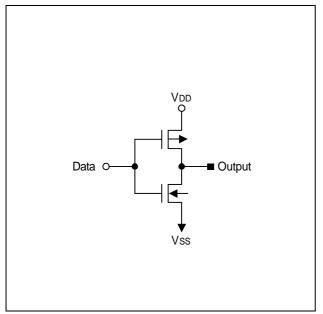

Figure 1-10. Pin Circuit Type D-1

Figure 1-11. Pin Circuit Type E

Figure 1-12. Pin Circuit Type E-1

Figure 1-13. Pin Circuit Type G-3

# **NOTES**

# 2 ADDRESS SPACES

### **OVERVIEW**

S3C8639/C863A/C8647 microcontrollers have two types of address space:

- Internal program memory (ROM)

- Internal register file

The 16-bit address and data bus support program memory operations. The separate 8-bit register bus carries addresses and data between the CPU and the internal register file. S3C8639/C863A/C8647 employ an internal 32/48/24-Kbyte mask-programmable ROM. External memory interface is not implemented.

There are 852/1108/462 8-bit registers in the internal register file. In this space, there are 784/1040/400 registers for general use, 19 for CPU and system control, and 49(43) for peripheral control and data. An area of 16-byte common working register (scratch) is part of the general-purpose register space. Most of these registers serve as either a source or destination address, or as accumulators for data memory operations.

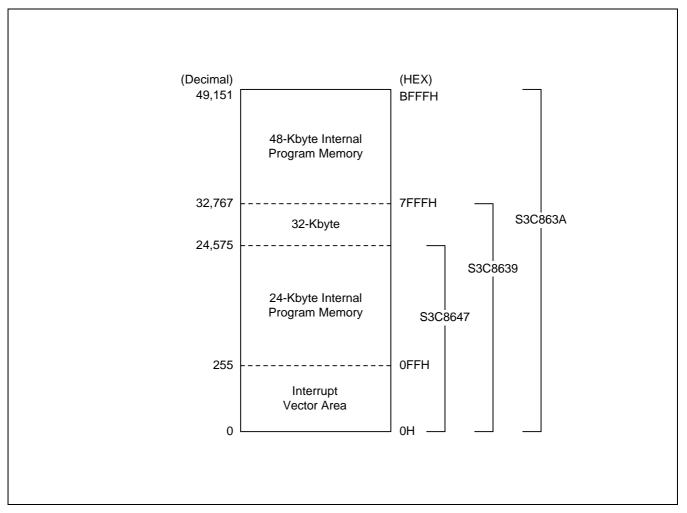

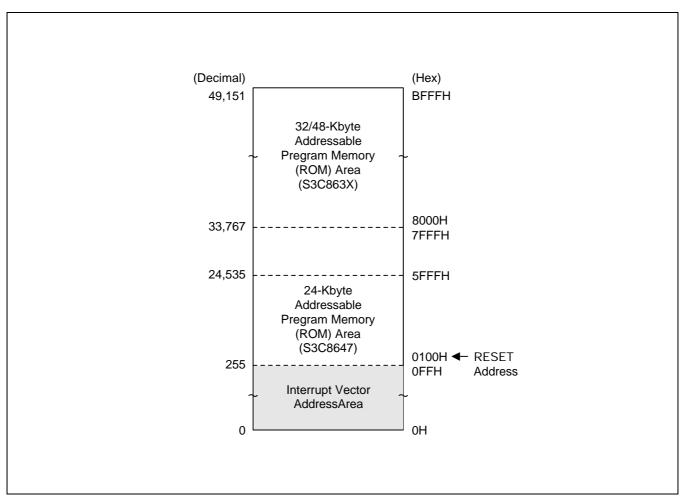

### **PROGRAM MEMORY (ROM)**

Program memory (ROM) stores program code or table data. S3C8639/C863A employ 32/48-Kbytes of mask-programmable program memory. The memory address range is 0H–7FFFH/BFFFH (see Figure 2-1).

S3C8647 employs 24-Kbytes of mask-programmable program memory. The memory address large is 0H-5FFFH.

The first 256 bytes of the ROM (0H–FFH) are reserved for interrupt vector addresses. Unoccupied locations in the address range can be used as normal program memory. When you use the vector address area to store program code, be careful not to overwrite vector addresses stored in these locations.

The ROM address at which program execution starts after a reset is 0100H.

Figure 2-1. Program Memory Address Space

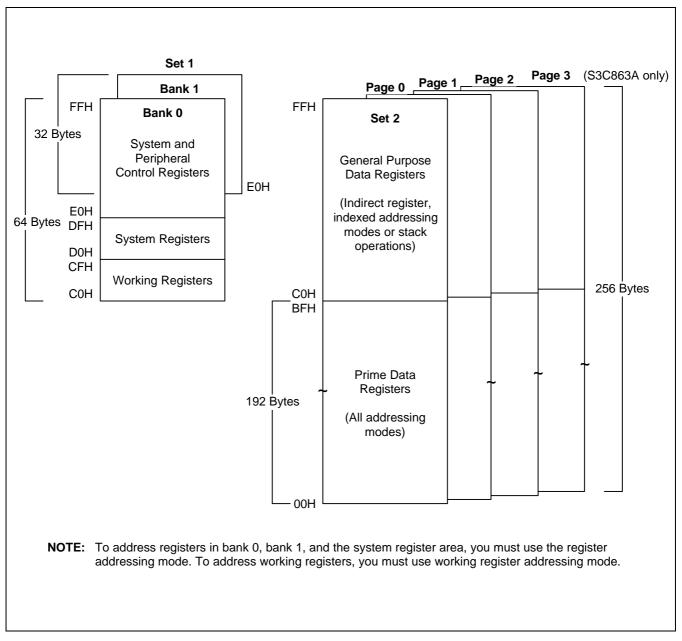

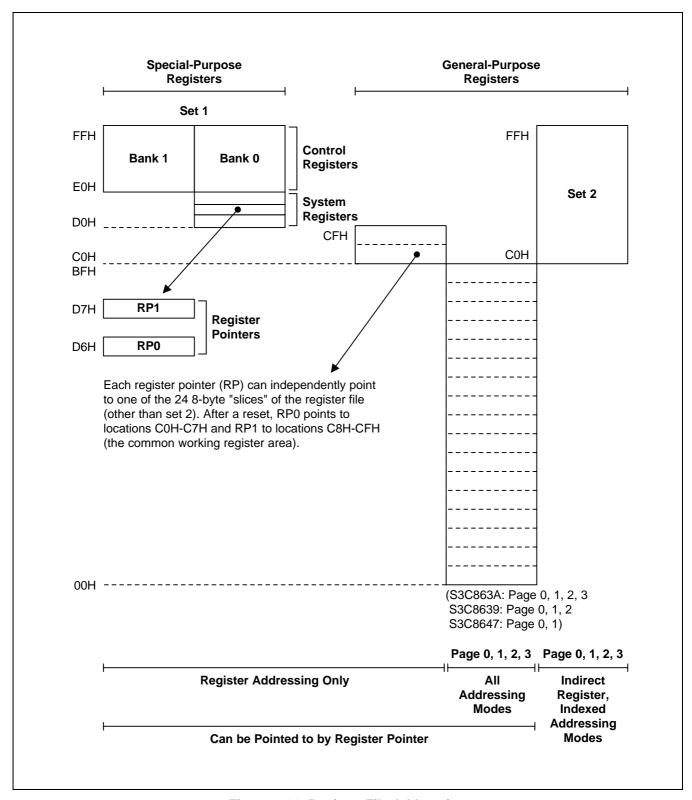

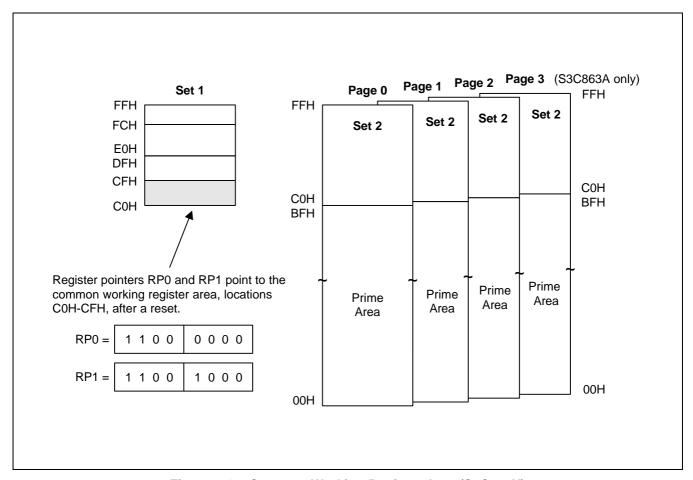

### REGISTER ARCHITECTURE

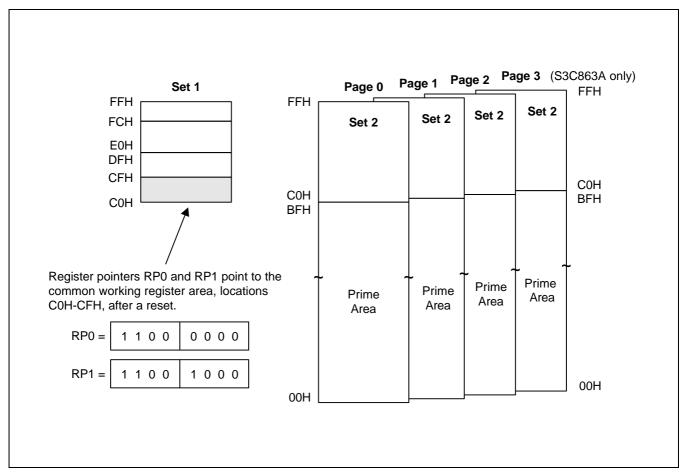

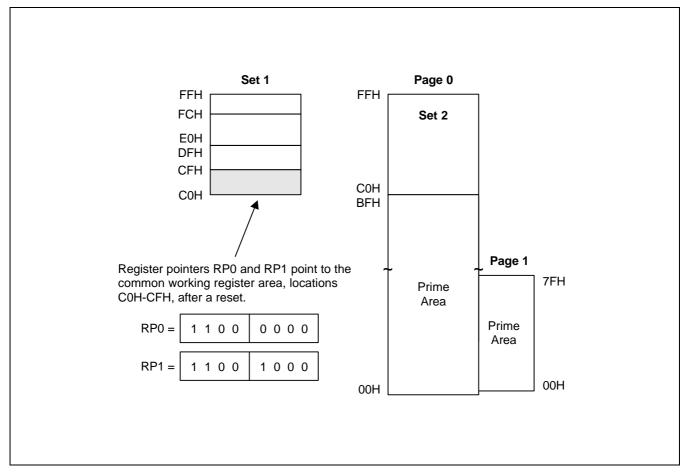

The upper 64-byte area of the S3C8639/C863A/C8647 files is logically expanded to two 64-byte areas, called *set 1* and *set 2*. The upper 32-byte area of set 1 is divided into two register banks, *bank 0* and *bank 1*. The total physical register space is thereby expanded internal register to 864/1120 bytes. Within this physical space, there are 864/1120/462-byte registers, of which 852/1108/450 are addressable.

Given the microcontroller's 8-bit register bus architecture, up to 256 bytes of physical register space can be addressed as a single page. The S3C8639 register files have three pages, page 0, page 1 and page 2. And the S3C863A register files have four pages, page 0, page 1, page 2 and page 3. The S3C8647 register files have two pages, page 0, and page 1. All page contain 256 bytes respectively.

The extension of physical register space into separately addressable areas (sets, banks, and pages) is enabled by addressing mode restrictions, the select bank instructions SB0 and SB1, and the register page pointer, PP.

Specific register types and areas (in bytes) they occupy in the S3C8639/C863A/C8647 internal register files are summarized in Table 2-1.

**Table 2-1. Register Type Summary**

| Register Type                                                                  | Number of Bytes<br>(S3C8639/C863A) | Number of Bytes<br>(S3C8647) |

|--------------------------------------------------------------------------------|------------------------------------|------------------------------|

| General-purpose registers (including the 16-byte common working register area) | 784/1040                           | 400                          |

| CPU and system control registers                                               | 19                                 | 19                           |

| Clock, peripheral, I/O control, and data registers                             | 49                                 | 43                           |

| Total Addressable Bytes                                                        | 852/1108                           | 462                          |

Figure 2-2. Internal Register File Organization (S3C863X)

Figure 2-3. Register File Layout (S3C8647)

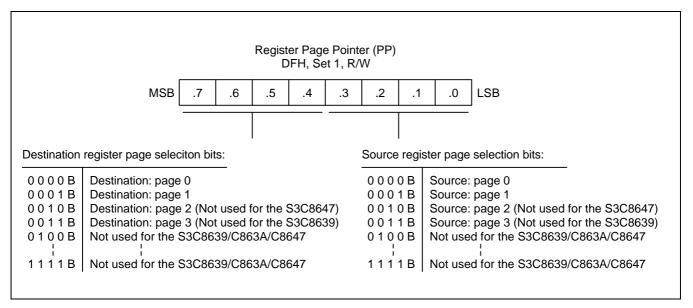

### **REGISTER PAGE POINTER (PP)**

The SAM8 architecture supports the logical expansion of the physical 256-byte internal register file (which use an 8-bit data bus) to as many as 16 separately addressable register pages. Page addressing is controlled by the register page pointer (PP, DFH). Two logical pages are implemented in S3C8639/C863A/C8647. These pages are used as general purpose register space.

Figure 2-4. Register Page Pointer (PP)

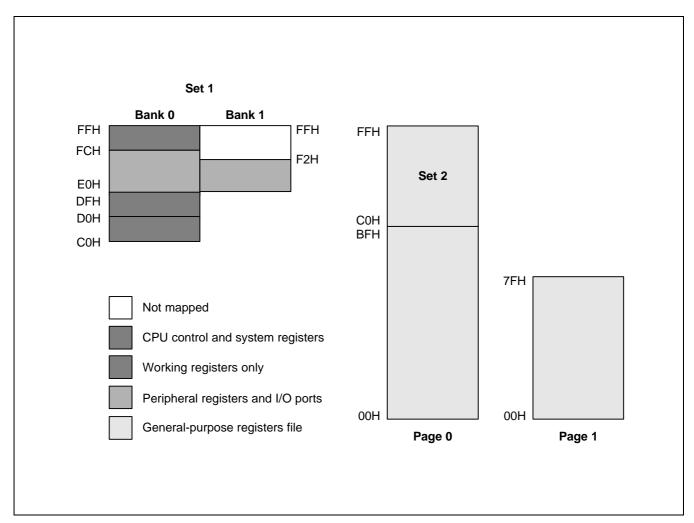

### **REGISTER SET 1**

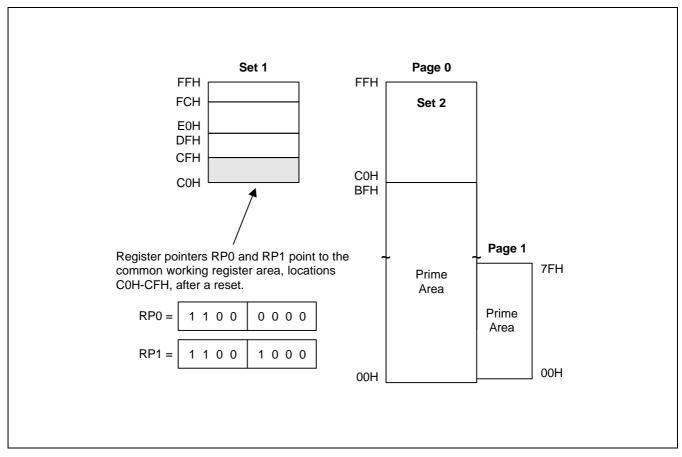

The term set 1 refers to the upper 64 bytes of the register file, locations C0H–FFH. The upper 32-byte area of this 64-byte space (E0H–FFH) is divided into two 32-byte register banks, bank 0 and bank 1. You execute the set register bank instructions SB0 or SB1 to address one bank or the other. Bank 0 is automatically selected by a reset operation.

In S3C8639/C863A, register locations of only E0H–F4H are addressable in the bank 1 area; the remaining locations (F5H–FFH) are not mapped. The lower 32-byte area of set 1 is not banked and can be addressed at any time. It contains 16 mapped system registers (D0H–DFH) and a 16-byte "scratch" area (C0H–CFH) for working register addressing.

Registers in set 1 are directly accessible at all times using Register addressing mode. The 16-byte working register area can only be accessed using working register addressing. (For more information about working register addressing, please refer to Chapter 3, "Addressing Modes.")

### **REGISTER SET 2**

The same 64-byte physical space that is used for set 1 register locations C0H–FFH is logically duplicated to add another 64 bytes of space. This expanded area of the register file is called *set* 2. All set 2 locations (C0H–FFH) can be addressed in all page of the S3C8639/C863A register space.

The logical division of set 1 and set 2 is maintained by means of addressing mode. In order to access set 1, you should use resister addressing mode. When you want to access register locations in set 2, you have to select Register Indirect addressing mode or Indexed addressing mode access register locations in set 2.

### PRIME REGISTER SPACE

The lower 192 bytes of the 256-byte physical internal register file (00H–BFH) is called the *prime register space*, or more simply, the *prime area*. You can access registers in this address range at all page using any of the seven explicit addressing modes (see chapter 3, "Addressing Modes"). All registers in the prime area can be addressed immediately after a reset.

Figure 2-5. Set 1, Set 2, and Prime Area Register Map (S3C863X)

Figure 2-6. Set 1, Set 2, and Prime Area Register Map (S3C8647)

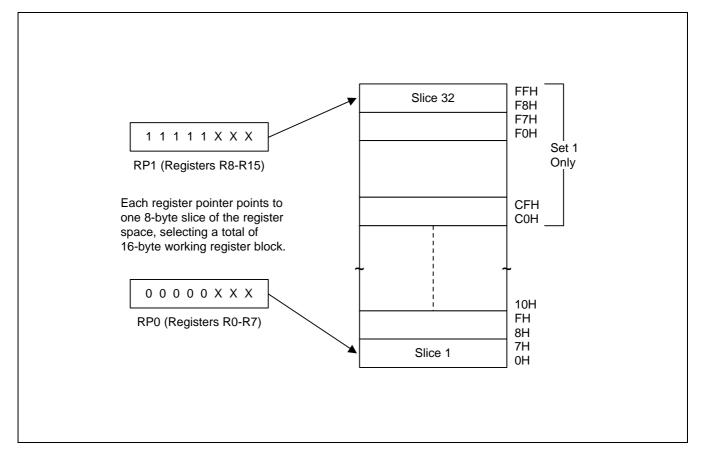

### **WORKING REGISTERS**

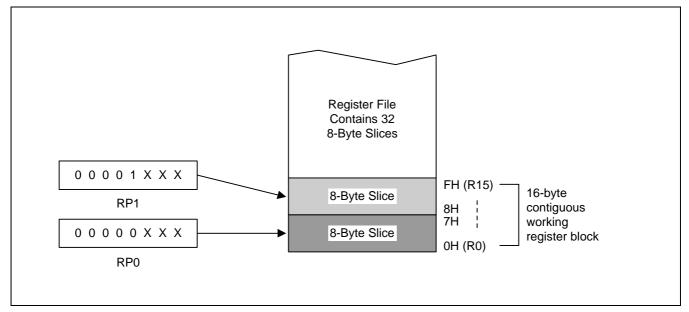

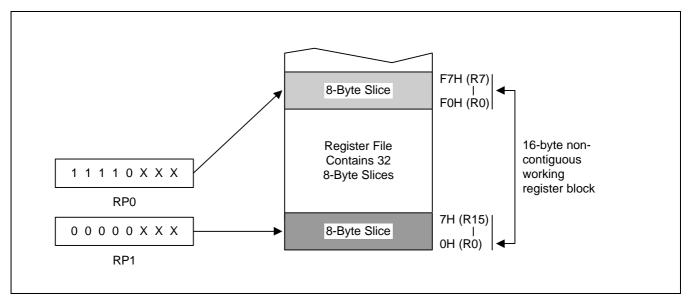

Instructions can access specific 8-bit registers or 16-bit register pairs using either 4-bit or 8-bit address fields. When 4-bit working register addressing is used, the 256-byte register file can be seen by the programmer as one that consists of 32 8-byte register groups or "slices." Each slice comprises of eight 8-bit registers.

With the two 8-bit register pointers, RP1 and RP0 employed, two working register slices can be selected at any time to form a 16-byte working register block. The register pointers help, you move this 16-byte register block to anywhere in the addressable register file, except for the set 2 area.

The terms *slice* and *block* are used in this manual to help you visualize the size and relative locations of selected working register spaces:

- One working register *slice* is 8 bytes (eight 8-bit working registers; R0–R7 or R8–R15)

- One working register *block* is 16 bytes (sixteen 8-bit working registers; R0–R15)

All the registers in an 8-byte working register slice have the same binary value for their five most significant address bits. This makes it possible for each register pointer to point to one of the 24 slices in the register file. The base addresses for the two 8-byte register slices selected are contained in register pointers RP0 and RP1.

After a reset, RP0 and RP1 always point to the 16-byte common area in set 1 (C0H-CFH).

Figure 2-7. 8-Byte Working Register Areas (Slices)

### **USING THE REGISTER POINTERS**

Register pointers of RP0 and RP1 which are mapped to the addresses D6H and D7H in set 1, are used to select two movable 8-byte working register slices in the register file. After a reset, they point to the working register common area: RP0 points to the addresses C0H–C7H, and RP1 points to the addresses C8H–CFH.

You can change a register pointer value, by loading a new value to RP0 and/or RP1 using an SRP or LD instruction (see Figures 2-6 and 2-7).

In working register addressing, you can only access those two 8-bit slices of the register file that are currently pointed to by RP0 and RP1. You cannot use the register pointers to select a working register area in set 2, C0H–FFH, because these locations can be accessed only with Indirect Register or Indexed addressing modes.

The 16-byte working register block selected usually consists of two contiguous 8-byte slices. As a general programming guideline, we recommend that RP0 point to the "lower" slice and RP1 point to the "upper" slice (see Figure 2-6). In some cases, it may be necessary to define working register areas in different (non-contiguous) areas of the register file. In Figure 2-7, RP0 points to the "upper" slice and RP1 to the "lower" slice.

As a register pointer can point to either of the two 8-byte slices in the working register block, you can flexibly define the working register area to support a variety of program requirements.

### PROGRAMMING TIP — Setting the Register Pointers

Figure 2-8. Contiguous 16-Byte Working Register Block

Figure 2-9. Non-Contiguous 16-Byte Working Register Block

### PROGRAMMING TIP — Calculate the Sum of a Series of Registers Using the RPs

Calculate the sum of registers 80H–85H using the register pointer and working register addressing. The register addresses from 80H through 85H contain the values 10H, 11H, 12H, 13H, 14H, and 15H, respectively:

| SRP0 | #80H  | ; RP0 ← 80H                   |

|------|-------|-------------------------------|

| ADD  | R0,R1 | ; $R0 \leftarrow R0 + R1$     |

| ADC  | R0,R2 | ; $R0 \leftarrow R0 + R2 + C$ |

| ADC  | R0,R3 | ; $R0 \leftarrow R0 + R3 + C$ |

| ADC  | R0,R4 | ; $R0 \leftarrow R0 + R4 + C$ |

| ADC  | R0,R5 | ; $R0 \leftarrow R0 + R5 + C$ |

The sum of these six registers, 6FH, is located in the register R0 (80H). The instruction string used in this example takes 12 bytes of instruction code and its execution time is 24 cycles. If the register pointer is not used to calculate the sum of these registers, the following instruction sequence would have to be used:

| ADD | 80H,81H | ; 80H ← (80H) + (81H)                |

|-----|---------|--------------------------------------|

| ADC | 80H,82H | ; $80H \leftarrow (80H) + (82H) + C$ |

| ADC | 80H,83H | ; $80H \leftarrow (80H) + (83H) + C$ |

| ADC | 80H,84H | ; $80H \leftarrow (80H) + (84H) + C$ |

| ADC | 80H,85H | ; $80H \leftarrow (80H) + (85H) + C$ |

The sum of the six registers, here, is also located in the register 80H. This instruction string, however, takes 15 bytes of instruction code instead of 12 bytes, and its execution time is 30 cycles instead of 24 cycles.

### REGISTER ADDRESSING

The SAM8 register architecture provides an efficient method of working register addressing that takes full advantage of shorter instruction formats to reduce execution time.

With Register (R) addressing mode, in which the operand value is the content of a specific register or register pair, you can access all locations in the register file except for set 2. With working register addressing, you use a register pointer to specify an 8-byte working register space in the register file and an 8-bit register within that space.

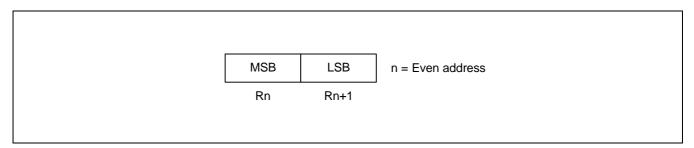

Registers are addressed either as a single 8-bit register or as a paired 16-bit register space. In a 16-bit register pair, the address of the first 8-bit register is always an even number and the address of the next register is always an odd number. The most significant byte of the 16-bit data is always stored in the even-numbered register; the least significant byte is always stored in the next (+1) odd-numbered register.

Working register addressing differs from Register addressing in a way that it uses a register pointer to specify an 8-byte working register space in the register file and an 8-bit register within that space (see Figure 3-2).

Figure 2-10. 16-Bit Register Pair

Figure 2-11. Register File Addressing

### **COMMON WORKING REGISTER AREA (C0H-CFH)**

After a reset, register pointers RP0 and RP1 automatically select two 8-byte register slices in set 1, locations C0H–CFH, as the active 16-byte working register block:

$RP0 \rightarrow C0H-C7H$  $RP1 \rightarrow C8H-CFH$

This16-byte address range is called *common working register area*. That is, locations in this area can be used as working registers by operations that address any location on any page in the register file. Typically, these working registers serve as temporary buffers for data operations between different pages.

Figure 2-12. Common Working Register Area (S3C863X)

Figure 2-13. Common Working Register Area (S3C8647)

### PROGRAMMING TIP — Addressing the Common Working Register Area

As the following examples show, you should access working registers in the common area, locations C0H–CFH, using working register addressing mode only.

**Examples:** 1. LD 0C2H,40H ; Invalid addressing mode!

Use working register addressing instead:

SRP #0C0H

LD R2,40H ; R2 (C2H)  $\leftarrow$  the value in location 40H

2. ADD 0C3H,#45H ; Invalid addressing mode!

Use working register addressing instead:

SRP #0C0H

ADD R3,#45H ; R3 (C3H)  $\leftarrow$  R3 + 45H

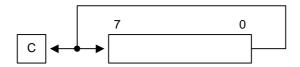

### 4-BIT WORKING REGISTER ADDRESSING

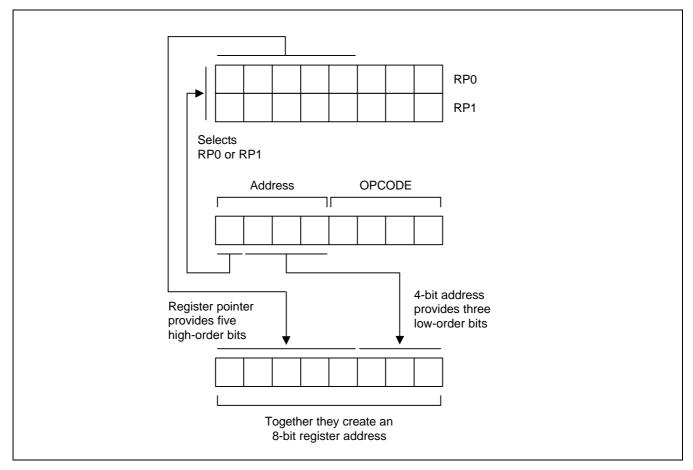

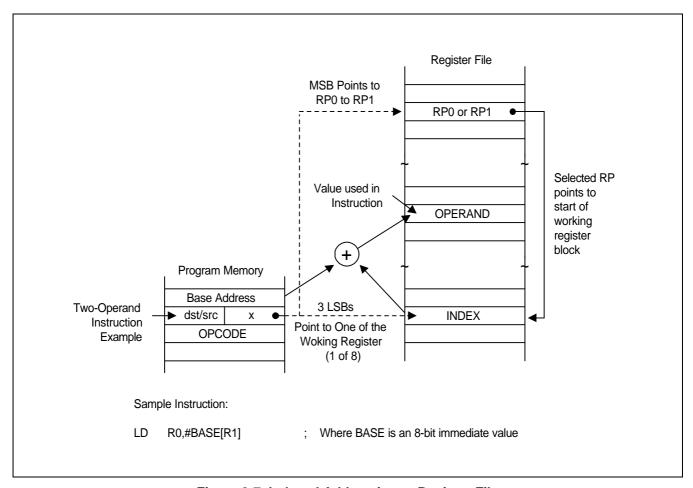

Each register pointer defines a movable 8-byte slice of working register space. The address information stored in a register pointer serves as an addressing "window" that makes it possible for instructions to access working registers very efficiently using short 4-bit addresses. When an instruction addresses a location in the selected working register area, the address bits are concatenated in the following way to form a complete 8-bit address:

- The high-order bit of the 4-bit address selects one of the register pointers ("0" selects RP0; "1" selects RP1);

- The five high-order bits in the register pointer select an 8-byte slice of the register space;

- The three low-order bits of the 4-bit address select one of the eight registers in the slice.

As shown in Figure 2-11, the result of this operation is that the five high-order bits from the register pointer are concatenated with the three low-order bits from the instruction address to form the complete address. As long as the address stored in the register pointer remains unchanged, the three bits from the address will always point to an address in the same 8-byte register slice.

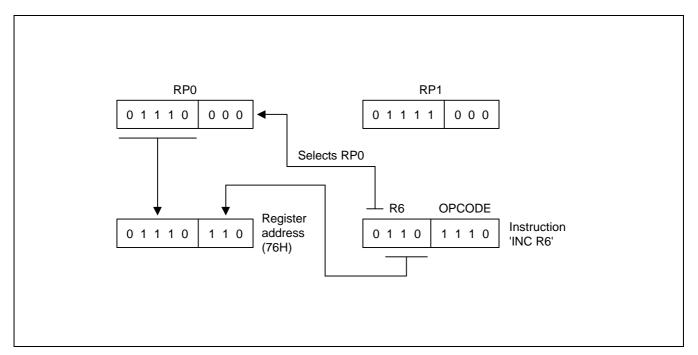

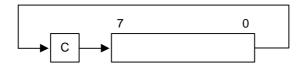

Figure 2-12 shows a typical example of 4-bit working register addressing: the high-order bit of the instruction "INC R6" is "0", which selects RP0. The five high-order bits stored in RP0 (01110B) are concatenated with the three low-order bits of the instruction's 4-bit address (110B) to produce the register address 76H (01110110B).

Figure 2-14. 4-Bit Working Register Addressing

Figure 2-15. 4-Bit Working Register Addressing Example

### 8-BIT WORKING REGISTER ADDRESSING

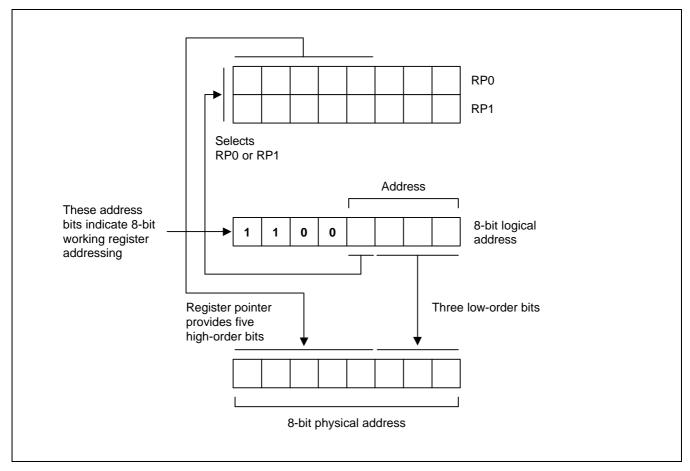

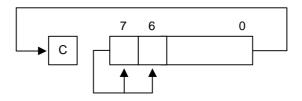

You can also use 8-bit working register addressing to access registers in a selected working register area. To initiate 8-bit working register addressing, the upper four bits of the instruction address must contain the value of 1100B. This 4-bit value (1100B) indicates that the remaining four bits have the same effect as 4-bit working register addressing.

As shown in Figure 2-13, the lower nibble of the 8-bit address is concatenated in much the same way as for 4-bit addressing: Bit 3 selects either RP0 or RP1, which then supplies the five high-order bits of the final address; the three low-order bits of the complete address are provided by the original instruction.

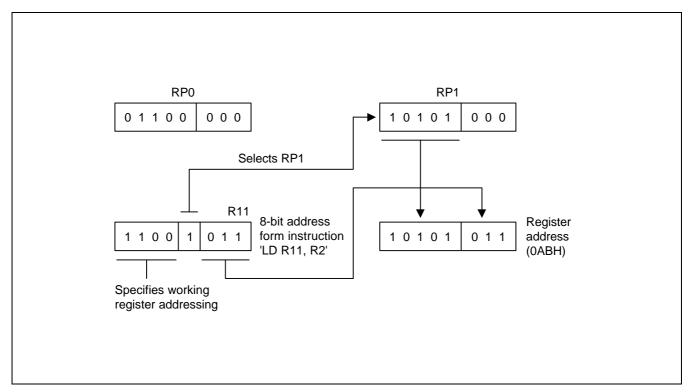

Figure 2-14 shows an example of 8-bit working register addressing: the four high-order bits of the instruction address (1100B) specify 8-bit working register addressing. Bit 4 ("1") selects RP1 and the five high-order bits in RP1 (10101B) become the five high-order bits of the register address. The three low-order bits of the register address (011) are provided by the three low-order bits of the 8-bit instruction address. The five address bits from RP1 and the three address bits from the instruction are concatenated to form the complete register address, 0ABH (10101011B).

Figure 2-16. 8-Bit Working Register Addressing

Figure 2-17. 8-Bit Working Register Addressing Example

### SYSTEM AND USER STACKS

S3-series microcontrollers can be programmed to use the system stack for subroutine calls, returns and interrupts and to store data. The PUSH and POP instructions are used to control system stack operations. The S3C8639/C863A architecture supports stack operations in the internal register file.

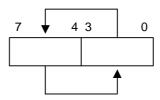

### **Stack Operations**

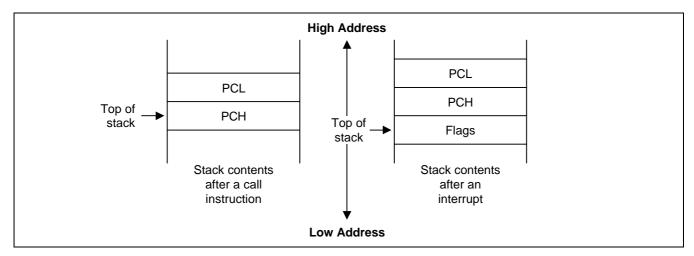

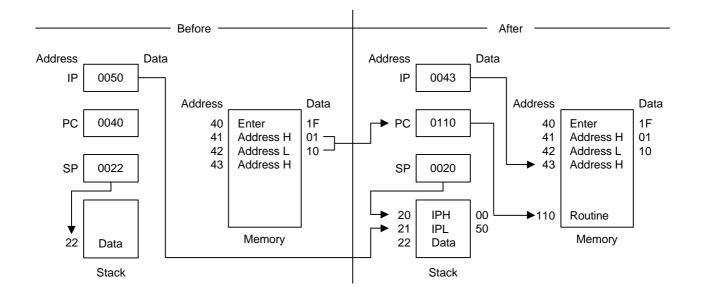

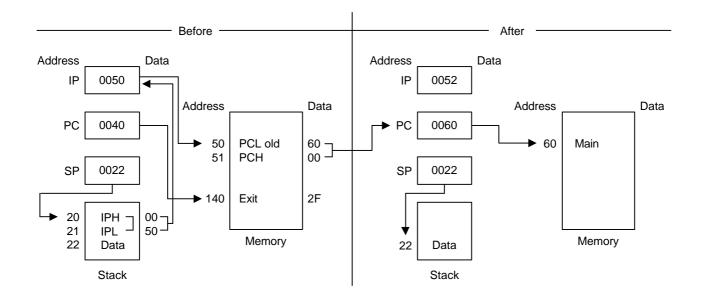

Return addresses for procedure calls and interrupts and data are stored on the stack. The contents of the PC are saved to stack by a CALL instruction and restored by the RET instruction. When an interrupt occurs, the contents of the PC and the FLAGS register are pushed to the stack. The IRET instruction then pops these values back to their original locations. The stack address is always decremented *before* a push operation and incremented *after* a pop operation. The stack pointer (SP) always points to the stack frame stored on the top of the stack, as shown in Figure 2-15.

Figure 2-18. Stack Operations

### **User-Defined Stacks**

You can freely define stacks in the internal register file as data storage locations. The instructions PUSHUI, PUSHUD, POPUI, and POPUD support user-defined stack operations.

### Stack Pointers (SPL, SPH)

Register locations D8H and D9H contain the 16-bit stack pointer (SP) that is used for system stack operations. The most significant byte of the SP address, SP15–SP8, is stored in the SPH register (D8H) and the least significant byte, SP7–SP0, is stored in the SPL register (D9H). After a reset, the SP value is undetermined.

Because only internal memory space is implemented in S3C8639/C863A, the SPL must be initialized to an 8-bit value in the range 00H–FFH. The SPH register is not needed here and can be used as a general-purpose register, if necessary.

When the SPL register contains the only stack pointer value (that is, when it points to a system stack in the register file), you can use the SPH register as a general-purpose data register. However, if an overflow or underflow condition occurs as the result of incrementing or decrementing the stack address in the SPL register during normal stack operations, the value in the SPL register will overflow (or underflow) to the SPH register, overwriting any data that is currently stored there. To avoid overwriting data in the SPH register, you can initialize the SPL value to "FFH" rather than "00H".

## PROGRAMMING TIP — Standard Stack Operations Using PUSH and POP

The following example shows you how to perform stack operations in the internal register file using PUSH and POP instructions:

| LD   | SPL,#0FFH | <ul><li>; SPL ← FFH</li><li>; (Normally, the SPL is set to 0FFH by the initialization</li><li>; routine)</li></ul> |

|------|-----------|--------------------------------------------------------------------------------------------------------------------|

| •    |           |                                                                                                                    |

| •    |           |                                                                                                                    |

| •    |           |                                                                                                                    |

| PUSH | PP        | ; Stack address 0FEH ← PP                                                                                          |

| PUSH | RP0       | ; Stack address 0FDH ← RP0                                                                                         |

| PUSH | RP1       | ; Stack address 0FCH ← RP1                                                                                         |

| PUSH | R3        | ; Stack address 0FBH ← R3                                                                                          |

| •    |           |                                                                                                                    |

| •    |           |                                                                                                                    |

| •    |           |                                                                                                                    |

| POP  | R3        | ; R3 ← Stack address 0FBH                                                                                          |

| POP  | RP1       | ; RP1 ← Stack address 0FCH                                                                                         |

| POP  | RP0       | : RP0 ← Stack address 0FDH                                                                                         |

| POP  | PP        | ; PP ← Stack address 0FEH                                                                                          |

# 3

# **ADDRESSING MODES**

### **OVERVIEW**

The program counter is used to fetch instructions that are stored in program memory for execution. Instructions indicate the operation to be performed and the data to be operated on. *Addressing mode* is used to determine the location of the data operand. The operands specified in SAM8 instructions may be condition codes, immediate data, or a location in the register file, program memory, or data memory.

The SAM8 instruction set supports seven explicit addressing modes. Not all of these addressing modes are available for each instruction:

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Indirect Address (IA)

- Relative Address (RA)

- Immediate (IM)

### REGISTER ADDRESSING MODE (R)

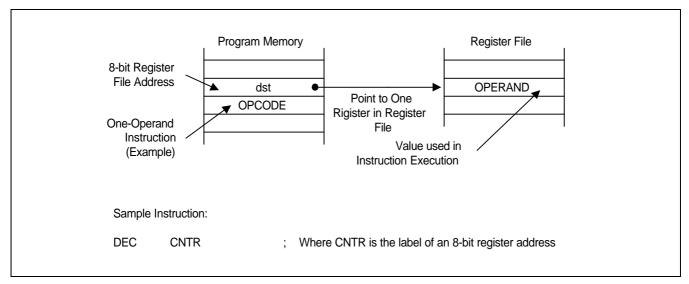

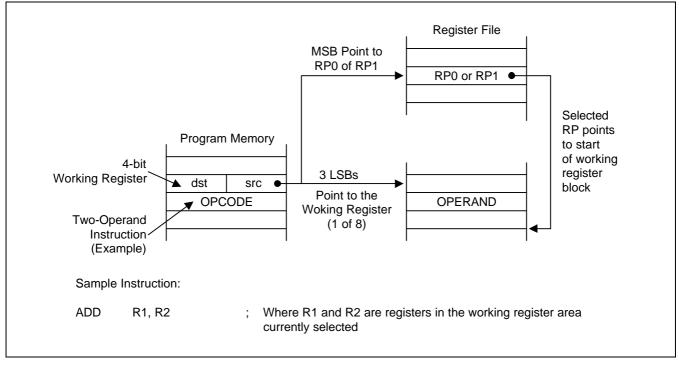

In Register addressing mode, the operand is the content of a specified register or register pair (see Figure 3-1). Working register addressing differs from Register addressing as it uses a register pointer to specify an 8-byte working register space in the register file and an 8-bit register within that space (see Figure 3-2).

Figure 3-1. Register Addressing

Figure 3-2. Working Register Addressing

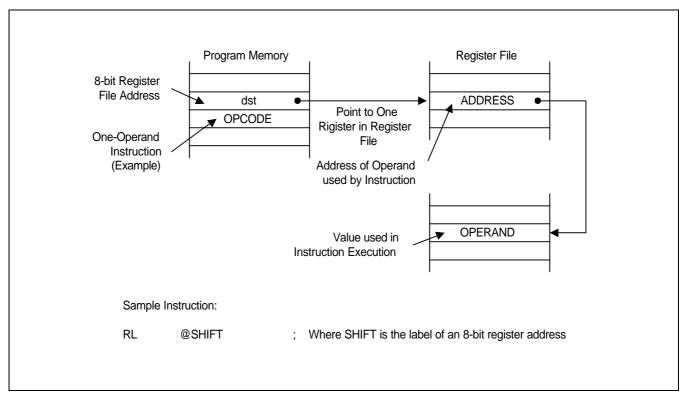

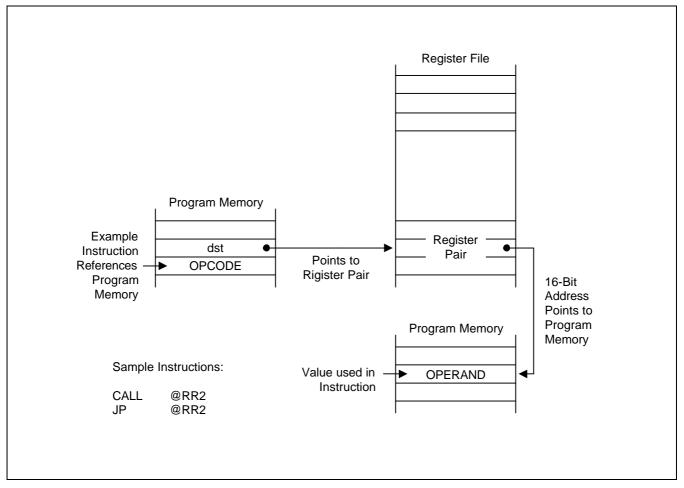

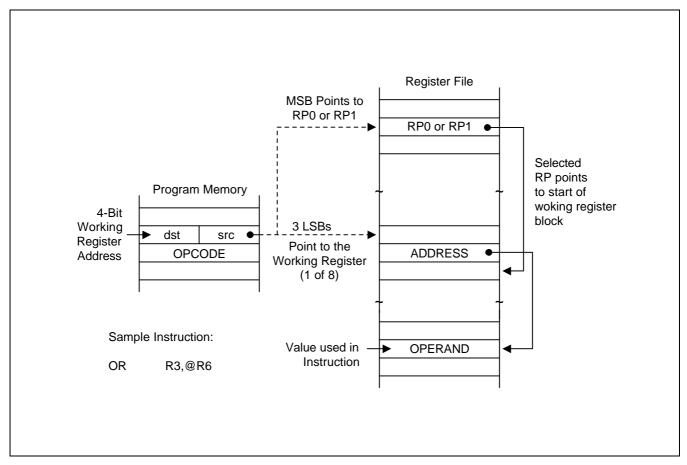

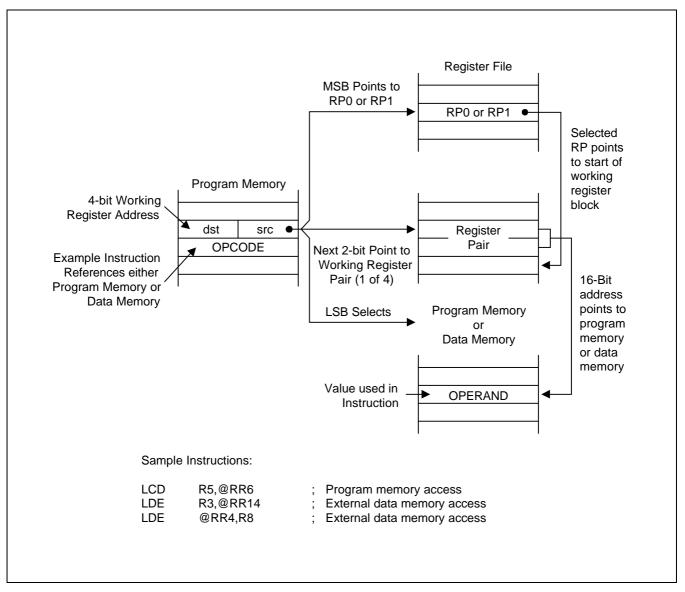

#### **INDIRECT REGISTER ADDRESSING MODE (IR)**

In Indirect Register (IR) addressing mode, the content of the specified register or register pair is the address of the operand. Depending on the instruction used, the actual address may point to a register in the register file, to program memory (ROM), or to an external memory space, if implemented (see Figures 3-3 through 3-6).

You can use any 8-bit register to indirectly address another register. Any 16-bit register pair can be used to indirectly address another memory location. Remember, however, that locations C0H–FFH in set 1 cannot be accessed using Indirect Register addressing mode.

Figure 3-3. Indirect Register Addressing to Register File

# **INDIRECT REGISTER ADDRESSING MODE (Continued)**

Figure 3-4. Indirect Register Addressing to Program Memory

# **INDIRECT REGISTER ADDRESSING MODE (Continued)**

Figure 3-5. Indirect Working Register Addressing to Register File

### INDIRECT REGISTER ADDRESSING MODE (Concluded)

Figure 3-6. Indirect Working Register Addressing to Program or Data Memory

### **INDEXED ADDRESSING MODE (X)**

Indexed (X) addressing mode adds an offset value to a base address during instruction execution in order to calculate the effective operand address (see Figure 3-7). You can use Indexed addressing mode to access locations in the internal register file or in external memory (if implemented). You cannot, however, access locations C0H–FFH in set 1 using Indexed addressing.

In short offset Indexed addressing mode, the 8-bit displacement is treated as a signed integer in the range from – 128 to +127. This applies to external memory accesses only (see Figure 3-8).

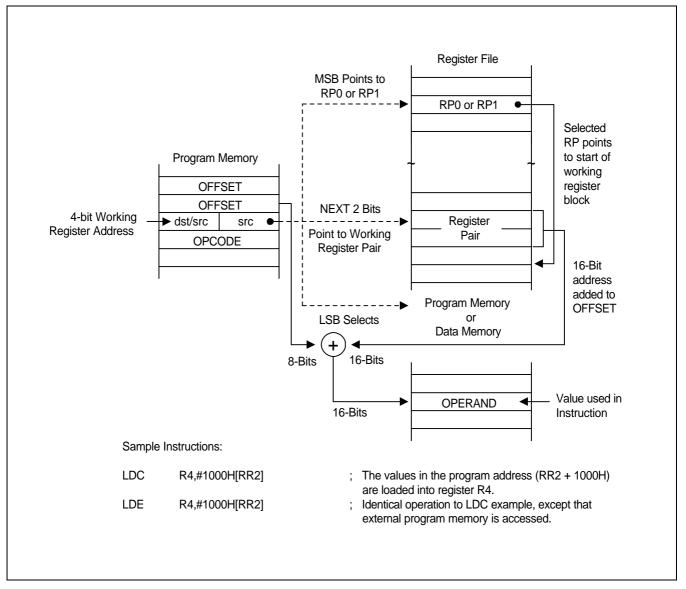

For register file addressing, an 8-bit base address provided by the instruction is added to an 8-bit offset contained in a working register. For external memory access, the base address is stored in the working register pair designated in the instruction. The 8-bit or 16-bit offset given in the instruction is then added to the base address (see Figure 3-9).

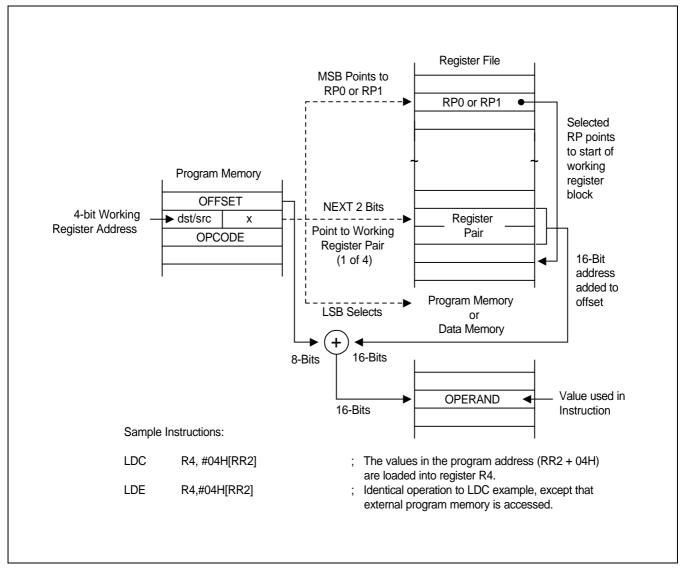

The only instruction that supports Indexed addressing mode for the internal register file is the Load instruction (LD). The LDC and LDE instructions support Indexed addressing mode for internal program memory and for external data memory (if implemented).

Figure 3-7. Indexed Addressing to Register File

# **INDEXED ADDRESSING MODE (Continued)**

Figure 3-8. Indexed Addressing to Program or Data Memory with Short Offset

# **INDEXED ADDRESSING MODE (Concluded)**

Figure 3-9. Indexed Addressing to Program or Data Memory

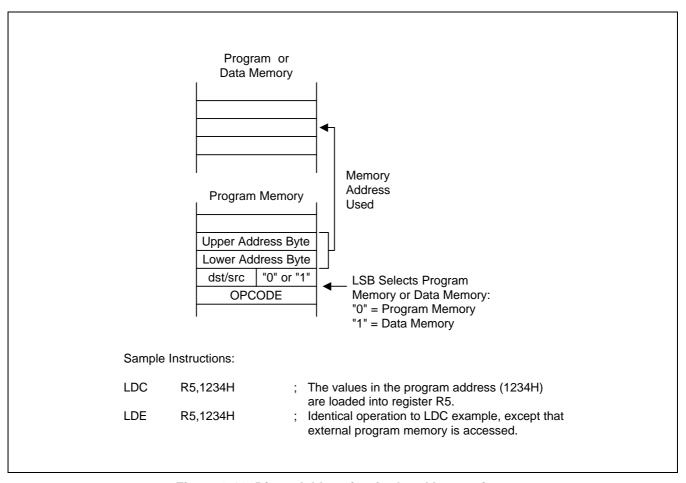

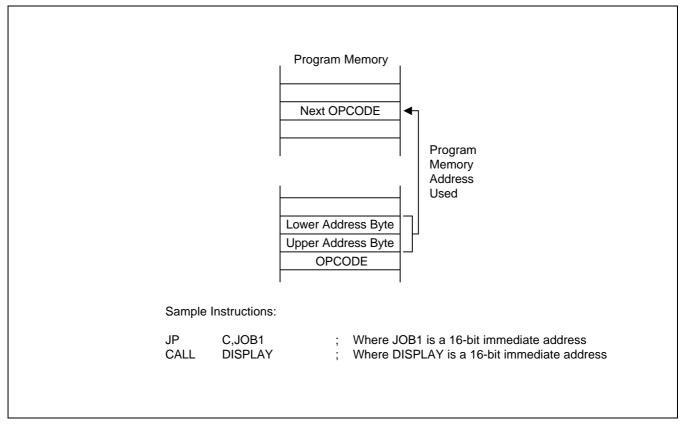

### **DIRECT ADDRESS MODE (DA)**

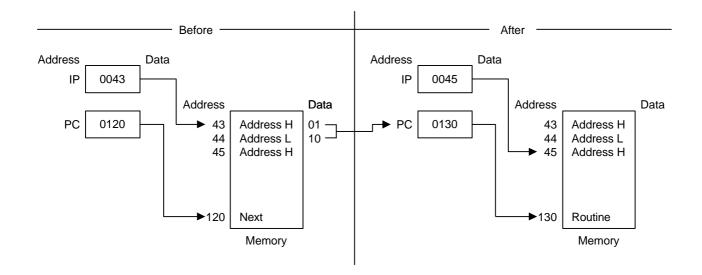

In Direct Address (DA) mode, the instruction provides the operand's 16-bit memory address. Jump (JP) and Call (CALL) instructions use this addressing mode to specify the 16-bit destination address that is loaded into the PC whenever a JP or CALL instruction is executed.

The LDC and LDE instructions can use Direct Address mode to specify the source or destination address for Load operations to program memory (LDC) or to external data memory (LDE), if implemented.

Figure 3-10. Direct Addressing for Load Instructions

# **DIRECT ADDRESS MODE (Continued)**

Figure 3-11. Direct Addressing for Call and Jump Instructions

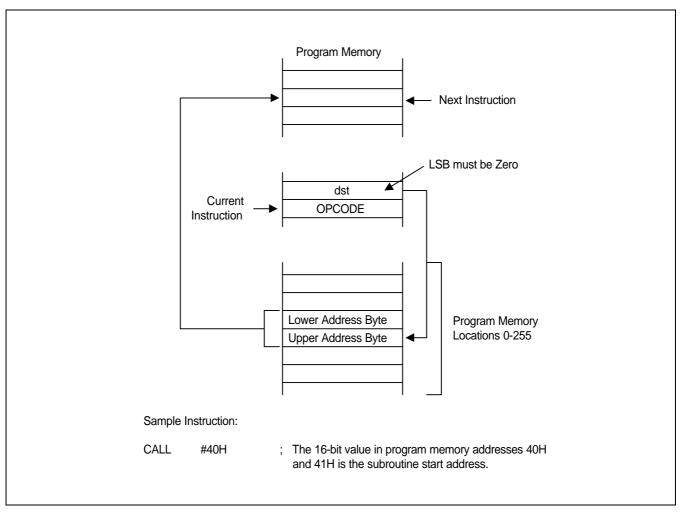

#### **INDIRECT ADDRESS MODE (IA)**

In Indirect Address (IA) mode, the instruction specifies an address located in the lowest 256 bytes of the program memory. The selected pair of memory locations contains the actual address of the next instruction to be executed. Only the CALL instruction can use Indirect Address mode.

Because Indirect Address mode assumes that the operand is located in the lowest 256 bytes of program memory, only an 8-bit address is supplied in the instruction. The upper bytes of the destination address are assumed to be all zeros.

Figure 3-12. Indirect Addressing

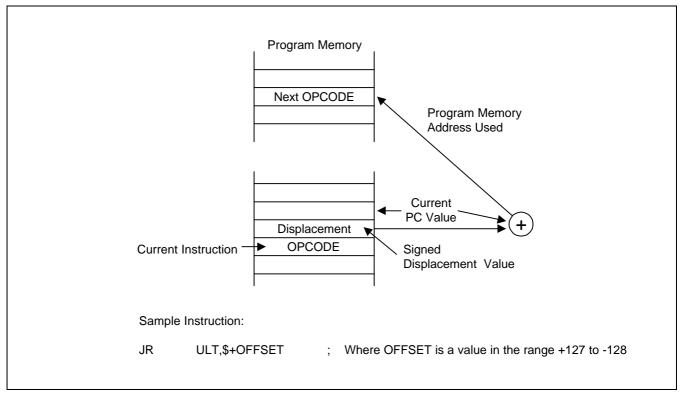

### **RELATIVE ADDRESS MODE (RA)**

In Relative Address (RA) mode, a two's-complement signed displacement between -128 and +127 is specified in the instruction. The displacement value is then added to the current PC value. The result is the address of the next instruction to be executed. Before this addition occurs, the PC contains the address of the next instruction immediately following the current instruction.

Several program control instructions use the Relative Address mode to perform conditional jumps. The instructions that support RA addressing are BTJRF, BTJRT, DJNZ, CPIJE, CPIJNE, and JR.

Figure 3-13. Relative Addressing

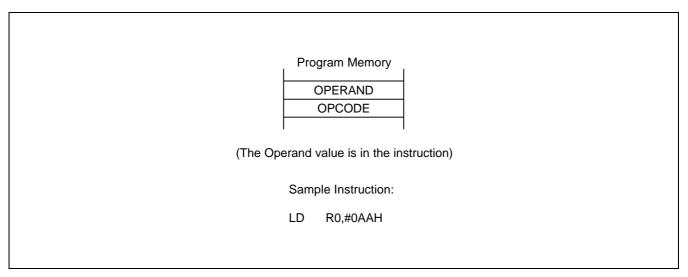

# **IMMEDIATE MODE (IM)**

In Immediate (IM) mode, the operand value used in the instruction is the value supplied in the operand field itself. The operand may be one byte or one word in length, depending on the instruction used. Immediate addressing mode is useful for loading constant values into registers.

Figure 3-14. Immediate Addressing

# **CONTROL REGISTERS**

#### **OVERVIEW**

In this chapter, detailed descriptions of the S3C8639/C863A/C8647 control registers are presented in an easy-to-read format. You can use this chapter as a quick-reference source when writing application programs.

The locations and read/write characteristics of all mapped registers in the S3C8639/C863A/C8647 register files are presented in Tables 4-1, 4-2, and 4-3. The hardware reset values for these registers are described in Chapter 8, "RESET and Power-Down."

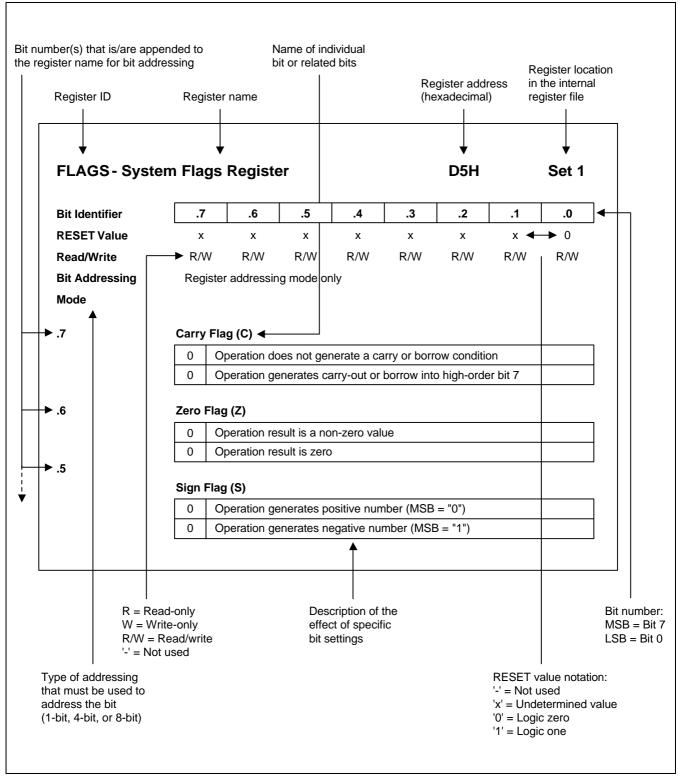

Figure 4-1 illustrates the important features of the standard register description format.

Control register descriptions are arranged in alphabetical order according to register mnemonic. More detailed information about control registers is presented in the context of the specific peripheral hardware descriptions in Part II of this manual.

Table 4-1. Set 1 Registers

| Register Name                   | Mnemonic | Decimal | Hex | R/W      |

|---------------------------------|----------|---------|-----|----------|

| Timer M0 counter register       | TM0CNT   | 208     | D0H | R (note) |

| Timer M0 data register          | TM0DATA  | 209     | D1H | R (note) |

| Timer M0 control register       | TM0CON   | 210     | D2H | R/W      |

| Basic timer control register    | BTCON    | 211     | D3H | R/W      |

| Clock control register          | CLKCON   | 212     | D4H | R/W      |

| System flags register           | FLAGS    | 213     | D5H | R/W      |

| Register pointer 0              | RP0      | 214     | D6H | R/W      |

| Register pointer 1              | RP1      | 215     | D7H | R/W      |

| Stack pointer (high byte)       | SPH      | 216     | D8H | R/W      |

| Stack pointer (low byte)        | SPL      | 217     | D9H | R/W      |

| Instruction pointer (high byte) | IPH      | 218     | DAH | R/W      |

| Instruction pointer (low byte)  | IPL      | 219     | DBH | R/W      |

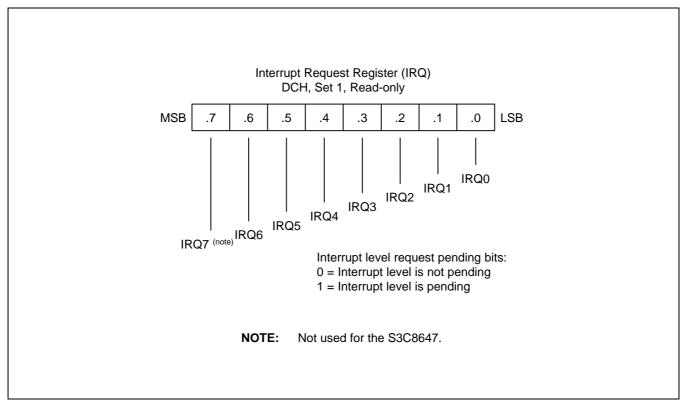

| Interrupt request register      | IRQ      | 220     | DCH | R (note) |

| Interrupt mask register         | IMR      | 221     | DDH | R/W      |

| System mode register            | SYM      | 222     | DEH | R/W      |

| Page pointer register           | PP       | 223     | DFH | R/W      |

**NOTE:** You cannot use a read-only register (TM0CNT, TM0DATA, IRQ) as a destination field for the instructions OR, AND, LD, or LDB.

Table 4-2. Set 1, Bank 0 Registers

| Register Name                              | Mnemonic         | Decimal | Hex | R/W              |

|--------------------------------------------|------------------|---------|-----|------------------|

| Port 0 data register                       | P0               | 224     | E0H | R/W              |

| Port 1 data register (2)                   | P1               | 225     | E1H | R/W              |

| Port 2 data register                       | P2               | 226     | E2H | R/W              |

| Port 3 data register                       | P3               | 227     | E3H | R/W              |

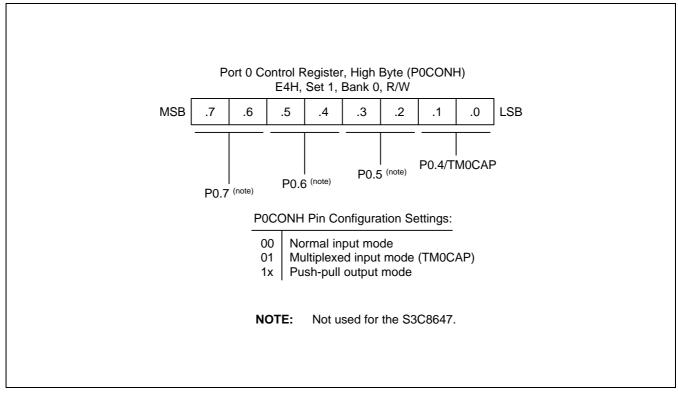

| Port 0 control register (high byte)        | P0CONH           | 228     | E4H | R/W              |

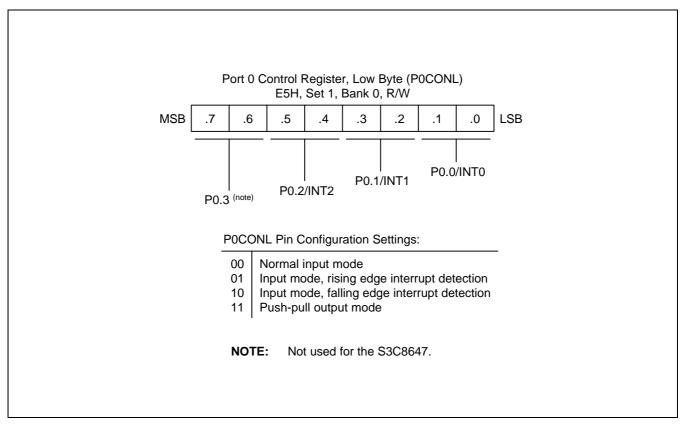

| Port 0 control register (low byte)         | P0CONL           | 229     | E5H | R/W              |

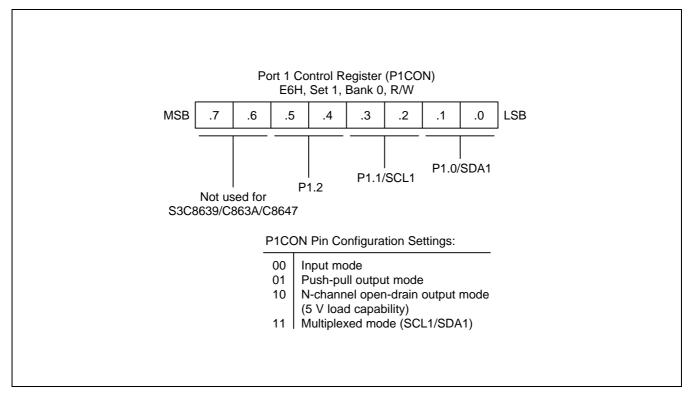

| Port 1 control register (2)                | P1CON            | 230     | E6H | R/W              |

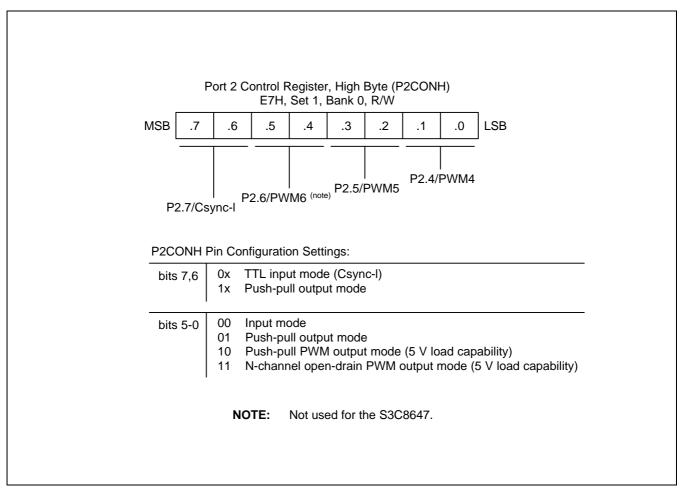

| Port 2 control register (high byte)        | P2CONH           | 231     | E7H | R/W              |

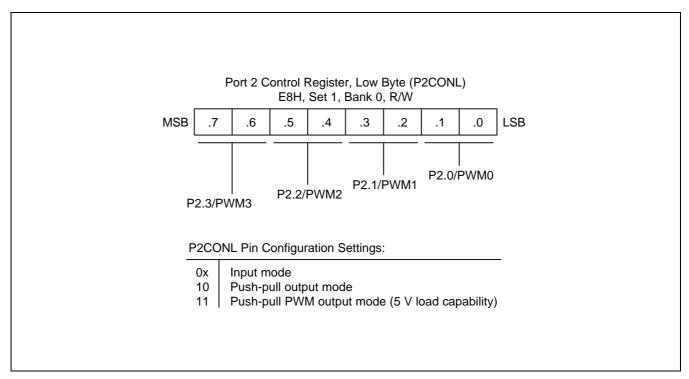

| Port 2 control register (low byte)         | P2CONL           | 232     | E8H | R/W              |

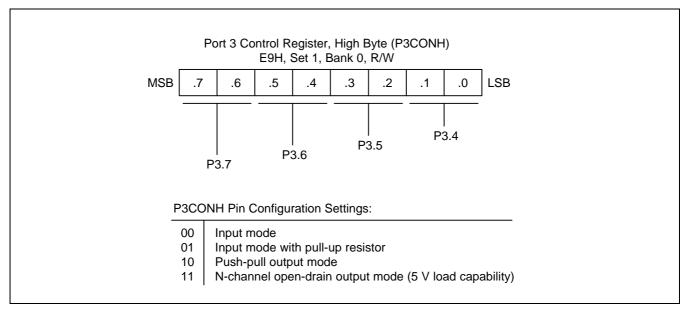

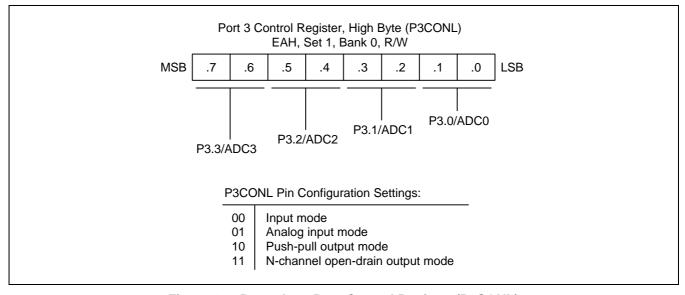

| Port 3 control register (high byte)        | P3CONH           | 233     | E9H | R/W              |

| Port 3 control register (low byte)         | P3CONL           | 234     | EAH | R/W              |

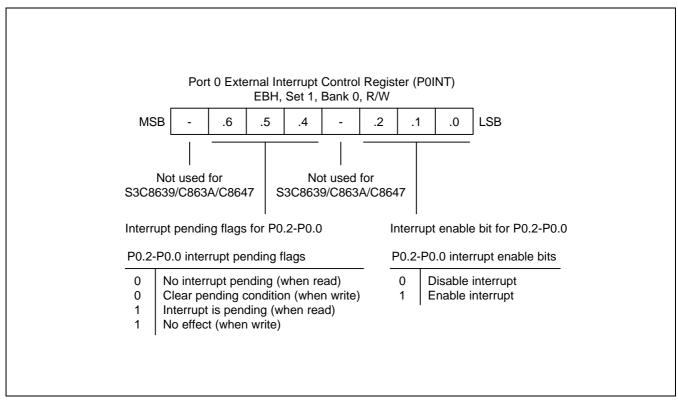

| Port 0 external interrupt control register | POINT            | 235     | EBH | R/W              |

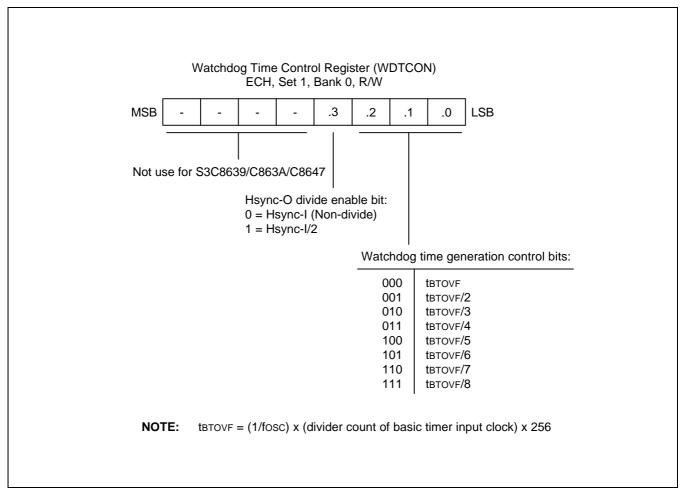

| Watchdog time control register             | WDTCON           | 236     | ECH | R/W              |

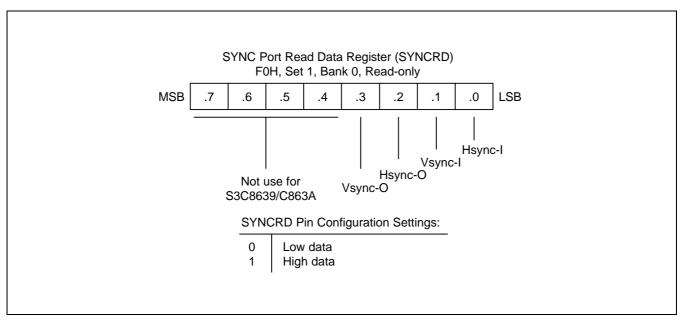

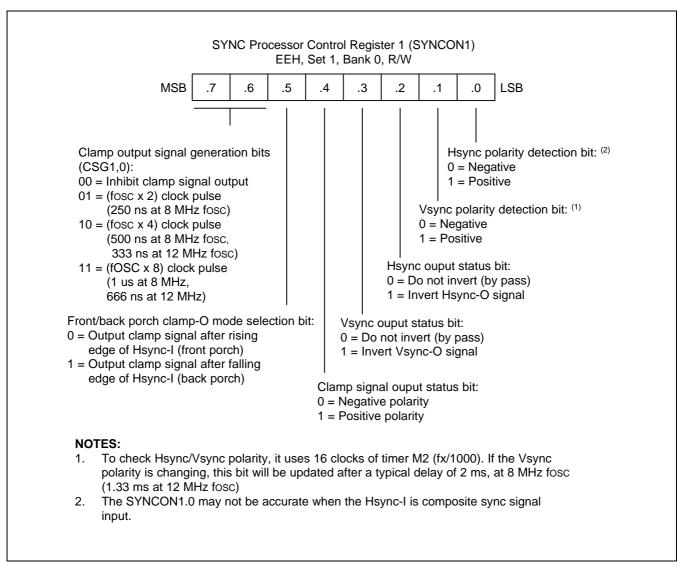

| Sync control register 0                    | SYNCON0          | 237     | EDH | R/W              |

| Sync control register 1                    | SYNCON1          | 238     | EEH | R/W              |

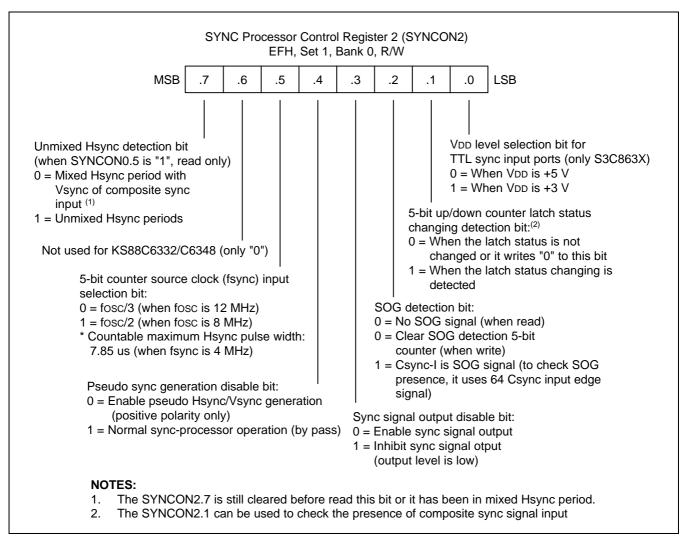

| Sync control register 2                    | SYNCON2          | 239     | EFH | R/W              |

| Sync port read data register               | SYNCRD           | 240     | F0H | R <sup>(1)</sup> |

| Timer M1 counter register (high byte)      | TM1CNTH          | 241     | F1H | R <sup>(1)</sup> |

| Timer M1 counter register (low byte)       | TM1CNTL          | 242     | F2H | R <sup>(1)</sup> |

| Timer M1 data register (high byte)         | TM1DATAH         | 243     | F3H | R <sup>(1)</sup> |

| Timer M1 data register (low byte)          | TM1DATAL         | 244     | F4H | R <sup>(1)</sup> |

| Timer M1 control register                  | TM1CON           | 245     | F5H | R/W              |

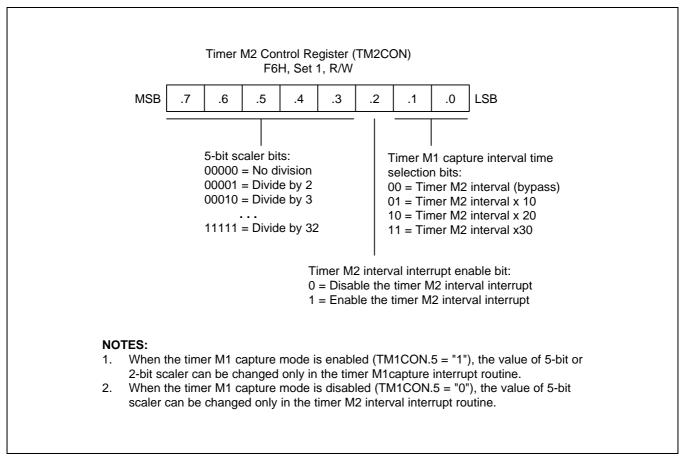

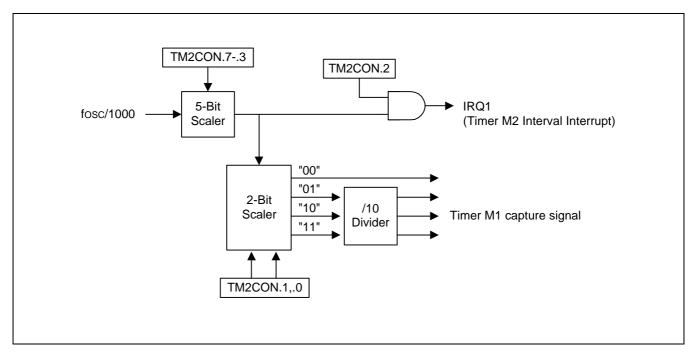

| Timer M2 control register                  | TM2CON           | 246     | F6H | R/W              |

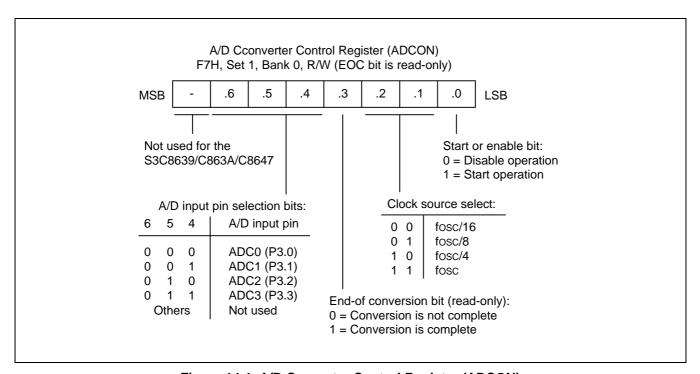

| A/D converter control register             | ADCON            | 247     | F7H | R/W              |

| A/D converter data register                | ADDATA           | 248     | F8H | R <sup>(1)</sup> |

| Pseudo Hsync generation register           | PHGEN            | 249     | F9H | R/W              |

| Pseudo Vsync generation register           | PVGEN            | 250     | FAH | R/W              |

| Stop control register                      | STOPCON          | 251     | FBH | R/W              |

| Locat                                      | ion FCH is not m | apped   |     |                  |

| Basic timer counter register               | BTCNT            | 253     | FDH | R <sup>(1)</sup> |

| External memory timing register            | EMT              | 254     | FEH | R/W              |

| Interrupt priority register                | IPR              | 255     | FFH | R/W              |

#### NOTES:

- 1. You cannot use a read-only register (SYNCRD, TM1CNTH, TM1TNCL, TM1DATAH, TM1DATAL, ADDATA, BTCNT) as a destination field for the instructions OR, AND, LD, or LDB.

- 2. Not used for the S3C8647.

Table 4-3. Set 1, Bank 1 Registers

| Register Name                             | Mnemonic | Decimal | Hex | R/W              |  |

|-------------------------------------------|----------|---------|-----|------------------|--|

| PWM 0 data register                       | PWM0     | 224     | E0H | R/W              |  |

| PWM 1 data register                       | PWM1     | 225     | E1H | R/W              |  |

| PWM 2 data register                       | PWM2     | 226     | E2H | R/W              |  |

| PWM 3 data register                       | PWM3     | 227     | E3H | R/W              |  |

| PWM 4 data register                       | PWM4     | 228     | E4H | R/W              |  |

| PWM 5 data register                       | PWM5     | 229     | E5H | R/W              |  |

| PWM 6 data register <sup>(2)</sup>        | PWM6     | 230     | E6H | R/W              |  |

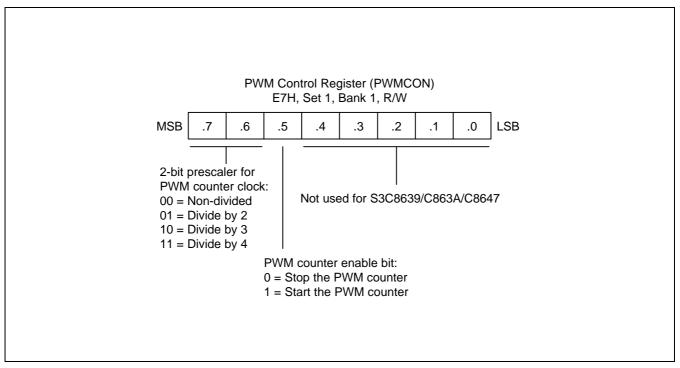

| PWM control register                      | PWMCON   | 231     | E7H | R/W              |  |

| PWM counter register                      | PWMCNT   | 232     | E8H | R <sup>(1)</sup> |  |

| DDC control register                      | DCON     | 233     | E9H | R/W              |  |

| DDC address register 0                    | DAR0     | 234     | EAH | R/W              |  |

| DDC clock control register                | DCCR     | 235     | EBH | R/W              |  |

| DDC control/status register 0             | DCSR0    | 236     | ECH | R/W              |  |

| DDC control/status register 1             | DCSR1    | 237     | EDH | R/W              |  |

| DDC address register 1                    | DAR1     | 238     | EEH | R/W              |  |

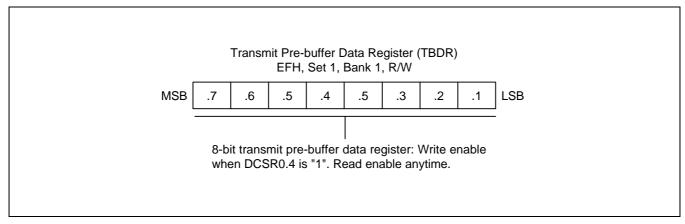

| Transmit prebuffer data register          | TBDR     | 239     | EFH | R/W              |  |

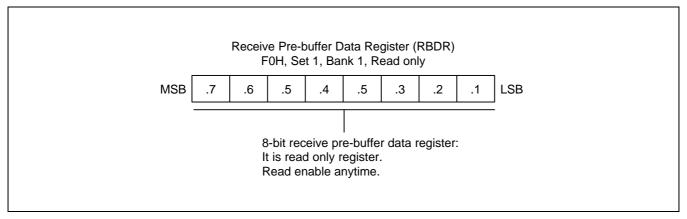

| Receive prebuffer data register           | RBDR     | 240     | F0H | R <sup>(1)</sup> |  |

| DDC data shift register                   | DDSR     | 241     | F1H | R/W              |  |

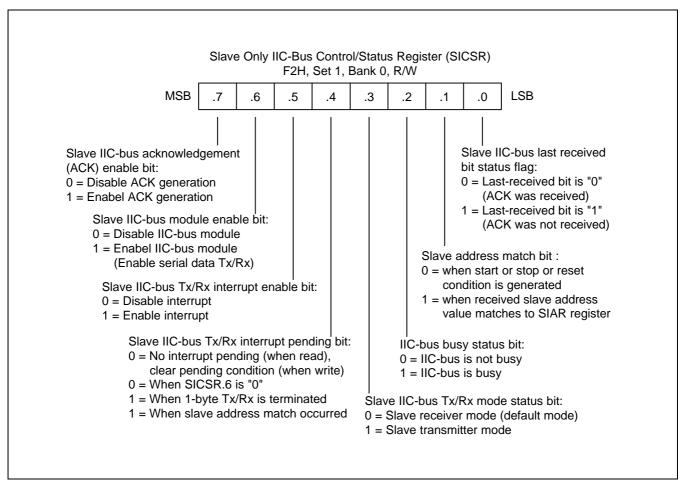

| Slave IIC-Bus control/status register (2) | SICSR    | 243     | F2H | R/W              |  |

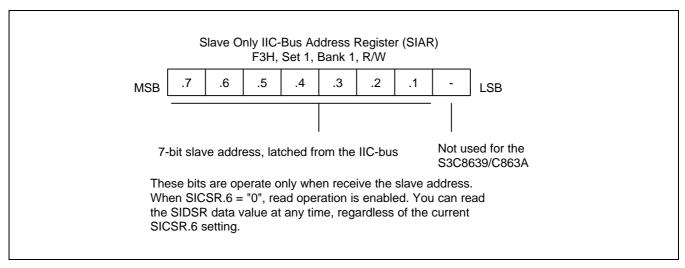

| Slave IIC-Bus address register (2)        | SIAR     | 242     | F3H | R/W              |  |

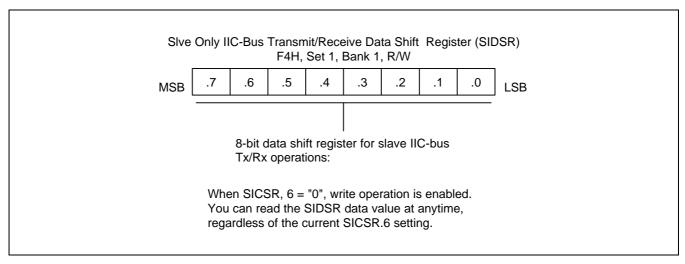

| Slave IIC-Bus data shift register (2)     | SIDSR    | 244     | F4H | R/W              |  |

| Locations F5H–FFH are not mapped          |          |         |     |                  |  |

# NOTES:

- 1. You cannot use a read-only register (PWMCNT, RBDR) as a destination field for the instructions OR, AND, LD, or LDB.

- 2. Not used for the S3C8647.

Figure 4-1. Register Description Format

# **ADCON** — A/D Converter Control Register

F7H

Set 1, Bank 0

Bit Identifier

RESET Value

Read/Write

| .7 | .6  | .5  | .4  | .3 | .2  | .1  | .0  |

|----|-----|-----|-----|----|-----|-----|-----|

| _  | 0   | 0   | 0   | 0  | 0   | 0   | 0   |

| _  | R/W | R/W | R/W | R  | R/W | R/W | R/W |

**Addressing Mode**

Register addressing mode only

.7

Not used for the S3C8639/C863A/C8647

#### .6 and .4

#### **Analog Input Pin Selection Bits**

| 0 | 0      | 0 | ADC0 (Port 3.0) |

|---|--------|---|-----------------|

| 0 | 0      | 1 | ADC1 (Port 3.1) |

| 0 | 1      | 0 | ADC2 (Port 3.2) |

| 0 | 1      | 1 | ADC3 (Port 3.3) |

| ( | Others |   | Not used        |

#### .3

# **End-of Conversion (EOC) Flag (read-only)**

| 0 | Conversion not complete |  |  |  |  |

|---|-------------------------|--|--|--|--|

| 1 | Conversion is complete  |  |  |  |  |

### .2 and .1

### **Clock Source Selection Bits**

| 0 | 0 | f <sub>OSC</sub> /16 |

|---|---|----------------------|

| 0 | 1 | f <sub>OSC</sub> /8  |

| 1 | 0 | f <sub>osc</sub> /4  |

| 1 | 1 | fosc                 |

#### .0

#### Start or Enable Bit

| 0 | Disable operation |

|---|-------------------|

| 1 | Start operation   |

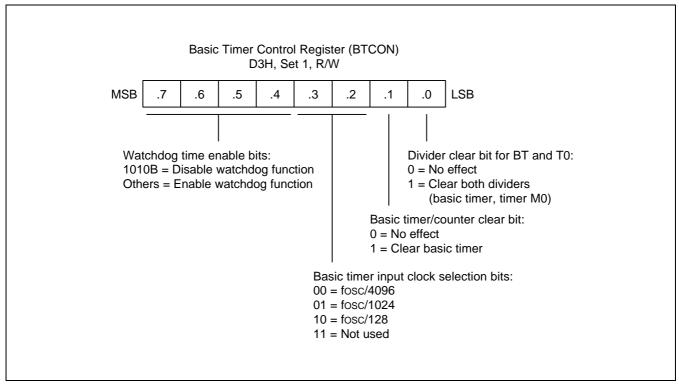

# ${\color{red}\textbf{BTCON}} - {\color{blue}\textbf{Basic Timer Control Register}}$

D3H

Set 1

**Bit Identifier**

**RESET Value**

Read/Write

**Addressing Mode**

| .7  | .6  | .5  | .4  | .3  | .2  | .1  | .0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W |

Register addressing mode only

### .7-.4 Watchdog Timer Function Disable Bits

| 1      | 0 | 1 | 0                              | Disable watchdog timer function |  |  |

|--------|---|---|--------------------------------|---------------------------------|--|--|

| Others |   |   | Enable watchdog timer function |                                 |  |  |

### .3 and .2 Basic Timer Input Clock Selection Bits

| 0 | 0 | f <sub>OSC</sub> /4096                                |

|---|---|-------------------------------------------------------|

| 0 | 1 | f <sub>OSC</sub> /1024                                |

| 1 | 0 | f <sub>OSC</sub> /128                                 |

| 1 | 1 | Invalid setting; not used for the S3C8639/C863A/C8647 |

#### Basic Timer Counter Clear Bit (1)

| 0 | No effect                           |

|---|-------------------------------------|

| 1 | Clear the basic timer counter value |

# Clock Frequency Divider Clear Bit for Basic Timer and Timer M0 (2)

| 0 | No effect                                         |

|---|---------------------------------------------------|

| 1 | Clear basic timer and timer M0 frequency dividers |

#### NOTES:

.1

.0

- 1. When you write a "1" to BTCON.1, the basic timer counter value is cleared to "00H". Immediately after the write operation, the BTCON.1 value is automatically cleared to "0".

- 2. When you write a "1" to BTCON.0, the corresponding frequency divider is cleared to "00H". Immediately after the write operation, the BTCON.0 value is automatically cleared to "0".

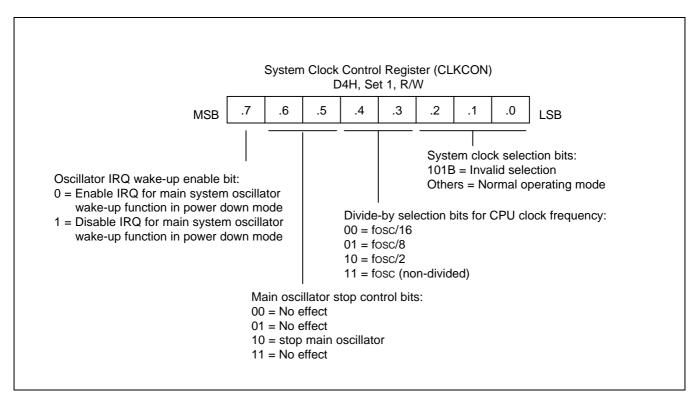

# ${\color{red}\textbf{CLKCON}} - {\color{blue}\textbf{System Clock Control Register}}$

D4H

Set 1

Bit Identifier

RESET Value Read/Write

.7

**Addressing Mode**

| .7  | .6  | .5  | .4  | .3  | .2  | .1  | .0  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W |

Register addressing mode only

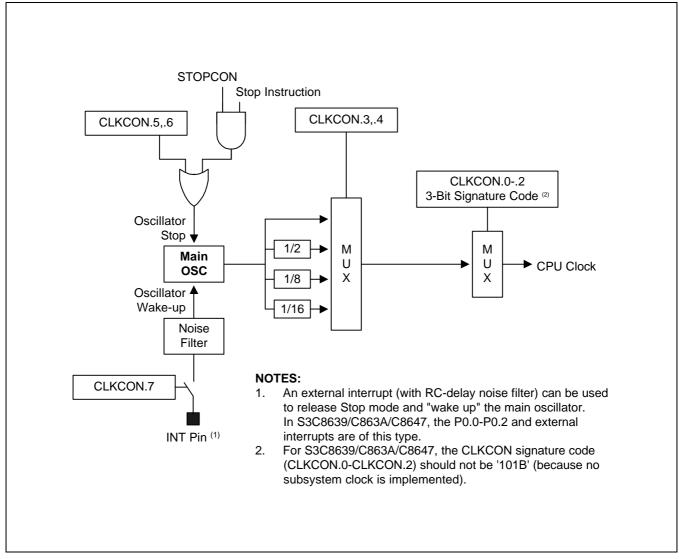

#### Oscillator IRQ Wake-up Function Enable Bit

| 0 | Enable IRQ for main system oscillator wake-up in power-down mode  |

|---|-------------------------------------------------------------------|

| 1 | Disable IRQ for main system oscillator wake-up in power-down mode |

### .6 and .5 Main Oscillator Stop Control Bits

| 0 | 0 | No effect            |

|---|---|----------------------|

| 0 | 1 | No effect            |

| 1 | 0 | Stop main oscillator |

| 1 | 1 | No effect            |

# .4 and .3 CPU Clock (System Clock) Selection Bits (1)

| 0 | 0 | Divide by 16 (f <sub>OSC</sub> /16)       |

|---|---|-------------------------------------------|

| 0 | 1 | Divide by 8 (f <sub>OSC</sub> /8)         |

| 1 | 0 | Divide by 2 (f <sub>OSC</sub> /2)         |

| 1 | 1 | Non-divided clock (f <sub>OSC</sub> ) (2) |

#### .2–.0 Subsystem Clock Selection Bits (3)

| 1                                      | 0 | 1 | Invalid setting for S3C8639/C863A/C8647 |

|----------------------------------------|---|---|-----------------------------------------|

| Others Select main system clock (MCLK) |   |   | Select main system clock (MCLK)         |

#### NOTES:

- 1. After a reset, the slowest clock (divided by 16) is selected as the system clock. To select faster clock speeds, load the appropriate values to CLKCON.3 and CLKCON.4.

- 2. If the oscillator frequency is higher than 12 MHz, this selection is invalid.

- 3. These selection bits are required only for systems that have a main clock and a subsystem clock. S3C8639/C863A/C8647 use only the main oscillator clock circuit. For this reason, the setting "101B" is invalid.

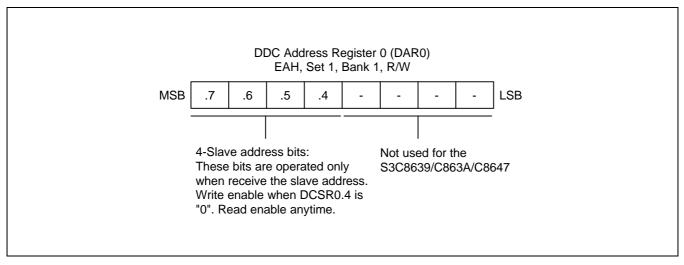

# DAR0 — DDC Address Register 0

**EAH**

Set 1, Bank 1

.0

**Bit Identifier**

**RESET Value**

**Addressing Mode**

1 R/W

.7

1 R/W

.5

0 R/W

.4

.2 .3

.1

Read/Write

R/W Register addressing mode only

.6

0

.7-.4

#### **4-Slave Address Bits**

These bits are operate only when receive the slave address. Read enable anytime. Write enable when DCSR0.4 is "0".

.3-.0

Not used for the S3C8639/C863A/C8647

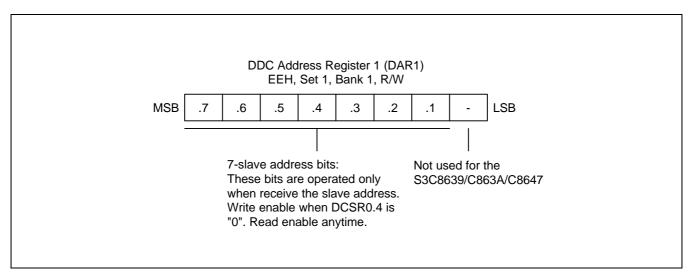

# DAR1 — DDC Address Register 1

EEH

.2

Set 1, Bank 1

.0

**Bit Identifier**

**RESET Value**

Read/Write

**Addressing Mode**

.7 .6 .5 Х Х Х

R/W

Register addressing mode only

Х R/W

R/W

.4

Х R/W

.3

Х Х R/W

R/W

.1

7-Slave Address Bits .7-.1

R/W

These bits are operate only when receive the slave address. Read enable anytime.

Write enable when DCSR0.4 is "0".

.0

Not used for the S3C8639/C863A/C8647

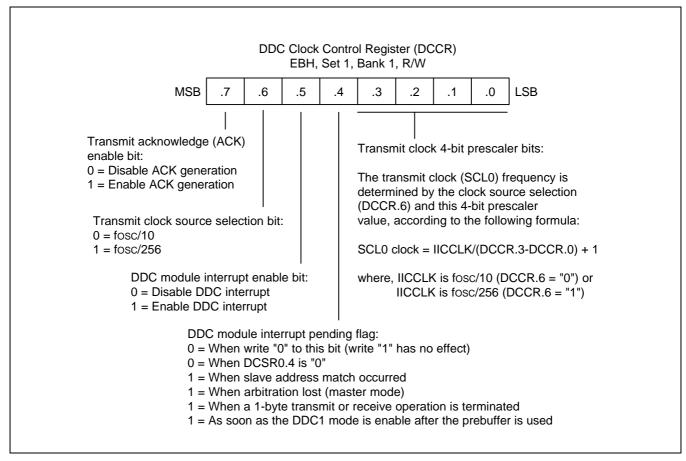

# ${\color{red} \textbf{DCCR}} - {\color{blue} \textbf{DDC Clock Control Register}}$

EBH Set 1, Bank 1

Bit Identifier

RESET Value

Read/Write

Addressing Mode

| _        |           | _          | 1 4 |     |     |     |     |

|----------|-----------|------------|-----|-----|-----|-----|-----|

| ./       | .6        | .5         | .4  | .3  | .2  | .1  | .0  |

| 0        | 0         | 0          | 0   | 1   | 1   | 1   | 1   |

| R/W      | R/W       | R/W        | R/W | R/W | R/W | R/W | R/W |

| Dogistor | ddroooina | برامه مامم |     |     |     |     |     |

dressing Mode Register addressing mode only

.7 Transmit acknowledgement enable mode when this bit is "1".

.6 Tx Clock Selection Bit

| 0 | f <sub>OSC</sub> /10  |

|---|-----------------------|

| 1 | f <sub>OSC</sub> /256 |

.5 DDC Module Interrupt Enable Bit

| 0 | Disable interrupt |

|---|-------------------|

| 1 | Enable interrupt  |

.4 DDC Module Interrupt Pending Bit

| 0 | When write "0" to this bit (write "1" has no effect)            |

|---|-----------------------------------------------------------------|

| 0 | When DCSR0.4 is "0"                                             |

| 1 | When slave address match occurred                               |

| 1 | When arbitration lost (master mode)                             |

| 1 | When an 1-byte transmit or receive operation is terminated      |

| 1 | As soon as the DDC1 mode is enabled after the prebuffer is used |

.3–.0 Transmit Clock 4-Bit Prescaler Bits (CCR3–CCR0)

SCL clock = IICLK/(CCR < 3: 0 > +1) where, IICLK is  $f_{OSC}/10$  when DCCR.6 is "0" IICLK is  $f_{OSC}/256$  when DCCR.6 is "1"

.0 0 R/W

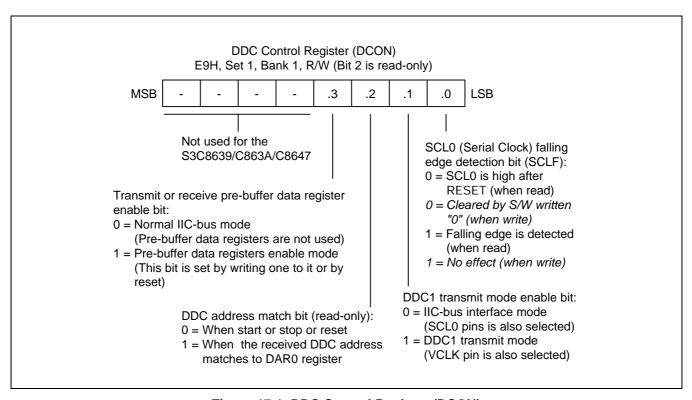

# **DCON** — DDC Control Register

E9H Set 1, Bank 1

| Bit Identifier  | .7         | .6         | .5        | .4 | .3  | .2  | .1  |

|-----------------|------------|------------|-----------|----|-----|-----|-----|

| RESET Value     | _          | -          | _         | -  | 1   | 0   | 0   |

| Read/Write      | _          | _          | _         | _  | R/W | R/W | R/W |

| Addressing Mode | Register a | addressing | mode only |    |     |     |     |

.7-.4 Not used for the S3C8639/C863A/C8647.

# .3 Tx/Rx Pre-Buffer Data Registers Enable Bit

| 0 | Normal IIC-bus mode (Pre-buffer data registers are not used.)                        |  |  |  |

|---|--------------------------------------------------------------------------------------|--|--|--|

| 1 | Pre-buffer data registers enable mode. This bit is set by writing "1" or by a reset. |  |  |  |

.2 DDC Address Match Bit

| 0 | When start or stop or reset                       |

|---|---------------------------------------------------|

| 1 | When DDC received address matchs to DAR0 register |

.1 DDC1 Tx Mode Enable Bit

| 0 | IIC-bus interface mode (SCL pin is also selected) |

|---|---------------------------------------------------|

| 1 | DDC1 Tx mode (VCLK pin is also selected)          |

.0 SCL Pin Falling Edge Detection Flag (note)

| 0 | SCL pin level remains high after a reset (when read)                                                                                                                                                                                                                             |

|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 | This bit can be cleared by S/W written "0" (when write)                                                                                                                                                                                                                          |

| 1 | Falling edge can be detected at the SCL pin after a reset or after this flag is cleared by software (when read) After start condition, the clock source of DDC module automatically charges from VCLK (Vsync-I) to SCL0 (DCON.1 is "1" to "0") and slave address match possible. |

| 1 | No effect (when write)                                                                                                                                                                                                                                                           |

**NOTE:** When DDC interrupt is occurred, the SCL line is not pull-down in the DDC1 mode and Tx/Rx pre-buffer data registers enable bit, DCON.3 is "1" (only slave mode).

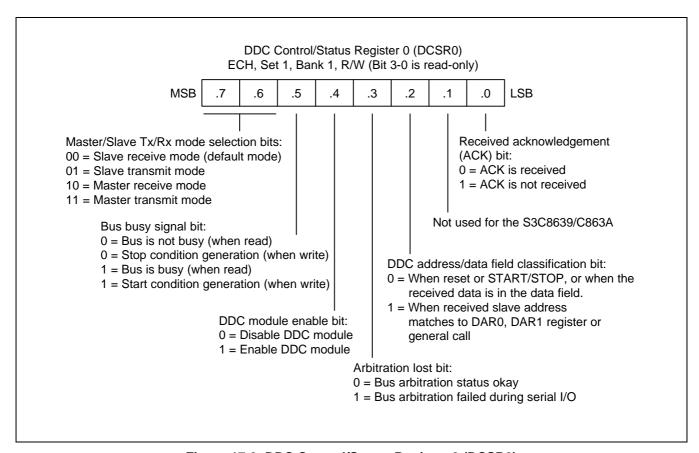

|               | C Con                | roi/s                                                | Status Re                                                                                                                                     | egister u                                                             |                                                  |            | ECH          | Set 1      | , Bank  |  |

|---------------|----------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------|------------|--------------|------------|---------|--|

| Identifier    |                      | .7                                                   | .6                                                                                                                                            | .5                                                                    | .4                                               | .3         | .2           | .1         | .0      |  |

| SET Value     |                      | 0                                                    | 0                                                                                                                                             | 0                                                                     | 0                                                | 0          | 0            | _          | 0       |  |

| ad/Write      | R                    | /W                                                   | R/W                                                                                                                                           | R/W                                                                   | R/W                                              | R          | R            | _          | R       |  |

| dressing Mode | Reg                  | ister a                                              | addressing                                                                                                                                    | mode only                                                             | ′                                                |            |              |            |         |  |

| .6            | Mas                  | Master/Slave, Tx/Rx Mode Selection Bits              |                                                                                                                                               |                                                                       |                                                  |            |              |            |         |  |

|               | 0                    | 0                                                    | Slave rec                                                                                                                                     | eiver mode                                                            | e (Default m                                     | ode)       |              |            |         |  |

|               | 0                    | 1                                                    | Slave trai                                                                                                                                    | nsmitter m                                                            | ode                                              |            |              |            |         |  |

|               | 1                    | 0                                                    | Master re                                                                                                                                     | ceiver mod                                                            | de                                               |            |              |            |         |  |

|               | 1                    | 1                                                    | Master tra                                                                                                                                    | ansmitter n                                                           | node                                             |            |              |            |         |  |

|               | Bus                  | Bus                                                  | y Bit                                                                                                                                         |                                                                       |                                                  |            |              |            |         |  |

|               | 0                    | IIC-l                                                | ous is not b                                                                                                                                  | usy (when                                                             | read), stop                                      | condition  | generation ( | when write | e)      |  |

|               | _                    |                                                      | IIC-bus is not busy (when read), stop condition generation (when write)  IIC-bus is busy (when read), start condition generation (when write) |                                                                       |                                                  |            |              |            |         |  |

|               | 1                    | IIC-k                                                | ous is busy                                                                                                                                   | (when rea                                                             | id), start con                                   | dition gen | eration (whe | en write)  |         |  |

|               | DDC                  | C Mod                                                | dule Enabl                                                                                                                                    | e Bit                                                                 | d), start con                                    | dition gen | eration (whe | en write)  |         |  |

|               | <b>DD</b> (          | Disa                                                 | dule Enabl                                                                                                                                    | e Bit                                                                 | d), start con                                    | dition gen | eration (whe | en write)  |         |  |

|               | DDC                  | Disa                                                 | dule Enabl                                                                                                                                    | e Bit                                                                 | d), start con                                    | dition gen | eration (whe | en write)  |         |  |

|               | <b>DDC</b> 0 1       | Disa<br>Ena                                          | dule Enabl                                                                                                                                    | e Bit<br>nodule                                                       | d), start con                                    | dition gen | eration (whe | en write)  |         |  |

|               | <b>DDC</b> 0 1       | Disa<br>Ena                                          | dule Enabl<br>able DDC n<br>ble DDC m                                                                                                         | e Bit<br>nodule<br>nodule                                             |                                                  | dition gen | eration (whe | en write)  |         |  |

|               | 0<br>1               | Disa<br>Ena<br>itratio                               | dule Enablable DDC mon Lost Bit arbitration                                                                                                   | e Bit<br>nodule<br>nodule<br>t<br>status oka                          |                                                  |            | eration (whe | en write)  |         |  |

|               | 0<br>1<br><b>Arb</b> | Disa<br>Ena<br>itratio                               | dule Enablable DDC mon Lost Bit arbitration                                                                                                   | e Bit<br>nodule<br>nodule<br>t<br>status oka                          | у                                                |            | eration (whe | en write)  |         |  |

|               | 0<br>1<br><b>Arb</b> | Disa<br>Ena<br>itration<br>Bus<br>Bus                | dule Enablable DDC mon Lost Bit arbitration                                                                                                   | e Bit nodule dodule t status oka                                      | y<br>ng serial I/O                               |            | eration (whe | en write)  |         |  |

|               | 0<br>1<br><b>Arb</b> | Disa<br>Ena<br>itration<br>Bus<br>Bus<br>C Add       | dule Enablable DDC mon Lost Bit arbitration arbitration                                                                                       | e Bit nodule dodule status oka failed duri                            | y<br>ng serial I/O                               |            |              |            | data is |  |

|               | DDC 0 1 Arb 0 1      | Disa<br>Ena<br>itration<br>Bus<br>Bus<br>C Add       | dule Enable able DDC m ble DDC m bn Lost Bit arbitration arbitration lress/Data en reset or se data field                                     | e Bit nodule odule t status oka failed duri classifica start/stop od. | y<br>ng serial I/O                               | generated  | , or when th | e received | data is |  |

|               | DDC 0 1 DDC 0 1      | Disa<br>Ena<br>itration<br>Bus<br>Bus<br>Wheelin the | dule Enable able DDC m ble DDC m bn Lost Bit arbitration arbitration lress/Data en reset or se data field                                     | e Bit nodule todule status oka failed duri classifica start/stop od.  | y<br>ng serial I/O<br>tion Bit<br>condition is o | generated  | , or when th | e received | data is |  |

**NOTE:** Bits 3–0 are read only.

0

1

ACK is received

ACK is not received

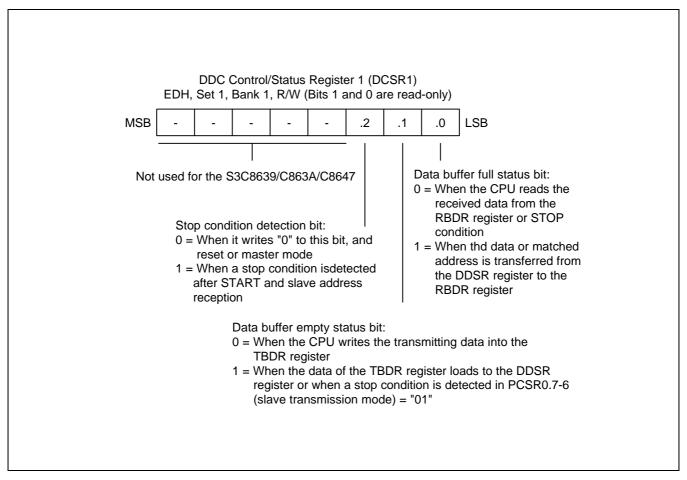

# DCSR1 — DDC Control/Status Register 1

EDH Set 1, Bank 1

| Bit Identifier         |

|------------------------|

| RESET Value            |

| Read/Write             |

| <b>Addressing Mode</b> |

| .7 | .6 | .5 | .4 | .3 | .2  | .1  | .0  |

|----|----|----|----|----|-----|-----|-----|

| _  | -  | _  | _  | _  | 0   | 1   | 0   |

| _  | _  | _  | _  | _  | R/W | R/W | R/W |

Register addressing mode only

.7–.3

Not used for the S3C8639/C863A/C8647

.2

# **Stop Condition Detection Bit**

| 0 | When it writes "0" to this bit, it is reset or master mode.               |

|---|---------------------------------------------------------------------------|

| 1 | When a STOP condition is detected after START and slave address reception |

.1

# **Data Buffer Empty Status Bit**

| 0 | When the CPU writes the transmitted data into the TBDR register            |

|---|----------------------------------------------------------------------------|

| 1 | When the data of the TBDR register is loads to the DDSR register or when a |

|   | STOP condition is detected in DCSR0.76 (slave transmitter mode) = "01"     |

.0

# **Data Buffer Full Status Bit**

| 0 | When the CPU reads the received data from the RBDR register or STOP condition               |

|---|---------------------------------------------------------------------------------------------|

| 1 | When the data or matched address is transferred from the DDSR register to the RBDR register |

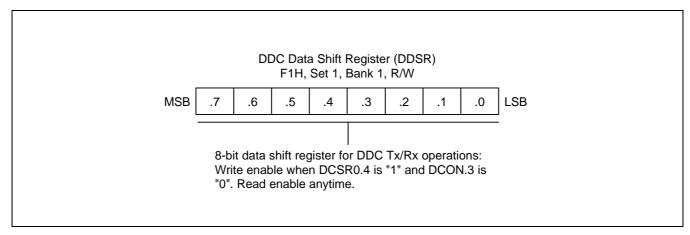

| DDSR — DDC Data Shift | t Register |

|-----------------------|------------|

|-----------------------|------------|

F1H Set 1, Bank 1

Bit Identifier

RESET Value

Read/Write

Addressing Mode

| .7         | .6         | .5        | .4  | .3  | .2  | .1  | .0  |

|------------|------------|-----------|-----|-----|-----|-----|-----|

| X          | x          | X         | Х   | Х   | х   | Х   | х   |

| R/W        | R/W        | R/W       | R/W | R/W | R/W | R/W | R/W |

| Register a | addressing | mode only |     |     |     |     |     |

.7-.0

Write enable when DCSR0.4 is "1" and DCON.3 is "0". Read enable anytime.

# **EMT** — External Memory Timing Register

FEH Set 1, Bank 0

| Bit Identifier  |

|-----------------|

| RESET Value     |

| Read/Write      |

| Addressing Mode |

| .7  | .6  | .5  | .4  | .3  | .2  | .1  | .0 |

|-----|-----|-----|-----|-----|-----|-----|----|

| 0   | 1   | 1   | 1   | 1   | 1   | 0   | _  |

| R/W | -  |

Register addressing mode only

### .7 External WAIT Input Function Enable Bit

| 0 | Disable WAIT input function for external device |

|---|-------------------------------------------------|

| 1 | Enable WAIT input function for external device  |

# .6 Slow Memory Timing Enable Bit

| 0 | Disable slow memory timing |

|---|----------------------------|

| 1 | Enable slow memory timing  |

#### .5 and .4 Program Memory Automatic Wait Control Bits

| 0 | 0 | No wait (Normal Operation) |

|---|---|----------------------------|

| 0 | 1 | Wait one cycle             |

| 1 | 0 | Wait two cycles            |

| 1 | 1 | Wait three cycles          |

### .3 and .2 Data Memory Automatic Wait Control Bits

| 0 | 0 | No wait (Normal Operation) |

|---|---|----------------------------|

| 0 | 1 | Wait one cycle             |

| 1 | 0 | Wait two cycles            |

| 1 | 1 | Wait three cycles          |

#### .1 Stack Area Selection Bit

| 0 | Select internal register file area |

|---|------------------------------------|

| 1 | Select external data memory area   |

**.0** Not used for the S3C8639/C863A/C8647

**NOTE**: As external peripheral interface is not implemented in S3C8639/C863A/C8647, EMT register is not used. The program initialization routine should clear the EMT register to "00H" after a reset. Modification of EMT values during the normal operation may cause a system malfunction.

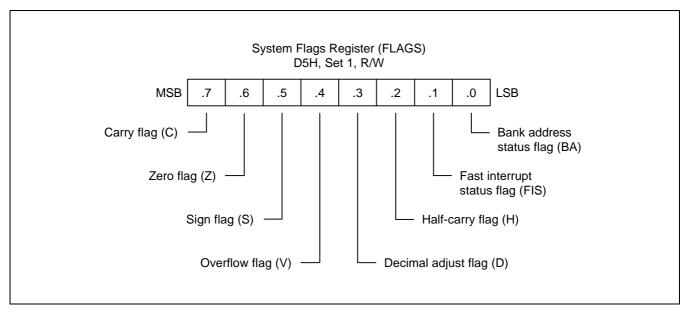

| FLAGS — Sy | stem Flags | Register |

|------------|------------|----------|

|------------|------------|----------|

D5H

Set 1

| Bit Identifier |

|----------------|

| RESET Value    |

| Read/Write     |

**Addressing Mode**

.6

.5

| .7                            | .6  | .5  | .4  | .3  | .2  | .1  | .0  |

|-------------------------------|-----|-----|-----|-----|-----|-----|-----|

| X                             | X   | x   | Х   | Х   | х   | 0   | 0   |

| R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Register addressing mode only |     |     |     |     |     |     |     |

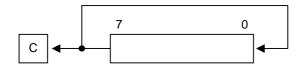

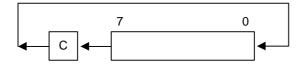

.7 Carry Flag (C)

| 0 | Operation does not generate a carry or borrow condition         |

|---|-----------------------------------------------------------------|

| 1 | Operation generates a carry-out or borrow into high-order bit 7 |

Zero Flag (Z)

| 0 | Operation result is a non-zero value |

|---|--------------------------------------|

| 1 | Operation result is zero             |

Sign Flag (S)

| 0 | Operation generates a positive number (MSB = "0") |

|---|---------------------------------------------------|

| 1 | Operation generates a negative number (MSB = "1") |

.4 Overflow Flag (V)

| 0 | Operation result is $\leq$ +127 or $\geq$ -128 |

|---|------------------------------------------------|

| 1 | Operation result is > +127 or < -128           |

.3 Decimal Adjust Flag (D)

| 0 | Add operation completed         |

|---|---------------------------------|

| 1 | Subtraction operation completed |

.2 Half-Carry Flag (H)

| 0 | No carry-out of bit 3 or no borrow into bit 3 by addition or subtraction         |

|---|----------------------------------------------------------------------------------|

| 1 | Addition generated carry-out of bit 3 or subtraction generated borrow into bit 3 |

.1 Fast Interrupt Status Flag (FIS)

| 0 | Cleared automatically during an interrupt return (IRET)                |

|---|------------------------------------------------------------------------|

| 1 | Automatically set to logic one during a fast interrupt service routine |

.0 Bank Address Selection Flag (BA)

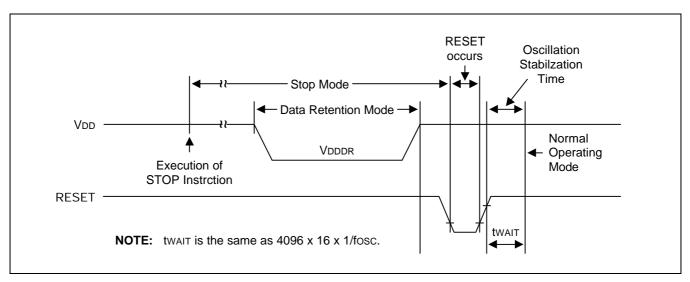

| 0 | Bank 0 is selected (by executing the instruction SB0) |