# PCM FRAME ALIGNER

## FEATURES

- Frame alignment/synthesis for PCM30 double frame and CRC-multiframe format.

- Meets CCITT Rec.G704

- Interface to route selectable between HDB3 and fibre optical

- HDB3 outputs switchable between fully bauded and half bauded format

- Error checking via CRC4 procedure

- Insertion and extraction of alarms and facility signals

- Selectable system clock (4096 kHz/ 8192 kHz)

- Selectable Interface mode (2048/4096 kBit/s) to system internal highway

- Programmable offsets for receive and transmit data

- Two frame receive buffer for receive route clock wander and jitter compensation

- Slip detection and direction indication

- Extended HDB3 error detection

- Error counters for code errors (switchable to "S, zeros counter"), frame errors and CRC4 errors

- Sub-multiframe assigned CRC Error indication with possibility of automatic insertion in Si-bit position of outgoing multiframe.

- Simplified data transfer between SA9101 and controller, supported by data stacks for receive and transmit signalling data, selectable interruptsources and DMA facilities.

- Double frame marker for serial data extraction support

- Repeated transmission of signalling data, if not updated.

- Three transparent modes for timeslot 0 in transmit direction

- Transparent mode for receive direction

- HDB3 error indication

- Idle channel data insertion selectable for any timeslot

- Channel loopback capabilities, test and diagnostic capabilities

- Parity checks

### **DESCRIPTION:**

The SA9101 (Frame Alignment unit for PCM30 Systems) is a C-MOS device which implements the interface to PCM30 Transmission Systems.

In the receive direction, the device performs HDB3 decoding, Frame alignment (selectable between doubleframe and CRC-Multiframe) and extraction of signalling data.

Wander absorption between the PCM carrier and the system internal highway is performed using an internal 2 frame memory. The incoming data stream is monitored

## **Description (Cont.)**

status and error conditions are reported through the  $\mu$ P interface. In the transmit direction, Frame (and Multiframe) alignment, signalling data insertion and HDB3 coding is performed.

If Multiframe format is enabled, CRC4 extraction and checking are carried out in the receive direction and CRC4 data is inserted in the transmit direction.

Stacks for transmit and receive signalling data with DMA capability as well as maskable interrupt sources simplify interfacing to microcontrollers.

Alarm simulation capabilities and selectable channel-loopback, support system diagnostics.

Different transparent modes for timeslot 0 in transmit direction simplify system test and data transmission through the system.

Advanced algorithms for synchronisation of doubleframe and CRC4 multiframe format data, and monitoring of frame and doubleframe formats minimise loss of data.

Control Registers allow different control settings through the µP interface.

Advanced C-MOS Technology ensures low power consumption and high reliability.

The device is upwards compatible with the Siemens ACFA (PEB 2035 V4.1) in PCM30

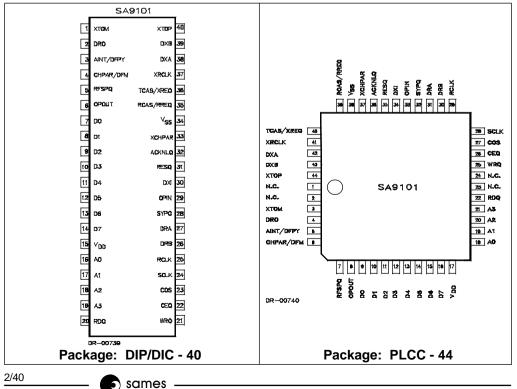

# PIN CONNECTIONS

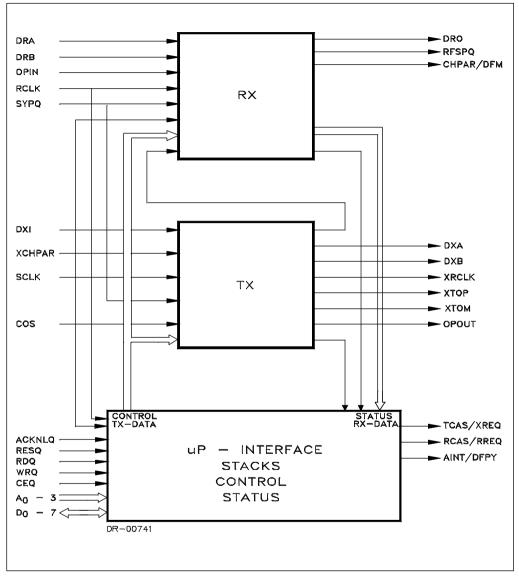

## **Block Diagram**

#### ELECTRICAL CHARACTERISTICS Absolute Maximum Ratings\*

| Parameters                | Symbol                            | Min  | Max                  | Unit |

|---------------------------|-----------------------------------|------|----------------------|------|

| Supply Voltage            | V <sub>DD</sub> - V <sub>SS</sub> | -0.3 | 6                    | V    |

| Voltage on any I/O pin    | V <sub>I</sub> /V <sub>o</sub>    | -0.3 | V <sub>DD</sub> +0.3 | V    |

| Current on any I/O pin    | I <sub>I</sub> /I <sub>o</sub>    |      | 20                   | mA   |

| Storage Temperature       | T <sub>stg</sub>                  | -55  | +125                 | °C   |

| Operating Temperature     | T <sub>OP</sub>                   | -10  | +70                  | °C   |

| Package Power Dissipation | P <sub>D</sub>                    |      | 1000                 | mW   |

\*Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This a stress rating only. Functional operation of the device at these or any other condition above those indicated in the operational sections of this specification, is not implied. Exposure to Absolute Maximum Ratings for extended periods may affect device reliability.

## **DC Operational Characteristics**

$V_{DD} = 5V, T = 10^{\circ}C..+70^{\circ}C$

|                          |                                  | Limit \ | Limit Values |      |                                  |

|--------------------------|----------------------------------|---------|--------------|------|----------------------------------|

| Parameter                | Symbol                           | Min.    | Max.         | Unit | Remarks                          |

| Supply Voltage           | V <sub>DD</sub> -V <sub>SS</sub> | 4.5     | 5.5          | V    |                                  |

| Supply Current (dynamic) | I <sub>DD</sub>                  |         | 100          | mA   |                                  |

| Standby Current          | I <sub>DDS</sub>                 |         | 100          | μA   |                                  |

| Inputs                   |                                  |         |              |      |                                  |

| High Voltage             | V <sub>IH</sub>                  | 2.4     |              | V    |                                  |

| Low Voltage              | V                                |         | 0.8          | V    |                                  |

| Leakage Current          | ILEAK                            | -5      | 5            | μA   | V <sub>1</sub> =0V <sub>DD</sub> |

| Input ACKNQ              |                                  |         |              |      |                                  |

| Pullup Current           | -I <sub>PUP</sub>                | 10      | 30           | μA   | V <sub>I</sub> =0                |

| Outputs                  |                                  |         |              |      |                                  |

| High Voltage             | V <sub>OH</sub>                  | 2.8     |              | V    | I <sub>он</sub> =-1mA            |

| Low Voltage              | V <sub>oL</sub>                  |         | 0.4          | V    | I <sub>oL</sub> =2mA             |

| Bidirects                |                                  |         |              |      |                                  |

| Input High Voltage       | V <sub>IH</sub>                  | 2.4     |              | V    |                                  |

| Input Low Voltage        | V                                |         | 0.8          | V    |                                  |

| Tristate Current         |                                  | -10     | 10           | μA   | V <sub>1</sub> =0V <sub>DD</sub> |

| Output High Voltage      | V <sub>OH</sub>                  | 2.8     |              | V    | I <sub>OH</sub> =-1mĀ            |

| Output Low Voltage       | V <sub>OL</sub>                  |         | 0.4          | V    | I <sub>oL</sub> =2mA             |

### **Operational Characteristics**

$T_A = 25^{\circ}C; V_{DD} = 5V \pm 5\%; V_{SS} = 0V$

|                    |                  | Limit | Values |      |

|--------------------|------------------|-------|--------|------|

| Parameter          | Symbol           | Min.  | Max.   | Unit |

| Input capacitance  | C <sub>IN</sub>  |       | 10     | pF   |

| Output capacitance | C <sub>OUT</sub> |       | 15     | pF   |

| I/O                | C <sub>IO</sub>  |       | 20     | pF   |

| 4/40               |                  |       |        |      |

## **PIN DESCRIPTION**

| Pin Name        | Direction | Pin No. |       | Description                                          |

|-----------------|-----------|---------|-------|------------------------------------------------------|

| Pin Name        | Direction | DIL     | PLCC  | Description                                          |

| AINT/DFPY       | 0         | 3       | 5     | Alarm interrupt/Double Frame Parity                  |

| ACKNLQ          | I         | 32      | 36    | DMA Acknowledge                                      |

| A[3-0]          | I         | 19-16   | 21-18 | Address Bus                                          |

| CEQ             | I         | 22      | 26    | Chip Enable                                          |

| CHPAR/DFM       | 0         | 4       | 6     | Receive Channel Parity/                              |

|                 |           |         |       | Double Frame Marker                                  |

| COS             | I         | 23      | 27    | Carrier out of Service                               |

| DRA             | I         | 27      | 31    | Receive Data in Plus                                 |

| DRB             | I         | 26      | 30    | Receive Data in Minus                                |

| DRO             | 0         | 2       | 4     | Receive Data Out                                     |

| DXA             | 0         | 38      | 42    | Transmit Data Out Plus                               |

| DXB             | 0         | 39      | 43    | Transmit Data Out Minus                              |

| DXI             | I         | 30      | 34    | Transmit Data In                                     |

| D[7-0]          | В         | 14-7    | 16-9  | Data Bus                                             |

| OPIN            | I         | 29      | 33    | Receive Optical Interface Data                       |

| OPOUT           | 0         | 6       | 8     | Transmit Optical Interface Data                      |

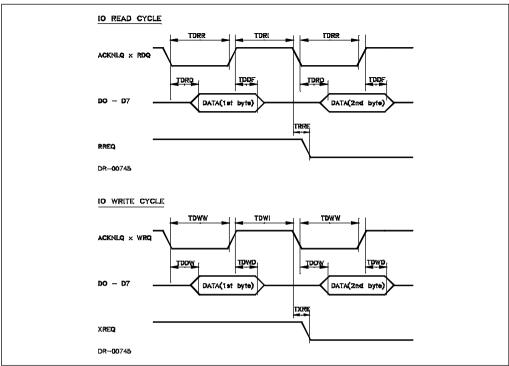

| RCAS/RREQ       | 0         | 35      | 39    | Receive TS16 Signal/Receive DMA<br>Interrupt Request |

| RCLK            | 1         | 25      | 29    | Receive Route Clock                                  |

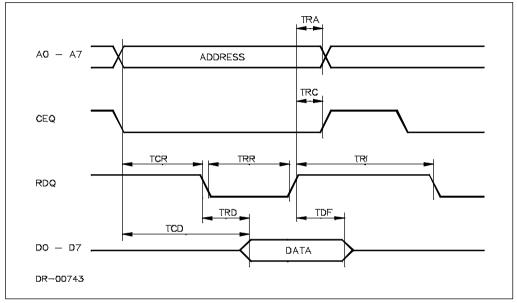

| RDQ             | I         | 20      | 22    | Read Enable                                          |

| RESQ            | I         | 31      | 35    | Reset                                                |

| RFSPQ           | Ō         | 5       | 7     | Receive Frame Synchronisation                        |

|                 |           |         |       | Pulse                                                |

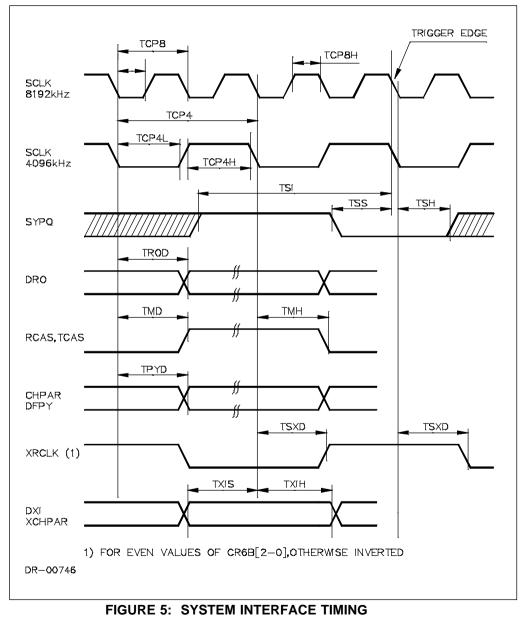

| SCLK            | I         | 24      | 28    | System Clock                                         |

| SYPQ            | I         | 28      | 32    | Synchronisation Pulse                                |

| TCAS/XREQ       | 0         | 36      | 40    | TransmitTS16Signal/TransmitDMA<br>Interrupt Request  |

| V <sub>DD</sub> | S         | 15      | 17    | +5V Supply                                           |

| V <sub>ss</sub> | S         | 34      | 38    | 0V Ground                                            |

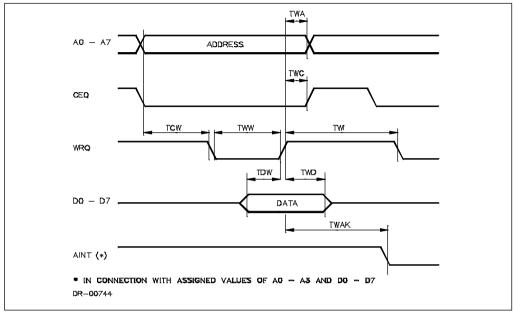

| WRQ             | I         | 21      | 25    | Write Enable                                         |

| XCHPAR          | 0         | 33      | 37    | Transmit Channel Parity                              |

| XRCLK           | 0         | 37      | 41    | Transmit Route Clock                                 |

| хтом            | 0         | 1       | 3     | Test Data Output Minus                               |

| XTOP            | 0         | 40      | 44    | Test Data Output Plus                                |

## DESCRIPTION OF INTERFACES

## Fibre Optical Interface

The fibre optical interface is enabled via the microprocessor interface.

| Signal | Pin | Input/Output/Bidirect | Function                                                                                                                                                                                                                                                             |

|--------|-----|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OPIN   | 29  | I                     | Optical Fibre In<br>Unipolar Input Signal at 2048 kbps<br>Input polarity sense is programmable<br>via CR8B3. Latching of data is<br>performed with the falling edge of<br>RCLK if optical interface is selected<br>via CR1B2. (See Fig. 6 Line Interface<br>Timing.) |

| OPOUT  | 6   | 0                     | Optical Fibre Out<br>Unipolar Output Signal at 2048 kbps<br>The output's active polarity is<br>programmable via CR6B7. Data is<br>clocked out on the rising edge of<br>XRCLK. Data duty cycle is 100%.                                                               |

| RCLK   | 25  | I                     | (See Fig. 6 Line Interface Timing.)<br>Route Clock<br>This clock, derived from the incoming<br>data by the line interface circuit (eg.<br>IPAT (PEB2235)), is necessary for<br>clocking received data into the SA9101.                                               |

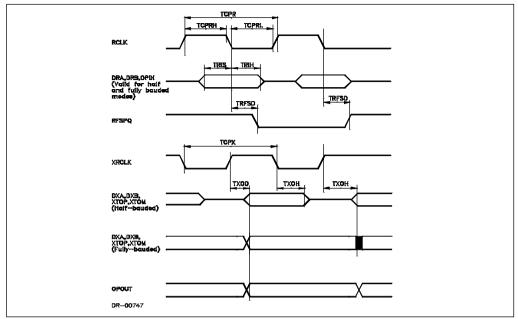

| XRCLK  | 37  | 0                     | Transmit Route Clock<br>This 2048kHz clock is generated from<br>the Station Clock, SCLK. (See Fig. 5<br>System Interface Timing and Fig. 6<br>Line Interface Timing.)                                                                                                |

## PCM30 Interface

| Signal | Pin | Input/Output/Bidirect | Function                  |

|--------|-----|-----------------------|---------------------------|

| DRA    | 27, | I                     | Data Receive +/-          |

| DRB    | 26  | I                     | HDB3 coded PCM Signal     |

| DXA    | 38, | 0                     | Data transmit +/-         |

| DXB    | 39  | 0                     | HDB3 coded PCM Signal     |

| RCLK   | 25  | I                     | Route Clock f = 2.048 MHz |

| XRCLK  | 37  | 0                     | Transmit route clock      |

## **Clock Generator**

| Signal | Pin | Input/Output/Bidirect | Function                                                                                                                                                                                                      |

|--------|-----|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCLK   | 24  | I                     | System Clock f=4,096 MHz/8,192MHz                                                                                                                                                                             |

| RFSPQ  | 5   | 0                     | Receive Frame Pulse<br>Frequency: 8 kHz<br>Duration: 488 ns<br>If loss of synchronisation, the line frame<br>pulse is inhibited                                                                               |

| SYPQ   | 28  | I                     | Synchronous Pulse<br>Defines start of frame for System internal<br>data, together with the programmed offset<br>values of transmit and receive counter.<br>Pulse width: >244 ns<br>Period: Multiples of 125µs |

## **DIU Controller**

| Signal  | Pin     | Input/Output/Bidirect | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------|---------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0 - D7 | 7 - 14  | В                     | Bidirectional 8 bit data-bus                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| A0 - A3 | 16 - 19 | Ι                     | Address lines for SA9101 internal<br>registers                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CEQ     | 22      | Ι                     | Chip enable input                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WRQ     | 21      | I                     | Write enable input                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RDQ     | 20      | Ι                     | Read enable input                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| COS     | 23      | I                     | Carrier out of service input.<br>SA9101 sends AIS to PCM30 interface<br>if input is at "1"                                                                                                                                                                                                                                                                                                                                                                                          |

| XREQ    | 36      | 0                     | Transmit DMA interrupt request                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RREQ    | 37      | 0                     | Receive DMA interrupt request                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| AINT    | 3       | 0                     | Alarm interrupt request                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ACKNLQ  | 32      | I                     | DMA Acknowledge (Active Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|         |         |                       | (Not used when CR6B6 = 0. If not used<br>then pin must be fixed to $V_{DD}$ .) If access to<br>internal TS16 signalling stacks is enabled<br>this input acts as an "access enable" to the<br>internal stacks (CRAB0-7 for T <sub>x</sub> and<br>SR7B0-7 for R <sub>x</sub> ) in conjunction with a<br>read/write command without the need of<br>generating the chip enable signal at CEQ.<br>In this case it is to be connected to the<br>acknowledge output of the DMA controller. |

## System Internal Highway

| Signal | Pin | Input/Output/Bidirect | Function         |

|--------|-----|-----------------------|------------------|

| DRO    | 2   | 0                     | Data Receive Out |

| DXI    | 30  | I                     | Data Transmit In |

Timeslot channels 0 - 31 to/from PCM30 interface.

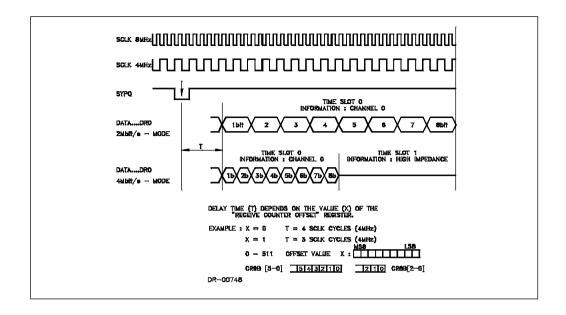

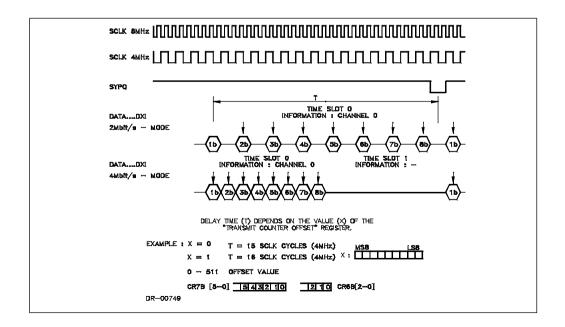

Bit rate 2048 kbit/s or 4096 kbit/s selectable via microprocessor interface.

#### **CAS Processing**

| Signal | Pin | Input/Output/Bidirect | Function                                                   |

|--------|-----|-----------------------|------------------------------------------------------------|

| DRO    | 2   | 0                     | Data Receive Out                                           |

| DXI    | 30  | I                     | Data Transmit In                                           |

| RCAS   | 35  | 0                     | Receive CAS, active high marks reception of channel 16     |

| TCAS   | 36  | 0                     | Transmit CAS, active high marks transmission of channel 16 |

## **Test/Supervision**

| Signal       | Pin      | I nput/Output/Bidirect | Function                                                                                                                                                            |

|--------------|----------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHPAR        | 4        | 0                      | Receive Channel parity<br>Appears according to the related<br>channel (timeslot)                                                                                    |

| DFPAR        | 3        | 0                      | Doubleframe Parity<br>During a current double-frame, the<br>parity of the previous double-frame<br>appears on DFPAR                                                 |

| XTOP<br>XTOM | 40,<br>1 | 0<br>0                 | HDB3-coded PCM (+), PCM (-) signal<br>for HDB3 diagnostic loop                                                                                                      |

| RESQ         | 31       | I                      | Reset (Output Disable)                                                                                                                                              |

|              |          |                        | Asynchronous reset signal (active low),<br>resets the internal circuit and switches<br>all outputs to high impedance state -<br>must be held low for minimum of 2µs |

| XCHPAR       | 33       | I                      | Transmit channel parity                                                                                                                                             |

# FUNCTIONAL DESCRIPTION Receive path

### Receive Link Interface

For data input, two different data types, with selectable input active polarity sense, are supported:

- Dual rail data (PCM[+], PCM[-]) at ports DRA, DRB received from a Line Interface Unit.

- Unipolar data at port OPIN (PCM 30) received from a fibre optical Interface.

Latching of data is carried out using the falling edge of the Receive route Clock (RCLK, 2048 kHz) recovered from the PCM receive data stream. Dual rail data is subsequently converted into a single rail, unipolar bit stream. The HDB3 line code is used along with Double Violation Detection or Extended Code Violation Detection (selectable). These errors increment the Code Violation Counter.

When using the unipolar input mode, the decoder is by-passed and no code violation will be detected.

Additionally, the receive Link Interface comprises the alarm detection for AIS (Alarm Indication Signal: unframed bit stream with constant logical 'one') and NOS (No Signal: Input signal with insufficient bit rate or insufficient density of ones).

The single rail bit stream is then processed by the Receiver.

### Receiver

The following functions are performed:

- Synchronization of pulse frame

- Synchronization of CRC4 multi-frame

- Error Indication when pulse frame synchronization is lost. In this case, AIS is sent to the system side. If the receiver is in transparent mode, AIS is suppressed.

- Initiating and controlling of re-synchronization after loss of synchronization. This may be carried out automatically by the SA9101, or under user control via the microprocessor interface.

- Detection of Remote Alarm Indication from the incoming data stream.

- Separation of service bits and data link bits. This information is stored in special status registers.

- Generation of control signals to synchronize the CRC checker, the parity generator, and the Receive Speech Memory control unit.

If the multi-frame format is selected, CRC checking of the Incoming data stream is done by generating check bits for a CRC submultiframe according to the CRC 4 procedure (PCM30, refer to CCITT Rec. G704). These bits are compared with those check bits that are received during the next CRC sub-multiframe. If there is a mismatch, the CRC error counter will be incremented. This 8-bit counter (default) can be extended to 10-bit length, by writing to the control registers.

#### **Receive Speech Memory**

The speech memory is organized as a two-frame elastic buffer with a size of  $64 \times 9$  bit (8-bit channel data plus one parity bit).

The functions are:

- Compensation of Input wander and jitter. Maximum wander amplitude (peak-to-peak) = 190 UI (1UI = 488 nS)

- Frame alignment between system frame and receive route frame

- Reporting and controlling of slips

Controlled by special signals generated by the Receiver, the unipolar bit stream is converted into bit-parallel, channel-serial data which is circularly written to the speech memory. At the same time, a parity signal is generated over each channel and also stored in the speech memory.

Reading of stored data is controlled by the System Clock (SCLK) and the Synchronization Pulse (SYPQ) in conjunction with the programmed offset values for the Receive timeslot/ Clock slot Counters. After conversion into a serial data stream and parity checking (errors are reported via the status registers), the data is given out via port DRO. Channel parity information is output at port CHPAR with selectable parity type (odd or even). Two bit rates (2048/4096 kbps) are selectable via the microprocessor interface.

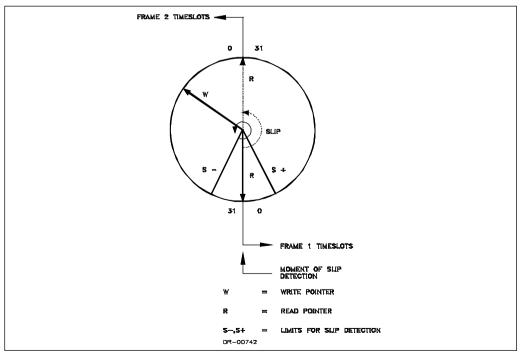

Figure 1.0: The Receive Speech Memory as circularly organized memory

Figure 1.0 illustrates the operation of the receive Speech Memory:

A slip condition is detected when the Write Pointer (W) and the Read pointer (R) of the memory are nearly coincident, i.e. the Write pointer is within the Slip Limits (S+, S-). If a slip condition is detected, a negative slip ( the next received frame is skipped) or a positive slip (the previous received frame is read out twice) is performed at the System Interface, depending on the difference between RCLK and SCLK, i.e. on the position of pointer R and W within the memory.

To reduce delay, the Receive Speech Memory can be switched to one frame length. For correct operation, System Clock SCLK and Synchronization Pulse SYPQ have to be derived from the Receive Route Clock RCLK and the Receive Frame Synchronous Pulse RFSPQ (PLL application). In Single Frame Mode, however, it is not possible to perform a slip after the slip condition has been detected.

## **Receive Transparent Mode**

If enabled, the frame aligner does not try to synchronise on the received data if synchronisation is lost. The AIS to the System Interface is disabled. The data appears on the System Interface synchronised to the System Clock (SCLK) as received.

## Transmit path

The PCM data is received from the system internal highway at port DXI at 2048 kbps or 4096 kbps. The channel assignment is equivalent to the receive direction. Data in invalid timeslots will be ignored.

Latching of data is controlled by the System Clock (SCLK) and the Synchronization Pulse (SYPQ), in conjunction with the programmed offset values of the Transmit Timeslot/ Clockslot Counters.

The Transmit Route Clock (XRCLK) is derived directly from the system clock by an internal clock divider. Consequently, the data received from the system interface is switched through without the need of intermediate storage.

The parity generation/checking mechanism is symmetrical to the receive path. The channel data is checked with the channel parity information generated internally or externally (input at port XCHPAR with selectable parity type). Errors are reported to the microprocessor interface. To avoid difficulties with external parity generation, the parity signal for non-speech data (TS0 and TS16) is ignored.

## Transmitter

The serial bit stream is then processed by the transmitter which has the following functions:

- Frame/multiframe synthesis of one of the selectable framing formats

- Insertion of service and data link information.

- Remote Alarm generation

- CRC generation and insertion of CRC bits

### Transmit Link Interface

Similar to the Receive Link Interface two different data types with selectable active polarity for the output are supported:

- Dual rail data (PCM[+], PCM[-]) at ports DXA, DXB with selectable duty cycle (50% or 100%) transmitted to a Line Interface Unit. Single rail data is converted into a dual rail bit stream. The HDB3 line code is employed.

- Unipolar data at port OPOUT with 100% duty cycle transmitted to a fibre optical interface.

Clocking of data is carried out on the positive transitions of the Transmit Route Clock: XRCLK (2048 kHz). XRCLK is generated by the SA9101.

Additionally, the dual rail outputs XTOP and XTOM are provided for test applications.

## Additional functions

#### Alarm Interrupt

Normally, the control of data transmission via the PCM line is carried out by polling the internal status registers of the SA9101 at equal time intervals. However, for fast error handling the option exists to configure a specific output port as interrupt port (AINT). This signal may be connected to an interrupt input of the on-board processor. Triggering of the output may be caused by up to 10 maskable interrupt sources.

### Single Channel Loop Back

As one of the extended test options, the Single Channel Loop Back enables reflection of a selected channel back to the system interface at port DRO.

#### **TS16** Extraction/Insertion

TS16 data can be extracted/inserted via the  $\mu$ P or the DMA facility provided. For  $\mu$ P interface, RREQ/XREQ act as interrupts. When one of these interrupts is received two bytes must be read/written consecutively before next frame information is written into it. For DMA operation see detailed timing diagram, Fig 7.3. (See DIU Controller Pin description table, CR6B6 Register and SR5B5 Register descriptions.)

Data Extraction/Insertion is also possible through the serial ports DRO and DXI by using a multiplexer in conjunction with the control signals RCAS/TCAS generated by the SA9101.

### Serial Data extraction on System Side

Together with the Double Frame Marker generated by the SA9101, any position in the serial data can be pointed to, for extraction.

### **Idle Code Insertion**

In TX direction any channel can be selected for idle code insertion using the Idle Channel Register bank.

### Signal Processing General

| PCM line bit rate   | : | 2048 kbps ±50 ppm         |

|---------------------|---|---------------------------|

| Single frame length | : | 256 bit, No. 1 256        |

| Framing frequency   | : | 8 kHz                     |

| Organization        | : | 32 timeslots, No. 0 31    |

|                     |   | with 8 bits each, No. 1 8 |

Timeslot 0 is reserved for frame alignment word and service Information. Switching between the two word framing formats (Doubleframe/CRC-Multiframe) is done via the Control Register.

#### Line Interfacing

- Dual rail data with HDB3 coding in conjunction with double violation detection or extended code violation detection. Errors are counted by the Code Violation Counter. (Selectable between 8 and 10 bit counter.)

- Single rail unipolar data with no zero suppression algorithm.

#### General alarms

- AIS : Detection and Transmission.

- NOS : No Signal Detection.

- RAI : Remote Alarm Indication and Transmission.

## **Channel Assignment (including Timeslot 0)**

The channel (timeslot) assignment from the PCM line to the system internal highway is performed without any changes of channel numbering (TS0,...,TS31). In the receive direction, the contents of timeslot 0 are switched through transparently. In the transmit direction, the contents of timeslot 0 of the outgoing PCM frame are normally generated by the SA9101. Additionally, one of three Transparent Modes can be selected to achieve transparency either for Sn bit information, Sn and Si bit information or for all of the data in timeslot 0.

$S_n$  and  $S_i$  bits can be fed through from the system interface (DXI) by activating transparent mode CR5B4, known as Timeslot 0 Signalling Transparent mode. Only  $S_n$  bits can be fed through DXI when the Extended Signalling Transparent mode is activated.

Priority is in the following order:

- Highest Timeslot 0 Transparent Mode (CR5B5)

- Medium Timeslot 0 Extended Signalling Transparent Mode (CX1B6)

- Lowest Timeslot 0 Signalling Transparent Mode (CR5B4)

| Transparent     | Framing              | A Bit   | S bits              | S <sub>i</sub> b | oits                       |

|-----------------|----------------------|---------|---------------------|------------------|----------------------------|

| Mode            | (incl. CRC)          |         |                     | Double frame     | CRC                        |

| Non-Transparent | Internally generated | CR4B5   | CR4B04 <sup>1</sup> | CR4B7 & CR5B2    | CR5B0 & CR5B1 <sup>2</sup> |

| CR5B5           | via DXI              | via DXI | via DXI             | via DXI          | via DXI                    |

| CR5B4           | Internally generated | CR4B5   | via DXI             | via DXI          | via DXI                    |

| CX1B6           | Internally generated | CR4B5   | via DXI             | CR4B7 & CR5B2    | CR5B0 & CR5B1 <sup>2</sup> |

**Notes:** 1) The S<sub>n</sub> bit stack may be used optionally

2) Automatic transmission of submultiframe error indication is selectable

## **General signalling**

- S<sub>n</sub> (Y) bits.

- S, bits.

## Signalling

- CCS: For Common Channel Signalling the use of timeslot 16 is recommended. The use of CCS is allowed with both the doubleframe and the CRC-Multiframe format.

- CAS-CC: For Channel Associated Signalling the use of timeslot 16 is recommended. The autonomous CAS multiframe structure is not related to a doubleframe or a CRC-Multiframe structure (refer to CCITT G704 paragraph 3.3.3). Note: CAS multiframe synchronization and syntheses are not performed by the SA9101.

#### **Doubleframe format**

The framing structure is defined by the contents of timeslot 0 (refer to table 1).

| Alternate Frames           | Bit Number     |                             |        |                 |                 |                 |                 |                 |

|----------------------------|----------------|-----------------------------|--------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Alternate Frames           | 1              | 2                           | 3      | 4               | 5               | 6               | 7               | 8               |

| Frame containing the frame | S <sub>i</sub> | 0                           | 0      | 1               | 1               | 0               | 1               | 1               |

| alignment signal           | Note 1         | te 1 Frame alignment signal |        |                 |                 |                 |                 |                 |

| Frame not containing the   | S <sub>i</sub> | 1                           | A      | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

| frame alignment signal     | Note 1         | Note 2                      | Note 3 |                 |                 | Note 4          |                 |                 |

### Table 1: Allocation of bits 1 to 8 of Timeslot 0

- S<sub>i</sub> bits: reserved for international use. If not used, these bits should be fixed to '1'. Access to received information via bits SR4B7 and SR5B2. Transmission is enabled via bits CR4B7 and CR5B2.

- 2. Fixed to '1'. Used for synchronization.

- 3. Remote Alarm Indication: In normal operation '0'; in alarm condition '1'. Transmission is done through CR4B5 and reception is indicated by interrupt (maskable) and SR0B4.

- S<sub>n</sub> (Y) bits: Reserved for national use. If not used, they should be fixed at '1'. Access to received information via bits SR4B[4-0]. Transmission is enabled via bits CR4B[4-0]

## Synchronization procedure

Synchronization status is reported via  $\mu$ P-interface Status Register. Framing errors are counted by the Framing Error Counter. Loss of synchronization is reached after detecting 3 consecutive incorrect FAS words or 3 consecutive incorrect service words (bit  $2 \neq 1$  in timeslot 0 of every frame not containing the frame alignment word). When this occurs, counting of framing errors will be stopped and AIS will be sent to the system internal highway.

The re-synchronization procedure starts automatically after entering loss of synchronisation state. Additionally, it may be invoked under user control via the  $\mu$ P-interface.

Synchronized state is reached after detecting:

- a correct FAS word in frame n,

- the presence of the correct service word (bit 2 = 1) in frame n+1

- a correct FAS word in frame n+2

Normal Synchronized operation starts with the data in frame n+2.

### **CRC-Multiframe**

The multiframe structure shown in table 2 is enabled via  $\mu$ P-interface.

| Multiframe           | : | 2 submultiframes = 2*8 frames                          |  |  |  |

|----------------------|---|--------------------------------------------------------|--|--|--|

| Multiframe alignment | : | bit 1 of frames 1,3,5,7,9,11 with the pattern '001011' |  |  |  |

| CRC bits             | : | bit 1 of frames 0,2,4,6,8,10,12,14                     |  |  |  |

| CRC block size       | : | 2048 bit (length of a submultiframe)                   |  |  |  |

| CRC procedure        | : | CRC4, according to CCITT Rec. G704                     |  |  |  |

The CRC procedure is automatically invoked when the multiframe structure is enabled. CRC errors in the received data stream are counted by the CRC Error Counter (max. one error per sub-multiframe). This 8-bit counter is extendable to 10 bit length.

## Synchronization procedure

Multiframe alignment is assumed to have been lost if double-frame alignment has been lost or 2 consecutive multiframe patterns are received with an error.

The multiframe re-synchronization procedure starts when doubleframe alignment has been regained. It may also be invoked by the user through the  $\mu$ P-interface. The CRC checking mechanism will be enabled after the second correct multiframe pattern has been found. However, CRC errors will not be counted in unsynchronized state.

The (multiframe) synchronized state is reached after detecting two correct multiframe alignment patterns in multiframe n and multiframe n+1. The CRC4 flag SR0B1 will be reset. Resynchronization starts whenever two consecutive multiframes are received with incorrect multiframe alignment pattern.

|            | Sub-       | Frame |                                  |   | Bit | s 1 to          | 8 of            | the f           | rame            |                 |

|------------|------------|-------|----------------------------------|---|-----|-----------------|-----------------|-----------------|-----------------|-----------------|

|            | Multiframe | No.   | 1                                | 2 | 3   | 4               | 5               | 6               | 7               | 8               |

|            |            | 0     | C <sub>1</sub>                   | 0 | 0   | 1               | 1               | 0               | 1               | 1               |

|            |            | 1     | 0                                | 1 | А   | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

|            |            | 2     | C <sub>2</sub>                   | 0 | 0   |                 |                 | 0               |                 |                 |

|            | I          | 3     | 0                                | 1 | А   | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

|            |            | 4     | C <sub>3</sub>                   | 0 | 0   |                 |                 | 0               |                 |                 |

|            |            | 5     | 1                                | 1 | А   | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

|            |            | 6     | C <sub>4</sub>                   | 0 | 0   | 1               | 1               | 0               |                 |                 |

|            |            | 7     | 0                                | 1 | А   | $S_{n0}$        | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

| Multiframe |            | 8     | C <sub>1</sub>                   | 0 | 0   | 1               | 1               | 0               | 1               | 1               |

|            |            | 9     | 1                                | 1 | А   | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

|            |            | 10    | C <sub>2</sub>                   | 0 | 0   |                 |                 | 0               |                 |                 |

|            | II         | 11    | 1                                | 1 | А   | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

|            |            | 12    | C <sub>3</sub>                   | 0 | 0   |                 |                 | 0               |                 |                 |

|            |            | 13    | C <sub>3</sub><br>S <sup>*</sup> | 1 | Α   | S <sub>n0</sub> | S <sub>n1</sub> | S <sub>n2</sub> | S <sub>n3</sub> | S <sub>n4</sub> |

|            |            | 14    |                                  | 0 | 0   |                 |                 | 0               |                 |                 |

|            |            | 15    | C <sub>4</sub><br>S <sup>*</sup> | 1 | А   | $S_{n0}$        | S <sub>n1</sub> | S <sub>n2</sub> | $S_{n3}$        | $S_{n4}$        |

- $S_i^*$ : Spare bits for international use. Access to received information via  $\mu$ P-interface. (For transmission, automatic transmission of sub-multiframe error or insertion through  $\mu$ P-interface is selectable).

- S<sub>n</sub>: Spare bits for national use. Additionally, the 5-byte stacks for receive and transmit are provided.

- C1..C4: Cyclic Redundancy Check bits.

- A: Remote Alarm Indication.

#### Table 2: CRC-Multiframe Structure

## S<sub>n</sub>-bit access

Due to new signalling procedures using the five  $S_n$  bits ( $S_{n0} \dots S_{n4}$ ) of every other frame of the CRC Multiframe structure, two possibilities of access via the microprocessor are suported:

- The standard procedure allows reading/writing the S<sub>n</sub>-bit registers without further support. The S<sub>n</sub>-bit information will be updated every other frame.

- The advanced procedure, allows reading/writing two S<sub>n</sub>-bit stacks each with a size of 5 bytes. Two status bits (SR5B6 and SR5B7) provide an indication for updating the stack information by reading/writing five bytes per multiframe from/to the assigned stack address. To avoid loss of information, the status bits should be monitored at time intervals less than 2ms (1,5ms recommended). With the first access to a stack, the associated status bit will be reset.

A Transmit or Receive Multiframe Begin interrupt is supported when Alarm Interrupt mode is enabled (CR5B6 and CR5B7).

If one makes use of the Sn bit stack in the Double frame format it is necessary that this be done in conjunction with an externally enforced Multi-frame structure to ensure the proper recovery of data on the far side. This is only possible in the Non-Transparent Mode for Timelsot 0.

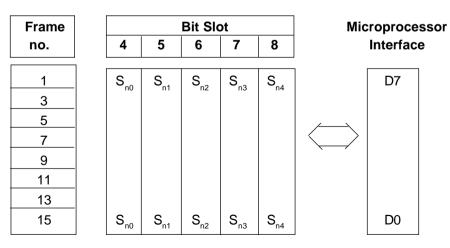

## Organization of the stacks:

The sequentially received  $S_n$  bits ( $S_{n0}$  up to  $S_{n4}$ ) of odd numbered frames of the multiframe structure are re-organized to bytes containing the  $S_n$ -information of the same level ( $S_{n0}$  byte up to  $S_{n4}$  byte). The  $S_{n4}$  byte is the first byte to be read or written via the microprocessor interface (refer to table 3).

Alternatively, S<sub>n</sub> bits may be processed via the system interface, if one of the transparent modes are enabled.

## Table 3: Organisation of the S<sub>n</sub>-Bit Stacks

## S<sub>i</sub>-bit access

In accordance with CCITT signalling requirements, the S, bits of frame 13 and frame 15 of the CRC Multi-frame can be used to indicate received error submultiframes:

| Submultiframe I status<br>Submultiframe II status : | :<br>S:15 | <b>S</b> <sub>i13</sub> |

|-----------------------------------------------------|-----------|-------------------------|

| no CRC error<br>CRC error                           | :         | $S_i = 1$<br>$S_i = 0$  |

$S_i$ -bits insertion can be done through the  $\mu$ P-interface(in non-Transparent and Extended Timeslot 0 Signalling Transparent modes) or, if enabled, automatically by the SA9101 without any intervention of the microprocessor. In this case, the status information of received sub-multiframe, is inserted in  $S_i$ -bit position of the outgoing CRC-Multiframe. A third option is via the system interface should the Timeslot 0 Transparent or Timeslot 0 Signalling Transparent modes be selected.

## Differences to Siemens ACFA (PEB2035 V4.1)

- 1. Automatic Force Resynchronisation feature for CRC mode, CR1B6 (Mode Register, bit AFR), is not used because this feature is implemented in hardware to be carried out automatically.

- 2. S<sub>n</sub> bit stack

$\ddot{C}$ R1B5 (Mode Register, bit ENSN) enables the S<sub>n</sub> bit stack for both CRC Multiframe and Double frame formats.

3. CRC Multiframe enable

CR1B3 (Mode Register, bit CRC) switches only between CRC Multiframe and DoubleFrame formats. No need for CX1B7 (EMOD DFSN) to enable  $S_n$  bit stack in Double Frame format due to point 2 above.

- 4. Service Word Condition Disable CR9B7 (RC1.SWD) is not used. Always functions in Standard Operation mode, i.e. 3 consecutive incorrect service words will cause loss of synchronisation.

- Select loss of Sync Condition CR9B6 (RC1.ASY4) is not used. Always functions in Standard Operation Mode (according to CCITT Rec.), i.e. 3 consecutive incorrect service words will cause loss of synchronisation.

- Extended DMA Mode CX1B1 (EMOD EDMA) is not used. The DMA facility must always read/write two consecutive bytes. This is the only mode of operation therefore no selection is required.

- 7. Disable AIS to System Interface CX1B0 (EMOD DAIS) is redefined. Siemens allowed for AIS selection for receive transparent mode. However, in Receive transparent mode synchronisation may be lost and therefore AIS is always disabled in the SA9101. This bit is redefined to provide a double frame marker to provide synchronisation to the Double Frame format.

- 8. Unique feauture in Timeslot 0 Signalling Transparent Mode The SA9101 is capable of recognising the frame alignment pattern and therefore will not overwrite the Sn and Si information inserted externally (via DXI) in the desired bit locations of the alternating timeslot 0 words.

### SA9101 REGISTER DESCRIPTION Control Register Default setting

After RESET, the SA9101 is initialized for PCM30 doubleframe format with register values listed in Table 4.

| Register | Register | Reset     | Meaning                                                                                                                                                                                                                             |  |

|----------|----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Name     | ADR      | Value     | _                                                                                                                                                                                                                                   |  |

| CR0B[70] | 0        | 00H       | Alarm Interrupt mode disabled/Double Violation<br>Detection, no influence on error counting, channel<br>parity alarms, data transmission via port DRO, or<br>synchronization. No Alarm simulation. Status register<br>read enabled. |  |

| CR1B[70] | 1        | C0H       | PCM30-doubleframe format with dual rail (RZ) line interface ports/4 Mbps system interface mode/no AIS transmission to remote $end/S_n$ -bit stacks are disabled.                                                                    |  |

| CR2B[70] | 2        | 00H       | Channel Parity Check is active for channel 0.                                                                                                                                                                                       |  |

| CR3B[70] | 3        | 00H       | Channel Loop Back and Single Frame mode are disabled.                                                                                                                                                                               |  |

| CR4B[70] | 4        | 40H       | All bits of the transmitted service word are cleared (bit 2 excl.).                                                                                                                                                                 |  |

| CR5B[70] | 5        | 00H       | Spare bit values and additional interrupts are cleared.                                                                                                                                                                             |  |

| CR6B[70] | 6        | 00H       | Outputs for transmit dual rail line data and assigned<br>test data are active low, internal signalling stacks and<br>external transmit channel parity are disabled.<br>The Transmit Clock slot Offset is cleared.                   |  |

| CR7B[70] | 7        | 40H       | 4096 kHz system clock frequency. The Transmit Timeslot Offset is cleared.                                                                                                                                                           |  |

| CR8B[70] | 8        | 30H       | Even Receive Channel Parity, Receive dual rail line<br>data inputs are active low. The Receive Clock slot<br>Offset is cleared. CRC Error Counter Extension is<br>disabled.                                                         |  |

| CR9B[70] | 9        | C0H       | The Receive Timeslot Offset is cleared.                                                                                                                                                                                             |  |

| CRAB[70] | A        | FFH       | The Transmit Signalling stack is cleared. Its values are not readable until the signalling stack mode is enabled.                                                                                                                   |  |

| CRBB[70] | В        | Undefined | S <sub>n</sub> bit stack contents unknown.                                                                                                                                                                                          |  |

| CRCB[70] | С        | 00H       | No interrupt source is enabled.                                                                                                                                                                                                     |  |

| CRDB[70] | D        | 54H       | Idle Channel Code is set to '54' hex.                                                                                                                                                                                               |  |

| CX1B[70] | 1        | 00H       | Half-bauded mode                                                                                                                                                                                                                    |  |

| CX6B[70] | 6        | 00H       | Normal operation                                                                                                                                                                                                                    |  |

| CX7B[70] | 7        | 00H       | Normal operation                                                                                                                                                                                                                    |  |

| CX8B[70] | 8        | 00H       | Normal operation                                                                                                                                                                                                                    |  |

| CX9B[70] | 9        | 00H       | Normal operation                                                                                                                                                                                                                    |  |

#### Table 4: Initial Values after reset

## **Detailed Description**

|                  | ADR 0 | ALARM Control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register<br>Name | Bit   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CR0B0            | 0     | Alarm simulation<br>A "1" initiates error simulation of alarm indication signal<br>(AIS), slip, parity, CRC, no signal, loss of frame alignment,<br>remote alarm, code violations and framing errors.<br>Error counters for frame errors, code violations and CRC<br>errors will be incremented.                                                                                                                                                                                                                          |

| CR0B1            | 1     | Force re-synchronisation<br>Setting of this bit initializes resynchronisation to establish<br>normal frame alignment and, if enabled, CRC4 frame re-<br>synchronization.Resetting is not necessary.                                                                                                                                                                                                                                                                                                                       |

| CR0B2            | 2     | Clear CHNL Parity Alarm Latch<br>Setting of this bit forces reset of CHNL Parity error alarms.<br>Status-registers ADR 0, bit 2 and ADR 5, bit 3, 4 will be reset<br>to "0".                                                                                                                                                                                                                                                                                                                                              |

| CR0B3            | 3     | Send AIS towards System interface (DRO), i.e. switching<br>network (SN). Device sends AIS (continuously one's) to the<br>SN. Tests of the speech memory in loopback mode are not<br>effected.                                                                                                                                                                                                                                                                                                                             |

| CR0B4            | 4     | Disable Error Counters<br>This bit can be set 1µs before the contents of the error<br>counters are read to get stable values. The error counters<br>will be reset after this bit is reset to zero. No errors are<br>counted while this bit is active. This procedure has been<br>implemented to maintain compatibility with the previous<br>frame aligners. If an error counter is read without setting this<br>bit previously, only the adressed error - counter will be reset<br>after read -access has been completed. |

| CR0B5            | 5     | Enable Control Registers Read<br>If this bit is set to one, the control registers (ADR0-ADRD) are<br>selected instead of the status registers during read operation.                                                                                                                                                                                                                                                                                                                                                      |

| CR0B6            | 6     | Enable Full HDB3-Error Detection<br>This bit enables HDB3 check for groups of more than 3<br>spaces (zeros)                                                                                                                                                                                                                                                                                                                                                                                                               |

| CR0B7            | 7     | Enable Alarm Interrupt Mode<br>Output DFPY changes its function to AINT while this bit is at<br>"1".                                                                                                                                                                                                                                                                                                                                                                                                                      |

Note: All "Not used" bits must be set to zero in all control registers

ADR 1 SA9101 Configuration

| Register<br>Name | Bit | Description                                                                                                                                                                                                                                                       |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR1B0            | 0   | Send AIS Towards Remote End<br>Setting of this bit causes transmitting AIS towards the remote<br>end. The test data-outputs are not affected.                                                                                                                     |

| CR1B1            | 1   | Select Interface Mode<br>Switches operation mode on DRO and DXI.<br>1 = 2 Mbits/s<br>0 = 4 Mbits/s                                                                                                                                                                |

| CR1B2            | 2   | Enable optical Interface<br>If set to one, OPIN is enabled instead of dual rail ports.                                                                                                                                                                            |

| CR1B3            | 3   | Activate CRC4<br>A "1" activates CRC4-operation                                                                                                                                                                                                                   |

| CR1B4            | 4   | Select counter mode<br>Only two channels per frame are counted if set to "1".                                                                                                                                                                                     |

| CR1B5            | 5   | Enable Sn-bit Stack<br>In CRC-mode, the transmit and receive Sn bit stacks can be<br>used instead of the registers for transmit and receive service<br>word. Transmitting from Sn-Bit stack is disabled if one of the<br>timeslot 0 transparent modes is enabled. |

| CR1B6            | 6   | Not used (fixed 1)                                                                                                                                                                                                                                                |

| CR1B7            | 7   | For Re-synchronisation of CRC4 Multiframe                                                                                                                                                                                                                         |

## ADR 2 Channel Parity Check

| Register<br>Name | Bit | Description                                                |

|------------------|-----|------------------------------------------------------------|

| CR2B[0-4]        | 0-4 | Selects channel                                            |

| CR2B5            | 5   | A "1" disables parity-check of selected channel            |

| CR2B6            | 6   | Not used                                                   |

| CR2B7            | 7   | Extended Mode Register access enabled                      |

|                  |     | Allows access to the Extended Control Registers CX1 to CX9 |

| Register<br>Name | Bit | Description                                                                                                                                                                                                  |

|------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CR3B[0-4]        | 0-4 | The addressed timeslot (131) is looped back to the system<br>interface.<br>Idle channel code content of control register D for this channel<br>is sent to remote end.<br>Code "00000" deactivates loop-back. |

| CR3B5            | 5   | A "1" disables loop back of selected channel                                                                                                                                                                 |

| CR3B6            | 6   | Select single frame delay mode<br>Signal delay set to max. one frame length., if this bit is at "1".                                                                                                         |

| CR3B7            | 7   | Alarm Interrupt Acknowledge<br>A "1" clears AINT. Resetting is not necessary.                                                                                                                                |

ADR 3 Channel Loop Back

ADR 4 Service Word

| Register<br>Name | Bit | Description                                                                                                                                                 |  |

|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CR4B[0-4]        | 0-4 | Y (Sn) bits for national use<br>These bits are inserted in the service word, if $S_n$ -bit stack mod<br>is disabled and no TS0 transparent mode is enabled. |  |

| CR4B5            | 5   | Send Remote Alarm to Remote End<br>A "1" causes bit 3 of service word to be set to "1".<br>It is ignored if TS0 transparent mode is enabled.                |  |

| CR4B6            | 6   | Synchronization bit, internally set to "1". It cannot be overwritten.                                                                                       |  |

| CR4B7            | 7   | First bit of service word if double-frame format enabled,<br>and Non-transparent or Extended TS0 Signalling Transparent<br>modes enabled.                   |  |

| ADR 5 Data link bits for internal use |     |                                                                                                                                                                                                                                                                               |                                                                           |  |  |  |

|---------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|--|--|--|

| Register<br>Name                      | Bit |                                                                                                                                                                                                                                                                               | Description                                                               |  |  |  |

| CR5B0                                 | 0   | S <sub>i</sub> (X)-bit in frame 15                                                                                                                                                                                                                                            | Only if CRC4 processing activated and<br>Non- transparent or Extended TS0 |  |  |  |

| CR5B1                                 | 1   | S <sub>i</sub> (X)-bit in frame 13                                                                                                                                                                                                                                            | Signalling Transparent mode enabled.                                      |  |  |  |

| CR5B2                                 | 2   | S <sub>1</sub> (X)-bit of frame alignment signal for international use, if<br>double frame format enabled and Non-transparent or Extended<br>TS0 Signalling Transparent mode enabled.                                                                                         |                                                                           |  |  |  |

| CR5B3<br>CRC4                         | 3   | Automatic Transmission of Submultiframe Status (only in mode, and Non-transparent or Extended TS0 signalling transparent mode).<br>Instead of transmitting Si bits (CR5 bit 0 and 1), the submultiframe status is inserted (SR 8, bit 1 -> X-bit(13), SR8 bit 0 -> X-bit(15). |                                                                           |  |  |  |

| CR5B4                                 | 4   | Timeslot 0 Signalling Transparent mode. In Double frame and CRC Multiframe modes Sn and Si bits of Timeslot 0 are transmitted as applied on DXI.                                                                                                                              |                                                                           |  |  |  |

| CR5B5                                 | 5   | Timeslot 0 Full Transparent mode<br>All information is transmitted as applied on DXI.                                                                                                                                                                                         |                                                                           |  |  |  |

| CR5B6                                 | 6   | Interrupt Mask "Begin                                                                                                                                                                                                                                                         |                                                                           |  |  |  |

|                                       |     | Receive Multiframe"                                                                                                                                                                                                                                                           | A "1" enables interrupt source<br>only if alarm interrupt mode            |  |  |  |

| CR5B7                                 | 7   | Interrupt Mask "Begin<br>Transmit Multiframe"                                                                                                                                                                                                                                 | enabled                                                                   |  |  |  |

ADR 5 Data link bits for internal use

| Register<br>Name | Bit | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CR6B[0-2]        | 0-2 | Set value for transmit bit counter (bit 0-2) which is loaded in the transmit counter when the synchronization pulse is active.                                                                                                                                                                                                                                                                                      |  |  |  |  |

| CR6B3            | 3   | Transmit Test data Polarity<br>Outputs are active low if bit is at "0"                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| CR6B4            | 4   | External Transmit Channel Parity Type<br>0 : Even<br>1 : Odd                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| CR6B5            | 5   | Enable External Transmit Channel Parity Input.<br>The internally generated channel parity signal is compared<br>with the signal at the channel parity input if this register bit is<br>set to "1". For signalling, the parity-value on the parity input is<br>ignored, because it is generated internally.                                                                                                          |  |  |  |  |

| CR6B6            | 6   | Enable Internal Signalling Stack.<br>If set to "1" the two-byte stacks for receive and transmit<br>signaling data (timeslot 16) are enabled. Access to the TS16<br>Signalling Stack is possible via µP interface or by means of<br>DMA. The RREQ and XREQ signals can be used either as<br>interrupts or as DMA request signals. For DMA transfer the<br>ACKNLQ pin should be used for direct access to the stacks. |  |  |  |  |

| CR6B7            | 7   | <ul> <li>Transmit Data Output Polarity</li> <li>Bit at "1": Dual rail outputs are active high, optical output is active low</li> <li>Bit at "0": Dual rail outputs are active low, optical output is active high</li> </ul>                                                                                                                                                                                         |  |  |  |  |

ADR 6 Transmit control 0

## ADR 7 Transmit Control 1

| Register<br>Name | Bit | Description                                                                                               |  |  |  |  |  |

|------------------|-----|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| CR7B[0-5]        | 0-5 | Set value for timeslot which is loaded into the transmit counter when the synchronization pulse is active |  |  |  |  |  |

| CR7B6            | 6   | Mark CRC Alarm (Bit at "1" - Enable Alarm Source)                                                         |  |  |  |  |  |