# **SIEMENS**

# ICs for Consumer Electronics

Single Chip PIP System

SDA 9288X (A141)

PIP 2

Data Sheet 03.96

#### Edition 03.96

This edition was realized using the software system FrameMaker<sup>®</sup>.

Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1996. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport. For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

# Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

| SDA 9288<br>Revision                |                             | Current     | Version: 03.96                                                    |

|-------------------------------------|-----------------------------|-------------|-------------------------------------------------------------------|

| Previous \                          | /ersion:                    |             |                                                                   |

| Page<br>(in<br>previous<br>Version) | Page<br>(in new<br>Version) | Subjects (m | ajor changes since last revision)                                 |

|                                     |                             | 25.1.1994:  | Preliminary Specification V1.1                                    |

|                                     | 22; 23; 24                  | 25.1.1994:  | warnings                                                          |

|                                     | 24                          | 25.1.1994:  | additional bits VSIISQ, VSPISQ at subad. 07/08                    |

|                                     | 25                          | 25.1.1994:  | additional bits DACONDE, DACONST at subad. 0D                     |

|                                     | 26                          | 25.1.1994:  | supply voltage range                                              |

|                                     | 32                          | 25.1.1994:  | values DAC                                                        |

|                                     | 35                          | 25.1.1994:  | diagram                                                           |

|                                     | 43                          | 25.1.1994:  | influence HSIDEL to VSIDEL adjustment                             |

|                                     | 19; 21                      | 19.4.1994:  | additional note PLL switch READ27                                 |

|                                     | 43                          | 19.4.1994:  | timing of ADC clamping                                            |

|                                     | 15                          | 20.6.1994:  | warning subaddr. 02                                               |

|                                     | 20; 25                      | 20.6.1994:  | additional bit SELDOWN at subaddr. 0B                             |

|                                     | 23                          | 20.6.1994:  | value $V_{OL}$ outputs SEL, SELD added                            |

|                                     | All                         | 18.7.1994:  | pages no. shifted                                                 |

|                                     | 10; 15; 18                  | 18.7.1994:  | improvement: additional bits D5, D6 (CLPS; CLPFIX) at subaddr. 06 |

|                                     | 15; 19                      | 18.7.1994:  | bit D0 of subaddress 0D deleted                                   |

|                                     | 17                          | 18.7.1994:  | new: examples for adjustment of frame colors                      |

|                                     | 17                          | 18.7.1994:  | text bits IMOD, PMOD                                              |

|                                     | 22                          | 18.7.1994:  | additional remark at subaddress 02                                |

|                                     | 25                          | 18.7.1994:  | clamping current. Additional values                               |

|                                     | 28; 29                      | 18.7.1994:  | application board layout and application circuit new              |

|                                     | 30                          | 18.7.1994:  | timing of ADC clamping changed                                    |

|                                     | 32                          | 18.7.1994:  | values DAC output current                                         |

# **SIEMENS**

| Table o                                                                                                  | of Contents                                                                                                                                                                                                                                                                                            | Page                                               |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                                                            | General Description  Features  Pin Configuration  Pin Definitions and Functions  Functional Block Diagram                                                                                                                                                                                              | 6<br>8<br>9                                        |

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.5<br>2.6<br>2.7<br>2.7.1<br>2.7.2<br>2.7.3 | System Description AD Conversion, Inset Synchronization Input Signal Processing PIP Field Memory Output Signal Processing Matrix Equations Frame Insertion Select Signal DA Conversion PLL I²C Bus I²C Bus Addresses I²C Bus Receiver Format I²C Bus Commands                                          | 12<br>13<br>14<br>16<br>17<br>17<br>18<br>18<br>18 |

| 3<br>3.1<br>3.2<br>3.3                                                                                   | Electrical Characteristics Absolute Maximum Ratings Operational Range Characteristics                                                                                                                                                                                                                  | 25<br>26                                           |

| 4.1<br>4.2<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3.1<br>4.3.2                                | Diagrams Output Current of DA Converters Application Information Reference Voltage Generation for ADC Adjustment of YDEL Three Level Interface (3-L) Application Board Layout Proposal Application Circuit (R, G, B-mode) Waveforms Timing of ADC Clamping Phase Relation of Sync Pulses at Frame Mode | 34<br>35<br>35<br>39<br>40<br>41<br>42<br>43       |

| 5                                                                                                        | Package Outlines                                                                                                                                                                                                                                                                                       | 45                                                 |

#### I<sup>2</sup>C Bus

Purchase of Siemens  $I^2C$  components conveys the license under the Philips  $I^2C$  patent to use the components in the  $I^2C$  system provided the system conforms to the  $I^2C$  specifications defined by Philips.

1 General Description

The Picture-in-Picture Processor SDA 9288X A141 generates a picture of reduced size of a video signal (inset channel) for the purpose of combining it with another video signal (parent channel). The easy implementation of the IC in an existing system needs only a few additional external components. There is a great variety of application facilities in professional and consumer products (TV sets, supervising monitors, multi-media, ...)

#### Single Chip PIP System

**SDA 9288X**

Data Sheet MOS

#### 1.1 Features

#### · Single chip solution

Clamping, AD conversion, filtering, field memory, RGB matrix, DA-conversion and clock generation integrated on one chip

#### • 2 picture sizes

1/9 or 1/16 of normal size

#### High resolution display

13.5 MHz/27 MHz display clock frequency

212 luminance and 53 chrominance pixels per inset line for picture size 1/9

6-bit amplitude resolution for each incoming signal component

Field and frame mode display

Horizontal and vertical filtering

Special antialias filtering for the luminance signal

#### 16:9 compatibility

Operation in 4:3 and 16:9 sets

4:3 inset signals on 16:9 displays or v.v. with picture size 1/9 and 1/16, respectively

#### Analog inputs

$$Y$$

, + (B-Y), + (R-Y) or  $Y$ , -(B-Y), -(R-Y)

#### Analog outputs

Y, + (B-Y), + (R-Y) or Y, - (B-Y), - (R-Y) or RGB

3 RGB matrices: EBU, NTSC (Japan), NTSC (USA)

#### • Free programmable position of inset picture

Steps of 1 pixel and 1 line

All PIP and POP positions are possible

#### Programmable framing

4096 frame colors

Variable frame width

| Туре      | Ordering Code | Package    |

|-----------|---------------|------------|

| SDA 9288X | on request    | P-DSO-32-2 |

# **SIEMENS**

- Freeze picture

- I2C Bus control

- Threefold PIP/POP facility

Three different I<sup>2</sup>C-addresses (pin-programmable)

Tri-State outputs

- Numerical PLL circuit for high stability clock generation

- No necessity of PAL/SECAM delay lines (using suitable color decoders i.e. TDA 8310)

- Multistandard applications

625 lines/525 lines standard (inset and parent channel)

Scan conversion systems as flickerfree display systems (parent channel)

HDTV (parent channel)

- P-DSO-32-2 package/350 mil (SMD)

- 5 V supply voltage

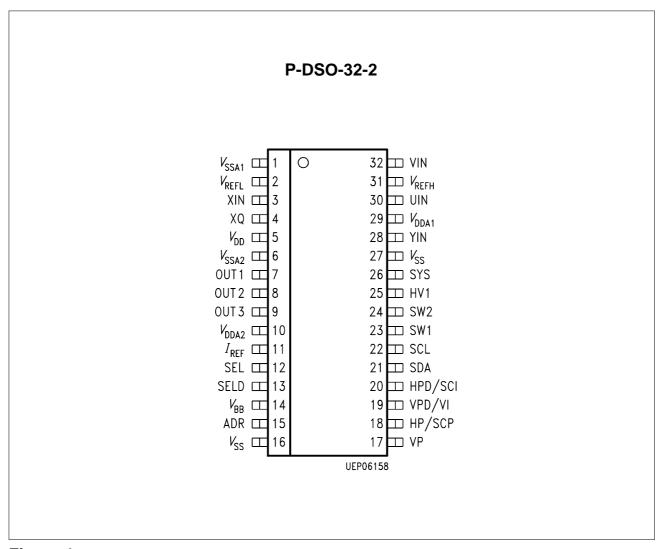

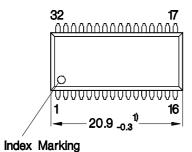

# 1.2 Pin Configuration

(top view)

Figure 1

## 1.3 Pin Definitions and Functions

| Pin No. | Symbol           | Function <sup>1)</sup> | Descriptions                                                                                                                       |  |

|---------|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 1       | $V_{\sf SSA1}$   | S                      | Analog voltage supply $(V_{ m SS})$ for ADC                                                                                        |  |

| 2       | $V_{REFL}$       | 1                      | Lower reference voltage for AD converters                                                                                          |  |

| 3       | XIN              | I                      | Quartz oscillator (input) or quartz clock<br>(from another PIP IC) or line locked clock<br>(27 MHz, from a digital parent channel) |  |

| 4       | XQ               | Q                      | Quartz oscillator (output)                                                                                                         |  |

| 5       | $V_{DD}$         | S                      | Digital voltage supply $(V_{ m DD})$                                                                                               |  |

| 6       | $V_{\sf SSA2}$   | S                      | Analog voltage supply $(V_{ m SS})$ for DAC and PLL                                                                                |  |

| 7       | OUT1             | Q/ana                  | Analog output: chrominance signal + (R-Y) or – (R-Y) or R                                                                          |  |

| 8       | OUT2             | Q/ana                  | Analog output: luminance signal Y or G                                                                                             |  |

| 9       | OUT3             | Q/ana                  | Analog output: chrominance signal + (B-Y) or – (B-Y) or B                                                                          |  |

| 10      | $V_{DDA2}$       | S                      | Analog voltage supply $(V_{ m DD})$ for DAC and PLL                                                                                |  |

| 11      | $I_{REF}$        | Q/ana                  | Reference current for DA-converters                                                                                                |  |

| 12      | SEL              | Q                      | Single frequency fast PIP switching output (tristate)                                                                              |  |

| 13      | SELD             | Q                      | Double frequency fast PIP switching output (tristate)                                                                              |  |

| 14      | $V_{BB}$         | S                      | Capacitor connection for smoothing internally generated substrate bias                                                             |  |

| 15      | ADR              | I <sub>3-L</sub>       | I <sup>2</sup> C Bus address control                                                                                               |  |

| 16,27   | $V_{	extsf{SS}}$ | S                      | Digital voltage supply ( $V_{ m SS}$ )                                                                                             |  |

| 17      | VP               | 1                      | Multifrequency vertical sync for parent channel                                                                                    |  |

| 18      | HP/SCP           | 1                      | Multifrequency horizontal sync for parent channel                                                                                  |  |

| 19      | VPD/VI           | I                      | Double frequency vertical sync for parent channel or vertical sync input for inset channel                                         |  |

| 20      | HPD/SCI          | I                      | Double frequency horizontal sync for parent channel or horizontal sync input for inset channel                                     |  |

| 21      | SDA              | I/Q                    | I <sup>2</sup> C Bus data                                                                                                          |  |

| 22      | SCL              | I                      | I <sup>2</sup> C Bus clock                                                                                                         |  |

| 23      | SW1              | Q <sub>3-L</sub>       | I <sup>2</sup> C Bus controlled output1                                                                                            |  |

| 24      | SW2              | Q <sub>3-L</sub>       | I <sup>2</sup> C Bus controlled output2                                                                                            |  |

| 4) 1    |                  | ·                      | digital /TTL \ 2.1 + 2 layel C + aupply yeltage                                                                                    |  |

<sup>&</sup>lt;sup>1)</sup> I : input, Q : output, ana : analog, TTL : digital (TTL), 3-L : 3-level, S : supply voltage

# 1.3 Pin Definitions and Functions (cont'd)

| Pin No. | Symbol | Function <sup>1)</sup> | Descriptions                                                                                      |

|---------|--------|------------------------|---------------------------------------------------------------------------------------------------|

| 25      | HVI    | I <sub>3-L</sub>       | Special 3-level hor. and vert. sync signal for inset channel                                      |

| 26      | SYS    | I <sub>3-L</sub>       | Input for standard depending internal switching (LOW (L) = PAL, MID (M) = NTSC, HIGH (H) = SECAM) |

| 28      | YIN    | I/ana                  | Analog input: luminance signal Y                                                                  |

| 29      | VDDA1  | S                      | Analog voltage supply $(V_{ m DD})$ for ADC                                                       |

| 30      | UIN    | I/ana                  | Analog input: chrominance signal + (B-Y) or - (B-Y)                                               |

| 31      | VREFH  | I                      | Upper reference voltage for AD converters                                                         |

| 32      | VIN    | I/ana                  | Analog input: chrominance signal + (R-Y) or - (R-Y)                                               |

I : input, Q : output, ana : analog, TTL : digital (TTL), 3-L : 3-level, S : supply voltage

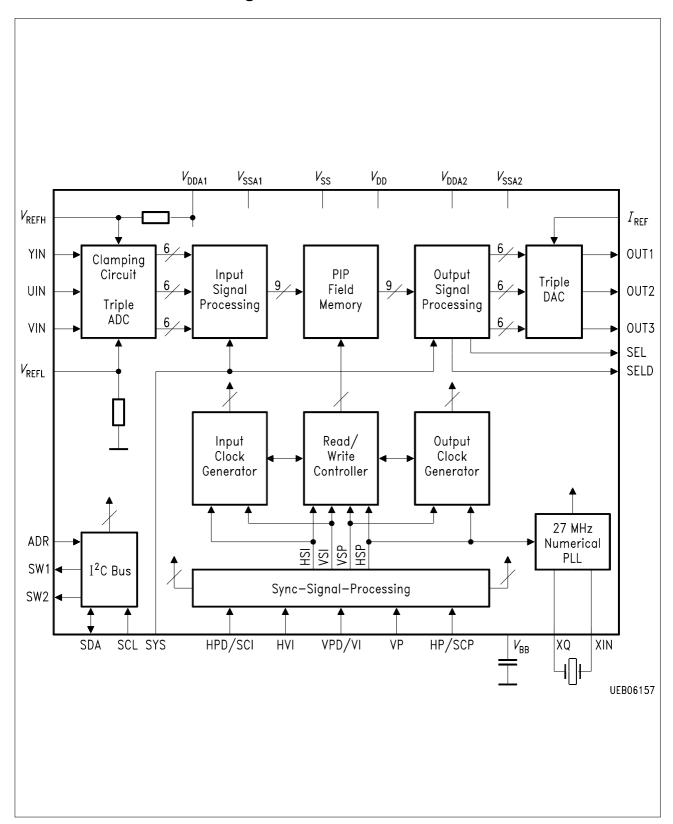

## 1.4 Functional Block Diagram

Figure 2

SIEMENS SDA 9288X

#### 2 System Description

#### 2.1 AD Conversion, Inset Synchronization

The inset video signal is fed to the SDA 9288X A141 as analog luminance and chrominance components<sup>1)</sup>. The polarity of the chrominance signals is programmable. After clamping the video components are AD-converted with an amplitude resolution of 6 bit. The conversion is done using a 13.5 MHz clock for the luminance signal and a 3.375 MHz clock for the chrominance signals.

For the adaption to different application the clamp timing for the analog inputs can be chosen (CLPS; CLPFIX). Setting this bits to '1' can be useful for non-standard input signals.

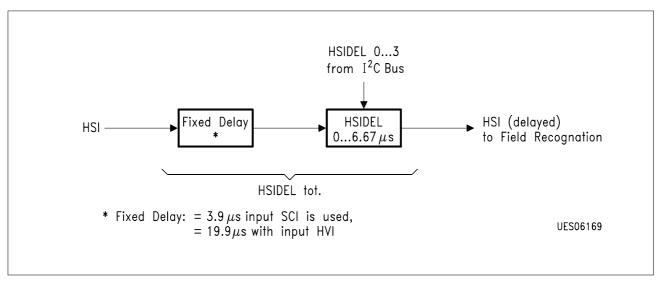

For inset synchronization it is possible to feed either a special 3-level signal via pin HVI (detection of horizontal and vertical pulses) or separate signals via pins SCI for horizontal and VI for vertical synchronization. SCI is the horizontal synchron signal of the inset channel. If the burst gate pulse of the sandcastle is used it must be adapted to TTL compatible levels by a simple external circuit. Centering of the displayed picture area is possible by a programmable delay for the horizontal synchronization signal (HSIDEL).

The inset horizontal synchronization signals are sampled with 27 MHz. This 27 MHz clock and the AD converter clocks are derived from the parent horizontal synchronization pulse (see **chapter 2.6**) or from the quartz frequency converted by a factor of 4/3.

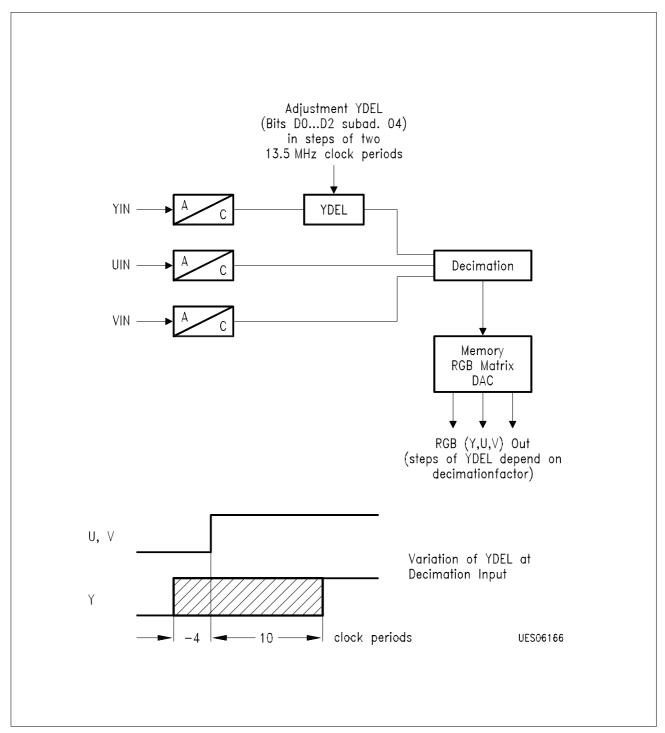

Delay differences between luminance and chrominance signals at the input of the IC caused by chroma decoding are compensated by a programmable luminance delay line (YDEL) of about  $-290 \text{ ns} \dots 740 \text{ ns}$  (at decimation input; see **Application Information**).

By analyzing the synchronization pulses the line standard of the inset signal source is detected and interference noise on the vertical sync signal is removed. For applications with fixed line standard (only 625 lines or 525 lines) the automatic detection can be switched off.

The phase of the vertical sync pulse is programmable (VSIDEL; VSPDEL). By this way a correct detection of the field number is possible, an important condition for frame mode display.

Note: The adjustment of VSIDEL is influenced by HSIDEL (see **chapter 4.3**), vertical synchronization via pin HVI causes an additional internal delay for the vertical sync pulse of about 16 µs.

Semiconductor Group 12 03.96

<sup>1)</sup> To improve the signal-to-noise ratio the amplitude of the input signals should be as large as possible.

#### 2.2 Input Signal Processing

This stage performs the decimation of the inset signal by horizontal and vertical filtering and sub-sampling. A special antialias filter improves the frequency response of the luminance channel. It is optimized for the use of the horizontal decimation factor 3:1.

A window signal, derived from the sync pulses and the detected line standard, defines the part of the active video area used for decimation. For HSIDEL = '0' the decimation window is opened about 104 clock periods (13.5 MHz) after the horizontal synchronization pulse. For the 625 lines standard the 36th video line is the first decimated line, for the 525 lines standard decimation starts in the 26th video line.

The following filters are implemented:

| Horizontal Decimation | Component   | Filter                         |

|-----------------------|-------------|--------------------------------|

| 3:1                   | Luminance   | $1 + z^{-1} + z^{-2}$          |

| 3:1                   | Chrominance | $1 + 2 \times z^{-1} + z^{-2}$ |

| 4:1                   | Luminance   | $1 + z^{-1} + z^{-2} + z^{-3}$ |

| 4:1                   | Chrominance | $1 + z^{-1} + z^{-2} + z^{-3}$ |

| Vertical Decimation | Component   | Filter                                 |

|---------------------|-------------|----------------------------------------|

| 3:1                 | Luminance   | 1 + z <sup>-L</sup> + z <sup>-2L</sup> |

| 3:1                 | Chrominance | $1 + 2 \times z^{-L} + z^{-2L}$        |

| 4:1                 | Luminance   | $1 + z^{-L} + z^{-2L} + z^{-3L}$       |

| 4:1                 | Chrominance | $1 + z^{-L} + z^{-2L} + z^{-3L}$       |

$z = e^{j\omega T}$ , T = 1/13.5 MHz for luminance T = 1/3.375 MHz for chrominance

The realized chrominance filtering allows omitting the color decoder delay line for PAL and SECAM demodulation if the color decoder supplies the same output voltages independent of the kind of operation. In case of SECAM signals an amplification of the chrominance signals by a factor of 2 is necessary because just every second line a signal is present. This chrominance amplification is programmable via pin SYS or I<sup>2</sup>C Bus (AMSEC).

The horizontal and vertical decimation factors are free programmable (DECHOR, DECVER). Using different decimations horizontal and vertical 16:9 applications become realizable:

DECHOR = '1', DECVER = '0': picture size 1/9 for 4:3 inset signals on 16:9 displays DECHOR = '0', DECVER = '1': picture size 1/16 for 16:9 inset signals on 4:3 displays

L = samples per line for luminance respectively chrominance

#### 2.3 PIP Field Memory

The on-chip memory stores one decimated field of the inset picture. Its capacity is 169 812 bits. The picture size depends on the horizontal and vertical decimation factors.

| <b>Horizontal Decimation</b> | PIP PIXELS per Line |       |       |

|------------------------------|---------------------|-------|-------|

|                              | Υ                   | (B-Y) | (R-Y) |

| 3:1                          | 212                 | 53    | 53    |

| 4:1                          | 160                 | 40    | 40    |

| <b>Vertical Decimation</b> | Line Standard | PIP Lines |

|----------------------------|---------------|-----------|

| 3:1                        | 625           | 88        |

| 3:1                        | 525           | 76        |

| 4:1                        | 625           | 66        |

| 4:1                        | 525           | 57        |

In field mode display just every second inset field is written into the memory, in frame mode display the memory is continuously written. Data are written with the lower inset clock frequency depending on the horizontal decimation factor (4.5 MHz or 3.375 MHz). Normally the read frequency is 13.5 MHz and 27 MHz for scan conversion systems. For progressive scan conversion systems and HDTV displays a line doubling mode is available (LINEDBL). Every line of the inset picture is read twice.

Memory writing can be stopped by program (FREEZE), a freeze picture display results (one field).

Having no scan conversion and the same line numbers in inset and parent channel (625 lines or 525 lines both) frame mode display is possible. The result is a higher vertical and time resolution because of displaying every incoming field. For this purpose the standards are internally analysed and activating of frame mode display is blocked automatically when the described restrictions are not fulfilled.

As in the inset channel a field number detection is carried out for the parent channel. Depending on the phase between inset and parent signals a correction of the display raster for the read out data is performed by omitting or inserting lines when the read address counter outruns the write address counter.

The display position of the inset picture is free programmable (POSHOR, POSVER). The first possible picture position (without frame) is 54 clock periods (13.5 MHz or 27 MHz) after the horizontal and 4 lines after the vertical synchronization pulses. Starting at this position the picture can be moved over the whole display area. Even POP-positions (Picture Outside Picture) at 16:9 applications are possible.

Having different line standards in inset and parent channels we have a so called mixed mode display. It causes deformations in the aspect ratio of the inset picture. A special mixed mode display is available for the picture size 1/9 (MIXDIS):

- Parent channel 625 lines, inset channel 525 lines: The inset picture is shifted down by 6 lines. By performing this shifting the centers of the inset pictures have the same position for both line standards.

- Parent channel 525 lines, inset channel 625 lines: The inset picture gets a reduced line number of 76. The first and the last 6 lines are omitted. This way the inset picture size is the same as for 525 lines inset signals. The display shows the center part of the original picture.

Synchronization of memory reading with the parent channel is achieved by processing the parent horizontal and vertical synchronization signals in the same way as described for the inset channel. The synchronization signals are fed to the IC at pin HP/SCP for horizontal synchronization and pin VP for vertical synchronization. In the same way as described for the inset channel the burst gate of the sandcastle signal can be used for horizontal synchronization. In scan conversion systems also the inputs HPD/SCI and VPD/VI are available if the input HVI is activated for inset synchronization.

## 2.4 Output Signal Processing

At the memory output the chrominance components are demultiplexed and linearly interpolated to the luminance sample rate.

Different output formats are available: luminance signal Y with inverted or non-inverted chrominance signals (B-Y), (R-Y) or RGB. For the RGB conversion 3 matrices are integrated:

| Standard     | B-Y | R-Y   | G-Y   | B-Y | R-Y  | G-Y  |

|--------------|-----|-------|-------|-----|------|------|

| EBU          | 1   | 0.558 | 0.345 | 0°  | 90°  | 237° |

| NTSC (Japan) | 1   | 0.783 | 0.31  | 0°  | 95°  | 240° |

| NTSC (USA)   | 1   | 1.013 | 0.305 | 0°  | 104° | 252° |

Matrix selection is done by pin SYS or I<sup>2</sup>C Bus. The matrices are designed for the following input voltages (100 % white, 75 % color saturation):

| Component | Input Voltage (without sync) in % of Full Scale Input Range of ADC |

|-----------|--------------------------------------------------------------------|

| Y         | 75                                                                 |

| B-Y       | 100                                                                |

| R-Y       | 100                                                                |

#### 2.4.1 Matrix Equations

**EBU**

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 \\ 0 & 0.78125 & 1 \\ -0.1875 & -0.40625 & 1 \end{bmatrix} \begin{bmatrix} B - Y \\ R - Y \\ Y \end{bmatrix}$$

#### NTSC (Japan)

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 \\ -0.0625 & 1.09375 & 1 \\ -0.15625 & -0.375 & 1 \end{bmatrix} \begin{bmatrix} B - Y \\ R - Y \\ Y \end{bmatrix}$$

# NTSC (USA)

$$\begin{bmatrix} R \\ G \\ B \end{bmatrix} = \begin{bmatrix} 1 & 0 & 1 \\ -0.25 & 1.375 & 1 \\ -0.09375 & -0.40625 & 1 \end{bmatrix} \begin{bmatrix} B - Y \\ R - Y \\ Y \end{bmatrix}$$

#### 2.4.2 Frame Insertion

A colored frame is added to the inset picture. 4096 frame colors are programmable, 4 bits for each component Y, (B-Y), (R-Y) (bits FRY, FRU, FRV). The horizontal and

vertical width of the frame are independently programmable. Width = 0 means display without frame.

### **Examples for the Adjustment of Frame Colors**

| Frame   | FRY                    | FRU                    | FRV                    |

|---------|------------------------|------------------------|------------------------|

| Color   | D3 D0 of Subaddress 09 | D3 D0 of Subaddress 0A | D7 D4 of Subaddress 0A |

| Blue    | 0100                   | 0110                   | 1010                   |

| Green   | 0100                   | 1000                   | 1010                   |

| White   | 1100                   | 0000                   | 0000                   |

| Red     | 0100                   | 1000                   | 0111                   |

| Yellow  | 1100                   | 1000                   | 0100                   |

| Cyan    | 1100                   | 0010                   | 1010                   |

| Magenta | 0100                   | 0110                   | 0100                   |

# 2.4.3 Select Signal

For controlling an external switch (for example an RGB processor) a select signal is supplied. Pin SEL is active in normal 13.5 MHz reading mode, pin SELD is active using 27 MHz. The phases of these signals are programmable for adaption to different external output signal processing.

#### 2.5 DA Conversion

The SDA 9288X A141 includes three 6-bit DA converters. Each converter supplies a current through an external resistor that is connected between  $V_{\rm SSA}$  and OUT1, OUT2, OUT3 respectively. The current is controlled by a digital control circuit. Each command DACONST or PIPON starts the adjustment cycle.

#### 2.6 PLL

A numerical PLL circuit supplies a clock of about 27 MHz with high stability. The generated clock is locked to the parent horizontal synchronization pulse. Its frequency depends linearly on the frequency of the sync signal and the quartz frequency. The recommended quartz frequencies are listed under 'Recommended Operation Conditions'. Using up to three SDA 9288X A141 ICs in one application only a single quartz is necessary. Four time constants are programmable via I<sup>2</sup>C Bus. If the PLL is switched off an external 27 MHz parent line locked clock can be fed to the IC.

The inset clock generation is possible in two ways:

- 1. Synchron with the parent horizontal synchronization pulse (bit CLISW = '0')

- 2. Synchron with the quartz frequency (bit CLISW = '1';  $f_{cli} = 4/3 \times f_{quartz}$ ). In this mode the aspect ratio is independent on the parent sync frequency but depends on the used resonator type. It is only possible to use one of the two modes.

Note: Before setting bit D3 of subaddress 00 (READ27) noise reduction of the VSP pulse must be switched off (D5 of subaddress 08 = '1').

#### 2.7 I<sup>2</sup>C Bus

#### 2.7.1 I<sup>2</sup>C Bus Addresses

Three different I<sup>2</sup>C addresses are programmable via pin ADR.

| Pin ADR                                      | Address (bin.) | Address (hex.) |

|----------------------------------------------|----------------|----------------|

| Low level ( $V_{\rm SS}$ or $V_{\rm SSA}$ )  | 11010110       | D6             |

| Mid level (open)                             | 11011100       | DC             |

| High level ( $V_{\rm DD}$ or $V_{\rm DDA}$ ) | 11011110       | DE             |

#### 2.7.2 I<sup>2</sup>C Bus Receiver Format

| S | Address | Α | Subaddress | Α | Data Byte | Α | **** | Α | Р |

|---|---------|---|------------|---|-----------|---|------|---|---|

|---|---------|---|------------|---|-----------|---|------|---|---|

S: start condition A: acknowledge P: stop condition

Only write operation is possible. An automatically address increment function is implemented.

### 2.7.3 I<sup>2</sup>C Bus Commands

| Sub-<br>addr. | Data Bytes |         |         |         |         |         |         |         |

|---------------|------------|---------|---------|---------|---------|---------|---------|---------|

| Hex           | D7         | D6      | D5      | D4      | D3      | D2      | D1      | D0      |

| 00            | 0          | SYSACT  | FREEZE  | PLLOFF  | READ27  | LINEDBL | FRAME   | PIPON   |

| 01            | 0          | SELDEL3 | SELDEL2 | SELDEL1 | SELDEL0 | MIXDIS  | POSHOR9 | POSHOR8 |

| 02            | POSHOR7    | POSHOR6 | POSHOR5 | POSHOR4 | POSHOR3 | POSHOR2 | POSHOR1 | POSHOR0 |

| 03            | POSVER7    | POSVER6 | POSVER5 | POSVER4 | POSVER3 | POSVER2 | POSVER1 | POSVER0 |

| 04            | 0          | SW21    | SW20    | SW11    | SW10    | YDEL2   | YDEL1   | YDEL0   |

| 05            | DECVER     | DECHOR  | INSHVI  | CHRINS  | PMOD1   | PMOD0   | IMOD1   | IMOD0   |

| 06            | 0          | CLPS    | CLPFIX  | CLISW   | HSIDEL3 | HSIDEL2 | HSIDEL1 | HSIDEL0 |

| 07            | AMSEC      | 0       | VSIISQ  | VSIDEL4 | VSIDEL3 | VSIDEL2 | VSIDEL1 | VSIDEL0 |

| 80            | PARSYND    | 0       | VSPISQ  | VSPDEL4 | VSPDEL3 | VSPDEL2 | VSPDEL1 | VSPDEL0 |

| 09            | CON3       | CON2    | CON1    | CON0    | FRY5    | FRY4    | FRY3    | FRY2    |

| 0A            | FRV5       | FRV4    | FRV3    | FRV2    | FRU5    | FRU4    | FRU3    | FRU2    |

| 0B            | 0          | 0       | SELDOWN | FRWIDV1 | FRWIDV0 | FRWIDH2 | FRWIDH1 | FRWIDH0 |

| 0C            | 0          | 0       | 0       | MAT2    | MAT1    | MAT0    | CHRPIP  | OUTFOR  |

| 0D            | DACONST    | PLLTC1  | PLLTC2  | 0       | 0       | 0       | 0       | 0       |

After switching on the IC the data bytes of all registers are set to '0', the bit PLLOFF is set to '1'.

| Bit   | Name     | Function                                                                                                                                                                                                                          |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subad | dress 00 |                                                                                                                                                                                                                                   |

| D0    | PIPON    | 0: PIP insertion OFF  1: PIP insertion ON                                                                                                                                                                                         |

| D1    | FRAME    | O: field display  1: frame display (under special restrictions).  Correct adjustment of bits VSIDEL, VSPDEL required (see chapter 4.3)                                                                                            |

| D2    | LINEDBL  | each line of the PIP memory is read once (normal operation)     each line of the PIP memory is read twice (line doubling for progressive scan conversion systems in parent channel)                                               |

| D3    | READ27   | <ul><li>0: PIP display with single read frequency (13.5 MHz)</li><li>1: PIP display with double read frequency (27 MHz) (see note page 19).</li></ul>                                                                             |

| D4    | PLLOFF   | internal PLL ON     internal PLL OFF (external clock generation)                                                                                                                                                                  |

| D5    | FREEZE   | 0: live picture 1: freeze picture                                                                                                                                                                                                 |

| D6    | SYSACT   | <ul> <li>0: pin SYS inactive: selection of decimation amplification and RGB-matrix is done via I<sup>2</sup>C Bus</li> <li>1: pin SYS active: selection of decimation amplification and RGB-matrix is done via pin SYS</li> </ul> |

### **Subaddress 01**

| D1 D0 | POSHOR | 2 MSBs of POSHOR (see also subaddress 02)                                                                                                                                                                                                      |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D2    | MIXDIS | <ul> <li>0: PIP picture height depends just upon inset line standard, position upon POSHOR</li> <li>1: modified PIP picture height and position for different inset and parent line standards (mixed display mode)</li> </ul>                  |

| D6 D3 | SELDEL | Delay of output signal SELECT at pins SEL respectively SELD (-8 7 periods of read frequency clock, programmable in 2's complement code). SELDEL = '0': SELECT signal has the same phase as the PIP picture signal referenced to the IC output. |

| Bit      | Name   | Function                                                                                                                                                                                                                                                       |

|----------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subaddre | ess 02 |                                                                                                                                                                                                                                                                |

| D7 D0    | POSHOR | Horizontal position of PIP picture (raster: 1 pixel)  Note: The 2 MSBs of POSHOR are located at subaddress 01                                                                                                                                                  |

|          |        | Warning: It is not allowed to adjust positions < 2 and > 740.  Note: To avoid horizontal jumping of the picture by changing POSHOR from '00 1111 1111' to '01 0000 0000' its necessary to transfer the bits of both subaddresses during the same field period. |

| Subaddre | ess 03 |                                                                                                                                                                                                                                                                |

| D7 D0    | POSVER | Vertical position of PIP picture (raster: 1 line)  Warning: It is not allowed to adjust positions > 220 (50 Hz) or > 182 (60 Hz).                                                                                                                              |

| Subaddre | ess 04 |                                                                                                                                                                                                                                                                |

| D2 D0    | YDEL   | Delay of luminance input signal 000: minimum delay 111: maximum delay; see <b>chapter 4.2</b>                                                                                                                                                                  |

| D4 D3    | SW1    | Direct control of output pin SW1 (3 levels) 00: low level 01: mid level 10: high level 11: high level                                                                                                                                                          |

| D6 D5    | SW2    | Direct control of output pin SW2 (3 levels) 00: low level 01: mid level 10: high level 11: high level                                                                                                                                                          |

| Bit      | Name   | Function                                                                                                                                                                                                                      |

|----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subaddre | ess 05 |                                                                                                                                                                                                                               |

| D1 D0    | IMOD   | <ul> <li>00: automatic detection of line standard (inset signal)</li> <li>01: fixed adjustment 625 lines<sup>1)</sup></li> <li>10: fixed adjustment 525 lines<sup>1)</sup></li> <li>11: freeze last line standard</li> </ul>  |

| D3 D2    | PMOD   | <ul> <li>00: automatic detection of line standard (parent signal)</li> <li>01: fixed adjustment 625 lines<sup>1)</sup></li> <li>10: fixed adjustment 525 lines<sup>1)</sup></li> <li>11: freeze last line standard</li> </ul> |

| D4       | CHRINS | 0: chrominance input signals + (B-Y), + (R-Y) 1: inverted chrominance input signals – (B-Y), – (R-Y)                                                                                                                          |

| D5       | INSHVI | <ul><li>0: inset synchronization signals via pins HPD/SCI and VPD/VI</li><li>1: inset synchr. signals via pin HVI (3-I. sand-castle signal)</li></ul>                                                                         |

| D6       | DECHOR | horizontal decimation 3 to 1     horizontal decimation 4 to 1                                                                                                                                                                 |

| D7       | DECVER | vertical decimation 3 to 1     vertical decimation 4 to 1                                                                                                                                                                     |

#### Subaddress 06

| D3 D0 | HSIDEL | Delay of horizontal synchronization pulse (inset signal) Raster: 6 clock periods of 13.5 MHz.  Warning: Adjustment of HSIDEL will influence the adjustment of VSIDEL (subaddr. 07); see chapter 4.3 |

|-------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D4    | CLISW  | 0: inset clock synchronized with parent clock 1: inset clock synchronized with quartz frequency Note: Only one of the two modes can be used. Switching back from '1' to '0' is not possible!        |

| D5    | CLPFIX | clamp pulses of ADC are dependent on the adjustment of HSIDEL     clamp pulses fixed; no influence of HSIDEL                                                                                        |

| D6    | CLPS   | three clamp cycles per line (timing see diagram)     two clamp cycles per line                                                                                                                      |

<sup>&</sup>lt;sup>1)</sup> Fixed adjustments for IMOD and PMOD result in undefined working conditions when signal standards are used which are different from the programmed values.

| Bit      | Name          | Function                                                                                                                                                                                 |  |  |  |

|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Subaddre | Subaddress 07 |                                                                                                                                                                                          |  |  |  |

| D4 D0    | VSIDEL        | Delay of vertical synchronization pulse (inset signal) in steps of 2.37 μs.  Warning: Correct adjustment value is influenced by the adjustment of HSIDEL (subaddr. 06); see chapter 4.3. |  |  |  |

| D5       | VSIISQ        | Noise reduction of the VSI pulse (set to '0' under normal conditions)                                                                                                                    |  |  |  |

| D7       | AMSEC         | <ul><li>0: unity amplification of decimation filters (normal mode)</li><li>1: amplification by a factor of 2 (SECAM signals without delay line in the chroma decoder)</li></ul>          |  |  |  |

### Subaddress 08

| D4 D0 | VSPDEL  | Delay of vertical synchronization pulse (parent signal) in steps of 2.37 μs/1.68 s (50/100 Hz)                                                                                                                                  |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5    | VSPISQ  | Noise reduction of the VSP pulse (should be set to '0' under<br>normal conditions); in case changing from standard mode to<br>line or frame conversion modes '1' should be set during the<br>changement of line frequency       |

| D7    | PARSYND | <ul> <li>0: parent synchronization signals for double frequency read via pins HP/SCP and VP</li> <li>1: parent synchronization signals for double frequency read via pins HPD/SCI and VPD/VI (INSHVI = '1' required)</li> </ul> |

### Subaddress 09

| D3 D0 | FRY | Luminance component of frame color (4 MSBs of 6 bit)                                                                                             |

|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| D7 D4 | CON | Contrast adjustment of PIP picture; steps and adjustment range depending on the external output resistors. Proposed value see <b>chapter 3.3</b> |

#### Subaddress 0A

| D3 D0 | FRU | Chrominance component (B-Y) of frame color (4 MSBs of 6 bit) |

|-------|-----|--------------------------------------------------------------|

| D7 D4 | FRV | Chrominance component (R-Y) of frame color (4 MSBs of 6 bit) |

| Bit | Name    | Function |

|-----|---------|----------|

|     | 1101110 |          |

### Subaddress 0B

| D2 D0 | FRWIDH | Horizontal width of PIP frame (0 7 pixels)                            |  |  |  |  |  |  |

|-------|--------|-----------------------------------------------------------------------|--|--|--|--|--|--|

| D4 D3 | FRWIDV | Vertical width of PIP frame (0 3 lines)                               |  |  |  |  |  |  |

| D5    |        | open source output at pins SEL, SELD     TTL output at pins SEL, SELD |  |  |  |  |  |  |

#### Subaddress 0C

| D0 | OUTFOR | <ul><li>0: format of output signals: Y, (B-Y), (R-Y)</li><li>1: format of output signals: R G B</li></ul>                             |

|----|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| D1 | CHRPIP | <ul> <li>0: chrominance output signals: + (B-Y), + (R-Y)</li> <li>1: inverted chrominance output signals: - (B-Y), - (R-Y)</li> </ul> |

| D2 | MAT0   | EBU RGB-matrix     NTSC RGB-matrix                                                                                                    |

| D3 | MAT1   | preselection of NTSC RGB matrix (USA)     preselection of NTSC RBG matrix (Japan)                                                     |

| D4 | MAT2   | matrix selection by bit MAT0     automatic matrix selection depending on inset line standard                                          |

### Subaddress 0D

| D0 | DACONDE | Set to '0'                                                                                                                                                                                      |

|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D5 | PLLTC2  | Time constant of internal PLL: 00: medium damping, low resonance frequency 01: medium damping, high resonance frequency                                                                         |

| D6 | PLLTC1  | <ul><li>10: high damping, low resonance frequency</li><li>11: high damping, high resonance frequency</li><li>Note: After power ON PLLTC must remain at 00 until the system is locked.</li></ul> |

| D7 | DACONST | Changing from '0' to '1' starts automatic adjustment of OUT1 3 output current (switching PIPON gives the same result).                                                                          |

#### 3 Electrical Characteristics

### 3.1 Absolute Maximum Ratings

| Parameter                    | Symbol     | Limit Values |                         | Unit | Remark                                                              |

|------------------------------|------------|--------------|-------------------------|------|---------------------------------------------------------------------|

|                              |            | min.         | max.                    |      |                                                                     |

| Ambient temperature          | $T_{A}$    | 0            | 70                      | °C   |                                                                     |

| Storage temperature          | $T_{stg}$  | - 55         | 125                     | °C   |                                                                     |

| Junction temperature         | $T_{j}$    |              | 125                     | °C   |                                                                     |

| Soldering temperature        | $T_{SOLD}$ |              | 260                     | °C   | Duration < 10 s                                                     |

| Input voltage                | $V_1$      | - 0.5 V      | V <sub>DD</sub> + 0.5 V | 1    | Analog inputs (YIN, UIN, VIN, $I_{\text{REF}}$ )                    |

|                              | $V_{l}$    | <b>-</b> 1   | 7                       | V    | All other pins                                                      |

| Output voltage               | $V_{Q}$    | - 0.5 V      | V <sub>DD</sub> + 0.5 V | 1    | Pins OUT1, OUT2,<br>OUT3, XQ, SW1,<br>SW2                           |

|                              | $V_{Q}$    | <b>-</b> 1   | 7                       | V    | All other pins                                                      |

| Supply voltages              | $V_{DD}$   | <b>-</b> 1   | 7                       | V    |                                                                     |

| Supply voltage differentials | $V_{DDD}$  | - 0.25       | 0.25                    | V    |                                                                     |

| Total power dissipation      | $P_{tot}$  |              | 900                     | mW   |                                                                     |

| Latch-up protection          |            | - 100        | 100                     | mA   | Except pins OUT1, OUT2, OUT3, $I_{\rm REF}$ , XQ, XQ, YIN, UIN, VIN |

Note: All voltages listed are referenced to ground (0 V,  $V_{\rm SS}$ ) except where noted. Stresses above those listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

03.96

## 3.2 Operational Range

| Parameter           | Symbol     | Limit Values |      |      | Unit | Remark |

|---------------------|------------|--------------|------|------|------|--------|

|                     |            | min.         | typ. | max. |      |        |

| Supply voltages     | $V_{DDxx}$ | 4.75         | 5    | 5.5  | V    |        |

| Ambient temperature | $T_{A}$    | 0            | 25   | 70   | °C   |        |

### **All TTL Inputs**

| Low-level input voltage  | $V_{IL}$ | <b>–</b> 1 | 0.8 | V |  |

|--------------------------|----------|------------|-----|---|--|

| High-level input voltage | $V_{IH}$ | 2.0        | 6   | V |  |

## All Three Level Inputs (3-L) (see figure)

| High-level input voltage | $V_{IH}$ | 3.5        | 6   | V |                                    |

|--------------------------|----------|------------|-----|---|------------------------------------|

| Low-level input voltage  | $V_{IL}$ | <b>–</b> 1 | 0.8 | V |                                    |

| Medium-level voltage     | $V_{IM}$ |            |     |   | Open input, see <b>chapter 3.3</b> |

### All 3-L Outputs (see figure)

| High-level output current | $I_{OH}$ | - 500 | 0   | μΑ |  |

|---------------------------|----------|-------|-----|----|--|

| Low-level output current  | $I_{OL}$ | 0     | 1.6 | mA |  |

# Inset Horizontal Sync TTL and 3-L Inputs: HPD/SCI, HVI<sup>1)</sup>

| Horizontal frequency      | 14.53 | 16.72 | kHz |                                  |

|---------------------------|-------|-------|-----|----------------------------------|

| Signal rise time          |       | 100   | ns  | Noisefree L/M-to-H<br>transition |

| Signal high time          | 100   |       | ns  |                                  |

| Signal medium or low time | 900   |       | ns  |                                  |

$<sup>\</sup>overline{}^{1)}$  All values are referred to the corresponding min  $(V_{\rm IH})$ , max  $(V_{\rm IM})$  and max  $(V_{\rm IL})$

#### Operational Range (cont'd) 3.2

| Parameter | Symbol | Limit Values |      |      | Unit | Remark |

|-----------|--------|--------------|------|------|------|--------|

|           |        | min.         | typ. | max. |      |        |

#### Inset Vertical Sync TTL and 3-L Inputs: VPD/VI, HVI<sup>1)</sup>

| Signal medium or high time | 17  |  | μs | Necessary for vertical sync detection |

|----------------------------|-----|--|----|---------------------------------------|

| Signal low time            | 200 |  | ns |                                       |

#### Parent Horizontal Sync TTL Inputs: HP/SCP, HPD/SCI<sup>2)</sup>

| Sync frequency in single frequency | 14.53 | 16.72  | kHz | Quartz frequency<br>20.480 MHz |

|------------------------------------|-------|--------|-----|--------------------------------|

| display mode                       | 15    | 17.19  | kHz | Quartz frequency<br>21.090 MHz |

| Sync frequency in double frequency | 29.06 | 33.44  | kHz | Quartz frequency<br>20.480 MHz |

| display mode                       | 30    | 34.375 | kHz | Quartz frequency<br>21.090 MHz |

| Signal rise time                   |       | 100    | ns  | Noisefree transition           |

| Signal high time                   | 100   |        | ns  |                                |

| Signal low time                    | 900   |        | ns  |                                |

# Parent Vertical Sync TTL Input VDP/VI<sup>2)</sup>

| Signal HIGH time | 200 | ns |  |

|------------------|-----|----|--|

| Signal LOW time  | 200 | ns |  |

All values are referred to the corresponding min  $(V_{\rm IH})$ , max  $(V_{\rm IM})$  and max  $(V_{\rm IL})$  All values are referred to the corresponding min  $(V_{\rm IH})$  and max  $(V_{\rm IL})$

## 3.2 Operational Range (cont'd)

| Parameter | Symbol | Limit Values   |  | Unit | Remark |

|-----------|--------|----------------|--|------|--------|

|           |        | min. typ. max. |  |      |        |

#### Quartz/Ceramic Resonator<sup>2)</sup>

| Recommended frequency | 20.25 | 20.48 | 21.3 | MHz | 21.09 MHz for MUSE                                            |

|-----------------------|-------|-------|------|-----|---------------------------------------------------------------|

| Series resistance     |       |       | 10   | Ω   | $C_1, C_2 \le 33 \text{ pF}$                                  |

|                       |       |       | 20   | Ω   | $C_1, C_2 \le 22 \text{ pF}$                                  |

|                       |       |       | 30   | Ω   | $C_1, C_2 \le 15 \text{ pF}$                                  |

|                       |       |       | 40   | Ω   | $C_1$ , $C_2 \le 10 \text{ pF}$<br>(total series capacitance) |

# Optional TTL Clock Input: XIN¹)

| Clock input cycle time | 35 | 40 | ns | External line locked;<br>27 MHz clock<br>(I <sup>2</sup> C: internal PLL<br>OFF) |

|------------------------|----|----|----|----------------------------------------------------------------------------------|

| Clock input rise time  |    | 5  | ns |                                                                                  |

| Clock input fall time  |    | 5  | ns |                                                                                  |

| Clock input low time   | 10 |    | ns |                                                                                  |

| Clock input high time  | 10 |    | ns |                                                                                  |

#### Fast I<sup>2</sup>C Bus<sup>1) 3)</sup>

| SCL clock frequency                        | $f_{	t SCL}$         | 0   | 400 | kHz |  |

|--------------------------------------------|----------------------|-----|-----|-----|--|

| Inactive time before start of transmission | $t_{BUF}$            | 1.3 |     | μs  |  |

| Setup time start condition                 | t <sub>SU; STA</sub> | 0.6 |     | μs  |  |

| Hold time start condition                  | t <sub>HD; STA</sub> | 0.6 |     | μs  |  |

| SCL low time                               | $t_{LOW}$            | 1.3 |     | μs  |  |

<sup>&</sup>lt;sup>1)</sup> All values are referred to min  $(V_{IH})$  and max  $(V_{IL})$ .

<sup>&</sup>lt;sup>2)</sup> There is no internal protection for the crystal driver against oscillation at harmonic frequencies.

<sup>&</sup>lt;sup>3)</sup> This specification of the bus lines does not have to be identical with the I/O stages specification because of optional series resistors between bus lines and I/O pins.

# **3.2** Operational Range (cont'd)

| Parameter                 | Symbol               | ool Limit Values |      |      | Unit | Remark          |

|---------------------------|----------------------|------------------|------|------|------|-----------------|

|                           |                      | min.             | typ. | max. |      |                 |

| SCL high time             | $t_{HIGH}$           | 0.6              |      |      | μs   |                 |

| Setup time data           | t <sub>SU; DAT</sub> | 100              |      |      | ns   |                 |

| Hold time data            | $t_{HD;DAT}$         | 0                |      | 0.9  | μs   |                 |

| SDA/SCL rise/fall times   | $t_{R},t_{F}$        | 20 + \$          |      | 300  | ns   | $$ = 0.1C_b/pF$ |

| Setup time stop condition | $t_{ m SU;STO}$      | 0.6              |      |      | μs   |                 |

| Capacitive load/bus line  | $C_{b}$              |                  |      | 400  | pF   |                 |

# I<sup>2</sup>C Bus Inputs/Output: SDA, SCL

| High-level input voltage | $V_{IH}$ | 3     |   | V <sub>DD</sub> + 0.5 | V  | Also for SDA/SCL input stages |

|--------------------------|----------|-------|---|-----------------------|----|-------------------------------|

| Low-level input voltage  | $V_{IL}$ | - 0.5 |   | 1.5                   | V  |                               |

| Spike duration at inputs |          | 0     | 0 | 50                    | ns |                               |

| Low-level output current | $I_{OL}$ |       |   | 6                     | mA |                               |

# **Analog to Digital Converters (6 bit)**

| Input coupling capacitors    |                         | 10  | 100 |     | nF | Necessary for proper clamping                                                           |

|------------------------------|-------------------------|-----|-----|-----|----|-----------------------------------------------------------------------------------------|

| Y, U, V source resistance    |                         |     |     | 1   | kΩ |                                                                                         |

| Reference voltage low        | $V_{REFL}$              | 0.5 | 1.0 | 1.5 | V  | Min and max values only with optional external resistors, see also <b>chapter 3.3</b> . |

| Reference voltage high       | $V_{REFH}$              | 1.5 | 2.0 | 2.5 | V  |                                                                                         |

| Reference voltage difference | $V_{REFH}$ – $V_{REFL}$ | 0.5 | 1.0 | 2   | V  |                                                                                         |

# 3.2 Operational Range (cont'd)

| Parameter | Symbol | Limit Values   |  | Unit | Remark |

|-----------|--------|----------------|--|------|--------|

|           |        | min. typ. max. |  |      |        |

## **Digital-to-Analog Converters (6 bit)**

| Full range output voltage | $V_{OFR}$  |     | 1   | 2   | V  | Peak to peak                                         |

|---------------------------|------------|-----|-----|-----|----|------------------------------------------------------|

| Reference resistance      | $R_{REF1}$ | 4.2 | 5.1 | 6.3 | kΩ | Bits CON = '0000';<br>no contrast<br>adjustment used |

|                           | $R_{REF2}$ | 6.0 | 6.8 | 7.5 | kΩ | Contrast adjustment via I <sup>2</sup> C Bus         |

Note: In the operational range the functions given in the circuit description are fulfilled.

## 3.3 Characteristics

| Parameter                      | Symbol      | Limit Values |      | Unit | Remark                                                                 |

|--------------------------------|-------------|--------------|------|------|------------------------------------------------------------------------|

|                                |             | min.         | max. |      |                                                                        |

| Average total supply current   | $I_{DDtot}$ |              | 160  | mA   | $I_{\text{DDtot}} = I_{\text{DD}} + I_{\text{DDA1}} + I_{\text{DDA2}}$ |

| Average digital supply current | $I_{DD}$    |              | 120  | mA   | Note: The maxima do                                                    |

| Average analog supply current  | $I_{DDA1}$  |              | 40   | mA   | not necessarily coincide.                                              |

| Average analog supply current  | $I_{DDA2}$  |              | 20   | mA   | comerciae.                                                             |

# All Digital Inputs (TTL, I<sup>2</sup>C)

| Input capacitance     | $C_{I}$ |      | 7  | pF  | Not tested                                    |

|-----------------------|---------|------|----|-----|-----------------------------------------------|

| Input leakage current |         | - 10 | 10 | . • | Including leakage current of SDA output stage |

## All Three Level Inputs (3-L) (see figure)

| Input capacitance               | $C_{I}$  |     | 7   | pF | Not tested                                                        |

|---------------------------------|----------|-----|-----|----|-------------------------------------------------------------------|

| Medium-level open input voltage | $V_{IM}$ | 2.1 | 2.5 | V  | $ I_{\text{IN}}  \le 1 \mu\text{A}, \ V_{\text{DD}} = 5 \text{V}$ |

| Differential input resistance   | $R_{IN}$ | 8   | 14  | kΩ | Not tested                                                        |

# SEL, SELD

| High-level output voltage | $V_{OH}$ | 2.4 V | $V_{	extsf{DD}}$ | V  | $I_{OH} = -200  \mu A$                                 |

|---------------------------|----------|-------|------------------|----|--------------------------------------------------------|

| High-level output voltage | $V_{OH}$ | 1.5 V | $V_{	extsf{DD}}$ | V  | $I_{\rm OH} = -4.5 \; {\rm mA}$                        |

| Low-level output voltage  | $V_{OL}$ |       | 0.4              | V  | $I_{\rm OL}$ = 1.6 mA, only valid if bit SELDOWN = '1' |

| Leakage current           |          | - 10  |                  | Α  | $V_{\rm O}$ = 0 V $V_{\rm DD}$                         |

| Output capacitance        |          |       | 7                | pF | Not tested                                             |

# **All 3-L Outputs**

| High-level output voltage | $V_{OH}$ | 4   |     | V | $I_{OH} = -100  \mu A$ |

|---------------------------|----------|-----|-----|---|------------------------|

| High-level output voltage | $V_{OH}$ | 3.9 |     | V | $I_{OH} = -500  \mu A$ |

| Low-level output voltage  | $V_{OL}$ |     | 0.4 | V | $I_{\text{OL}} = \max$ |

## 3.3 Characteristics (cont'd)

| Parameter                           | Symbol   | Limit Values |      | Unit | Remark     |

|-------------------------------------|----------|--------------|------|------|------------|

|                                     |          | min.         | max. |      |            |

| Medium-level output leakage current | $I_{OM}$ | <b>– 1</b>   | 1    | μΑ   | Tristate   |

| Output capacitance                  |          |              | 7    | pF   | Not tested |

## I<sup>2</sup>C Inputs: SDA/SCL

| Schmitt trigger hysteresis | $V_{hvs}$ | 0.2 | V | Not tested |

|----------------------------|-----------|-----|---|------------|

|                            | ,-        |     |   |            |

### I<sup>2</sup>C Input/Output: SDA (referenced to SCL; open drain output)

| Low-level output voltage                                       | $V_{OL}$ |                          | 0.4 | V  | $I_{\rm OL}$ = 3 mA                |

|----------------------------------------------------------------|----------|--------------------------|-----|----|------------------------------------|

| Low-level output voltage                                       | $V_{OL}$ |                          | 0.6 | V  | $I_{OL} = max$                     |

| Output fall time from min $(V_{\rm IH})$ to max $(V_{\rm IL})$ | $t_{OF}$ | $20 + 0.1 \times C_b/pF$ | 250 | ns | 10 pF $\leq C_{\rm b} \leq$ 400 pF |

# **Analog-to-Digital Converters (6 bit)**

| Y, U, V input leakage current |                         | <b>– 100</b>   | 100             | nA             |                                                                                                        |

|-------------------------------|-------------------------|----------------|-----------------|----------------|--------------------------------------------------------------------------------------------------------|

| Y, U, V input capitance       |                         |                | 7               | pF             | Not tested                                                                                             |

| Input clamping error          |                         | - 1            | 1               | LSB            | Settled state                                                                                          |

| Input clamping current        | $ I_{CLP} $             | 15<br>40<br>70 | 50<br>90<br>150 | μΑ<br>μΑ<br>μΑ | Deviation < 1 LSB Deviation 1 2 LSB Deviation > 2 LSB                                                  |

| Reference voltage difference  | $V_{REFH}$ – $V_{REFL}$ | 0.98           | 1.02            | V              | $V_{\mathrm{DDA}} = \mathrm{nom},$ $(V_{\mathrm{REFH}} - V_{\mathrm{REFL}} \cong V_{\mathrm{DDA1}}/5)$ |

# Digital-to-Analog Converters (6 bit): Current Source Outputs OUT1, OUT2, OUT31)

| D.C. differential nonlinearity | DNLE    | - 0.5      | 0.5        | LSB | $R_{\rm REF}$ = 5.1 k $\Omega$                                                                                                                                     |

|--------------------------------|---------|------------|------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Full range output current      | $I_{O}$ | - 1.4<br>2 | - 1.7<br>3 | l   | $V_{\mathrm{DDA}} = \mathrm{max}, \ T_{\mathrm{A}} = \mathrm{nom},$ $R_{\mathrm{REF}} = 5.1 \ \mathrm{k}\Omega,$ $R_{\mathrm{L}} = 680 \ \Omega,$ after adjustment |

### 3.3 Characteristics (cont'd)

| Parameter                                                                                             | Symbol | Limit | Values | Unit | Remark                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------|--------|-------|--------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                       |        | min.  | max.   |      |                                                                                                                                                                                          |

| Output voltage $(V_{\text{ON}} \text{ 1.6} \times V_{\text{DDA}} \times R_{\text{L}}/R_{\text{REF}})$ | Vo     | 0.96  | 1.18   | V    | $V_{\rm DDA} = {\rm max},  T_{\rm A} = {\rm nom},$ $R_{\rm L} = 680  \Omega,$ $R_{\rm REF} = 5.1  {\rm k}\Omega,$ after adjustment                                                       |

| Tracking                                                                                              |        | - 3   | 3      | %    | $V_{ m DDA} = { m max},  T_{ m A} = { m nom}, \ R_{ m REF} = 5.1 \ { m k}\Omega, \ R_{ m L} = 680 \ \Omega$                                                                              |

| Contrast increase                                                                                     |        | 30    |        | %    | $V_{\rm DDA}$ = nom, $T_{\rm A}$ = nom, $R_{\rm L}$ = 680 $\Omega$ , $R_{\rm REF}$ = 6.8 k $\Omega$ , contrast bits change from '0000' to '1111' for typical values see <b>chapter 4</b> |

| Supply voltage dependence of DAC output current                                                       |        |       |        |      | For typical values see <b>chapter 4</b>                                                                                                                                                  |

| Temperature dependence of DAC output current                                                          |        |       |        |      | For typical values see <b>chapter 4</b>                                                                                                                                                  |

| Dependence of DAC output current on external reference resistor                                       |        |       |        |      | For typical values see <b>chapter 4</b>                                                                                                                                                  |

<sup>&</sup>lt;sup>1)</sup> I<sup>2</sup>C: Contrast bits set to zero unless otherwise noted.

Note: The listed characteristics are ensured over the operating range of the integrated circuit unless restricted to nominal operating conditions (all voltages refer to  $V_{\rm SS}$ ). The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specify mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_{\rm A}$  = 25°C and the given supply voltage.

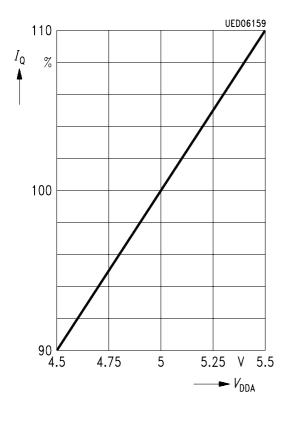

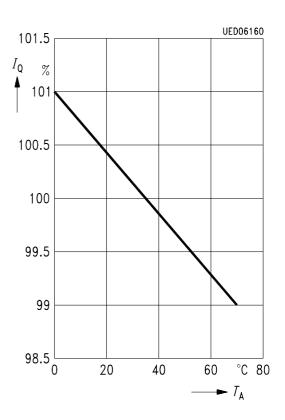

## 4 Diagrams

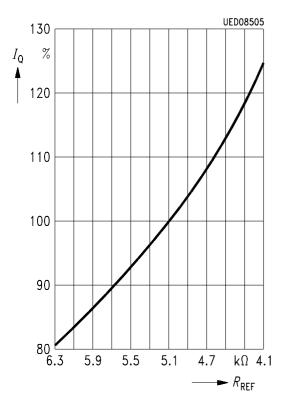

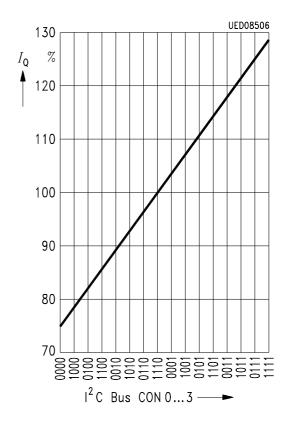

## 4.1 Output Current of DA Converters

Nominal values:  $V_{\rm DDA}$  = 5 V;  $V_{\rm REF}$  = 5.1 k $\Omega$ ; T = 25 °C

Measurements after adjustment via bit d7 of I2C Bus address 0D for each step

Note: The output currents are controlled in digital way, so inaccuracy of 1 LSB (ca. 2 %) is always possible.

# Output current = $f(V_{DDA})$

## Output current = $f(T_A)$

# **SIEMENS**

# Output current = $f(R_{REF})$

# Current = f (CON 0 ... 3)

# 4.2 Application Information

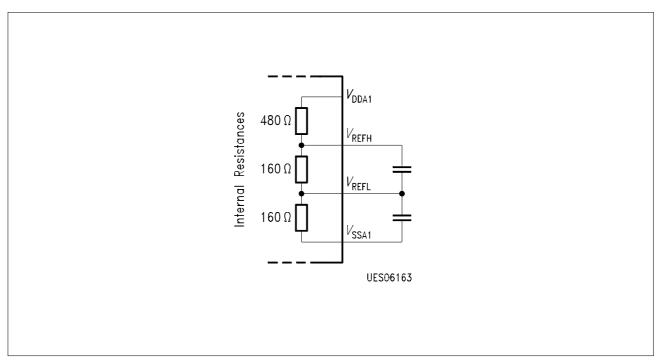

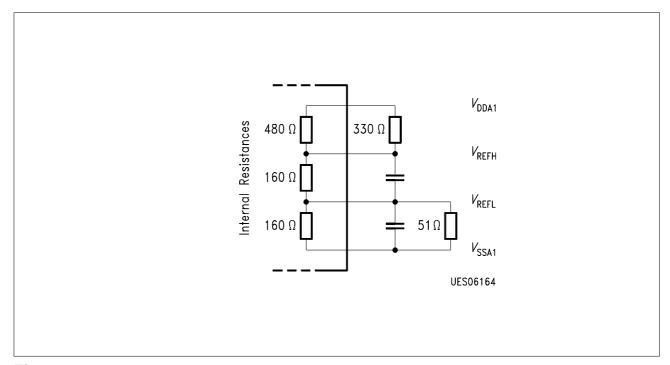

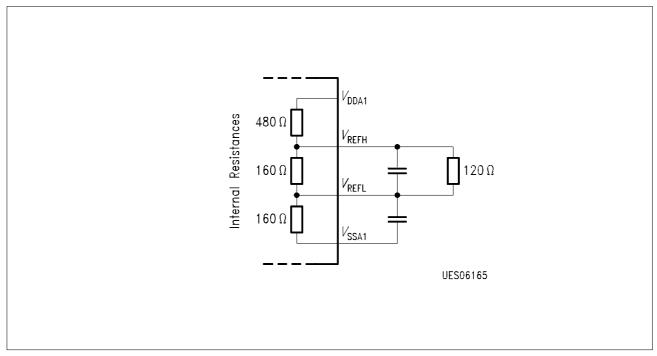

# 4.2.1 Reference Voltage Generation for ADC

Figure 3

Signal Input Range 1 Vpp at Y, U, V

Figure 4

Signal Input Range 2 Vpp at Y, U, V

Figure 5

Signal Input Range 0.5 Vpp at Y, U, V

# 4.2.2 Adjustment of YDEL

Figure 6

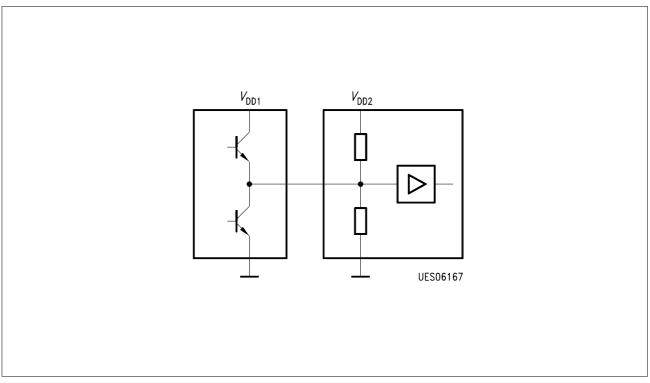

# 4.2.3 Three Level Interface (3-L)

Figure 7

**High level (H):** upper transistor ON, lower transistor OFF

**Medium level (M):** both transistors OFF (interface voltage determined by input stage)

**Low level (L):** upper transistor OFF, lower transistor ON

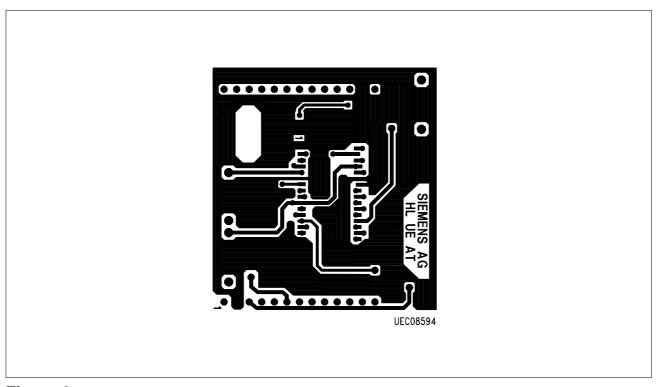

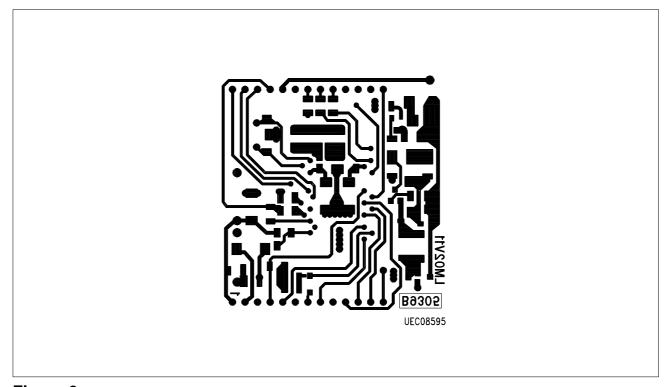

# 4.2.4 Application Board Layout Proposal

Figure 8 (top view)

Figure 9 (bottom view)

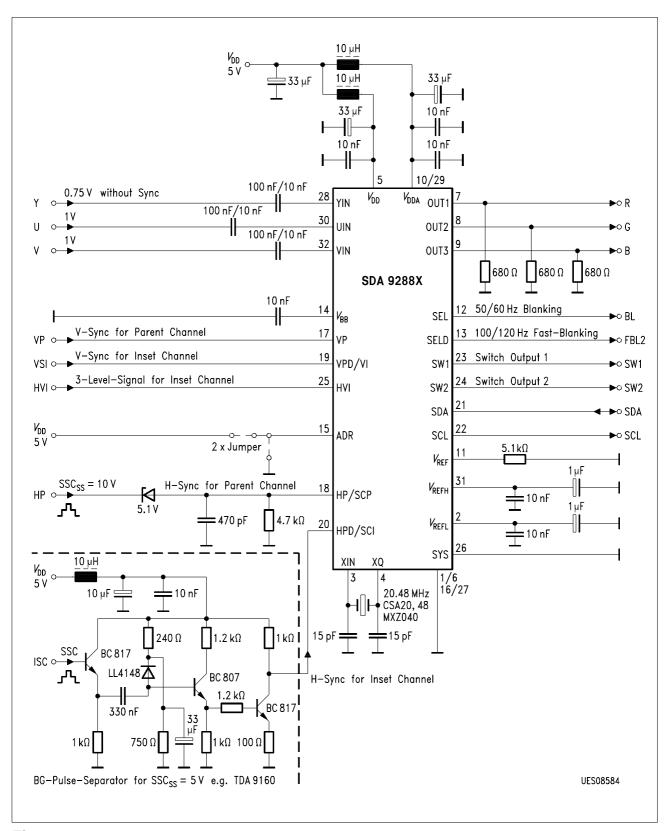

### 4.2.5 Application Circuit (R, G, B-mode)

Figure 10

SIEMENS SDA 9288X

#### 4.3 Waveforms

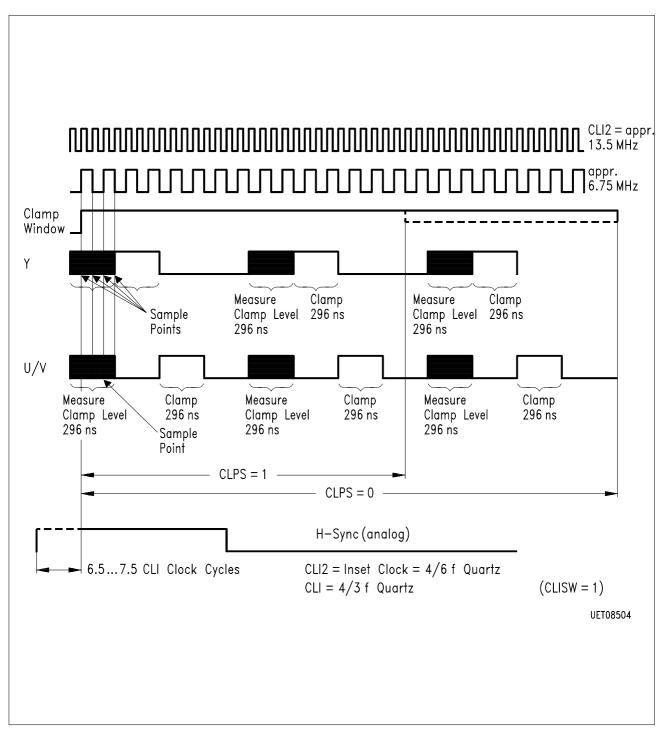

#### 4.3.1 Timing of ADC Clamping

Figure 11

The values are valid if HSIDEL = '0'. To get the maximum values 444 ns for each step of HSIDEL adjustment must be added (CLPFIX = '0'). With CLPFIX = '1' there is no influence of the HSIDEL adjustment to the clamp timing.

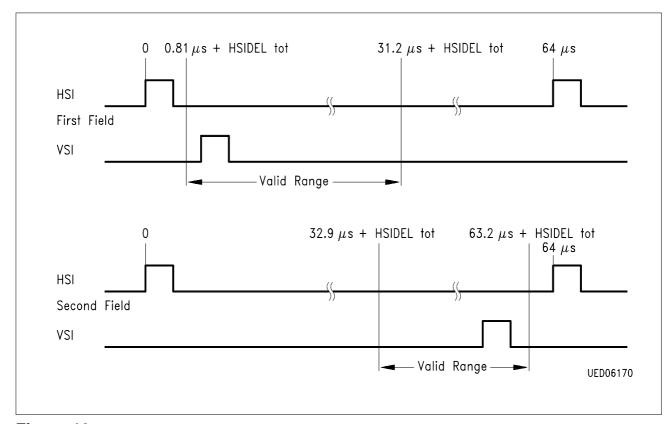

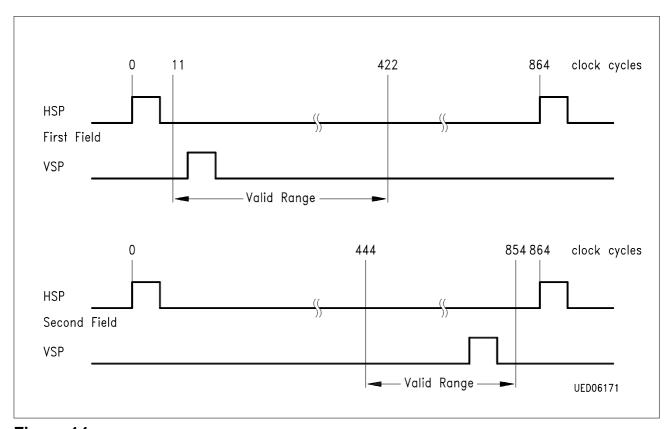

#### 4.3.2 Phase Relation of Sync Pulses at Frame Mode

If the phase relation is not correct at the H and V sync inputs, an adjustment via bits VSIDEL and VSPDEL is possible.

Figure 12 Signal Flow of the Horizontal Synchronization (insert part)

Figure 13

Allowed Phase Relation of the

Horizontal/Vertical Sync Pulses (insert channel) if VSIDEL(0:4) = '0000'

Figure 14

Allowed Phase Relation of the

Horizontal/Vertical Sync Pulses (parent channel)if VSIDEL(0:4) = '0000'

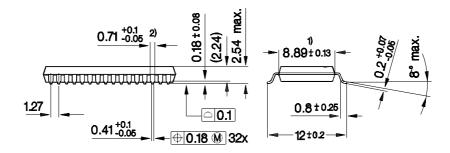

### 5 Package Outlines