# STK311-050

# RDS/RBDS Demodulator with Synchronization and Error Correction

# **Preliminary**

#### **Overview**

The STK311-050 is an RDS/RBDS demodulator hybrid IC for the Radio Data System (RDS) and the Radio Broadcast Data System (RBDS), or multiplexed FM broadcasting of various kinds of data, specified by the European Broadcasting Union (EBU) and US National Radio System Committee (NRSC), respectively. It demodulates the multiplexed data modulating signal to recover the RDS/RBDS signal and performs synchronization, error detection and error correction, Further, low-profile packaging is realized using Sanyo's insulated metal substrate technology (IMST) for the base, SC system and photoresist technologies and folded board construction.

# **Applications**

- · Car stereos

- Home stereos

#### **Features**

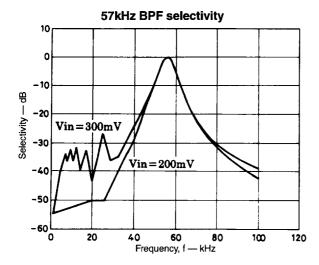

- 57kHz BPF built-in for adjustment-free operation

- 4MHz ceramic oscillator element built-in

- Few external components required for a complete RDS/ RBDS data demodulation system

- ARI-SK/DK decoder built-in

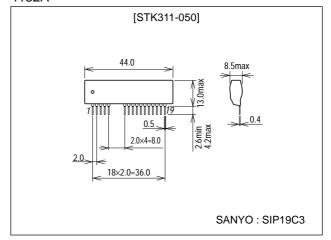

# **Package Dimensions**

unit:mm

4132A

# **Specifications**

## **Maximum Ratings** at Ta = 25°C

| Parameter              | Symbol              | Conditions | Ratings     | Unit |

|------------------------|---------------------|------------|-------------|------|

| Maximum supply voltage | V <sub>CC</sub> max |            | 6.3         | V    |

| Operating temperature  | Topr                |            | -30 to +85  | °C   |

| Storage temperature    | Tstg                |            | -40 to +100 | °C   |

#### **Recommended Operating Voltages** at $Ta = 25^{\circ}C$

| Parameter                      | Symbol          | Conditions | Ratings    | Unit |

|--------------------------------|-----------------|------------|------------|------|

| Supply voltage                 | V <sub>CC</sub> |            | 5          | V    |

| Operating supply voltage range | VCCOP           |            | 4.7 to 5.5 | V    |

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges,or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

# Operating Characteristics at Ta = 25°C, $V_{CC}=5V$

| Parameter                             | Symbol                      | Conditions                                                                  | Ratings              |              |     | Llmit |

|---------------------------------------|-----------------------------|-----------------------------------------------------------------------------|----------------------|--------------|-----|-------|

| Parameter                             | rarameter Symbol Conditions |                                                                             | min                  | typ          | max | Unit  |

| Quiescent current                     | Icco                        |                                                                             |                      | 26           | 38  | mA    |

| Band-pass filter gain                 | VG <sub>BPF</sub>           | f=57kHz                                                                     | 9                    | 12.5         | 17  | dB    |

|                                       |                             | f=60kHz (57kHz=0dB)                                                         | -6                   | -2.5         | 0   | dB    |

| Band-pass filter selectivity          |                             | f=54kHz (57kHz=0dB)                                                         | -6                   | -3.5         | 0   | dB    |

|                                       |                             | f=38kHz (57kHz=0dB)                                                         |                      | -39          | -33 | dB    |

| PLL capture range                     | CR                          | 5mVrms, CW input                                                            |                      | -0.5<br>+1.1 |     | %     |

| RDS/RBDS detector sensitivity         |                             | Pin 12 low, input on pin 4                                                  |                      | 0.4          | 1.0 | mVrms |

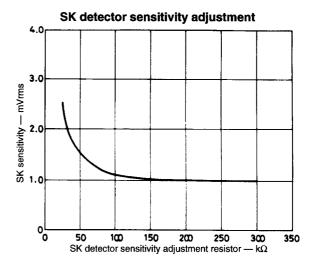

| SK detector sensitivity               |                             | Pin 11 low, input on pin 4                                                  |                      | 1.0          | 2.0 | mVrms |

| DK detector sensitivity               |                             | Pin 10 low, input on pin 4                                                  |                      | 1.9          | 2.9 | mVrms |

| RDS/RBDS input dynamic range          |                             | Pin 12 low, (ARI+RDS/RBDS) signal maximum input on pin 4                    | 30                   | 50           |     | mVrms |

|                                       |                             | RDS/RBDS data demodulated correctly, RDS/RBDS signal maximum input on pin 4 | 250                  |              |     | mVrms |

| DK input dynamic range                |                             | Pin 10 low, ARI signal maximum input on pin 4                               | 75                   | 100          |     | mVrms |

| VCO free-running frequency            | fosc                        |                                                                             | 453                  | 456          | 459 | kHz   |

| High level ouput voltage              | VOH                         | I <sub>OH</sub> =-50μA*1                                                    | V <sub>CC</sub> -1.2 |              |     | V     |

| nigh level ouput voltage              |                             | I <sub>OH</sub> =-10μΑ*1                                                    | V <sub>CC</sub> -0.5 |              |     | V     |

| Low level output voltage              | V <sub>OL</sub>             | I <sub>OL</sub> =10mA*2                                                     |                      |              | 1.5 | V     |

| Low level output voltage              |                             | I <sub>OL</sub> =1.8mA*2                                                    |                      |              | 0.4 | V     |

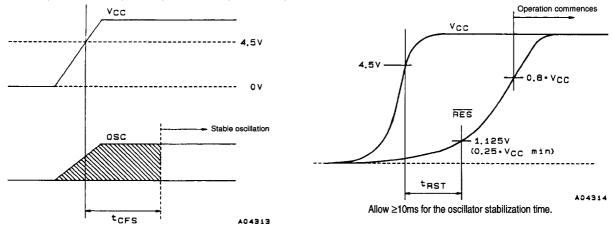

| Ceramic oscillator stabilization time | tCFS                        | See Figure 1.                                                               |                      |              | 10  | ms    |

| Reset time                            | t <sub>RST</sub>            |                                                                             | S                    | ee Figure 2  | 2.  |       |

<sup>\*1.</sup> DATA START, DATA OUT, CLOCK OUT

\*2. RECEIVE, CORRECTION, ERROR, DATA START, DATA OUT, CLOCK OUT

Figure 1. Oscillator stabilization time

Figure 2. Reset time

# **Output Signal Settings**

CLK OUT and DATA START output signals can be set as shown in the following table.

| Setting*1 | CLK OUT polarity | DATA START output |

|-----------|------------------|-------------------|

| 1         | Falling edge     | Each block        |

| 2         | Falling edge     | Second block only |

| 3         | Rising edge      | Each block        |

| 4         | Rising edge      | Second block only |

<sup>\*1.</sup> Setting 1 is the default setting.

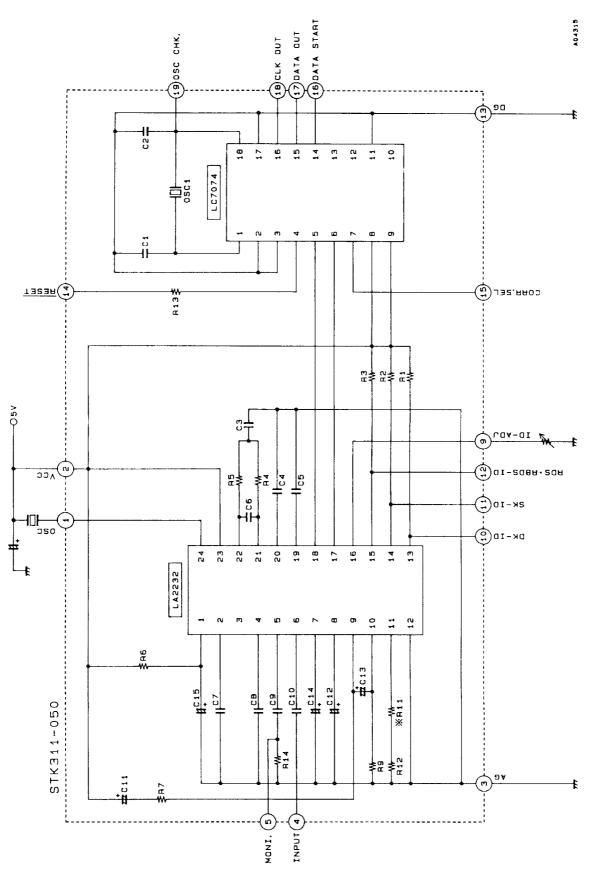

# **Equivalent Circuit**

\* R11 is a function trimming resistor. Pins 6, 7 and 8 are not used.

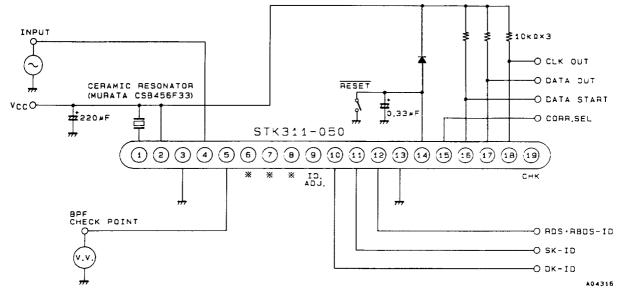

### **Sample Application Circuit**

\* Pins 6, 7 and 8 are not used.

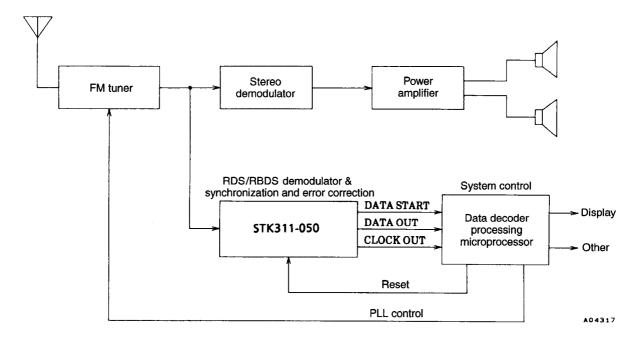

## **Sample System Configuration**

# STK311-050

## **Pin Functions**

| Pin No. | Pin name        | Function                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | OSC             | VCO ceramic oscillator pin (456kHz)                                                                                                                                                                                                                                                                          |  |  |  |  |

| 2       | V <sub>CC</sub> | Supply pin : LA2232 and LC7074 positive supply                                                                                                                                                                                                                                                               |  |  |  |  |

| 3       | AG              | Fround pin : LA2232 analog ground                                                                                                                                                                                                                                                                            |  |  |  |  |

| 4       | INPUT           | nput pin                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 5       | MONI            | PF (for adjustment) monitor output                                                                                                                                                                                                                                                                           |  |  |  |  |

| 9       | ID-ADJ          | K detector sensitivity adjustment pin                                                                                                                                                                                                                                                                        |  |  |  |  |

| 10      | DK-ID           | K signal detector indicator output.  bw-level output when an DK signal is detected, and high-level when not detected.                                                                                                                                                                                        |  |  |  |  |

| 11      | SK-ID           | SK signal detector indicator output.  Low-level output when an SK signal is detected, and high-level when not detected.                                                                                                                                                                                      |  |  |  |  |

| 12      | RDS/RBDS-ID     | RDS/RBDS signal detector indicator output.  Low-level output when an RDS/RBDS signal is detected, and high-level when not detected.                                                                                                                                                                          |  |  |  |  |

| 13      | DG              | Ground pin : LC7074 digital ground                                                                                                                                                                                                                                                                           |  |  |  |  |

| 14      | RESET           | Reset input. Reset restart occurs when held low for 4 cycles. Schmitt-trigger input. Pull-up resistor built-in.                                                                                                                                                                                              |  |  |  |  |

| 15      | CORR. SEL       | Error correction selection input. This pin selects whether the IC corrects errors in the RDS demodulated data. Input = 0 : No correction performed. Input = 1 : Error correction performed. In modes where error correction is enabled, up to five error bits are corrected for distances of 5 bits or less. |  |  |  |  |

| 16      | DATA START      | Serial data output block data start signal (D.S. CONTROL) input to control the output waveform. Pull-up MOS transistor (CMOS) output.                                                                                                                                                                        |  |  |  |  |

| 17      | DATA OUT        | Serial data output. Pull-up MOS transistor (CMOS) output.                                                                                                                                                                                                                                                    |  |  |  |  |

| 18      | CLK OUT         | Clock output. Pull-up MOS transistor (CMOS) output.                                                                                                                                                                                                                                                          |  |  |  |  |

| 19      | OSC CHK         | OSC1 oscillation frequency check pin                                                                                                                                                                                                                                                                         |  |  |  |  |

| 15      | 000 01110       | COOT COCINGUITY OF COOK PIT                                                                                                                                                                                                                                                                                  |  |  |  |  |

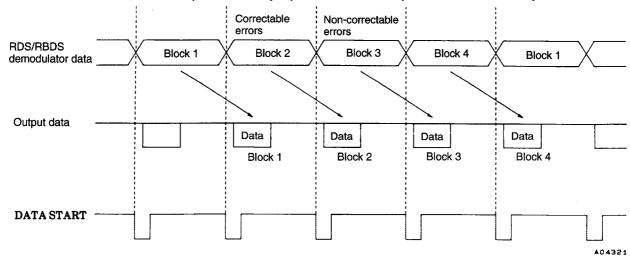

## RDS/RBDS Demodulator Data (LA2232 Output) and LC7074 Output Data Relationship

The LC7074 serial data output is delayed by 1 block from the data received from the LA2232.

Figure 3. Demodulator data and output data relationship

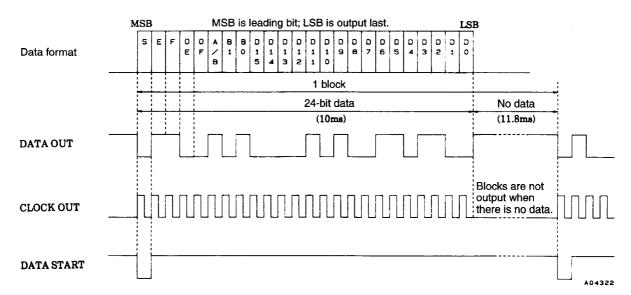

### **Serial Data Output Format and Timing**

| Bit       | Function                                       |                                                              |  |  |

|-----------|------------------------------------------------|--------------------------------------------------------------|--|--|

| S         | Start bit (normally "0")                       |                                                              |  |  |

| E         | Error flag                                     | Parameter E F                                                |  |  |

|           |                                                | No errors 0 0                                                |  |  |

|           |                                                | Errors corrected 0 1                                         |  |  |

| F         | Correction flag                                | Non-correctable errors 1 1                                   |  |  |

| '         |                                                | Note : When CORR. SEL is high.                               |  |  |

| OE        | Offset E                                       |                                                              |  |  |

| OF        | Offset F (normally "0", for future expansion)  |                                                              |  |  |

| A/B       | Group type version 0 : Version A 1 : Version B |                                                              |  |  |

| B1, B0    | Block number                                   | 00 : Block 1<br>01 : Block 2<br>10 : Block 3<br>11 : Block 4 |  |  |

| D15 to D0 | RDS/RBDS data                                  |                                                              |  |  |

Figure 4. Serial data output format and timing

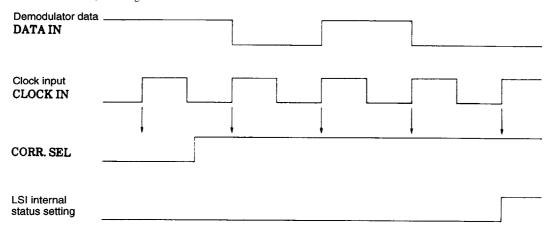

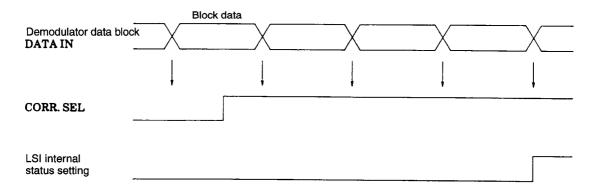

#### **Control Input CORR. SEL Read Timing**

Normally, this pin is checked for its state. However, error correction can be enabled/disabled at any time.

#### **During Sync Detection**

CORR. SEL is read for every bit of demodulator data from the RDS/RBDS demodulator IC (indiated by  $\downarrow$ ), and is read into the LSI when 4 consecutive, matching states occur.

Figure 5. CORR. SEL read timing during sync detection

A04323

#### **After Sync Detection**

CORR. SEL is read for the head of each block of demodulator data from the RDS/RDBS demodulator IC (indiated by  $\downarrow$ ), and is read into the LSI when 4 consecutive, matching states occur.

Figure 6. CORR. SEL read timing after sync detection

A04324

#### **Characteristics Data**

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of October, 1999. Specifications and information herein are subject to change without notice.