# TH8060

# LIN Bus Transceiver with integrated Voltage Regulator

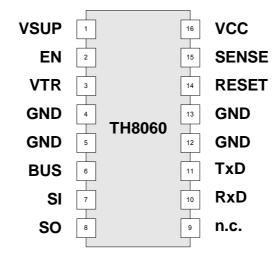

#### Pin Diagram Features and Benefits SOIC16 □ LIN-Bus Transceiver: PNP-open emitter driver with slew rate control and current limita-**VSUP** VCC ΕN SENSE BUS input voltage -24V ... 30V (independently of V<sub>SUP</sub>) RESET VTR Possibility of BUS wake up GND GND TH8060 GND GND Baud rate up to 20 kBaud BUS TxD ☐ Operating voltage V<sub>SUP</sub> = 5.5 ... 18 V RxD SI $\Box$ Very low standby current consumption < 110 $\mu$ A in normal mode SO n.c. (< 50 μA in sleep mode) ☐ Linear low drop voltage regulator: Output voltage 5V± 1% Output current max. 100mA Output current limitation Overtemperature shutdown Configurable reset time (15ms/100ms) and reset threshold voltage (3.15V / 4.65V) ■ Low voltage detection at VSUP ☐ Wake-up by LIN BUS traffic and start-up capable independent of EN voltage level ☐ Universal comparator with an input voltage range –24V ... 30V and digital output ☐ Load dump protected (40V)

### Ordering Information

Part No. Temperature Range Package

TH8060 JDF -40°C...125°C SOIC16, 300mil

### General Description

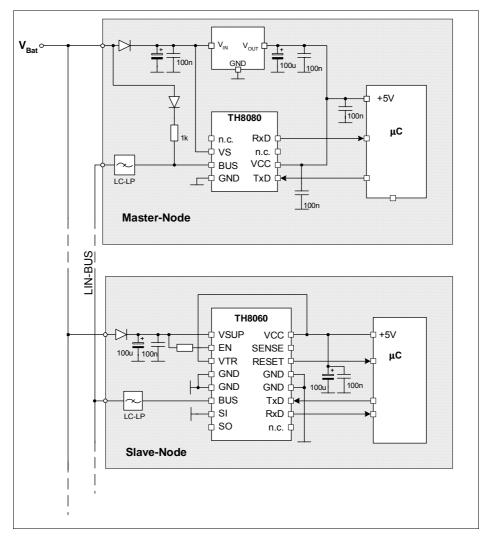

The RELIN TH8060 consists a low drop voltage regulator 5V/100mA and a LIN Bus transceiver. The LIN-transceiver is suitable for LIN-Bus systems conform to "LIN-Protocol Specification" Rev.1.1. from 04/17/2000.

The combination of voltage regulator and bus transceiver in combination with the monitoring functions make it

possible to develop simple, but powerful and cheap slave nodes in LIN Bus systems.

The wide output current area and the configurable reset time and reset voltage works together with many different microcontrollers.

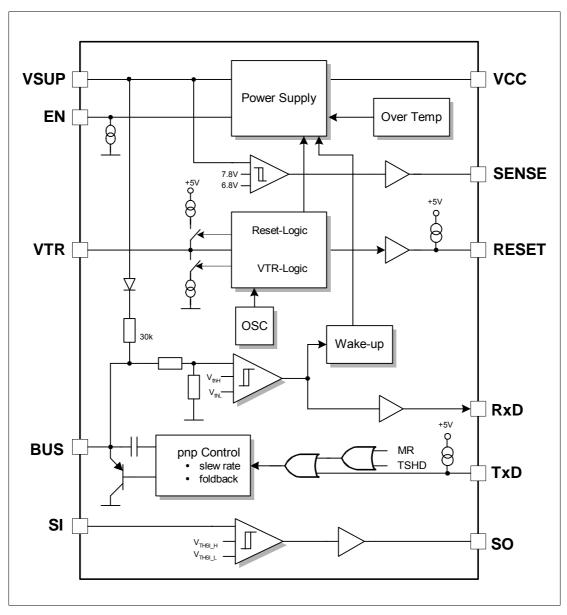

# Functional Diagram

Figure 1 - Block Diagram

## Functional Description

The TH8060 consists a voltage regulator 5V/100mA and a LIN Bus transceiver, which is a bi-directional bus interface device for data transfer between LIN-Bus and the LIN protocol controller.

Also integrated into the transceiver are a voltage and time controlled reset management, power down, wake up function and a universal comparator for extended applications.

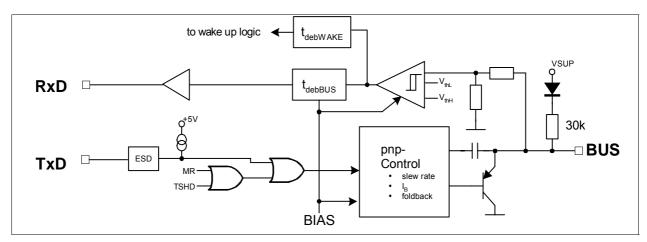

### LIN-BUS Transceiver

The TH8060 is a bi-directional bus interface device for data transfer between LIN-Bus and the LIN protocol controller.

The transceiver consists a pnp-driver (1.2V@40mA) with slew rate control and fold-back characteristic and con-

sists as well in the receiver a high voltage comparator followed by a debouncing unit.

The BUS pin has an integrated 30k pull up resistor with a diode, which prevent the reverse current of VBUS during differential voltage between VSUP and BUS ( $V_{BUS}$ > $V_{SUP}$ ).

Figure 2 - Block Diagram LIN Bus Transceiver

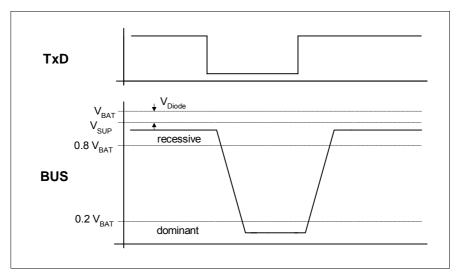

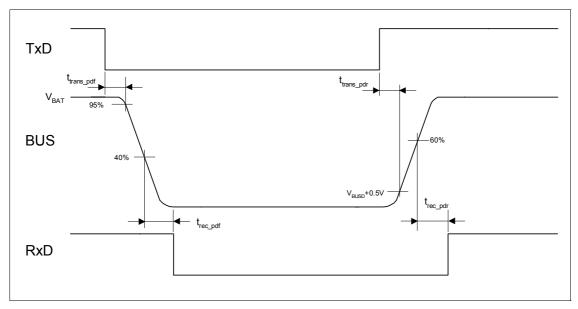

#### **Transmit Mode**

During the transmission the data at the pin TxD will be transferred to the pin BUS. To minimize the electromag-

netic emission of the bus line, the TH8060 has an integrated slew rate control.

Figure 3 - Transmit Mode Pulse Diagram

Datasheet Rev 1.1 March 2001 Page 3 www.melexis.com

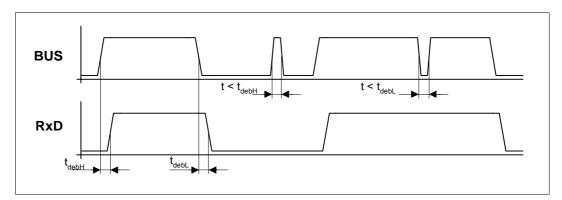

### **Receive Mode**

The data at the pin BUS will be transferred to the pin RxD. Short spikes on the bus signal are suppressed by

the implemented debouncing circuit.

Figure 4 - Block Diagram LIN Bus Transceiver

# **Linear Regulator and Controlling Functions**

### Regulator

The TH8060 has an integrated linear regulator with an output voltage of 5V ±2% and an output current of

≤100mA. The regulator is switched on or off with a signal on the EN pin or wake up with a BUS signal.

### Initialization

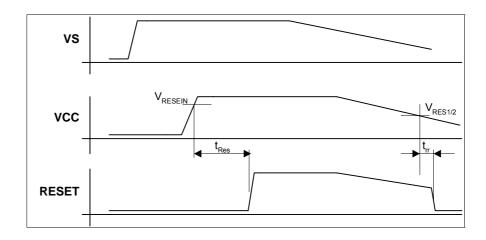

The initialization is started if the power supply is switched on, or after the temperature limitation has switched off the regulator or in case of BUS traffic (wake up).

If the  $V_{\text{CC}}$  voltage level is higher than  $V_{\text{RESEIN}}$ , the reset time  $t_{\text{RES}}$  is started. This reset time is determined by the voltage level on the VTR pin (see table VTR Programming). After  $t_{\text{RES}}$  a rising edge on the RESET output is

generated (see figure 10 - Initialization).

The regulator is active and can only switched off with a falling edge on EN. The regulator remain with EN=high in active mode and therefore also the V<sub>CC</sub> voltage is active.

The input EN has an internal pull down resistor. If EN=high, the internal pull down current is switched off to minimize the quiescent current.

Figure 5 - Initialization

### **RESET Output**

The RESET output is switched from low to high if  $V_{SUP}$  is switched on and  $V_{CC}$ > $V_{RESEIN}$  after the time  $t_{RES}$ .

If the voltage  $V_{\text{CC}}$  drop below  $V_{\text{RES1}}$  or  $V_{\text{RES2}}$  then the RESET output is switched from high to low after the time  $t_{\text{rr}}$  has been reached.

The voltage level for  $V_{\text{RES1}}$  and  $V_{\text{RES2}}$  or the corresponding times  $t_{\text{RES}}$  can be programmed via the analogue input VTR.

### Wake up with BUS traffic

If the regulator is put in standby mode it can be wake up with the BUS interface. Every pulse on the BUS (high pulse or low pulse) with a pulse width of min.  $45\mu s$  will switch on the regulator.

After the BUS has wake up the regulator, it can only be switched off with a high level followed by a low level on the EN pin.

### **Reset Programming on VTR**

With the VTR pin the reset switch off levels and delay time can be programmed.

The voltage on VCC influences the reset function.

### VTR-Programming

| VTR-Mode                              | $V_{RES}$                                    | t <sub>Res</sub> |

|---------------------------------------|----------------------------------------------|------------------|

| VTR = GND                             | V <sub>RES</sub> = V <sub>RES1</sub> = 3.15V | 100ms            |

| VTR = VCC                             | V <sub>RES</sub> = V <sub>RES2</sub> = 4.65V | 100ms            |

| VTR with R $\geq$ 50k $\Omega$ to GND | V <sub>RES</sub> = V <sub>RES1</sub> = 3.15V | 15ms             |

| VTR with R $\geq$ 50k $\Omega$ to VCC | V <sub>RES</sub> = V <sub>RES2</sub> = 4.65V | 15ms             |

The voltage on VTR input is read out if the voltage at this pin is higher than  $V_{\text{RESEIN}}$ . This value defines the reset switch off voltage  $V_{\text{RES}}$  and switches on with the next oscillator cycle the pull up current source if VTR=low or the pull down current source if VTR=high. The sources are active for one oscillator cycle. The level changes during this procedures on VTR, wich depends on the external pull up or pull down resistors control the reset time  $t_{\text{RR}}$

#### **Temperature Limitation**

If the junction temperature  $150^{\circ}\text{C} < T_j < 170^{\circ}\text{C}$  the over temperture recognition will be active and the regulator voltage will be switched off. After  $T_j$  fall below  $140^{\circ}\text{C}$  the TH8060 will be initialized, not depending on of the voltage levels on EN and BUS.

The function of the TH8060 is possible between  $T_{Amax}$  and the switch off temperature, but small parameter differences can appear.

### Low Voltage Detection V<sub>SUP</sub>

Low voltage on V<sub>SUP</sub> is monitored on SENSE output.

If  $V_{\text{SUP}}$  has reached the level of  $V_{\text{SUP}}$  =6.8V then the SENSE output generates low level. In the normal

operating range is  $V_{\text{SUP}} > 7.8V$  and the SENSE output generates a high level.

#### **Universal Comparator**

The TH8060 consist a universal comparator for general use. The positiv input of this comparator is connected with the pin SI. The input voltage range of SI is  $0V...V_{SUP}$ .

The input voltage is compared with a fixed reference voltage at high or low level and the comparator output SO drives a 5V digital signal.

# Application Hints

### Operating during Disturbances

The absence of  $V_{\text{SUP}}$ ,  $V_{\text{CC}}$  or GND connection or ground shift either alone or in any combination, do not influence

or disturb the communication between other bus nodes.

### Undervoltage

The reset unit secures the correct behavior of the driver during undervoltage. The BUS pin generates the recessive state if  $V_{\rm CC}$  <  $V_{\rm RES1}$ . The inputs have pull-up or pull-down characteristics.

With 4.5V  $\leq$  V\_CC  $\leq$  5.25V the bus connection operates within the correct parameters .

If  $V_{CC} \le 4.5V$  the TxD signal is transmitted to the bus. The receive mode is also activ.

SENSE and SO output the correct signal if  $V_{\text{CC}} > V_{\text{RES}}$ . The specificated values of the input voltages on SO can't quaranteed.

### Regulator Circuitry

The choice and dimension of the capacitor on VCC is determined by application point of view. Important parameters are the current difference on load changes and the maximum short time voltage drop.

The VCC pin must be connected to a min.  $2\mu F$  capacitor for stable operating of the regulator in the whole operating range.

#### **Short Circuit Proof**

# All in- and outputs are short circuit proof to battery and ground. A thermal shut down circuit prevent VCC and BUS from any damage

### **Baud Rate**

The TH8060 has a maximum Baud rate of 20 kBaud ( $C_{BUS}$ <10nF). This baud rate is supported by the typically value for the slew rate at BUS of  $\pm$  2V/ $\mu$ s.

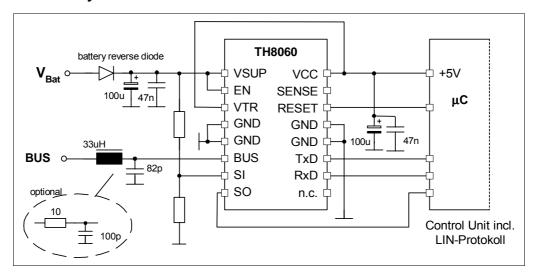

## **Application Circuitry**

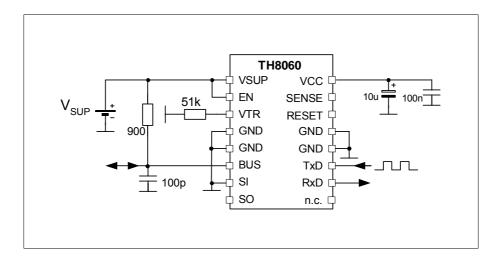

Figure 6 - Application Circuit

There should be used an LC- or RC-Filter to minimize the influence of EMI on the BUS lines.

Figure 7 - Application Circuit for LIN Subbus

# Electrical Specification

All voltages are referenced to ground (GND). Positive currents flow into the IC. The absolute maximum ratings given in the table below are limiting values that do not lead to a permanent damage of the device but exceeding

any of these limits may do so. Long term exposure to limiting values may affect the reliability of the device. Reliable operation of the TH8060 is only specified within the limits shown in "Operating conditions".

## **Operating Conditions**

| Parameter                     | Symbol          | Min  | Max  | Unit |

|-------------------------------|-----------------|------|------|------|

| Battery voltage               | $V_{SUP}$       | 5.25 | 18   | V    |

| Supply voltage                | V <sub>CC</sub> | 4.75 | 5.25 | V    |

| Operating ambient temperature | T <sub>A</sub>  | -40  | +125 | °C   |

| Junction temperature [1]      | T <sub>Jc</sub> |      | +150 | °C   |

### Absolute Maximum Ratings

| Parameter                                                  | Symbol               | Condition  | Min  | Max                   | Unit |

|------------------------------------------------------------|----------------------|------------|------|-----------------------|------|

|                                                            |                      |            | -1.0 | 18                    |      |

| Supply voltage at VSUP [2]                                 | V <sub>SUP</sub>     | T ≤ 60 s   | -    | 30                    | V    |

|                                                            |                      | T ≤ 500 ms | -    | 40                    |      |

| January welfage of his CL PLIC [2]                         | V                    |            | -24  | 30                    | \/   |

| Input voltage at pin SI, BUS [2]                           | V <sub>BUS</sub>     | T ≤ 500 ms | -    | 40                    | V    |

| Difference VSUP-VCC                                        | V <sub>SUP-VCC</sub> |            | -0.3 | 40                    | V    |

| Input voltage at pin EN and SI                             | V <sub>INENSI</sub>  |            | -0.3 | V <sub>SUP</sub> +0.3 | V    |

| Input voltage at pin VTR, TxD, RxD, SO, RESET, SENSE       | V <sub>IN</sub>      |            | -0.3 | V <sub>cc</sub> +0.3  | V    |

| Input current at pin EN, VTR, SI, SO, TxD, RxD,RESET,SENSE | I <sub>IN</sub>      |            | -25  | 25                    | mA   |

| Input current for short circuit of pin VSUP and VCC        | I <sub>Short</sub>   |            | -500 | 500                   | mA   |

| Power dissipation T <sub>A</sub> = 85 °C [3]               | P <sub>0</sub>       |            |      | 600                   | mW   |

| Thermal resistance from junction to ambient                | R <sub>THJA</sub>    |            |      | 50                    | K/W  |

| Junction temperature [4]                                   | TJ                   |            |      | 150                   | °C   |

| Storage temperature                                        | T <sub>STG</sub>     |            | -55  | 150                   | °C   |

Datasheet Rev 1.1 March 2001 Page 8 www.melexis.com

<sup>&</sup>lt;sup>[1]</sup> Junction temperature is defined in IEC 747-1

<sup>[2]</sup> The current and voltage values are valid independent from each other.

The maximum power dissipation is defined by the ambient temperature and the thermal resistance. It can be calculated with  $P_0 = (V_{SUP} - V_{CC})^* I_{VCC} + P_{BUS}$ .  $P_{BUS}$  is the BUS driver output with normally  $\leq 25$  mW

<sup>[4]</sup> see over temperature protection

## Static Characteristics

( $V_{SUP}$  = 5.25 to 18V,  $V_{CC}$ = 4.75 to 5.25V,  $T_A$  = -40 to +125°C, unless otherwise specified)

| Parameter                                      | Symbol              | Condition                                                     | Min                  | Тур  | Max                      | Unit |

|------------------------------------------------|---------------------|---------------------------------------------------------------|----------------------|------|--------------------------|------|

| Linear Regulator                               |                     |                                                               |                      |      |                          |      |

|                                                | V <sub>CCn</sub>    | $5.5V \le V_{SUP} \le 18V$<br>$T_A = 25^{\circ}C$             | 4.95                 | 5.0  | 5.05                     | V    |

| Output voltage VCC                             | V <sub>CCt</sub>    | $5.5V \le V_{SUP} \le 18V$                                    | 4.90                 | 5.0  | 5.10                     | V    |

|                                                | $V_{\text{CCh}}$    | V <sub>SUP</sub> > 18V                                        | 4.95                 | 5.0  | 5.25                     | V    |

|                                                | V <sub>CCI</sub>    | 3.3 V< V <sub>SUP</sub> < 5.5 V                               | $V_S$ - $V_D$        |      | 5.1                      | V    |

| Supply current, "normal mode" [2]              | I <sub>Snl</sub>    | $V_{EN} = V_{SUP} = 12V$ , Pins 8, 10, 11, 14-16 open         |                      |      | 110                      | μΑ   |

| Supply current, "sleep mode"                   | I <sub>Ssleep</sub> | V <sub>EN</sub> = 0V                                          |                      | 35   | 50                       | μΑ   |

|                                                |                     | $V_{SUP} \ge 4.0V$ , $I_{VCC} = 25mA$                         |                      |      | 200                      | mV   |

| Drop-out voltage                               | $V_D$               | $V_{SUP} \ge 4.0V$ , $I_{VCC} = 100mA$                        |                      |      | 400                      | mV   |

|                                                |                     | $V_{SUP} \ge 3.3V$ , $I_{VCC} = 20mA$                         |                      |      | 600                      | mV   |

| Output current VCC                             | I <sub>VCC</sub>    | $V_{\text{SUP}} \ge 3.0 V$                                    | 100                  |      |                          | mA   |

| Current limitation VCC                         | I <sub>LVCC</sub>   | V <sub>SUP</sub> > 0V                                         |                      |      | 300                      | mA   |

| Load capacity                                  | C <sub>load</sub>   | $ESR \leq 5\Omega$                                            | 2                    |      |                          | μF   |

| Power-on-reset threshold "V <sub>CC</sub> on"  | V <sub>RESEIN</sub> | refered to V <sub>CC</sub> , V <sub>SUP</sub> > 4.6V          | 4.5                  | 4.65 | 4.8                      | V    |

| Dower on recet threehold "\/ off"              | V <sub>RES2</sub>   | \\ -II\\ > 0\\                                                | 4.5                  | 4.65 | 4.8                      |      |

| Power-on-reset threshold "V <sub>CC</sub> off" | V <sub>RES1</sub>   | $V_{TR}=H,V_{SUP}>0V$                                         | 3.0                  | 3.15 | 3.3                      | V    |

| SENSE-Output                                   |                     |                                                               |                      |      |                          |      |

| VSUP - threshold low at SENSE                  | V <sub>SENL</sub>   |                                                               | 6.8                  |      |                          | V    |

| VSUP - threshold high an SENSE                 | $V_{SENH}$          |                                                               |                      |      | 7.8                      | V    |

| Hysteresis SENSE                               | V <sub>SENHYS</sub> |                                                               | 100                  |      |                          | mV   |

| Output voltage low                             | V <sub>OL</sub>     | I <sub>OUT</sub> = 1mA                                        |                      |      | 8.0                      | ٧    |

| Output voltage high                            | V <sub>OH</sub>     | I <sub>OUT</sub> = -1mA                                       | V <sub>CC</sub> -0.8 |      |                          | V    |

| Enable-Input EN                                |                     |                                                               |                      |      |                          |      |

| Input voltage low                              | $V_{ENL}$           |                                                               | -0.3                 |      | 1.75                     | V    |

| Input voltage high                             | V <sub>ENH</sub>    |                                                               | 2.5                  |      | V <sub>SUP</sub><br>+0.3 | V    |

| Hysteresis                                     | V <sub>ENHYS</sub>  |                                                               | 100                  |      |                          | mV   |

| Pull-down current EN                           | 1                   | $V_{EN} > V_{ENH}$                                            | 1.8                  | 4.0  | 7.5                      | μΑ   |

| T dil-down carrent Liv                         | I <sub>pdEN</sub>   | V <sub>EN</sub> < V <sub>ENL</sub>                            | 70                   | 100  | 130                      | μΑ   |

| Output RESET                                   |                     |                                                               |                      |      |                          |      |

|                                                |                     | $I_{OUT} = 1 \text{ mA}, V_{SUP} > 5.5 \text{ V}$             |                      |      | 0.8                      | V    |

| Output voltage low                             | V <sub>OL</sub>     | 10 k $\Omega$ RESET to VCC $V_{SUP} = V_{CC} = 0.8 \text{ V}$ |                      |      | 0.2                      | V    |

| Pull-up current                                | I <sub>pu</sub>     |                                                               | -500                 | -375 | -250                     | μΑ   |

# Static Characteristics (continued)

| Parameter                            | Symbol              | Condition                                                                                          | Min                  | Тур  | Max  | Unit             |

|--------------------------------------|---------------------|----------------------------------------------------------------------------------------------------|----------------------|------|------|------------------|

| Comparator SI, SO                    |                     |                                                                                                    |                      |      |      |                  |

| Input Current SI                     | I <sub>INSI</sub>   | $0V \le V_{SI} \le 18V$                                                                            | -20                  |      | 20   | μΑ               |

| Input Current SI                     | -I <sub>INSI</sub>  | V <sub>SI</sub> = -12V                                                                             | -1                   |      |      | mA               |

| Threshold low SI                     | V <sub>IL</sub>     |                                                                                                    | 1.05                 | 1.16 |      | V                |

| Threshold High SI                    | V <sub>IH</sub>     |                                                                                                    |                      | 1.21 | 1.4  | V                |

| Hysteresis                           | V <sub>HYS</sub>    |                                                                                                    | 30                   |      |      | mV               |

| Output valtage law et CO             |                     | $I_{OUT} = 1 \text{ mA}, V_{SUP} > 5.5 \text{ V}$                                                  |                      |      | 0.8  | V                |

| Output voltage low at SO             | V <sub>OL</sub>     | 10 k $\Omega$ SO to VCC, V <sub>CC</sub> > 3.3V                                                    |                      |      | 0.4  | V                |

| Pull-up current at SO                | I <sub>pu</sub>     |                                                                                                    | -500                 | -375 | -250 | μΑ               |

| Input VTR                            |                     |                                                                                                    |                      |      |      |                  |

| Threshold low                        | $V_{TRL}$           |                                                                                                    | 0.15                 | 0.25 |      | V <sub>CC</sub>  |

| Threshold high                       | $V_{TRH}$           |                                                                                                    |                      | 0.75 | 0.85 | V <sub>CC</sub>  |

| Output current low                   | I <sub>OL</sub>     | V <sub>CC</sub> > 3.3 V                                                                            | 160                  | 230  | 300  | μΑ               |

| Output current high                  | I <sub>OH</sub>     |                                                                                                    | -300                 | -230 | -160 | μΑ               |

| LIN-Bus-Interface                    |                     |                                                                                                    |                      |      |      |                  |

| Power-on-reset threshold             | $V_{POR}$           | V <sub>POR</sub> =V <sub>RES1</sub>                                                                | 3.0                  | 3.15 | 3.3  | V                |

| Pull-up current TxD                  | I <sub>pu</sub>     |                                                                                                    | -500                 | -375 | -250 | μΑ               |

| Input voltage low TxD                | V <sub>IL</sub>     |                                                                                                    |                      |      | 0.25 | V <sub>CC</sub>  |

| Input voltage high TxD               | V <sub>IH</sub>     |                                                                                                    | 0.75                 |      |      | V <sub>CC</sub>  |

| Input voltage low BUS dominant       | V <sub>IL</sub>     |                                                                                                    |                      |      | 0.45 | $V_{\text{SUP}}$ |

| Input voltage high BUS recessive     | V <sub>IH</sub>     |                                                                                                    | 0.55                 |      |      | $V_{\text{SUP}}$ |

| Hysteresis BUS                       | V <sub>HYS</sub>    |                                                                                                    |                      | 50   |      | mV               |

| Input current BUS recessive [2]      | I <sub>INBUSR</sub> | $8 \le V_{BUS} \le 18 \text{ V},$<br>$V_{SUP} = V_{BUS} - 0.7 \text{V}, \text{ TxD} = \text{high}$ |                      |      | 20   | μΑ               |

| Input current BUS dominant           | I <sub>INBUSD</sub> | $V_{BUS}$ = 0V, TxD = high                                                                         | -1                   |      |      | mA               |

| Pull up resistor BUS                 | R <sub>BUSpu</sub>  |                                                                                                    | 20                   | 30   | 47   | kΩ               |

| Output voltage BUS dominant          | $V_{\text{BUSD}}$   | $V_{SUP}$ = 12V, TxD = low $I_{BUS}$ = 40 mA                                                       |                      |      | 1.2  | V                |

| Output voltage BUS recessive [1] [2] | V <sub>BUSR</sub>   | $8 \le V_{SUP} \le 18 \text{ V, TxD} = \text{high}$                                                |                      |      | 0.8  | $V_{BAT}$        |

| Current limitation BUS               | I <sub>LIM</sub>    | $V_{BUS} > 2.5V$ , $TxD = low$                                                                     | 40                   |      | 100  | mA               |

| Output voltage low RxD               | V <sub>OL</sub>     | I <sub>OUT</sub> = 1 mA                                                                            |                      |      | 0.8  | V                |

| Output voltage high RxD              | V <sub>OH</sub>     | I <sub>OUT</sub> = -1 mA                                                                           | V <sub>CC</sub> -0.8 |      |      | V                |

<sup>[1]</sup> The recessive voltage at pin BUS don't should be less than 80% of voltage at KL30  $V_{BAT}$ . The voltage at  $V_{SUP}$  results with consideration of reverse diode  $V_{SUP} = V_{BAT} - 0.7V$ [2] See test circuit for dynamic characteristics on page 12

Datasheet Rev 1.1 March 2001 Page 10 www.melexis.com

## **Dynamic Characteristics**

All dynamic values of the table below refer to the test-schematic schown in Figure 3 - Test Circuit for Dynamic Characteristics

For the definition of delay and transitions times see Figure 2 - TH8060 Timing Diagram.

$(7V \leq V_{SUP} \leq 18V,\, 4.75V \leq V_{CC} \leq 5.25V,\, -40^{\circ}C \leq T_{A} \leq 125^{\circ}C,\, unless \,\, otherwise \,\, specified)$

| Parameter                                    | Symbol                                         | Symbol Condition                                                                                         |      | Тур  | Max  | Unit |

|----------------------------------------------|------------------------------------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|

| RESET                                        |                                                |                                                                                                          |      |      |      |      |

| Reset time                                   | t <sub>Res</sub>                               | $R_{VTR} < 1 \text{ k}\Omega$                                                                            | 70   | 100  | 140  | ms   |

| reset une                                    | *Res                                           | $R_{VTR} > 45 \text{ k}\Omega$                                                                           | 10   | 15   | 20   | ms   |

| Reset rising time                            | t <sub>rr</sub>                                |                                                                                                          | 3.0  | 6.5  | 10   | μs   |

| LIN-Bus-Interface                            |                                                |                                                                                                          |      |      |      |      |

| Slew rate BUS falling edge [2]               | dV/dT <sub>fall</sub>                          | $20\% \le V_{BUS} \le 80\%$ $100pF \le C_{BUS} \le 10nF$                                                 | -2.5 | -2.0 | -1.0 | V/μs |

| Slew rate BUS rising edge [2]                | dV/d <sub>Trise</sub>                          | 20% ≤ V <sub>BUS</sub> ≤ 80%<br>C <sub>BUS</sub> = 100 pF                                                | 1.0  | 2.0  | 2.5  | V/μs |

| Symmetry of Slew rate BUS                    | dV/dT <sub>sym</sub>                           | $\frac{\text{dV/dT}_{\text{rise}} - \text{dV/dT}_{\text{fall}}}{\text{C}_{\text{BUS}} = 100 \text{ pF}}$ | -0.3 |      | 0.3  | V/μs |

| Debouncing time BUS                          | t <sub>debBUS</sub>                            | High pulse or low pulse                                                                                  | 1.5  | 2.8  | 4.0  | μs   |

| Symmetry of debouncing BUS                   | t <sub>debsym</sub>                            |                                                                                                          | -0.5 |      | 0.5  | μs   |

| Propagation delay TxD -> BUS [1] [2]         | $t_{	ext{trans\_pdr}}, \ t_{	ext{trans\_pdf}}$ |                                                                                                          |      |      | 4    | μs   |

| Symmetry of propagation delay TxD -> BUS [1] | t <sub>trans_sym</sub>                         | t <sub>trans_pdr</sub> - t <sub>trans_pdf</sub>                                                          | -2   |      | 2    | μs   |

| Propagation delay BUS -> RxD [1] [2]         | $t_{rec\_pdr}$                                 |                                                                                                          |      |      | 6    | μs   |

| Symmetry of propagation delay BUS -> RxD [1] | t <sub>rec_sym</sub>                           | t <sub>rec_pdr</sub> - t <sub>rec_pdf</sub>                                                              | -2   |      | 2    | μs   |

| Debouncing time TxD [1]                      | t <sub>deb</sub>                               |                                                                                                          | 0.6  | 1.0  | 1.5  | μs   |

| Debouncing time EN [1]                       | t <sub>deb</sub>                               |                                                                                                          | 200  |      |      | ns   |

| Wake-up-debouncing BUS                       | t <sub>debWake</sub>                           |                                                                                                          | 25   | 45   | 90   | μs   |

| Propagation delay SI -> SO                   | t <sub>pdcomp</sub>                            |                                                                                                          | 4    |      | 11   | μs   |

| VSUP-SENSE debouncing [1]                    | t <sub>deb</sub>                               |                                                                                                          | 10   | 17   | 25   | μs   |

Datasheet Rev 1.1 March 2001 Page 11 www.melexis.com

<sup>[1]</sup> See timing diagram

<sup>[2]</sup> See test circuit for dynamic characteristics on page 12

## **Timing Diagram**

Figure 8 - Timing Diagram

## **Test Circuit for Dynamic Characteristics**

Figure 9 - Test Circuit for Delay Time and Slope Control

### **Test Circuit for Dynamic Characteristics** (continued)

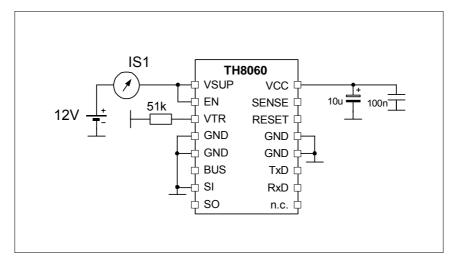

Figure 10 - Test Circuit for Supply Current Is1

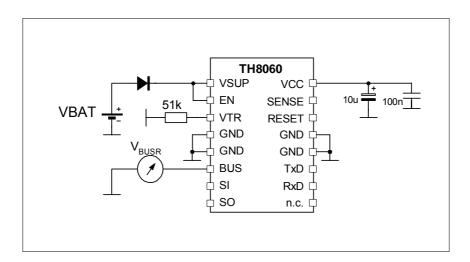

Figure 11 - Test Circuit for Bus Voltage "recessiv" V<sub>BUSR</sub>

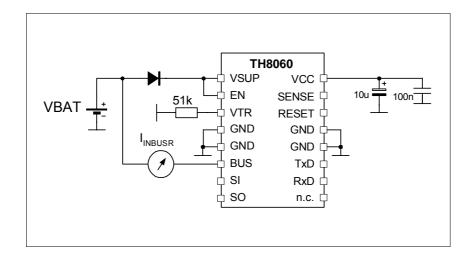

Figure 12 - Test Circuit for Bus Current "recessiv" IBUSR

# Pin Description

| Pin | Name  | I/O | Function                                                          |

|-----|-------|-----|-------------------------------------------------------------------|

| 1   | VSUP  |     | Supply voltage                                                    |

| 2   | EN    | I   | Enable Input voltage regulator, HV-pull-down-Input, High-active   |

| 3   | VTR   | I   | Analogue Input - definition of reset time und Reset voltage level |

| 4   | GND   |     | Ground                                                            |

| 5   | GND   |     | Ground                                                            |

| 6   | BUS   | I/O | Bi-directional bus line                                           |

| 7   | SI    | Ι   | Comparator Input, HV-Input                                        |

| 8   | SO    | 0   | 5V-Comparator Output                                              |

| 9   | n.c.  |     | not connected                                                     |

| 10  | RxD   | 0   | Receive Output, 5V-push-pull                                      |

| 11  | TxD   | I   | 5V-Transmit Input, pull-up-Input                                  |

| 12  | GND   |     | Ground                                                            |

| 13  | GND   |     | Ground                                                            |

| 14  | RESET | 0   | 5V-output reset, active low                                       |

| 15  | SENSE | 0   | 5V-output of VSUP-Monitoring                                      |

| 16  | VCC   | 0   | Regulator output 5V/100mA                                         |

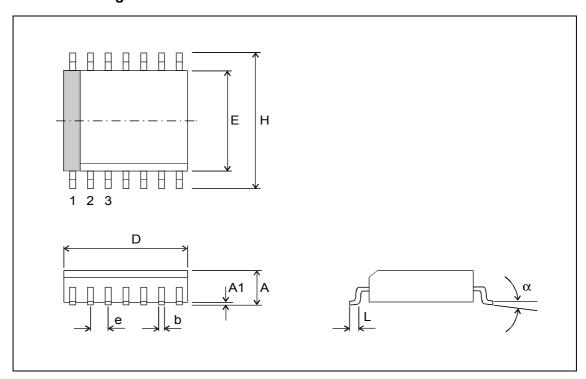

# Mechanical Specifications

# **SOIC16 Package Dimensions**

# Small Outline Integrated Circiut (SOIC), SOIC 16, 300 mil

| All Dimension in mm, coplanarity < 0.1 mm |                                             |       |       |       |            |       |       |       |    |

|-------------------------------------------|---------------------------------------------|-------|-------|-------|------------|-------|-------|-------|----|

|                                           | D                                           | Е     | н     | Α     | <b>A</b> 1 | е     | b     | L     | α  |

| min                                       | 10.1                                        | 7.40  | 10.00 | 2.35  | 0.10       | 1.07  | 0.33  | 0.40  | 0° |

| max                                       | 10.5                                        | 7.60  | 10.65 | 2.65  | 0.30       | 1.27  | 0.51  | 1.27  | 8° |

| All Dimension in i                        | All Dimension in inch, coplanarity < 0.004" |       |       |       |            |       |       |       |    |

| min                                       | 0.398                                       | 0.291 | 0.394 | 0.093 | 0.004      | 0.050 | 0.013 | 0.016 | 0° |

| max                                       | 0.413                                       | 0.299 | 0.419 | 0.104 | 0.012      | 0.050 | 0.020 | 0.050 | 8° |

For the latest version of this document, go to our website at:

www.melexis.com

Or for additional information contact Melexis direct:

### ■ Europe

Phone: +32 13 67 04 95

E-mail: sales\_europe@melexis.com

### All other locations

Phone: +1 603 223 2362

E-mail: sales\_usa@melexis.com

### **Important Notice**

Devices sold by Melexis are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. Melexis makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. Melexis reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with Melexis for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requiremental req

sustaining equipment are specifically not recommended without additional processing by Melexis for each application.

The information furnished by Melexis is believed to be correct and accurate. However, Melexis shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interrupt of business or indirect, special incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of Melexis' rendering of technical or other services.

© 2000 Melexis GmbH. All rights reserved.