# Mos integrated circuit $\mu \mathbf{PD62}$

# 4-BIT SINGLE-CHIP MICROCONTROLLER

# FOR INFRARED REMOTE CONTROL TRANSMISSION

#### DESCRIPTION

Equipped with low-voltage 1.8 V operation, a carrier generation circuit for infrared remote control transmission, a standby release function through key entry, and a programmable timer, the  $\mu$ PD62 is suitable for infrared remote control transmitters.

For the  $\mu$ PD62, we have made available the one-time PROM product  $\mu$ PD6P4B for program evaluation or smallquantity production.

#### FEATURES

- Program memory (ROM):  $512 \times 10$  bits

- Data memory (RAM):  $32 \times 4$  bits

- Built-in carrier generation circuit for infrared remote control

- 9-bit programmable timer : 1 channel

- Command execution time : 8  $\mu$ s (when operating at fx = 8 MHz: ceramic oscillation)

- Stack level : 1 level (Stack RAM is for data memory RF as well.)

- I/O pins (Ki/o) : 8 units

- Input pins (Kı) : 4 units

- Sense input pin (So) : 1 unit

- S<sub>1</sub>/LED pin (I/O) : 1 unit (When in output mode, this is the remote control transmission display pin.)

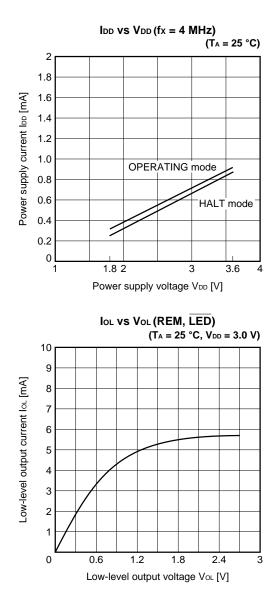

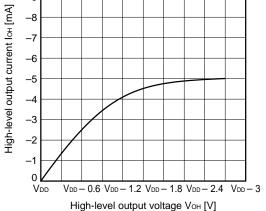

- Power supply voltage : VDD = 1.8 to 3.6 V (when operating at fx = 4 MHz)

- $V_{DD}$  = 2.2 to 3.6 V (when operating at fx = 8 MHz)

- Operating ambient temperature  $: T_A = -40$  to +85 °C

- Oscillator frequency : fx = 2.4 to 8 MHz

- POC circuit (Mask option)

#### **APPLICATION**

Infrared remote control transmitter (for AV and household electric appliances)

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

#### **ORDERING INFORMATION**

| Part Number                          | Package                       |

|--------------------------------------|-------------------------------|

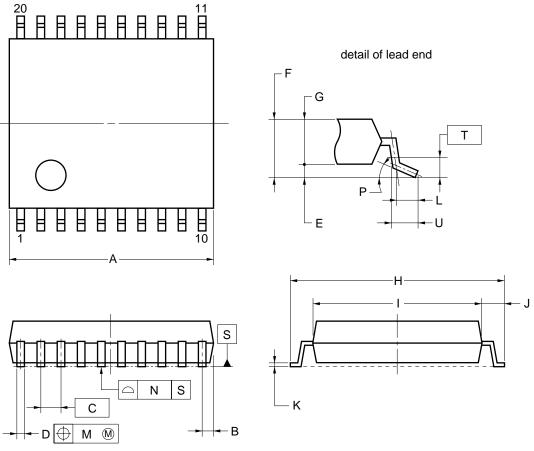

| $\mu$ PD62MC- $\times$ $\times$ -5A4 | 20-pin plastic SSOP (300 mil) |

**Remark** ××× indicates ROM code suffix.

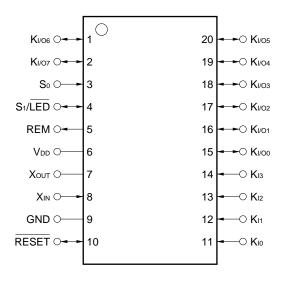

#### **PIN CONFIGURATION (TOP VIEW)**

#### 20-pin Plastic SSOP (300 mil)

• μPD62MC-×××-5A4

Caution The pin numbers of K<sub>1</sub> and K<sub>1/0</sub> are in the reverse order of the  $\mu$ PD6600A, and 6124A.

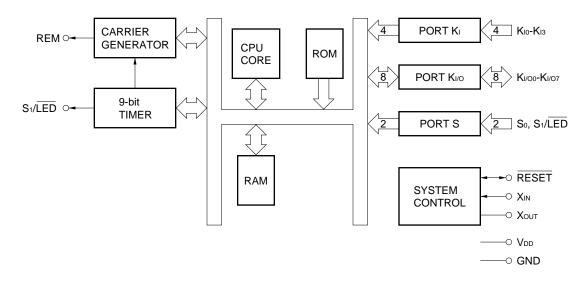

### **BLOCK DIAGRAM**

#### LIST OF FUNCTIONS

| Item                          | μPD62                                                                 | μPD6P4B                                                                  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|--|--|

| ROM capacity                  | $512 \times 10$ bits                                                  | $1002 \times 10$ bits                                                    |  |  |  |  |

|                               | Mask ROM                                                              | One-time PROM                                                            |  |  |  |  |

| RAM capacity                  | $32 \times 4$ bits                                                    |                                                                          |  |  |  |  |

| Stack                         | 1 level (multiplexed with RF of RAM)                                  |                                                                          |  |  |  |  |

| I/O pins                      | • Key input (Kı)                                                      | : 4                                                                      |  |  |  |  |

|                               | • Key I/O (KI/O)                                                      | : 8                                                                      |  |  |  |  |

|                               | <ul> <li>Key extended input (S<sub>0</sub>, S<sub>1</sub>)</li> </ul> | : 2                                                                      |  |  |  |  |

|                               | Remote control transmission display outp                              | ut ( $\overline{\text{LED}}$ ) : 1 (multiplexed with S <sub>1</sub> pin) |  |  |  |  |

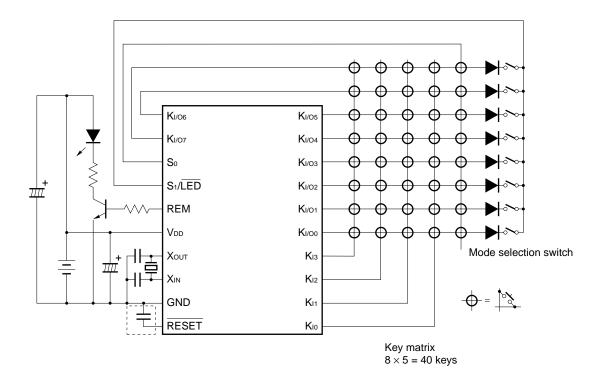

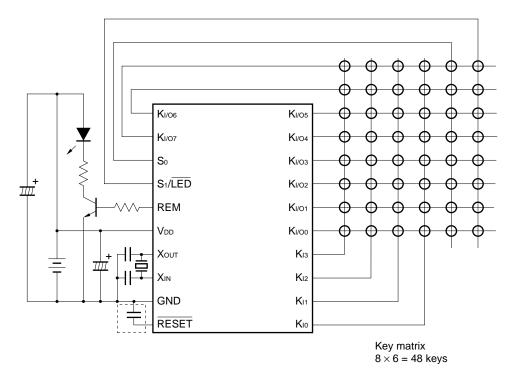

| Number of keys                | • 32 keys                                                             |                                                                          |  |  |  |  |

|                               | <ul> <li>48 keys (when extended by key extension input)</li> </ul>    |                                                                          |  |  |  |  |

|                               | 96 keys (when extended by key extension input and diode)              |                                                                          |  |  |  |  |

| Clock frequency               | Ceramic oscillation                                                   |                                                                          |  |  |  |  |

|                               | • fx = 2.4 to 8 MHz                                                   |                                                                          |  |  |  |  |

|                               | • fx = 2.4 to 4 MHz                                                   |                                                                          |  |  |  |  |

| Instruction execution time    | 8 µs (fx = 8 MHz)                                                     |                                                                          |  |  |  |  |

| Carrier frequency             | fx/8, fx/16, fx/64, fx/96, fx/128, fx/192, no ca                      | rrier (high level)                                                       |  |  |  |  |

| Timer                         | 9-bit programmable timer: 1 channel                                   |                                                                          |  |  |  |  |

| POC circuit                   | Mask option                                                           | Internal                                                                 |  |  |  |  |

| Supply voltage                | V <sub>DD</sub> = 1.8 to 3.6 V                                        | V <sub>DD</sub> = 2.2 to 3.6 V (f <sub>x</sub> = 2.4 to 4 MHz)           |  |  |  |  |

|                               |                                                                       | $V_{DD} = 2.7$ to 3.6 V (fx = 4 to 8 MHz)                                |  |  |  |  |

| Operating ambient temperature | • T <sub>A</sub> = -40 to +85 °C                                      |                                                                          |  |  |  |  |

|                               | • $T_A = -20$ to +70 °C (with POC circuit)                            |                                                                          |  |  |  |  |

| Package                       | • 20-pin plastic SSOP (300 mil)                                       | • 20-pin plastic SOP (300 mil)                                           |  |  |  |  |

|                               |                                                                       | <ul> <li>20-pin plastic SSOP (300 mil)</li> </ul>                        |  |  |  |  |

# TABLE OF CONTENTS

| 1. | PIN  | FUNCTIONS                               | 6  |

|----|------|-----------------------------------------|----|

|    | 1.1  | List of Pin Functions                   | 6  |

|    | 1.2  | INPUT/OUTPUT Circuits of Pins           | 7  |

|    | 1.3  | Dealing with Unused Pins                | 8  |

| 2. | INTE | ERNAL CPU FUNCTIONS                     | 9  |

|    | 2.1  | Program Counter (PC)                    | 9  |

|    | 2.2  | Stack Pointer (SP)                      | 9  |

|    | 2.3  | Address Stack Register (ASR (RF))       | 9  |

|    | 2.4  | Program Memory (ROM)                    | 10 |

|    | 2.5  | Data Memory (RAM)                       | 10 |

|    | 2.6  | Data Pointer (DP)                       | 11 |

|    | 2.7  | Accumulator (A)                         | 11 |

|    | 2.8  | Arithmetic and Logic Unit (ALU)         | 12 |

|    | 2.9  | Flags                                   | 12 |

|    |      | 2.9.1 Status flag (F)                   | 12 |

|    |      | 2.9.2 Carry flag (CY)                   | 13 |

| 3. | POF  | RT REGISTERS (PX)                       | 14 |

|    | 3.1  | Ki/o Port (P0)                          | 15 |

|    | 3.2  | Kı Port/Special Ports (P1)              | 16 |

|    |      | 3.2.1 Ki port (P11: bits 4-7 of P1)     | 16 |

|    |      | 3.2.2 So port (bit 2 of P1)             | 16 |

|    |      | 3.2.3 S1/LED (bit 3 of P1)              | 16 |

|    | 3.3  | Control Register 0 (P3)                 | 17 |

|    | 3.4  | Control Register 1 (P4)                 | 18 |

| 4. | тім  | ER                                      | 19 |

|    | 4.1  | Timer Configuration                     | 19 |

|    | 4.2  | Timer Operation                         |    |

|    | 4.3  | Carrier Output                          | 21 |

|    | 4.4  | Software Control of Timer Output        | 21 |

| 5. | STA  | NDBY FUNCTION                           | 22 |

|    | 5.1  | Outline of Standby Function             | 22 |

|    | 5.2  | Standby Mode Setup and Release          |    |

|    | 5.3  | Standby Mode Release Timing             |    |

| 6. | RES  |                                         | 26 |

| 7. | POC  | CIRCUIT (MASK OPTION)                   | 27 |

|    | 7.1  | Functions of POC Circuit                | 28 |

|    | 7.2  | Oscillation Check at Low Supply Voltage | 28 |

| 8. | SYS  | TEM CLOCK OSCILLATION CIRCUIT           | 29 |

| 9.                                                                          | INST         | RUCTION SET                                                            | 30 |  |  |  |  |  |

|-----------------------------------------------------------------------------|--------------|------------------------------------------------------------------------|----|--|--|--|--|--|

|                                                                             | 9.1          | Machine Language Output by Assembler                                   | 30 |  |  |  |  |  |

|                                                                             | 9.2          | Circuit Symbol Description                                             |    |  |  |  |  |  |

|                                                                             | 9.3          | Mnemonic to/from Machine Language (Assembler Output) Contrast Table    | 32 |  |  |  |  |  |

|                                                                             | 9.4          | Accumulator Operation Instructions                                     | 36 |  |  |  |  |  |

|                                                                             | 9.5          | Input/Output Instructions                                              |    |  |  |  |  |  |

|                                                                             | 9.6          | Data Transfer Instructions                                             |    |  |  |  |  |  |

|                                                                             | 9.7          | Branch Instructions                                                    | 42 |  |  |  |  |  |

|                                                                             | 9.8          | Subroutine Instructions                                                |    |  |  |  |  |  |

|                                                                             | 9.9          | Timer Operation Instruction                                            |    |  |  |  |  |  |

|                                                                             | 9.10         | Others                                                                 | 45 |  |  |  |  |  |

|                                                                             |              |                                                                        |    |  |  |  |  |  |

| 10.                                                                         |              | EMBLER RESERVED WORDS                                                  |    |  |  |  |  |  |

|                                                                             | 10.1         | Mask Option Directives                                                 |    |  |  |  |  |  |

|                                                                             |              | 10.1.1 OPTION and ENDOP directives                                     |    |  |  |  |  |  |

|                                                                             |              | 10.1.2 Mask option definition directive                                | 47 |  |  |  |  |  |

|                                                                             |              |                                                                        |    |  |  |  |  |  |

| 11.                                                                         | ELE          | CTRICAL SPECIFICATIONS                                                 | 48 |  |  |  |  |  |

|                                                                             |              |                                                                        |    |  |  |  |  |  |

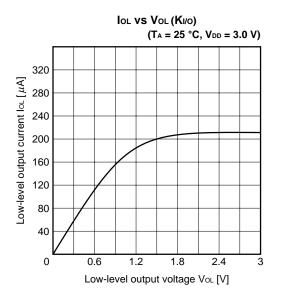

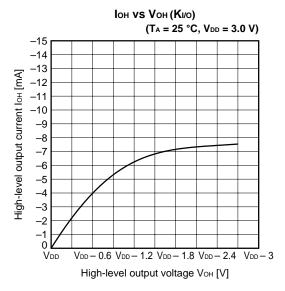

| 12.                                                                         | СНА          | RACTERISTIC CURVE (REFERENCE VALUES)                                   | 53 |  |  |  |  |  |

|                                                                             |              |                                                                        |    |  |  |  |  |  |

| 13.                                                                         | APP          | LIED CIRCUIT EXAMPLE                                                   | 55 |  |  |  |  |  |

|                                                                             | <b>D</b> 4 0 |                                                                        | 50 |  |  |  |  |  |

| 14.                                                                         | PAC          | KAGE DRAWINGS                                                          | 56 |  |  |  |  |  |

| 45                                                                          | DEC          | OMMENDED SOLDERING CONDITIONS                                          | 57 |  |  |  |  |  |

| 15.                                                                         | REC          | OMMENDED SOLDERING CONDITIONS                                          | 57 |  |  |  |  |  |

|                                                                             |              | DIX A. DEVELOPMENT TOOLS                                               | 59 |  |  |  |  |  |

| AP                                                                          |              |                                                                        | 30 |  |  |  |  |  |

| APPENDIX B. FUNCTIONAL COMPARISON BETWEEN $\mu$ PD62 AND OTHER SUBSERIES 59 |              |                                                                        |    |  |  |  |  |  |

| ٨P                                                                          |              | $\mu$ D. I GIG HORAL COMPANISON BETWEEN $\mu$ PD02 AND OTHER SUBSERIES | 72 |  |  |  |  |  |

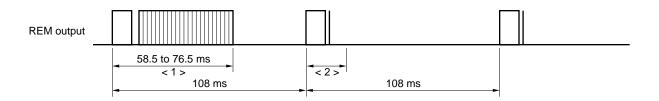

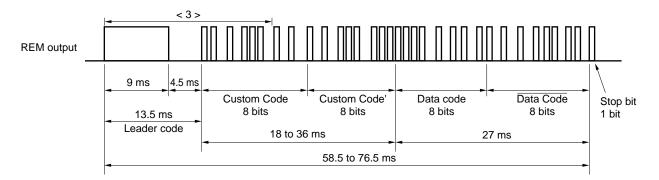

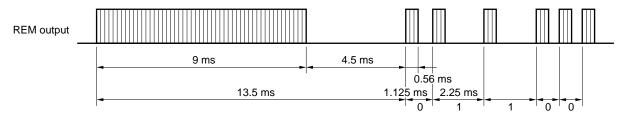

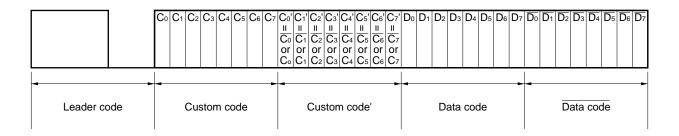

| AP                                                                          | ΡΕΝΓ         | DIX C. EXAMPLE OF REMOTE-CONTROL TRANSMISSION FORMAT                   | 60 |  |  |  |  |  |

|                                                                             |              |                                                                        |    |  |  |  |  |  |

## 1. PIN FUNCTIONS

#### 1.1 List of Pin Functions

| Pin No.         | Symbol                                  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Output Format                       | When Reset                         |

|-----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------|

| 1<br>2<br>15-20 | Ki/00-Ki/07                             | These pins refer to the 8-bit I/O ports. I/O switching can<br>be made in 8-bit units.<br>In INPUT mode, a pull-down resistor is added.<br>In OUTPUT mode, they can be used as the key scan<br>output of the key matrix.                                                                                                                                                                                                                                                                                                                                                                      | CMOS<br>push-pull <sup>Note 1</sup> | High-level output                  |

| 3               | So                                      | Refers to the input port.<br>Can also be used as the key return input of the key<br>matrix.<br>In INPUT mode, the availability of the pull-down resistor<br>of the S <sub>0</sub> and S <sub>1</sub> ports can be specified by software in<br>terms in 2-bit units.<br>If INPUT mode is canceled by software, this pin is placed<br>in OFF mode and enters the high-impedance state.                                                                                                                                                                                                         | _                                   | High-impedance<br>(OFF mode)       |

| 4               | S1/LED                                  | Refers to the I/O port.<br>In INPUT mode (S <sub>1</sub> ), this pin can also be used as the key<br>return input of the key matrix.<br>The availability of the pull-down resistor of the S <sub>0</sub> and S <sub>1</sub><br>ports can be specified by software in 2-bit units.<br>In OUTPUT mode ( $\overline{\text{LED}}$ ), it becomes the remote control<br>transmission display output (active low). When the<br>remote control carrier is output from the REM output, this<br>pin outputs the low level from the $\overline{\text{LED}}$ output synchronously<br>with the REM signal. | CMOS push-pull                      | High-level output<br>(LED)         |

| 5               | REM                                     | Refers to the infrared remote control transmission output.<br>The output is active high.<br>Carrier frequency: fx/8, fx/64, fx/96, high-level, fx/16,<br>fx/128, fx/192 (usable on software)                                                                                                                                                                                                                                                                                                                                                                                                 | CMOS push-pull                      | Low-level output                   |

| 6               | Vdd                                     | Refers to the power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                   | _                                  |

| 7<br>8          | Xout<br>Xin                             | These pins are connected to system clock ceramic resonators.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                   | Low level<br>(oscillation stopped) |

| 9               | GND                                     | Refers to the ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | _                                   | _                                  |

| 10              | RESET                                   | Normally, this pin is a system reset input. By inputting<br>a low level, the CPU can be reset. When resetting with<br>the POC circuit (mask option) a low level is output. A<br>pull-up resistor is incorporated.                                                                                                                                                                                                                                                                                                                                                                            | _                                   | -                                  |

| 11-14           | K <sub>10</sub> -K <sub>13</sub> Note 2 | These pins refer to the 4-bit input ports.<br>They can be used as the key return input of the key<br>matrix.<br>The use of the pull-down resistor can be specified by<br>software in 4-bit units.                                                                                                                                                                                                                                                                                                                                                                                            | _                                   | Input (low-level)                  |

**Notes 1.** Be careful about this because the drive capability of the low-level output side is held low.

2. In order to prevent malfunction, be sure to input a low level to more than one of pins K<sub>10</sub> to K<sub>13</sub> when reset is released (when RESET pin changes from low level to high level, or POC is released due to supply voltage startup).

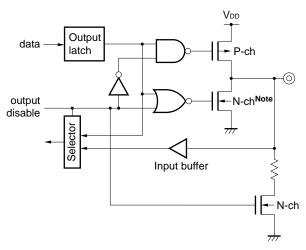

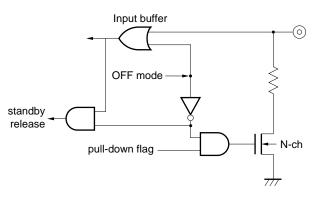

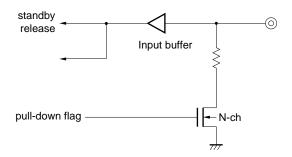

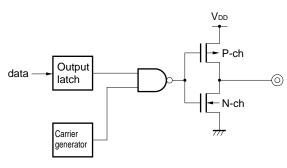

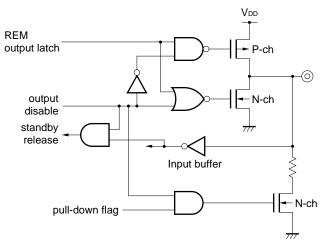

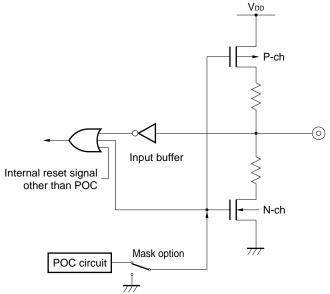

# 1.2 INPUT/OUTPUT Circuits of Pins

The input/output circuits of the  $\mu$ PD62 pins are shown in partially simplified forms below.

#### (1) KI/00-KI/07

(4) So

Note The drive capability is held low.

(2) KI0-KI3

(3) REM

(6) RESET

#### 1.3 Dealing with Unused Pins

The following connections are recommended for unused pins.

|           | Pin         | Connection                 |                             |  |  |  |

|-----------|-------------|----------------------------|-----------------------------|--|--|--|

|           | FIII        | Inside the microcontroller | Outside the microcontroller |  |  |  |

| Kı/o      | INPUT mode  | —                          | Leave open                  |  |  |  |

|           | OUTPUT mode | High-level output          |                             |  |  |  |

| REM       |             | _                          |                             |  |  |  |

| S1/LED    |             | OUTPUT mode (LED) setting  |                             |  |  |  |

| So        |             | OFF mode setting           | Directly connect these      |  |  |  |

| Kı        |             | _                          | pins to GND                 |  |  |  |

| RESETNote |             | Built-in POC circuit       | Leave open                  |  |  |  |

Table 1-1. Connections for Unused Pins

- **Note** If the circuit is an applied one requiring high reliability, be sure to design it in such a manner that the RESET signal is entered externally.

- Caution The I/O mode and the terminal output level are recommended to be fixed by setting them repeatedly in each loop of the program.

#### 2. INTERNAL CPU FUNCTIONS

#### 2.1 Program Counter (PC): 10 Bits

Refers to the binary counter that holds the address information of the program memory.

#### Figure 2-1. Program Counter Organization

| PC | PC9 | PC8 | PC7 | PC6 | PC5 | PC4 | PC3 | PC2 | PC1 | PC0 |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

The program counter contains the address of the instruction that should be executed next. Normally, the counter contents are automatically incremented in accordance with the instruction length (byte count) each time an instruction is executed.

However, when executing JUMP instructions (JMP, JC, JNC, JF, JNF), the program counter contains the jump destination address written in the operand.

When executing the subroutine call instruction (CALL), the call destination address written in the operand is entered in the PC after the PC contents at the time are saved in the address stack register (ASR). If the return instruction (RET) is executed after the CALL instruction is executed, the address saved in the ASR is restored to the PC.

When reset, the value of the program counter becomes "000H".

#### 2.2 Stack Pointer (SP): 1 Bit

Refers to the 1-bit register which holds the status of the address stack register.

The stack pointer contents are incremented when the call instruction (CALL) is executed; they are decremented when the return instruction (RET) is executed.

When reset, the stack pointer contents are cleared to "0".

When the stack pointer overflows (stack level 2 or more) or underflows, the CPU is hung up thus a system reset signal is generated and the PC becoming "000H".

As no instruction is available to set a value directly for the stack pointer, it is not possible to operate the pointer by means of a program.

#### 2.3 Address Stack Register (ASR (RF)): 10 Bits

The address stack register saves the return address of the program after a subroutine call instruction is executed. The low-order 8 bits are arranged in the RF of the data memory as a dual-function RAM. The register holds

the ASR value even after the RET is executed.

When reset, it holds the previous data (undefined when turning on the power).

#### Caution If the RF is accessed as the data memory, the high-order 2 bits of the ASR become undefined.

#### Figure 2-2. Address Stack Register Organization

| ASR | ASR9 | ASR8 | ASR7 | ASR6 | ASR5 | ASR4 | ASR3 | ASR2 | ASR1 | ASR0 |

|-----|------|------|------|------|------|------|------|------|------|------|

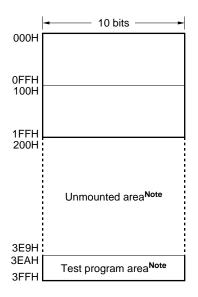

#### 2.4 Program Memory (ROM): 512 steps $\times$ 10 bits

The ROM consists of 10 bits per step, and is addressed by the program counter.

The program memory stores programs and table data, etc.

The 22 steps from 3EAH to 3FFH cannot be used in the test program area.

#### Figure 2-3. Program Memory Map

**Note** The unmounted area and the test program area are so designed that a program or data placed in either of them by mistake is returned to the 000H address.

#### 2.5 Data Memory (RAM): $32 \times 4$ Bits

The data memory, which is a static RAM consisting of  $32 \times 4$  bits, is used to retain processed data. The data memory is sometimes processed in 8-bit units. R0 can be used as the ROM data pointer.

RF is also used as the ASR.

When reset, R0 is cleared to "00H" and R1 to RF retain the previous data (undefined when turning on the power).

| <u>R0</u>             |             | $\rightarrow$ DP (refer to <b>2.6 Data Pointer (DP)</b> ) |

|-----------------------|-------------|-----------------------------------------------------------|

| <b>R</b> 10           | R00         |                                                           |

| R1                    |             |                                                           |

| R11                   | <b>R</b> 01 |                                                           |

| R2                    |             |                                                           |

| R <sub>12</sub><br>R3 | <b>R</b> 02 |                                                           |

| R13                   | Ros         |                                                           |

|                       | 1103        | -                                                         |

| R <sub>14</sub>       | <b>R</b> 04 |                                                           |

| R5                    |             |                                                           |

| R15                   | <b>R</b> 05 |                                                           |

| R6                    |             |                                                           |

| R16                   | R06         |                                                           |

| R7                    |             |                                                           |

| R17                   | <b>R</b> 07 |                                                           |

| R8                    |             |                                                           |

| R18<br>R9             | R08         |                                                           |

| R19                   | R09         | -                                                         |

| RA                    | 1109        | -                                                         |

| R <sub>1A</sub>       | ROA         |                                                           |

| RB                    |             |                                                           |

| R1B                   | Rob         |                                                           |

| RC                    |             |                                                           |

| R1C                   | Roc         |                                                           |

|                       | D           |                                                           |

| R <sub>1D</sub>       | Rod         | _                                                         |

| R1E RE                | ROE         | _                                                         |

| RF                    | IN UE       |                                                           |

| R1F                   | ROF         | →ASR (refer to 2.3 Address Stack Register (ASR (RF)))     |

#### Figure 2-4. Data Memory Organization

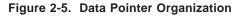

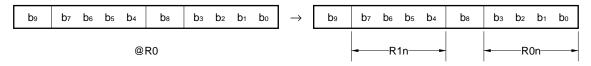

#### 2.6 Data Pointer (DP): 10 Bits

The ROM data table can be referenced by setting the ROM address in the data pointer to call the ROM contents. The low-order 8 bits of the ROM address are specified by R0 of the data memory; and the high-order 2 bits by bits 4 and 5 of the P3 register (CR0).

When reset, the pointer contents become "000H".

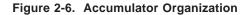

#### 2.7 Accumulator (A): 4 Bits

The accumulator, which refers to a register consisting of 4 bits, plays a leading role in performing various operations.

When reset, the accumulator contents are left undefined.

#### 2.8 Arithmetic and Logic Unit (ALU): 4 Bits

The arithmetic and logic unit (ALU), which refers to an arithmetic circuit consisting of 4 bits, executes simple manipulations with priority given to logical operations.

#### 2.9 Flags

#### 2.9.1 Status flag (F)

Pin and timer statuses can be checked by executing the STTS instruction to check the status flag. The status flag is set (to 1) in the following cases.

- If the condition specified with the operand is met when the STTS instruction has been executed

- When STANDBY mode is canceled.

- When the cancelation condition is met at the point of executing the HALT instruction. (In this case, the system is not placed in STANDBY mode.)

Conversely, the status flag is cleared (to 0) in the following cases:

- If the condition specified with the operand is not met when the STTS instruction has been executed.

- When the status flag has been set (to 1), the HALT instruction executed, but the cancelation condition is not met at the point of executing the HALT instruction. (In this case, the system is not placed in STANDBY mode.)

| Operand Value of STTS Instruction |                                     |    | struction | Condition for Status Flag (F) to be Set                      |  |  |  |  |

|-----------------------------------|-------------------------------------|----|-----------|--------------------------------------------------------------|--|--|--|--|

| bз                                | b2                                  | b1 | bo        | Condition for Status Flag (F) to be Set                      |  |  |  |  |

| 0                                 | 0 0 0                               |    | 0         | High level is input to at least one of K <sub>I</sub> pins.  |  |  |  |  |

|                                   | 0                                   | 1  | 1         | High level is input to at least one of K <sub>I</sub> pins.  |  |  |  |  |

|                                   | 1                                   | 1  | 0         | High level is input to at least one of Ki pins.              |  |  |  |  |

|                                   | 1                                   | 0  | 1         | The down counter of the timer is 0.                          |  |  |  |  |

| 1                                 | Either of the combinations          |    | binations | [The following condition is added in addition to the above.] |  |  |  |  |

|                                   | of $b_2$ , $b_1$ , and $b_0$ above. |    |           | High level is input to at least one of $S_0$ and $S_1$ pins. |  |  |  |  |

#### Table 2-1. Conditions for Status Flag (F) to be Set by STTS Instruction

#### 2.9.2 Carry flag (CY)

The carry flag is set (to 1) in the following cases:

- If the ANL instruction or the XRL instruction is executed when bit 3 of the accumulator is "1" and bit 3 of the operand is "1".

- If the RL instruction or the RLZ instruction is executed when bit 3 of the accumulator is "1".

- If the INC instruction or the SCAF instruction is executed when the value of the accumulator is 0FH.

The carry flag is cleared (to 0) in the following cases:

- If the ANL instruction or the XRL instruction is executed when at least either bit 3 of the accumulator or bit 3 of the operand is "0".

- If the RL instruction or the RLZ instruction is executed when bit 3 of the accumulator is "0".

- If the INC instruction or the SCAF instruction is executed when the value of the accumulator is other than 0FH.

- If the ORL instruction is executed.

- When Data is written to the accumulator by the MOV instruction or the IN instruction.

# 3. PORT REGISTERS (PX)

The K<sub>1/o</sub> port, the K<sub>1</sub> port, the special ports (S<sub>0</sub>, S<sub>1</sub>/ $\overline{\text{LED}}$ ), and the control register are treated as port registers. At reset, port register values are shown below.

|               | Port Register                   |                 |                    |               |               |                  |                     |                      |  |  |

|---------------|---------------------------------|-----------------|--------------------|---------------|---------------|------------------|---------------------|----------------------|--|--|

|               | P0                              |                 |                    |               |               |                  |                     |                      |  |  |

|               | Р                               | 10              |                    |               | P             | 00               |                     |                      |  |  |

| <b>K</b> I/07 | K1/06                           | K1/05           | <b>K</b> I/04      | Кі/оз         | <b>K</b> I/02 | <b>K</b> I/01    | K1/00               |                      |  |  |

|               |                                 |                 | Р                  | 1             |               |                  |                     | × FH <sup>Note</sup> |  |  |

|               | Р                               | 11              |                    |               | P             |                  |                     |                      |  |  |

| Кıз           | Kı2                             | Kıı             | Kıo                | S1/LED        | S₀            | 1                | 1                   |                      |  |  |

|               |                                 |                 | P3 (Contro         | l register 0) | 1             |                  |                     | 03H                  |  |  |

|               | P <sub>13</sub> P <sub>03</sub> |                 |                    |               |               |                  |                     |                      |  |  |

| 0             | 0                               | DP۹             | DP <sub>8</sub>    | TCTL          | CARY          | MOD <sub>1</sub> | MODo                |                      |  |  |

|               | 26H                             |                 |                    |               |               |                  |                     |                      |  |  |

|               | P <sub>14</sub> P <sub>04</sub> |                 |                    |               |               |                  |                     |                      |  |  |

| 0             | 0                               | Kı<br>pull-down | S₀/S₁<br>pull-down | 0             | S1/LED mode   | Ki/o mode        | S <sub>0</sub> mode |                      |  |  |

Note  $\times$ : Refers to the value based on the K<sub>I</sub> pin state.

| Table 3-1 | Relationship | between | Ports | and their | Read/Write  |

|-----------|--------------|---------|-------|-----------|-------------|

|           | Relationship | Dermeen | FUILS | and then  | iteau/wille |

| Port Name      | INPUT      | Mode         | OUTPUT Mode  |              |  |

|----------------|------------|--------------|--------------|--------------|--|

| Fort Name      | Read Write |              | Read         | Write        |  |

| Kı/o           | Pin state  | Output latch | Output latch | Output latch |  |

| Kı             | Pin state  | —            | —            | —            |  |

| S <sub>0</sub> | Pin state  | —            | Note         | —            |  |

| S1/LED         | Pin state  | —            | Pin state    | —            |  |

**Note** When in OFF mode, "1" is normally read.

#### 3.1 Ki/o Port (P0)

The K<sub>1/0</sub> port is an 8-bit input/output port for key scan output.

INPUT/OUTPUT mode is set by bit 1 of the P4 register.

If a read instruction is executed, the pin state can be read in INPUT mode, whereas the output latch contents can be read in OUTPUT mode.

If the write instruction is executed, data can be written to the output latch regardless of INPUT or OUTPUT mode. When reset, the port is placed in OUTPUT mode; and the value of the output latch (P0) becomes 1111 1111B. The K<sub>I/O</sub> port contains the pull-down resistor, allowing pull-down in INPUT mode only.

Caution During double pressing of a key, a high-level output and a low-level output may coincide with each other at the K<sub>I/O</sub> port. To avoid this, the low-level output current of the K<sub>I/O</sub> port is held low. Therefore, be careful when using the K<sub>I/O</sub> port for purposes other than key scan output. The K<sub>I/O</sub> port is so designed that, even when connected directly to V<sub>DD</sub> within the normal supply voltage range (V<sub>DD</sub> = 1.8 to 3.6 V), no problem may occur.

#### Table 3-2. Ki/o Port (P0)

| Bit  | b7    | b6    | b₅    | b4    | bз    | b <sub>2</sub> | b1    | bo    |

|------|-------|-------|-------|-------|-------|----------------|-------|-------|

| Name | K1/07 | K1/06 | K1/05 | K1/04 | Кі/оз | K1/02          | K1/01 | K1/00 |

$b_0\text{-}b_7$  : In reading : In INPUT mode, the K1/0 pin's state is read.

In OUTPUT mode, the Ki/o pin's output latch contents are read.

In writing : Data is written to the Ki/o pin's output latch regardless of INPUT or OUTPUT mode.

## 3.2 KI Port/Special Ports (P1)

#### 3.2.1 Ki port (P11: bits 4-7 of P1)

The K<sub>1</sub> port is to the 4-bit input port for key entry.

The pin state can be read.

Software can be used to set the availability of the pull-down resistor of the K<sub>1</sub> port in 4-bit units by means of bit 5 of the P4 register.

When reset, the pull-down resistor is connected.

#### Table 3-3. Ki/Special Port Register (P1)

| Bit  | b7  | be  | b₅  | b4  | bз     | b <sub>2</sub> | b1        | bo     |

|------|-----|-----|-----|-----|--------|----------------|-----------|--------|

| Name | Кіз | K12 | KI1 | KIO | S1/LED | So             | (Fixed to | o "1") |

b2 : In INPUT mode, state of the So pin is read (Read only).

In OFF mode, this bit is fixed to "1".

b3 : The state of the S1/LED pin is read regardless of INPUT/OUTPUT mode (Read only).

$b_4$ - $b_7$ : The state of the K<sub>I</sub> pin is read (Read only).

Caution In order to prevent malfunction, be sure to input a low level to more than one of pins K<sub>10</sub> to K<sub>13</sub> when reset is released (when RESET pin changes from low level to high level, or POC is released due to supply voltage startup).

#### 3.2.2 So port (bit 2 of P1)

The  $S_0$  port is the INPUT/OFF mode port.

The pin state can be read by setting this port to INPUT mode with bit 0 of the P4 register.

In INPUT mode, software can be used to set the availability of the pull-down resistor of the S<sub>0</sub> and S<sub>1</sub>/ $\overline{\text{LED}}$  port in 2-bit units by means of bit 4 of the P4 register.

If INPUT mode is canceled (thus set to OFF mode), the pin becomes high-impedance but it also makes that the through current does not flow internally. In OFF mode, "1" can be read regardless of the pin state.

When reset, it is set to OFF mode, thus becoming high-impedance.

#### 3.2.3 S<sub>1</sub>/LED (bit 3 of P1)

The  $S_1/\overline{LED}$  port is the input/output port.

It uses bit 2 of the P4 register to set INPUT or OUTPUT mode. The pin state can be read in both INPUT mode and OUTPUT mode.

When in INPUT mode, software can be used to set the availability of the pull-down resistor of the S<sub>0</sub> and  $S_1/\overline{\text{LED}}$  ports in 2-bit units by means of bit 4 of the P4 register.

When in OUTPUT mode, the pull-down resistor is automatically disconnected thus becoming the remote control transmission display pin (refer to **4. TIMER**).

When reset, it is placed in OUTPUT mode, and high level is output.

# 3.3 Control Register 0 (P3)

Control register 0 consists of 8 bits. The contents that can be controlled are as shown below. When reset, the register becomes 0000 0011B.

| Bit      |    | b7     | b6     | b₅                | b4  | bз   | b <sub>2</sub> | b1         | bo               |

|----------|----|--------|--------|-------------------|-----|------|----------------|------------|------------------|

| Name     |    | _      | _      | DP (Data pointer) |     | TCTL | CARY           | MOD1       | MOD <sub>0</sub> |

|          |    |        |        | DP۹               | DP8 |      |                |            |                  |

| Set      | 0  | Fixed  | Fixed  | 0                 | 0   | 1/1  | ON             | Refer to 1 | Table 3-5.       |

| value    | 1  | to "0" | to "0" | 1                 | 1   | 1/2  | OFF            |            |                  |

| When res | et | 0      | 0      | 0                 | 0   | 0    | 0              | 1          | 1                |

Table 3-4.

Control Register 0 (P3)

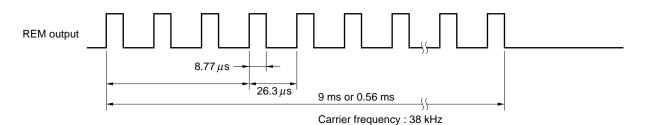

$b_0,\,b_1\,$  : These bits specify the carrier frequency and duty ratio of the REM output.

b2 : This bit specifies the availability of the carrier of the frequency specified by b<sub>0</sub> and b<sub>1</sub>.

"0" = ON (with carrier); "1" = OFF (without carrier; high level)

$b_3$   $\hfill :$  This bit changes the carrier frequency and the timer clock's frequency division ratio.

"0" = 1/1 (carrier frequency: the specified value of  $b_0$  and  $b_1$ ; timer clock: fx/64)

"1" = 1/2 (carrier frequency: half of the specified value of b<sub>0</sub> and b<sub>1</sub>; timer clock: fx/128)

| bз | b2 | b1 | bo | Timer Clock | Carrier Frequency (Duty Ratio) |

|----|----|----|----|-------------|--------------------------------|

| 0  | 0  | 0  | 0  | fx/64       | fx/8 (Duty 1/2)                |

|    |    | 0  | 1  |             | fx/64 (Duty 1/2)               |

|    |    | 1  | 0  |             | fx/96 (Duty 1/2)               |

|    |    | 1  | 1  |             | fx/96 (Duty 1/3)               |

|    | 1  | ×  | ×  |             | Without carrier (high level)   |

| 0  | 0  | 0  | 0  | fx/128      | fx/16 (Duty 1/2)               |

|    |    | 0  | 1  |             | fx/128 (Duty 1/2)              |

|    |    | 1  | 0  |             | fx/192 (Duty 1/2)              |

|    |    | 1  | 1  |             | fx/192 (Duty 1/3)              |

|    | 1  | ×  | ×  |             | Without carrier (high level)   |

#### Table 3-5. Timer Clock and Carrier Frequency Setup

$b_4$  and  $b_5~$  : These bits specify the high-order 2 bits (DP\_8 and DP\_9) of ROM's data pointer.

**Remark** ×: don't care

## 3.4 Control Register 1 (P4)

Control register 1 consists of 8 bits. The contents that can be controlled are as shown below. When reset, the register becomes 0010 0110B.

| Bit      |    | b7     | b6     | b₅        | b4        | bз     | b <sub>2</sub> | b1   | bo   |

|----------|----|--------|--------|-----------|-----------|--------|----------------|------|------|

| Name     |    | _      | _      | Kı        | S0/S1     | —      | S1/LED         | Kı/o | S₀   |

|          |    |        |        | Pull-down | Pull-down |        | mode           | mode | mode |

| Set      | 0  | Fixed  | Fixed  | OFF       | OFF       | Fixed  | S1             | IN   | OFF  |

| value    | 1  | to "0" | to "0" | ON        | ON        | to "0" | LED            | OUT  | IN   |

| When res | et | 0      | 0      | 1         | 0         | 0      | 1              | 1    | 0    |

#### Table 3-6. Control Register 1 (P4)

- b0 : Specifies the input mode of the S0 port. "0" = OFF mode (high impedance); "1" = IN (INPUT mode).

- $b_1 \ :$  Specifies the I/O mode of the Kı/o port.

- "0" = IN (INPUT mode); "1" = OUT (OUTPUT mode).

- b<sub>2</sub> : Specifies the I/O mode of the S<sub>1</sub>/ $\overline{\text{LED}}$  port. "0" = S<sub>1</sub> (INPUT mode); "1" =  $\overline{\text{LED}}$  (output mode).

- b4 : Specifies the availability of the pull-down resistor in S<sub>0</sub>/S<sub>1</sub> port INPUT mode. "0" = OFF (unavailable);

"1" = ON (available)

- b5 : Specifies the availability of the pull-down resistor in K<sub>1</sub> port. "0" = OFF (unavailable);

"1" = ON (available).

Remark In OUTPUT mode or in OFF mode, all the pull-down resistors are automatically disconnected.

### 4. TIMER

#### 4.1 Timer Configuration

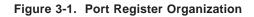

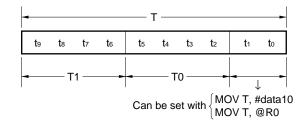

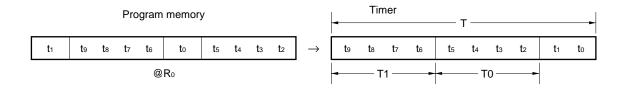

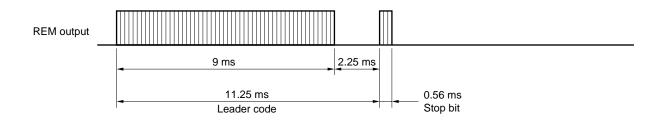

The timer is the block used for creating a remote control transmission pattern. As shown in Figure 4-1, it consists of a 9-bit down counter (t<sub>8</sub> to t<sub>0</sub>), a flag (t<sub>9</sub>) permitting the 1-bit timer output, and a zero detecting circuit.

Figure 4-1. Timer Configuration

#### 4.2 Timer Operation

The timer starts (counting down) when a value other than 0 is set for the down counter with a timer operation instruction. The timer operation instructions for making the timer start operation are shown below:

MOV T0, A MOV T1, A MOV T, #data10 MOV T, @R0

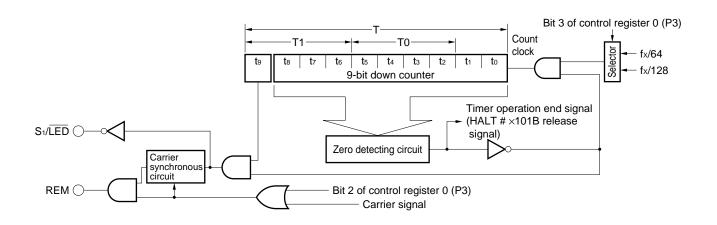

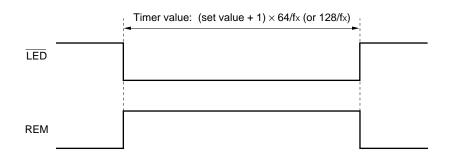

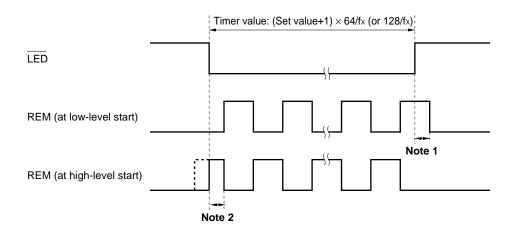

The down counter is decremented (-1) in the cycle of 64/fx or  $128/fx^{Note}$ . If the value of the down counter becomes 0, the zero detecting circuit generates the timer operation end signal to stop the timer operation. At this time, if the timer is in HALT mode (HALT #×101B) waiting for the timer to stop its operation, the HALT mode is canceled and the instruction following the HALT instruction is executed. The output of the timer operation end signal is continued while the down counter is 0 and the timer is stopped. There is the following relational expression between the timer's time and the down counter's set value.

Timer time = (Set value + 1)  $\times$  64/fx (or 128/fx<sup>Note</sup>)

Note This becomes 128/fx if bit 3 of the control register is set (to 1).

By setting 1 for the flag (t<sub>9</sub>) which enables the timer output, the timer can output its operation status from the  $S_1/\overline{\text{LED}}$  pin and the REM pin. The REM pin can also output the carrier while the timer is in operation.

|                 | S1/LED Pin | REM Pin                                |

|-----------------|------------|----------------------------------------|

| Timer operating | L          | H (or carrier output <sup>Note</sup> ) |

| Timer halting   | Н          | L                                      |

Note The carrier output results if bit 2 of the control register 0 is cleared (to 0).

Figure 4-2. Timer Output (when carrier is not output)

#### 4.3 Carrier Output

The carrier for remote-controlled transmission can be output from the REM pin by clearing (to 0) bit 2 of the control register 0.

As shown in Figure 4-3, in the case where the timer stops when the carrier is at a high level, the carrier continues to be output until its next fall and then stops due to the function of the carrier synchronous circuit. When the timer starts operation, however, the high-level width of the first carrier may become shorter than the specified width.

Figure 4-3. Timer Output (when carrier is output)

Notes 1. Error when the REM output ends: Lead by "the carrier's low-level width" to lag by "the carrier's highlevel width"

2. Error of the carrier's high-level width: 0 to "the carrier's high-level width"

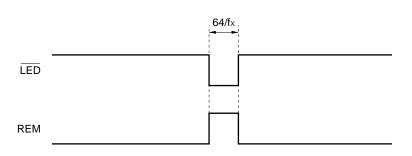

#### 4.4 Software Control of Timer Output

The timer output can be controlled by software. As shown in Figure 4-4, the pulse with a minimum width of 1-instruction cycle (64/fx) can be output.

#### Figure 4-4. Pulse Output of 1-Instruction Cycle Width

: MOV T, #000000000B; low-level output from the REM pin :

- MOV T, #100000000B; high-level output from the REM pin

- MOV T, #000000000B; low-level output from the REM pin

#### 5. STANDBY FUNCTION

#### 5.1 Outline of Standby Function

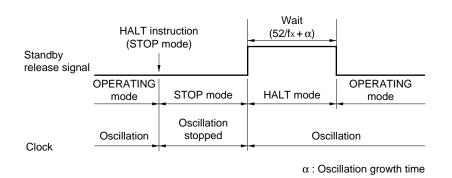

To save current consumption, two types of standby modes, i.e., HALT mode and STOP mode, are made available. In STOP mode, the system clock stops oscillation. At this time, the XIN and XOUT pins are fixed at a low level. In HALT mode, CPU operation halts, while the system clock continues oscillation. When in HALT mode, the timer (including REM output and LED output) operates.

In either STOP mode or HALT mode, the statuses of the data memory, accumulator, and port register, etc. immediately before the standby mode is set are retained. Therefore, make sure to set the port status for the system so that the current consumption of the whole system is suppressed before the standby mode is set.

|                           |             |    | STOP Mode HALT Mode                                       |                       |  |  |

|---------------------------|-------------|----|-----------------------------------------------------------|-----------------------|--|--|

| Setting instruction       |             |    | HALT instruction                                          |                       |  |  |

| Clock oscillation circuit |             |    | Oscillation stopped                                       | Oscillation continued |  |  |

|                           | CPU         |    | Operation halted                                          | Operation halted      |  |  |

|                           | Data memory |    | Immediately preceding status retained                     |                       |  |  |

| Operation                 | Accumulator |    | Immediately preceding status retained                     |                       |  |  |

| statuses                  | Flag        | F  | • 0 (When 1, the flag is not placed in the standby mode.) |                       |  |  |

|                           |             | CY | Immediately preceding status retained                     |                       |  |  |

| Port register             |             |    | Immediately preceding status retained                     |                       |  |  |

|                           | Timer       |    | Operation halted                                          | Operable              |  |  |

|                           |             |    | (The count value is reset to "0")                         |                       |  |  |

#### Table 5-1. Statuses During Standby Mode

Cautions 1. Write the NOP instruction as the first instruction after STOP mode is canceled.

- 2. When standby mode is canceled, the status flag (F) is set (to 1).

- 3. If, at the point the standby mode has been set, its cancelation condition is met, then the system is not placed in the standby mode. However, the status flag (F) is set (1).

#### 5.2 Standby Mode Setup and Release

The standby mode is set with the HALT #b<sub>3</sub>b<sub>2</sub>b<sub>1</sub>b<sub>0</sub>B instruction for both STOP mode and HALT mode. For the standby mode to be set, the status flag (F) is required to have been cleared (to 0).

The standby mode is released by the release condition specified with the RESET (RESET input; POC) or the operand of HALT instruction. If the standby mode is released, the status flag (F) is set (to 1).

Even when the HALT instruction is executed in the state that the status flag (F) has been set (to 1), the standby mode is not set. If the release condition is not met at this time, the status flag is cleared (to 0). If the release condition is met, the status flag remains set (to 1).

Even in the case when the release condition has been already met at the point that the HALT instruction is executed, the standby mode is not set. Here, also, the status flag (F) is set (to 1).

Caution Depending on the status of the status flag (F), the HALT instruction may not be executed. Be careful about this. For example, when setting HALT mode after checking the key status with the STTS instruction, the system does not enter HALT mode as long as the status flag (F) remains set (to 1) thus sometimes performing an unintended operation. In this case, the intended operation can be realized by executing the STTS instruction immediately after timer setting to clear (to 0) the status flag.

| Example | STTS<br>: | #03H        | ;To check the Ki pin status.                                                                      |

|---------|-----------|-------------|---------------------------------------------------------------------------------------------------|

|         | •         |             | ;To set the timer<br><b>:To clear the status flag</b>                                             |

|         |           | (During thi | s time, be sure not to execute an instruction that may set the status flag.)<br>;To set HALT mode |

#### Table 5-2. Addresses Executed After Standby Mode Release

| Release Condition                    | Address Executed After Release             |  |  |

|--------------------------------------|--------------------------------------------|--|--|

| Reset                                | 0 address                                  |  |  |

| Release condition shown in Table 5-3 | The address following the HALT instruction |  |  |

|     | Operand Value of<br>HALT Instruction |     |    | Setting Mode           | Precondition for Setup                                        | Release Condition                                           |

|-----|--------------------------------------|-----|----|------------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| bз  | b2                                   | bı  | bo | -                      |                                                               |                                                             |

| 0   | 0                                    | 0   | 0  | STOP                   | All K <sub>VO</sub> pins are high-level output.               | High level is input to at least one of K <sub>I</sub> pins. |

|     | 0                                    | 1   | 1  | STOP                   | All K <sub>VO</sub> pins are high-level output.               | High level is input to at least one of K <sub>I</sub> pins. |

|     | 1                                    | 1   | 0  | STOP <sup>Note 1</sup> | The K <sub>I/00</sub> pin is high-level output.               | High level is input to at least one of K <sub>1</sub> pins. |

| 1   | Any of                               | the |    | STOP                   | [The following condition is ad                                | ded in addition to the above.]                              |

|     | combinations of                      |     |    |                        |                                                               | High level is input to at least one                         |

|     | b2b1b0 above                         |     |    |                        | of S <sub>0</sub> and S <sub>1</sub> pins <sup>Note 2</sup> . |                                                             |

| 0/1 | 1                                    | 0   | 1  | HALT                   |                                                               | When the timer's down counter is 0                          |

#### Table 5-3. Standby Mode Setup (HALT #b3b2b1b0B) and Release Conditions

- **Notes 1.** When setting HALT #×110B, configure a key matrix by using the K<sub>1/00</sub> pin and the K<sub>1</sub> pin so that an internal reset takes effect at the time of program hang-up.

- At least one of the S<sub>0</sub> and S<sub>1</sub> pins (the pin used for releasing the standby) must be in INPUT mode. (The internal reset does not take effect even when both pins are in OUTPUT mode.)

- Cautions 1. The internal reset takes effect when the HALT instruction is executed with an operand value other than that above or when the precondition has not been satisfied when executing the HALT instruction.

- 2. If STOP mode is set when the timer's down counter is not 0 (timer operating), the system is placed in STOP mode only after all the 10 bits of the timer's down counter and the timer output permit flag are cleared to 0.

- 3. Write the NOP instruction as the first instruction after STOP mode is released.

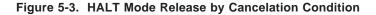

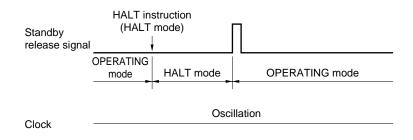

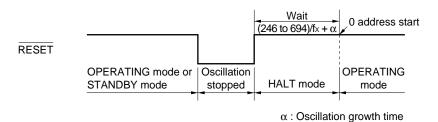

- 5.3 Standby Mode Release Timing

- (1) STOP Mode Release Timing

#### Figure 5-1. STOP Mode Cancelation by Release Condition

Caution When a release condition is established in the STOP mode, the device is released from the STOP mode, and goes into a wait state. At this time, if the release condition is not held, the device goes into STOP mode again after the wait time has elapsed. Therefore, when releasing the STOP mode, it is necessary to hold the release condition longer than the wait time.

#### Figure 5-2. STOP Mode Release by RESET Input

#### (2) HALT Mode Release Timing

$\boldsymbol{\alpha}$  : Oscillation growth time

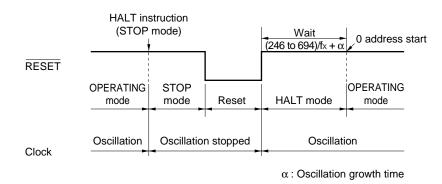

# 6. RESET PIN

The system reset takes effect by inputting low level to the  $\overline{\text{RESET}}$  pin.

While the RESET pin is at low level, the system clock oscillator is stopped and the XIN and XOUT pins are fixed to the GND.

If the RESET pin is raised from low level to high level, it executes the program from the 0 address after counting 246 to 694 of the system clock (fx).

Figure 6-1. Reset Operation by RESET Input

The RESET pin outputs low level when the POC circuit (mask option) is in operation.

# Caution When connecting a reset IC to the RESET pin, ensure that the IC is of the N-ch open drain output type.

| Table 6-1. Hardware Statuses After Reset | Table 6-1. | Hardware | Statuses | After | Reset |

|------------------------------------------|------------|----------|----------|-------|-------|

|------------------------------------------|------------|----------|----------|-------|-------|

| Hard            | ware         |    | <ul> <li>RESET Input in Operation</li> <li>Resetting by Internal POC Circuit in Operation</li> <li>Resetting by Other Factors<sup>Note 1</sup></li> </ul> | <ul> <li>RESET Input During STANDBY Mode</li> <li>Resetting by the Internal POC Circuit During<br/>STANDBY Mode</li> </ul> |  |  |  |  |  |  |

|-----------------|--------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| PC (10 bits)    |              |    | 000H                                                                                                                                                      |                                                                                                                            |  |  |  |  |  |  |

| SP (1 bit)      |              |    | 0B                                                                                                                                                        |                                                                                                                            |  |  |  |  |  |  |

| Data            | R0 = DP 000H |    |                                                                                                                                                           |                                                                                                                            |  |  |  |  |  |  |

| memory          | R1-R         | F  | Undefined                                                                                                                                                 | Previous status retained                                                                                                   |  |  |  |  |  |  |

| Accumulator (A) |              |    | Undefined                                                                                                                                                 | Undefined                                                                                                                  |  |  |  |  |  |  |

| Status fla      | g (F)        |    | 0B                                                                                                                                                        |                                                                                                                            |  |  |  |  |  |  |

| Carry flag      | (CY)         |    | 0B                                                                                                                                                        |                                                                                                                            |  |  |  |  |  |  |

| Timer (10       | bits)        |    | 000H                                                                                                                                                      |                                                                                                                            |  |  |  |  |  |  |

| Port regis      | ter          | P0 | FFH                                                                                                                                                       |                                                                                                                            |  |  |  |  |  |  |

|                 |              | P1 | ×FHNote 2                                                                                                                                                 |                                                                                                                            |  |  |  |  |  |  |

| Control re      | gister       | P3 | 03H                                                                                                                                                       |                                                                                                                            |  |  |  |  |  |  |

|                 | Ī            | P4 | 26H                                                                                                                                                       |                                                                                                                            |  |  |  |  |  |  |

Notes 1. The following resets are available.

- Reset when executing the HALT instruction (when the operand value is illegal or does not satisfy the precondition)

- Reset when executing the RLZ instruction (when A = 0)

- Reset by stack pointer's overflow or underflow

- 2. Refers to the value by the KI pin status.

In order to prevent malfunction, be sure to input a low level to more than one of pins  $K_{10}$  to  $K_{13}$  when reset is released (when  $\overrightarrow{\text{RESET}}$  pin changes from low level to high level, or POC is released due to supply voltage startup).

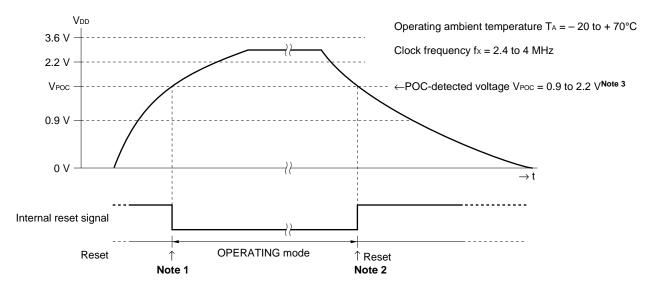

# 7. POC CIRCUIT (MASK OPTION)

The POC circuit monitors the power supply voltage and applies an internal reset in the microcontroller at the time of battery replacement. If the applied circuit satisfies the following conditions, the POC circuit can be incorporated by the mask option.

- High reliability is not required.

- Clock frequency fx =2.4 to 4 MHz

- Operating ambient temperature  $~T_{A}$  = –20 to +70  $^{\circ}C$

# Cautions 1. The one-time PROM product ( $\mu$ PD6P4B) originally contains the POC circuit.

- There are cases in which the POC circuit cannot detect a low power supply voltage of less than 1 ms. Therefore, if the power supply voltage has become low for a period of less than 1 ms, the POC circuit may malfunction because it does not generate an internal reset signal.

- 3. Clock oscillation is stopped by the resonator due to low power supply voltage before the POC circuit generates the internal reset signal. In this case, malfunction may result, for example when the power supply voltage is recovered after the oscillation is stopped. This type of phenomenon takes place because the POC circuit does not generate an internal reset signal (because the power supply voltage recovers before the low power supply voltage is detected) even though the clock has stopped. If, by any chance, a malfunction has taken place, remove the battery for a short time and put it back. In most cases, normal operation will be resumed.

- 4. If the applied circuit does not satisfy the conditions above, design the applied circuit in such a manner that the reset takes effect without failure within the power supply voltage range by means of an external reset circuit.

- 5. In order to prevent malfunction, be sure to input a low level to more than one of pins K<sub>10</sub> to K<sub>13</sub> when reset is released (when RESET pin changes from low level to high level, or POC is released due to supply voltage startup).

- **Remarks 1.** It is recommended that the POC circuit be incorporated when applied circuits are infrared remotecontrol transmitters for household appliances.

- 2. Even when a POC circuit is incorporated, the externally entered RESET input is valid with the OR condition; therefore, the POC circuit and the RESET input can be used at the same time. However, if the POC circuit detects a low power supply voltage, the RESET pin will be forced to low level; therefore, use an N-ch open drain output or NPN open collector output for the external reset circuit.

#### 7.1 Functions of POC Circuit

The POC circuit has the following functions:

- Generates an internal reset signal when  $V_{DD} \leq V_{POC}$ .

- Cancels an internal reset signal when VDD > VPOC.

Here, VDD: power supply voltage, VPOC: POC-detected voltage.

- **Notes 1.** In reality, there is the oscillation stabilization wait time until the circuit is switched to OPERATING mode. The oscillation stabilization wait time is about 252/fx to 700/fx (when about 70 to 190  $\mu$ s; fx = 3.64 MHz).

- For the POC circuit to generate an internal reset signal when the power supply voltage has fallen, it is necessary for the power supply voltage to be kept less than the VPOC for the period of 1 ms or more. Therefore, in reality, there is the time lag of up to 1 ms until the reset takes effect.

- 3. The POC-detected voltage (VPOC) varies between 0.9 to 2.2 V; thus, the resetting may be canceled at a power supply voltage smaller than the assured range (VDD = 1.8 to 3.6 V). However, as long as the conditions for operating the POC circuit are met, the actual lowest operating power supply voltage becomes lower than the POC-detected voltage. Therefore, there is no malfunction occurring due to the shortage of power supply voltage. However, malfunction for such reasons as the clock not oscillating due to low power supply voltage may occur (refer to Cautions 3. in 7. POC CIRCUIT).

#### 7.2 Oscillation Check at Low Supply Voltage

A reliable resetting operation can be expected of the POC circuit if it satisfies the condition that the clock can oscillate even at low power supply voltage (the oscillation start voltage of the resonator being even lower than the POC-detected voltage). Whether this condition is being met or not can be checked by measuring the oscillation status on a product which actually contains a POC circuit, as follows.

<1>Connect a storage oscilloscope to the Xout pin so that the oscillation status can be measured. <2> Connect a power supply whose output voltage can be varied and then gradually raise the power supply voltage VDD from 0 V (making sure to avoid VDD > 3.6V).

At first (during VDD < 0.9 V), the XOUT pin is 0 V regardless of the VDD. However, at the point that VDD reaches the POC-detected voltage (voltage somewhere between VPOC = 0.9 to 2.2 V), the voltage of the XOUT pin jumps to about 0.5 VDD. Maintain this power supply voltage for a while to measure the waveform of the XOUT pin. If, by any chance, the oscillation start voltage of the resonator is lower than the POC-detected voltage, the growing oscillation of the XOUT pin can be confirmed within several ms after the VDD has reached the VPOC.

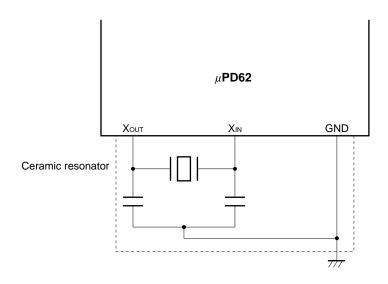

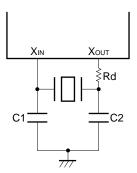

#### 8. SYSTEM CLOCK OSCILLATION CIRCUIT

The system clock oscillation circuit consists of oscillation circuits for ceramic resonators (fx = 2.4 to 8 MHz).

Figure 8-1. System Clock

The system clock oscillator stops its oscillation when reset or in STOP mode.

- Caution When using the system clock oscillator, wire area indicated by the dotted-line in the diagram as follows to reduce the effects of the wiring capacitance, etc.

- Make the wiring as short as possible.

- Do not allow the wiring to intersect other signal lines. Do not wire close to lines through which large fluctuating currents flow.

- Make sure that the point where the oscillation circuit capacitor is installed is always at the same electric potential as the ground. Never earth with a ground pattern through which large currents flow.

- Do not extract signals from the oscillator.

#### 9. INSTRUCTION SET

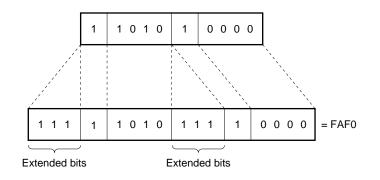

#### 9.1 Machine Language Output by Assembler

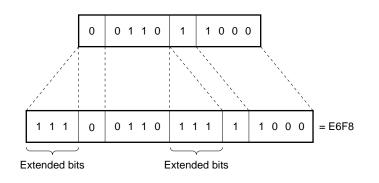

The bit length of the machine language of this product is 10 bits per word. However, the machine language that is output by the assembler is extended to 16 bits per word. As shown in the example below, the expansion is made by inserting 3-bit extended bits (111) in two locations.

#### Figure 9-1. Example of Assembler Output (10 bits extended to 16 bits)

<1> In the case of "ANL A, @R0H"

<2>In the case of "OUT P0, #data8"

# 9.2 Circuit Symbol Description

| А      | : Accumulator                                     |

|--------|---------------------------------------------------|

| ASR    | : Address Stack Register                          |

| addr   | : Program memory address                          |

| CY     | : Carry flag                                      |

| data4  | : 4-bit immediate data                            |

| data8  | : 8-bit immediate data                            |

| data10 | : 10-bit immediate data                           |

| F      | : Status flag                                     |

| PC     | : Program Counter                                 |

| Pn     | : Port register pair (n = 0, 1, 3, 4)             |

| P0n    | : Port register (low-order 4 bits)                |

| P1n    | : Port register (high-order 4 bits)               |

| ROMn   | : Bit n of the program memory's (n = 0-9)         |

| Rn     | : Register pair                                   |

| R0n    | : Data memory (General-purpose register; n = 0-F) |

| R1n    | : Data memory (General-purpose register; n = 0-F) |

| SP     | : Stack Pointer                                   |

| Т      | : Timer register                                  |

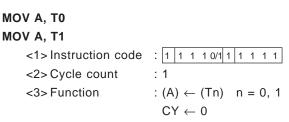

| Т0     | : Timer register (low-order 4 bits)               |

| T1     | : Timer register (high-order 4 bits)              |

| (×)    | : Content addressed with $\times$                 |

# 9.3 Mnemonic to/from Machine Language (Assembler Output) Contrast Table

#### Accumulator Operation Instructions

| Mnomonio | Onerend   | Ins      | struction Co | de       | Operation                                             | Instruction | Instruction |

|----------|-----------|----------|--------------|----------|-------------------------------------------------------|-------------|-------------|

| Mnemonic | Operand   | 1st Word | 2nd Word     | 3rd Word | Operation                                             | Length      | Cycle       |

| ANL      | A, R0n    | FBEn     |              |          | $(A) \leftarrow (A) \land (Rmn)  m = 0, 1  n = 0-F$   | 1           | 1           |

|          | A, R1n    | FAEn     |              |          | $CY \leftarrow A_3 \bullet Rmn_3$                     |             |             |

|          | A, @R0H   | FAF0     |              |          | (A) ← (A) ∧ ((P13), (R0)) <sub>7-4</sub>              |             |             |

|          |           |          |              |          | $CY \leftarrow A_3 \bullet ROM_7$                     |             |             |

|          | A, @R0L   | FBF0     |              |          | (A) ← (A) ^ ((P13), (R0)) <sub>3-0</sub>              |             |             |

|          |           |          |              |          | $CY \leftarrow A_3 \bullet ROM_3$                     |             |             |