DATA SHEET

# **MOS INTEGRATED CIRCUIT** μ**PD77110, 77111, 77112**

### **16-BIT FIXED-POINT DIGITAL SIGNAL PROCESSORS**

#### DESCRIPTION

The  $\mu$ PD77110, 77111, and 77112 are 16-bit fixed-point digital signal processors (DSPs). Compared with the µPD77016 family, these DSPs have improved power consumption and are ideal for batterypowered mobile terminals such as PDAs and cellular phones. Both mask ROM and RAM models are available. For details of the functions of these DSPs, refer to the following User's Manuals: µPD77111 Family User's Manual : To be available soon µPD7701X Family User's Manual - Instructions: U13116E **FEATURES**  Instruction cycle (operating clock) μPD77110: 15.3 ns MIN (65 MHz MAX) 13.3 ns MIN (75 MHz MAX) (Operating voltage and ambient temperature are limited.) µPD77111: 13.3 ns MIN (75 MHz MAX) µPD77112: 13.3 ns MIN (75 MHz MAX) Memory Internal instruction memory  $\mu$ PD77110: RAM 35.5K words  $\times$  32 bits  $\mu$ PD77111: RAM 1K words  $\times$  32 bits Mask ROM 31.75K words × 32 bits  $\mu$ PD77112: RAM 1K words  $\times$  32 bits Mask ROM 31.75K words × 32 bits · Data memory  $\mu$ PD77110: RAM 24K words  $\times$  16 bits  $\times$  2 banks External memory space 32K words  $\times$  16 bits  $\times$  2 banks  $\mu$ PD77111: RAM 3K words  $\times$  16 bits  $\times$  2 banks Mask ROM 16K words × 16 bits × 2 banks  $\mu$ PD77112: RAM 3K words  $\times$  16 bits  $\times$  2 banks Mask ROM 16K words × 16 bits × 2 banks External memory space 16K words × 16 bits × 2 banks

> The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version. Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

#### **ORDERING INFORMATION**

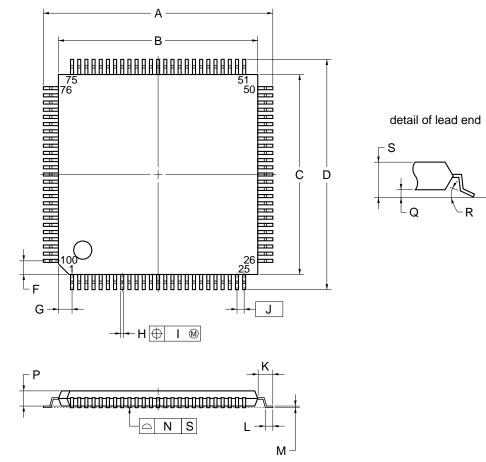

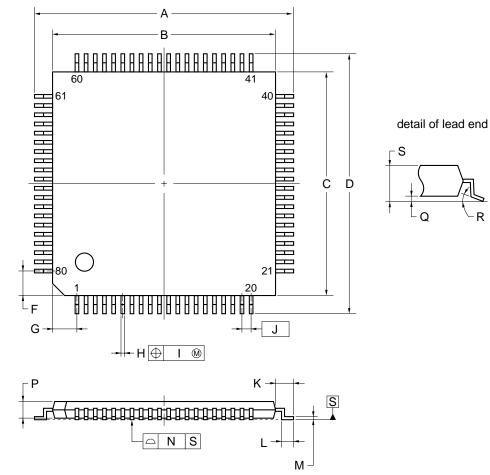

| Part Number             | Package                                              |

|-------------------------|------------------------------------------------------|

| μPD77110GC-9EU          | 100-pin plastic TQFP (fine pitch) (14 $	imes$ 14 mm) |

| $\mu$ PD77111GK-xxx-9EU | 80-pin plastic TQFP (fine pitch) (12 $\times$ 12 mm) |

| μPD77111F1-xxx-CN1      | 80-pin plastic fine-pitch BGA (9 $	imes$ 9 mm)       |

| μPD77112GC-xxx-9EU      | 100-pin plastic TQFP (fine pitch) (14 $	imes$ 14 mm) |

Remark xxx indicates ROM code suffix.

Π

Data Sheet U12801EJ4V0DS00

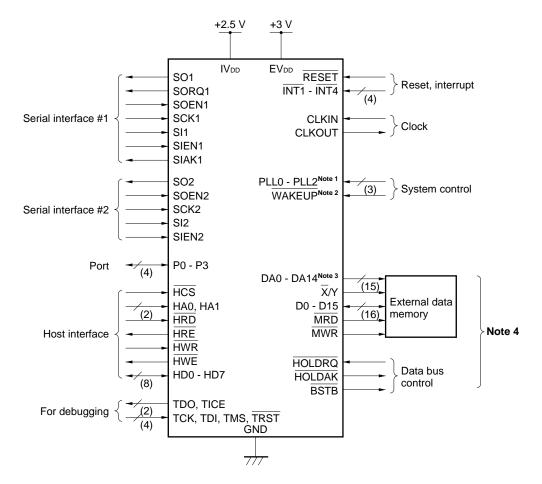

#### **PIN CONFIGURATION**

- **Notes 1.** These pins are provided only on the  $\mu$ PD77110.

- **2.** With the  $\mu$ PD77111 and 77112, the function of this pin can be activated or deactivated by mask option. With the  $\mu$ PD77110, this function is always valid.

- **3.** DA14 is not provided on the  $\mu$ PD77112.

- 4. An external data memory interface is not provided on the  $\mu$ PD77111.

# NEC

#### ★ DSP FUNCTION LIST

|                      | Item                                 | μPD77016                             | μPD77018A                                                        | μPD77019            | μPD77019-013  | μPD77110                             | μPD77111                          | μPD77112          | μPD77113             | μPD77114            |

|----------------------|--------------------------------------|--------------------------------------|------------------------------------------------------------------|---------------------|---------------|--------------------------------------|-----------------------------------|-------------------|----------------------|---------------------|

| Memory space         | Internal instruction RAM             | 1.5K × 32                            | 256 × 32                                                         | 4K                  | × 32          | 35.5K × 32                           | 1K × 32                           |                   | 3.5K × 32            |                     |

| (words $	imes$ bits) | Internal instruction ROM             | None                                 | 24K                                                              | × 32                | No            | one                                  | 31.75                             | K × 32            | 48K × 32             |                     |

|                      | Data RAM<br>(X/Y memory)             | $2K \times 16$ each                  |                                                                  | $3K \times 16$ each |               | $24K \times 16$ each                 | $3K \times 16$ each               |                   | $16K \times 16$ each |                     |

|                      | Data ROM<br>(X/Y memory)             | None                                 | 12K × 1                                                          | 16 each             | No            | None 16K × 16 each                   |                                   |                   | $32K \times 16$ each |                     |

|                      | External instruction memory          | 48K × 32                             |                                                                  |                     |               | None                                 |                                   |                   |                      |                     |

|                      | External data memory<br>(X/Y memory) | 48K × 16 each                        | $16K \times 16$ each                                             |                     |               | $32K \times 16$ each                 | None                              | 16K × 16 each     | None                 | $8K \times 16$ each |

| Instruction cyc      | le (at maximum speed)                | 30 ns (33 MHz)                       | 16.6 ns (60 MHz) 15.3 ns (                                       |                     |               | 15.3 ns (65 MHz)                     | 13.3 ns (75 MHz)                  |                   |                      |                     |

| Multiple             |                                      | -                                    | ×1, 2, 3, 4, 8                                                   | (mask option)       | Fixed to ×4   | Integer of ×1 to 8<br>(external pin) |                                   | Integer of ×1 to  | 16 (mask option)     | )                   |

| Serial interfact     | e (two channels)                     | Channels 1 and 2 have same function. |                                                                  | ame function as     | μΡD77016. Cha | annel 2 does not l                   | have SORQ2 an                     | d SIAK2 pins (for | connection of co     | dec).               |

| Supply voltage 5 V   |                                      |                                      | 3 V                                                              |                     |               |                                      | DSP core: 2.5 V<br>I/O pins : 3 V |                   |                      |                     |

| Package 160-pin QFP  |                                      |                                      | 100-pin TQFP     100-pin TQFP       116-pin BGA     100-pin TQFP |                     |               |                                      | 80-pin TQFP<br>80-pin FBGA        | 100-pin TQFP      | 80-pin FBGA          | 100-pin TQFP        |

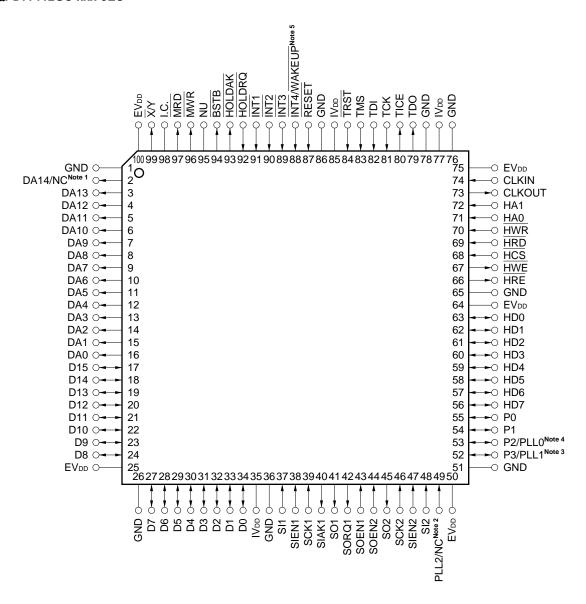

#### PIN CONFIGURATION

100-pin plastic TQFP (fine-pitch) (14  $\times$  14 mm) (Top View)  $\mu$ PD77110GC-9EU  $\mu$ PD77112GC-xxx-9EU

- **Notes 1.** DA14 with  $\mu$ PD77110, NC with  $\mu$ PD77112

- **2.** PLL2 with μPD77110, NC with μPD77112

- **3.** P3 only for μPD77112

- **4.** P2 only for  $\mu$ PD77112

- **5.** With the  $\mu$ PD77112, the function of the WAKEUP pin can be activated or deactivated by a mask option.

\_\_\_

| Pin No. | Pin Name    |

|---------|----------|---------|----------|---------|----------|---------|-------------|

| 1       | GND      | 26      | GND      | 51      | GND      | 76      | GND         |

| 2       | DA14/NC  | 27      | D7       | 52      | P3/PLL1  | 77      | IVdd        |

| 3       | DA13     | 28      | D6       | 53      | P2/PLL0  | 78      | GND         |

| 4       | DA12     | 29      | D5       | 54      | P1       | 79      | TDO         |

| 5       | DA11     | 30      | D4       | 55      | P0       | 80      | TICE        |

| 6       | DA10     | 31      | D3       | 56      | HD7      | 81      | тск         |

| 7       | DA9      | 32      | D2       | 57      | HD6      | 82      | TD1         |

| 8       | DA8      | 33      | D1       | 58      | HD5      | 83      | TMS         |

| 9       | DA7      | 34      | D0       | 59      | HD4      | 84      | TRST        |

| 10      | DA6      | 35      | IVdd     | 60      | HD3      | 85      | IVdd        |

| 11      | DA5      | 36      | GND      | 61      | HD2      | 86      | GND         |

| 12      | DA4      | 37      | SI1      | 62      | HD1      | 87      | RESET       |

| 13      | DA3      | 38      | SIEN1    | 63      | HD0      | 88      | INT4/WAKEUP |

| 14      | DA2      | 39      | SCK1     | 64      | EVDD     | 89      | ĪNT3        |

| 15      | DA1      | 40      | SIAK1    | 65      | GND      | 90      | ĪNT2        |

| 16      | DA0      | 41      | SO1      | 66      | HRE      | 91      | ĪNT1        |

| 17      | D15      | 42      | SORQ1    | 67      | HWE      | 92      | HOLDRQ      |

| 18      | D14      | 43      | SOEN1    | 68      | HCS      | 93      | HOLDAK      |

| 19      | D13      | 44      | SOEN2    | 69      | HRD      | 94      | BSTB        |

| 20      | D12      | 45      | SO2      | 70      | HWR      | 95      | NU          |

| 21      | D11      | 46      | SCK2     | 71      | HAO      | 96      | MWR         |

| 22      | D10      | 47      | SIEN2    | 72      | HA1      | 97      | MRD         |

| 23      | D9       | 48      | SI2      | 73      | CLKOUT   | 98      | I.C.        |

| 24      | D8       | 49      | PLL2/NC  | 74      | CLKIN    | 99      | ⊼/Υ         |

| 25      | EVDD     | 50      | EVDD     | 75      | EVDD     | 100     | EVDD        |

\_\_\_\_

NEC

⊖ IVbb ⊖ CLKIN ⊖ EV⊳⊳ 0 INT2 0 INT3 GND GND ⊖ IVbb ⊖ TRST ⊖ ⊖ TCK - TDO NU NT1 Q Q Q Q 10 79 77 77 61 60 -O EVDD NU 🔿 2 59 3 NU O-58 HA1 0 NU O-4 HA0 57 -NU O-5 56 HWR -0 NU O 6 55 HRD  $\overline{}$ HCS NU O 7 54 -0 NU O-8 HWE 53 -0 NU O-9 52 HRE -0 EVDD O-10 51 GND 0 GND O-11 50 -O EVDD NU O-12 49 ► HD0 NU O-13 HD1 48 -0  $NU \bigcirc$ 14 HD2 47 -0 15 NU O-46 HD3 -0 NU O-16 45 HD4 0 NU O-17 -O HD5 44 NU O-18 43 -O HD6 19 NU O-42 ►O HD7 41 86 40 40 40 EVDD O-20 -O GND 35 36 SCK1 O-S01 0-SORQ1 0-S02 0-SCK2 O-SIEN2 O-SI1 \_ SOEN2 O-IV pp ()-SI2 O GND () EV<sub>DD</sub> () SIEN1

80-pin plastic TQFP (fine-pitch) (12  $\times$  12 mm) (Top view)  $\mu$ PD77111GK-xxx-9EU

| Pin No. | Pin Name                    |

|---------|----------|---------|----------|---------|----------|---------|-----------------------------|

| 1       | GND      | 21      | GND      | 41      | GND      | 61      | GND                         |

| 2       | NU       | 22      | SI1      | 42      | HD7      | 62      | CLKIN                       |

| 3       | NU       | 23      | SIEN1    | 43      | HD6      | 63      | IVdd                        |

| 4       | NU       | 24      | SCK1     | 44      | HD5      | 64      | GND                         |

| 5       | NU       | 25      | SIAK1    | 45      | HD4      | 65      | TDO                         |

| 6       | NU       | 26      | SO1      | 46      | HD3      | 66      | TICE                        |

| 7       | NU       | 27      | SORQ1    | 47      | HD2      | 67      | тск                         |

| 8       | NU       | 28      | SOEN1    | 48      | HD1      | 68      | TDI                         |

| 9       | NU       | 29      | SOEN2    | 49      | HD0      | 69      | TMS                         |

| 10      | EVDD     | 30      | SO2      | 50      | EVDD     | 70      | TRST                        |

| 11      | GND      | 31      | IVdd     | 51      | GND      | 71      | IVdd                        |

| 12      | NU       | 32      | GND      | 52      | HRE      | 72      | GND                         |

| 13      | NU       | 33      | SCK2     | 53      | HWE      | 73      | RESET                       |

| 14      | NU       | 34      | SIEN2    | 54      | HCS      | 74      | INT4/WAKEUP <sup>Note</sup> |

| 15      | NU       | 35      | SI2      | 55      | HRD      | 75      | ĪNT3                        |

| 16      | NU       | 36      | P3       | 56      | HWR      | 76      | ĪNT2                        |

| 17      | NU       | 37      | P2       | 57      | HA0      | 77      | ĪNT1                        |

| 18      | NU       | 38      | P1       | 58      | HA1      | 78      | NU                          |

| 19      | NU       | 39      | P0       | 59      | CLKOUT   | 79      | NU                          |

| 20      | EVdd     | 40      | EVDD     | 60      | EVDD     | 80      | EVdd                        |

**Note** The function of the  $\overline{WAKEUP}$  pin can be activated or deactivated by a mask option.

\_\_\_\_

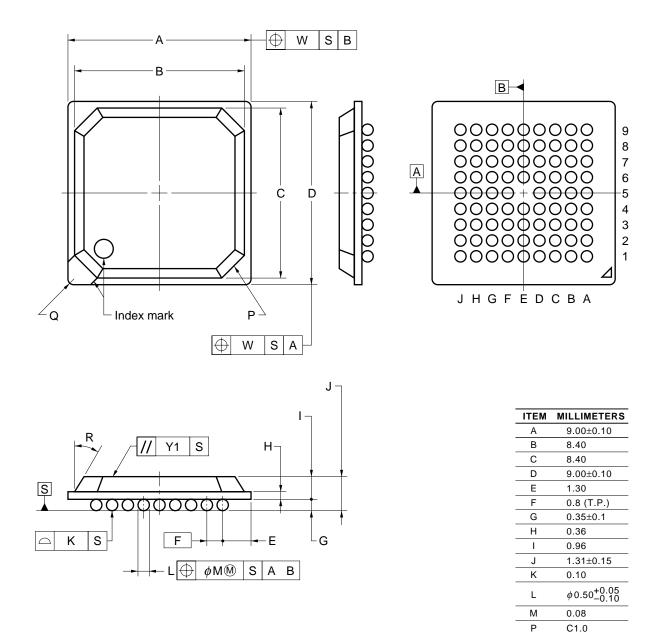

#### 80-pin plastic fine-pitch BGA (9 $\times$ 9 mm) $\mu$ PD77111F1-xxx-CN1

| (Bottom View) |   |   |   |   |   |   |   |   |     |  |

|---------------|---|---|---|---|---|---|---|---|-----|--|

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 9   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 8   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 7   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 6   |  |

| 0             | 0 | 0 | 0 |   | 0 | 0 | 0 | 0 | 5   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 4   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 3   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 2   |  |

| 0             | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | ] 1 |  |

| J             | Н | G | F | Е | D | С | В | A |     |  |

| Pin No. | Pin Name                    | Pin No. | Pin Name | Pin No. | Pin Name | Pin No. | Pin Name |

|---------|-----------------------------|---------|----------|---------|----------|---------|----------|

| A1      | EVDD                        | C3      | NU       | E6      | HRE      | G8      | HD4      |

| A2      | NU                          | C4      | RESET    | E7      | HD0      | G9      | HD5      |

| A3      | ĪNT2                        | C5      | TRST     | E8      | GND      | H1      | NU       |

| A4      | INT4/WAKEUP <sup>Note</sup> | C6      | TICE     | E9      | EVDD     | H2      | NU       |

| A5      | IVdd                        | C7      | CLKIN    | F1      | NU       | НЗ      | SIEN1    |

| A6      | тск                         | C8      | HA0      | F2      | NU       | H4      | SOEN1    |

| A7      | IVdd                        | C9      | HWR      | F3      | NU       | H5      | GND      |

| A8      | GND                         | D1      | NU       | F4      | SIAK1    | H6      | SI2      |

| A9      | EVDD                        | D2      | NU       | F5      | SOEN2    | H7      | P1       |

| B1      | NU                          | D3      | NU       | F6      | P2       | H8      | GND      |

| B2      | GND                         | D4      | ĪNT1     | F7      | HD1      | H9      | HD7      |

| B3      | NU                          | D5      | TMS      | F8      | HD3      | J1      | EVDD     |

| B4      | ĪNT3                        | D6      | TDO      | F9      | HD2      | J2      | GND      |

| B5      | GND                         | D7      | HCS      | G1      | NU       | J3      | SCK1     |

| B6      | TDI                         | D8      | HRD      | G2      | NU       | J4      | SORQ1    |

| B7      | GND                         | D9      | HWE      | G3      | SI1      | J5      | IVdd     |

| B8      | CLKOUT                      | E1      | EVDD     | G4      | SO1      | J6      | SCK2     |

| B9      | HA1                         | E2      | GND      | G5      | SO2      | J7      | P3       |

| C1      | NU                          | E3      | NU       | G6      | SIEN2    | J8      | P0       |

| C2      | NU                          | E4      | NU       | G7      | HD6      | J9      | EVDD     |

**Note** The function of the  $\overline{WAKEUP}$  pin can be activated or deactivated by a mask option.

#### PIN NAME

| BSTB : Bus Strobe                                           |       |

|-------------------------------------------------------------|-------|

| CLKIN : Clock Input                                         |       |

| CLKOUT : Clock Output                                       |       |

| D0 - D15 : 16-bit Data Bus                                  |       |

| DA0 - DA14 : External Data Memory Address                   | e Rue |

| EV <sub>DD</sub> : Power Supply for I/O Pins                | 5 Du3 |

| GND : Ground                                                |       |

| HA0, HA1 : Host Data Access                                 |       |

| HCS     : Host Data Access       HCS     : Host Chip Select |       |

| HD0 - HD7 : Host Data Bus                                   |       |

| HOLDAK : Hold Acknowledge                                   |       |

| HOLDRQ : Hold Request                                       |       |

| HRD : Host Read                                             |       |

|                                                             |       |

| HRE : Host Read Enable<br>HWE : Host Write Enable           |       |

|                                                             |       |

| HWR : Host Write                                            |       |

| I.C. : Internally Connected                                 |       |

| INT1 - INT4 : Interrupt                                     |       |

| IVDD : Power Supply for DSP Core                            |       |

| MRD : Memory Read Output                                    |       |

| MWR   : Memory Write Output                                 |       |

| NC : Non-Connection                                         |       |

| NU : Not Used                                               |       |

| P0 - P3 : Port                                              |       |

| PLL0 - PLL2 : PLL Multiple Rate Set                         |       |

| RESET : Reset                                               |       |

| SCK1, SCK2 : Serial Clock Input                             |       |

| SI1, SI2 : Serial Data Input                                |       |

| SIAK1 : Serial Input Acknowledge                            |       |

| SIEN1, SIEN2 : Serial Input Enable                          |       |

| SO1, SO2 : Serial Data Output                               |       |

| SOEN1, SOEN2: Serial Output Enable                          |       |

| SORQ1 : Serial Output Request                               |       |

| TCK : Test Clock Input                                      |       |

| TDI : Test Data Input                                       |       |

| TDO : Test Data Output                                      |       |

| TICE : Test In-Circuit Emulator                             |       |

| TMS : Test Mode Select                                      |       |

| TRST : Test Reset                                           |       |

| WAKEUP : Wakeup from STOP Mode                              |       |

| X/Y : X/Y Memory Select                                     |       |

#### CONTENTS

| 1.  | PIN FUNCTION                                    | 13 |

|-----|-------------------------------------------------|----|

|     | 1.1 Pin Function Description                    | 13 |

|     | 1.2 Connection of Unused Pins                   | 18 |

|     |                                                 |    |

| 2.  | FUNCTION OUTLINE                                | 20 |

|     | 2.1 Program Control Unit                        | 20 |

|     | •                                               | 21 |

|     | 2.3 Data Memory Unit                            | 22 |

|     | 2.4 Peripheral Units                            |    |

|     |                                                 |    |

| 3.  | CLOCK GENERATOR                                 | 23 |

| ٨   | RESET FUNCTION                                  | 22 |

| 4.  | 4.1 Hardware Reset                              |    |

|     | 4.1 Initializing PLL                            |    |

|     |                                                 | 24 |

| 5   | FUNCTIONS OF BOOT-UP ROM                        | 24 |

| 5.  | 5.1 Boot at Reset                               | 24 |

|     | 5.2 Reboot                                      |    |

|     | 5.3 Signature Operation                         |    |

|     |                                                 | 20 |

| 6   | STANDBY MODES                                   | 26 |

| 0.  | 6.1 HALT Mode                                   | -  |

|     | 6.2 STOP Mode                                   |    |

|     |                                                 | 21 |

| 7   | MEMORY MAP                                      | 27 |

| ••  | 7.1 Instruction Memory                          |    |

|     | 7.2 Data Memory                                 |    |

|     |                                                 | 20 |

| 8.  | MASK OPTION                                     | 30 |

| -   | 8.1 Clock Control Options                       |    |

|     | 8.2 WAKEUP Function                             |    |

|     | 8.3 Mask Option Equivalent Function of μPD77110 |    |

|     |                                                 | •  |

| 9.  | INSTRUCTIONS                                    | 33 |

|     | 9.1 Outline of Instructions                     |    |

|     | 9.2 Instruction Set and Operation               |    |

|     |                                                 |    |

| 10  | ELECTRICAL SPECIFICATIONS                       | 40 |

|     |                                                 |    |

| 11. | PACKAGE                                         | 72 |

|     |                                                 |    |

| 12  | RECOMMENDED SOLDERING CONDITIONS                | 75 |

#### 1. PIN FUNCTION

Because the pin numbers differ depending on the package, refer to the diagram of the package to be used.

#### 1.1 Pin Function Description

#### • Power supply

|          |                                     | Pin No.                                    |                                                | I/O |                            |            |

|----------|-------------------------------------|--------------------------------------------|------------------------------------------------|-----|----------------------------|------------|

| Pin Name | 100-pin<br>TQFP                     | 80-pin<br>TQFP                             | 80-pin<br>FBGA                                 |     | Function                   | Shared by: |

| IVdd     | 35, 77, 85                          | 31, 63, 71                                 | A5, A7, J5                                     | -   | Power to DSP core (+2.5 V) | -          |

| EVdd     | 25, 50,<br>64, 75,<br>100           | 10, 20,<br>40, 50,<br>60, 80               | A1, A9,<br>E1, E9,<br>J1, J9                   | -   | Power to I/O pins (+3 V)   | _          |

| GND      | 1, 26, 36,<br>51, 65,<br>76, 78, 86 | 1, 11, 21,<br>32, 41,<br>51, 61,<br>64, 72 | A8, B2,<br>B5, B7,<br>E2, E8,<br>H5, H8,<br>J2 | _   | Ground                     | _          |

#### System control

|          |                 | Pin No.        |                |        |                                                                                                                                                                                                                                                         |            |

|----------|-----------------|----------------|----------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Pin Name | 100-pin<br>TQFP | 80-pin<br>TQFP | 80-pin<br>FBGA | I/O    | Function                                                                                                                                                                                                                                                | Shared by: |

| CLKIN    | 74              | 62             | C7             | Input  | System clock input                                                                                                                                                                                                                                      | -          |

| CLKOUT   | 73              | 59             | B8             | Output | Internal system clock output                                                                                                                                                                                                                            | -          |

| RESET    | 87              | 73             | C4             | Input  | Internal system reset signal input                                                                                                                                                                                                                      |            |

| PLL0     | 53              | -              | _              | Input  | PLL multiple setting input ( $\mu$ PD77110 only)                                                                                                                                                                                                        | P2         |

| PLL1     | 52              | -              | -              | Input  | Determines the PLL multiple at reset as     followings:                                                                                                                                                                                                 | P3         |

| PLL2     | 49              | -              | _              | Input  | PLL2: PLL1: PLL0:<br>000 : Selects PLL multiple of ×1.<br>001 : Selects PLL multiple of ×2.<br>010 : Selects PLL multiple of ×3.<br>:<br>111 : Selects PLL multiple of ×8.<br>• These pins have no function on the<br>$\mu$ PD77111 and 77112.          | _          |

| WAKEUP   | 88              | 74             | A4             | Input  | <ul> <li>Stop mode release signal input.</li> <li>When this pin is asserted active, the stop mode is released. The function of this pin can be activated or deactivated by a mask option.</li> <li>This pin is always valid on the μPD77110.</li> </ul> | INT4       |

#### • Interrupt

|             |                 | Pin No.        |                |       |                                                                                      |            |

|-------------|-----------------|----------------|----------------|-------|--------------------------------------------------------------------------------------|------------|

| Pin Name    | 100-pin<br>TQFP | 80-pin<br>TQFP | 80-pin<br>FBGA | I/O   | Function                                                                             | Shared by: |

| INT1 - INT3 | 91 - 89         | 77 - 75        | D4, A3,<br>B4  | Input | External maskable interrupt input. <ul> <li>Detected at the falling edge.</li> </ul> | -          |

| INT4        | 88              | 74             | A4             | Input |                                                                                      | WAKEUP     |

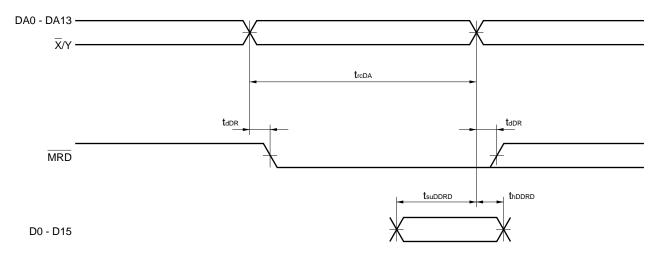

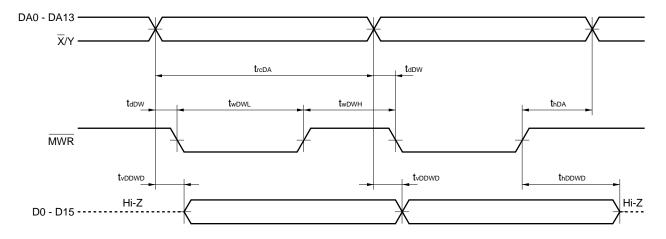

#### • External data memory interface

|            |                     | Pin No.        |                |                |                                                                                                                                                                                                                                                                                                                                                                           |            |

|------------|---------------------|----------------|----------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Pin Name   | 100-pin<br>TQFP     | 80-pin<br>TQFP | 80-pin<br>FBGA | I/O            | Function                                                                                                                                                                                                                                                                                                                                                                  | Shared by: |

| ⊼/Y        | 99                  | _              | -              | Output<br>(3S) | Memory select signal output.<br>0: Uses X memory.<br>1: Uses Y memory.                                                                                                                                                                                                                                                                                                    | _          |

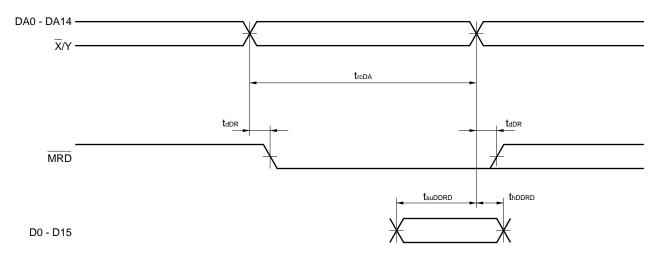

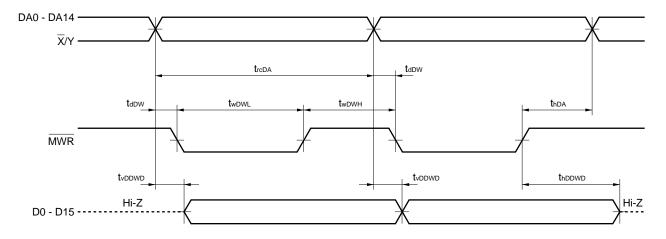

| DA0 - DA14 | 16 - 2              | _              | _              | Output<br>(3S) | <ul> <li>Address bus of external data memory.</li> <li>Accesses the external memory.</li> <li>Continuously outputs the external memory address accessed last when the external memory is not being accessed. Kept low (0x000) if the external memory is never accessed after reset.</li> <li>DA14 is NC (no connection) and does not function on the μPD77112.</li> </ul> | _          |

| D0 - D15   | 34 - 27,<br>24 - 17 | -              | _              | I/O<br>(3S)    | <ul><li>16-bit data bus.</li><li>Accesses the external memory.</li></ul>                                                                                                                                                                                                                                                                                                  | -          |

| MRD        | 97                  | -              | _              | Output<br>(3S) | Read output <ul> <li>External memory read</li> </ul>                                                                                                                                                                                                                                                                                                                      | -          |

| MWR        | 96                  | -              | _              | Output<br>(3S) | Write output <ul> <li>External memory write</li> </ul>                                                                                                                                                                                                                                                                                                                    | -          |

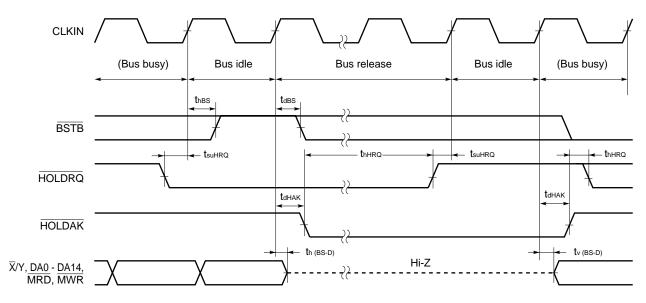

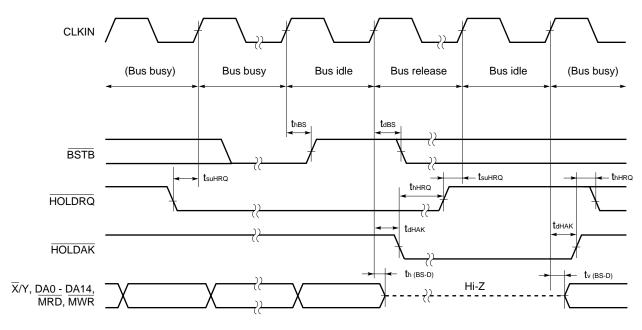

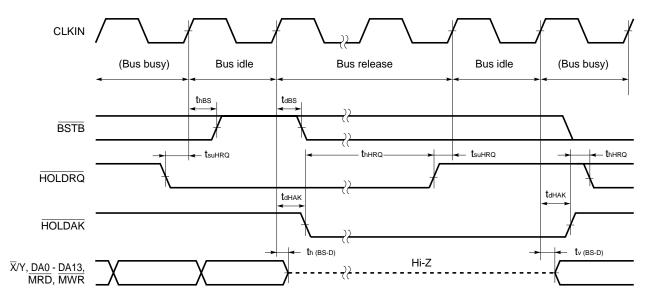

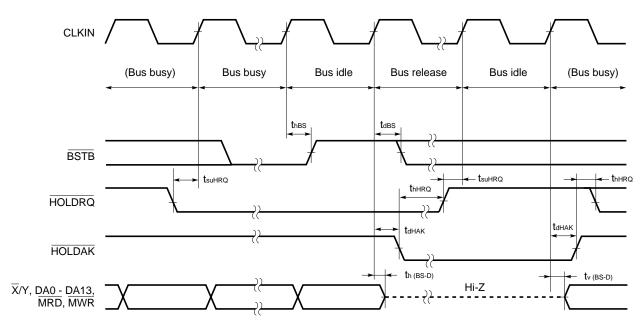

| HOLDRQ     | 92                  | _              | _              | Input          | <ul> <li>Hold request signal</li> <li>Input a low level to this pin when the external device uses the external data memory bus of the μPD77110 and 77112.</li> </ul>                                                                                                                                                                                                      | -          |

| BSTB       | 94                  | -              | -              | Output         | <ul> <li>Bus strobe signal</li> <li>This pin goes low when the μPD77110 and 77112 use the external data memory bus.</li> </ul>                                                                                                                                                                                                                                            | -          |

| HOLDAK     | 93                  | _              | _              | Output         | <ul> <li>Hold acknowledge signal</li> <li>This pin goes low when the external device is enabled to use the external data memory bus of the μPD77110 and 77112.</li> </ul>                                                                                                                                                                                                 | _          |

RemarkPins marked "3S" under the heading "I/O" go into a high-impedance state in the following conditions: $\overline{X}/Y$ , DA0-DA14,  $\overline{MRD}$ ,  $\overline{MWR}$ : When the bus is released ( $\overline{HOLDAK}$  = low level)D0-D15:When the external data memory is not being accessed and when the bus is released $(\overline{HOLDAK}$  = low level)

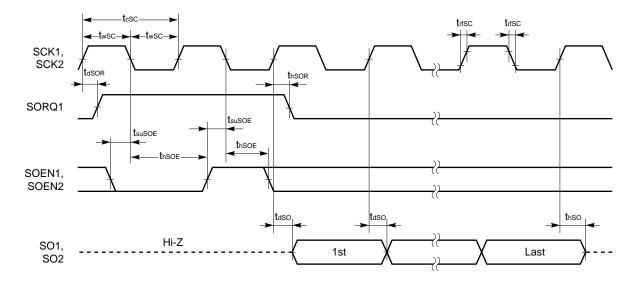

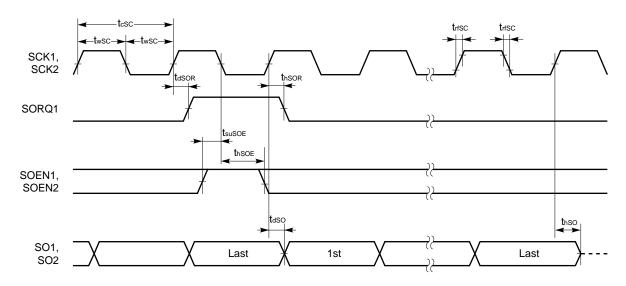

#### • Serial interface

|          |                 | Pin No.        |                |                |                            |            |

|----------|-----------------|----------------|----------------|----------------|----------------------------|------------|

| Pin Name | 100-pin<br>TQFP | 80-pin<br>TQFP | 80-pin<br>FBGA | I/O            | Function                   | Shared by: |

| SCK1     | 39              | 24             | J3             | Input          | Serial 1 clock input       | -          |

| SORQ1    | 42              | 27             | J4             | Output         | Serial output 1 request    | -          |

| SOEN1    | 43              | 28             | H4             | Input          | Serial output 1 enable     | -          |

| SO1      | 41              | 26             | G4             | Output<br>(3S) | Serial data output 1       | _          |

| SIEN1    | 38              | 23             | НЗ             | Input          | Serial input 1 enable      | -          |

| SI1      | 37              | 22             | G3             | Input          | Serial data input 1        | _          |

| SIAK1    | 40              | 25             | F4             | Output         | Serial input 1 acknowledge | -          |

| SCK2     | 46              | 33             | J6             | Input          | Serial 2 clock input       | -          |

| SOEN2    | 44              | 29             | F5             | Input          | Serial output 2 enable     | -          |

| SO2      | 45              | 30             | G5             | Output<br>(3S) | Serial data output 2       | _          |

| SIEN2    | 47              | 34             | G6             | Input          | Serial input 2 enable      | -          |

| SI2      | 48              | 35             | H6             | Input          | Serial data input 2        | -          |

**Remark** The pins marked "3S" under the heading "I/O" go into a high-impedance state on completion of data transfer and input of the hardware reset (RESET) signal.

#### • Host interface

|           |                 | Pin No.        |                                         |             |                                                                                                                                                                                                                                                                                                            |   |

|-----------|-----------------|----------------|-----------------------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Pin Name  | 100-pin<br>TQFP | 80-pin<br>TQFP | 80-pin<br>FBGA                          | I/O         | Function Shar                                                                                                                                                                                                                                                                                              |   |

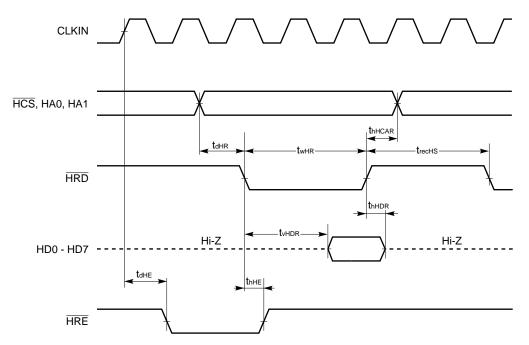

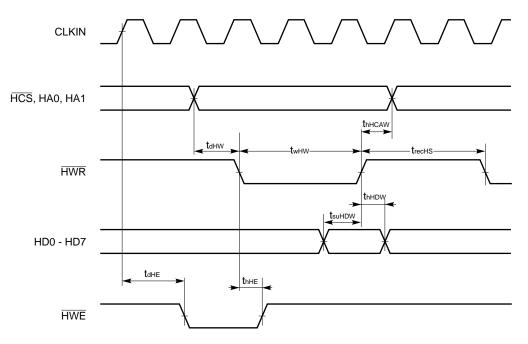

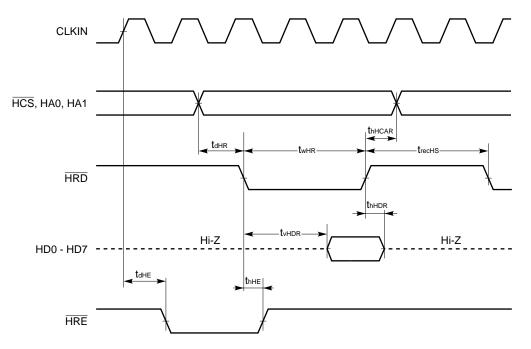

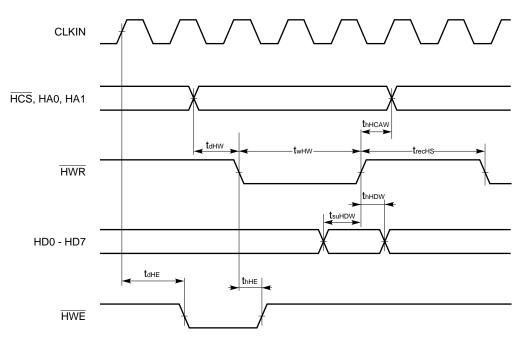

| HA1       | 72              | 58             | В9                                      | Input       | <ul> <li>Input Specifies the register to be accessed by HD7 through HD0.</li> <li>1: Accesses the host interface status register (HST).</li> <li>0: Accesses the host transmit data register (HDT (out)) when read (HRD = 0), and host receive data register (HDT (in)) when written (HWR = 0).</li> </ul> |   |

| HAO       | 71              | 57             | C8                                      | Input       | <ul> <li>Specifies the register to be accessed by HD7<br/>through HD0.</li> <li>1: Accesses bits 15 through 8 of HST, HDT<br/>(in), and HDT (out).</li> <li>0: Accesses bits 7 through 0 of HST, HDT<br/>(in), and HDT (out).</li> </ul>                                                                   | _ |

| HCS       | 68              | 54             | D7                                      | Input       | Chip select input                                                                                                                                                                                                                                                                                          | _ |

| HRD       | 69              | 55             | D8                                      | Input       | Host read input                                                                                                                                                                                                                                                                                            | - |

| HWR       | 70              | 56             | C9                                      | Input       | Host write input                                                                                                                                                                                                                                                                                           | - |

| HRE       | 66              | 52             | E6                                      | Output      | utput Host read enable output                                                                                                                                                                                                                                                                              |   |

| HWE       | 67              | 53             | D9                                      | Output      | Output Host write enable output                                                                                                                                                                                                                                                                            |   |

| HD0 - HD7 | 63 - 56         | 49 - 42        | E7, F7,<br>F9, F8,<br>G8, G9,<br>G7, H9 | I/O<br>(3S) | 8-bit host data bus                                                                                                                                                                                                                                                                                        | _ |

**Remark** The pins marked "3S" under the heading "I/O" go into a high-impedance state when the host interface is not being accessed.

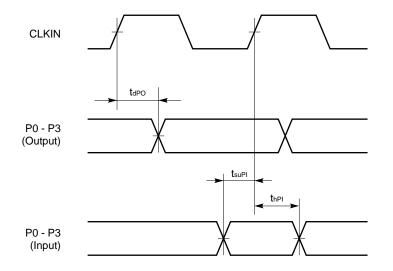

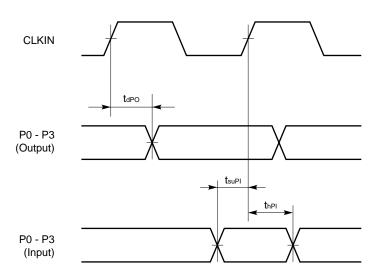

#### • I/O ports

|          | Pin No.         |                |                |     |                          |                      |

|----------|-----------------|----------------|----------------|-----|--------------------------|----------------------|

| Pin Name | 100-pin<br>TQFP | 80-pin<br>TQFP | 80-pin<br>FBGA | I/O | Function                 | Shared by:           |

| P0       | 55              | 39             | J8             | I/O | General-purpose I/O port | _                    |

| P1       | 54              | 38             | H7             | I/O |                          | _                    |

| P2       | 53              | 37             | F6             | I/O |                          | PLL0 <sup>Note</sup> |

| P3       | 52              | 36             | J7             | I/O |                          | PLL1 <sup>Note</sup> |

**Note** Only the  $\mu$ PD77110. The  $\mu$ PD77111 and 77112 have no multiplexed pins.

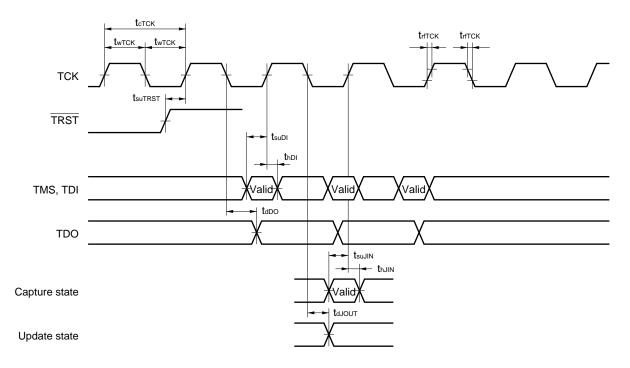

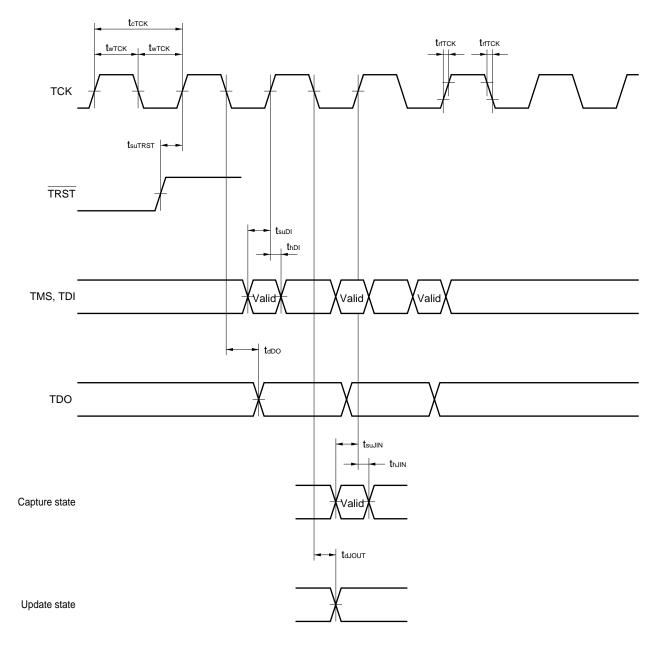

#### • Debugging interface

|          | Pin No.         |                |                |        |               |            |

|----------|-----------------|----------------|----------------|--------|---------------|------------|

| Pin Name | 100-pin<br>TQFP | 80-pin<br>TQFP | 80-pin<br>FBGA | I/O    | Function      | Shared by: |

| TDO      | 79              | 65             | D6             | Output | For debugging | -          |

| TICE     | 80              | 66             | C6             | Output |               | -          |

| тск      | 81              | 67             | A6             | Input  |               | -          |

| TDI      | 82              | 68             | B6             | Input  |               | -          |

| TMS      | 83              | 69             | D5             | Input  |               | -          |

| TRST     | 84              | 70             | C5             | Input  |               | -          |

#### • Others

|          |                 | Pin No.                                                                          |                                                                                                |     |                                                                     |            |

|----------|-----------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------|------------|

| Pin Name | 100-pin<br>TQFP | 80-pin<br>TQFP                                                                   | 80-pin<br>FBGA                                                                                 | I/O | Function                                                            | Shared by: |

| I.C.     | 98              | _                                                                                | _                                                                                              | _   | Internally connected. Leave this pin unconnected.                   | -          |

| NU       | 95              | 2, 3, 4, 5,<br>6, 7, 8, 9,<br>12, 13,<br>14, 15,<br>16, 17,<br>18, 19,<br>78, 79 | A2, B1,<br>B3, C1,<br>C2, C3,<br>D1, D2,<br>D3, E3,<br>E4, F1,<br>F2, F3,<br>G1, G2,<br>H1, H2 | _   | No function pins. Connect these pins to EVDD.                       | _          |

| NC       | 2, 49           | _                                                                                | -                                                                                              | _   | No-connect pins (with $\mu$ PD77112). Leave these pins unconnected. | -          |

Caution If any signal is input to these pins or if an attempt is made to read these pins, the normal operation of the  $\mu$ PD77110, 77111, and 77112 is not guaranteed.

#### 1.2 Connection of Unused Pins

#### 1.2.1 Connection of Function Pins

When mounting, connect unused pins as follows:

| Pin                                                                   | I/O    | Recommended Connection                                                          |  |

|-----------------------------------------------------------------------|--------|---------------------------------------------------------------------------------|--|

| INT1 - INT4                                                           | Input  | Connect to EVDD.                                                                |  |

| ¯Χ/Υ                                                                  | Output | Leave unconnected.                                                              |  |

| DA0 - DA14                                                            | Output |                                                                                 |  |

| D0 - D15 <sup>Note 1</sup>                                            | I/O    | Connect to EVDD via pull-up resistor, or connect to GND via pull-down resistor. |  |

| MRD, MWR                                                              | Output | Leave unconnected.                                                              |  |

| HOLDRQ                                                                | Input  | Connect to EVDD.                                                                |  |

| BSTB, HOLDAK                                                          | Output | Leave unconnected.                                                              |  |

| SCK1, SCK2                                                            | Input  | Connect to EVDD or GND.                                                         |  |

| SI1, SI2                                                              | Input  |                                                                                 |  |

| SIEN1, SIEN2                                                          | Input  | Connect to GND.                                                                 |  |

| SOEN1, SOEN2                                                          | Input  |                                                                                 |  |

| SORQ1                                                                 | Output | Leave unconnected.                                                              |  |

| SO1, SO2                                                              | Output |                                                                                 |  |

| SIAK1                                                                 | Output |                                                                                 |  |

| HA0, HA1                                                              | Input  | Connect to EVDD or GND.                                                         |  |

| $\overline{\text{HCS}}, \overline{\text{HRD}}, \overline{\text{HWR}}$ | Input  | Connect to EVDD.                                                                |  |

| HRE, HWE                                                              | Output | Leave unconnected.                                                              |  |

| HD0 - HD7 <sup>Note 2</sup>                                           | I/O    | Connect to EVDD via pull-up resistor, or connect to GND via pull-down resistor. |  |

| P0 - P3                                                               | I/O    |                                                                                 |  |

| тск                                                                   | Input  | Connect to GND via pull-down resistor.                                          |  |

| TDO, TICE                                                             | Output | Leave unconnected.                                                              |  |

| TMS, TDI                                                              | Input  | Leave unconnected. (internally pulled up).                                      |  |

| TRST                                                                  | Input  | Leave unconnected. (internally pulled down).                                    |  |

| CLKOUT                                                                | Output | Leave unconnected.                                                              |  |

- **Notes 1.** These pins may be left unconnected if the external data memory is not accessed in the program. However, connect these pins as recommended in the halt and stop modes when the power consumption must be lowered.

- These pins may be left unconnected if HCS, HRD, and HWR are fixed to the high level. However, connect these pins as recommended in the halt and stop modes when the power consumption must be lowered.

#### 1.2.2 Connection of no-function pins

| Pin  | I/O | Recommended Connection |  |  |

|------|-----|------------------------|--|--|

| I.C. | -   | Leave unconnected.     |  |  |

| NU   | -   | Connect to EVDD.       |  |  |

| NC   | -   | Leave unconnected.     |  |  |

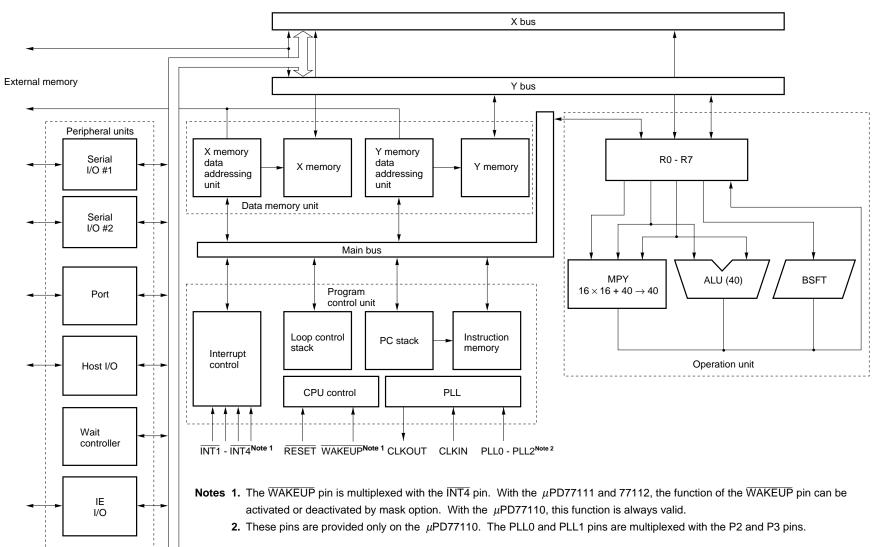

#### 2. FUNCTION OUTLINE

#### 2.1 Program Control Unit

This unit is used to execute instructions, and control branching, loops, interrupts, the clock, and the standby mode of the DSP.

#### 2.1.1 CPU control

A three-stage pipeline architecture is employed and almost all the instructions, except some instructions such as branch instructions, are executed in one system clock.

#### 2.1.2 Interrupt control

Interrupt requests input from external pins ( $\overline{INT1}$  through  $\overline{INT4}$ ) or generated by the internal peripherals (serial interface and host interface) are serviced. The interrupt of each interrupt source can be enabled or disabled. Multiple interrupts are also supported.

#### 2.1.3 Loop control task

A loop function without any hardware overhead is provided. A loop stack with four levels is provided to support multiple loops.

#### 2.1.4 PC stack

A 15-level PC stack that stores the program counter supports multiple interrupts and subroutine calls.

#### 2.1.5 PLL

A PLL is provided as a clock generator that can multiply or divide an external clock input to supply an operating clock to the DSP. The multiplication and division ratio are set as follows:

- μPD77110: A multiple of ×1 to ×8 is specified by an external pin (division ratio is fixed).

- $\mu$ PD77111 and 77112: A multiple of ×1 to ×16 or a division ratio of 1/1 to 1/16 can be set by a mask option.

Two standby modes are available for lowering the power consumption while the DSP is not in use.

- HALT mode: Set by execution of the HALT instruction. The current consumption drops to several mA. The normal operation mode is recovered by an interrupt or hardware reset.

- STOP mode: Set by execution of the STOP instruction. The current consumption drops to several 10 μA. The normal operation mode is recovered by hardware reset or WAKEUP pin<sup>Note</sup>.

Note If the WAKEUP function is activated by mask option

#### 2.1.6 Instruction memory

The capacity and type of the memory differ depending on the model of the DSP.

64 words of the instruction RAM are allocated to interrupt vectors.

A boot-up ROM that boots up the instruction RAM is provided, and the instruction RAM can be initialized or rewritten by self boot (boot from the internal data ROM or external data space) or host boot (boot via host interface).

- μPD77110: 35.5K-word RAM

- μPD77111, 77112: 1K-word RAM and 31.75K-word ROM

#### 2.2 Arithmetic Unit

This unit performs multiplication, addition, logical operations, and shift, and consists of a 40-bit multiply accumulator, 40-bit data ALU, 40-bit barrel shifter, and eight 40-bit general-purpose registers.

#### 2.2.1 General-purpose registers (R0 through R7)

These eight 40-bit registers are used to input/output data for arithmetic operations, and load or store data from/to data memory.

A general-purpose register (R0 to R7) is made up of three parts: R0L through R7L (bits 15 through 0), R0H through R7H (bits 31 through 16), and R0E through R7E (bits 39 through 32). Depending on the type of operation, RnL, RnH, and RnE are used as one register or in different combinations.

#### 2.2.2 Multiply accumulator (MAC)

The MAC multiplies two 16-bit values, and adds or subtracts the multiplication result from one 40-bit value, and outputs a 40-bit value.

The MAC is provided with a shifter (MSFT: MAC ShiFTer) at the stage preceding the input stage. This shifter can arithmetically shift the 40-bit value to be added to or subtracted from the multiplication result 1 or 16 bits to the right .

#### 2.2.3 Arithmetic logic unit (ALU)

This unit inputs one or two 40-bit values, executes an arithmetic or logical operation, and outputs a 40-bit value.

#### 2.2.4 Barrel shifter (BSFT: Barrel ShiFTer)

The barrel shifter inputs a 40-bit value, shifts it to the left or right by any number of bits, and outputs a 40-bit value. The data may be arithmetically shifted to the right shifted to the right, in which case the data is sign-extended, or logically shifted to the right, in which case 0 is inserted from the MSB.

#### 2.3 Data Memory Unit

The data memory unit consists of two banks of data memory and two data addressing units.

#### 2.3.1 Data memory

The capacity and type of the memory differ depending on the model of the DSP. All DSPs have two banks of data memory (X data memory and Y data memory). A 64-word peripheral area is assigned in the data memory space.

- $\mu$ PD77110: RAM of 24K words  $\times$  2 banks

- $\mu$ PD77111, 77112: RAM of 3K words  $\times$  2 banks and ROM of 16K words  $\times$  2 banks

In addition, some models have an external data memory interface so that the external memory can be expanded.

- μPD77110: External data memory of 32K words × 2 banks

- μPD77112: External data memory of 16K words × 2 banks

#### 2.3.2 Data addressing unit

An independent data addressing unit is provided for each of the X data memory and Y data memory spaces.

Each data addressing unit has four data pointers (DPn), four index registers (DNn), one modulo register (DMX or DMY), and an address ALU.

#### 2.4 Peripheral Units

A serial interface, host interface, general-purpose I/O port, and wait cycle register are provided. All these internal peripherals are mapped to the X data memory and Y data memory spaces, and are accessed from program as memory-mapped I/Os.

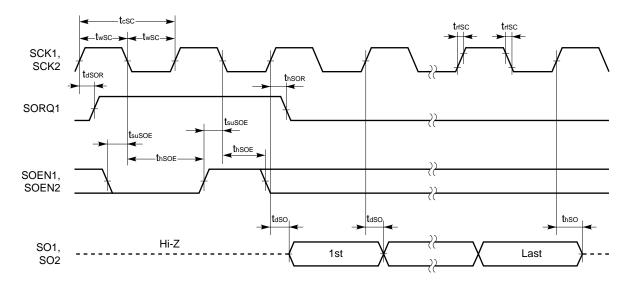

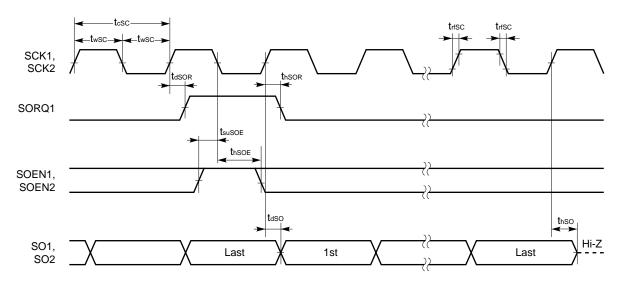

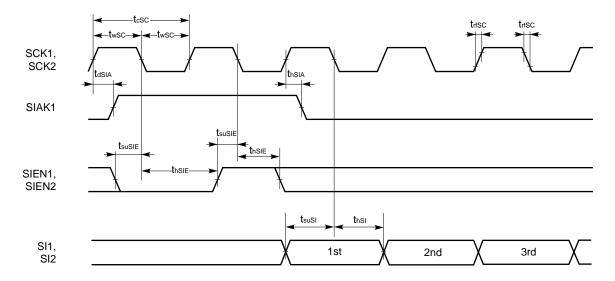

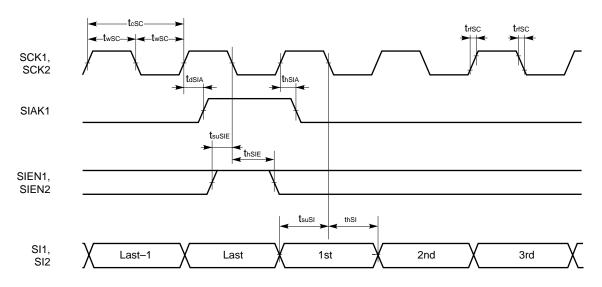

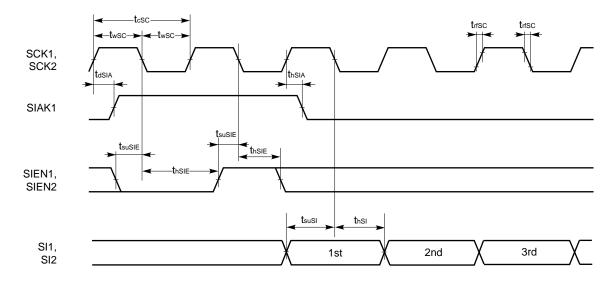

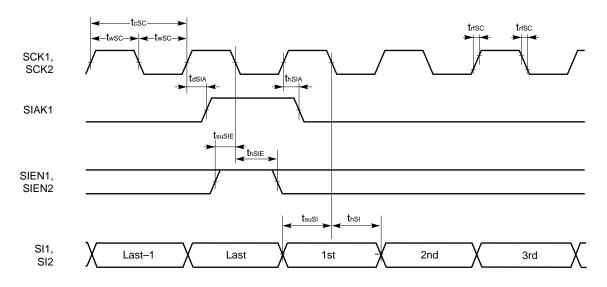

#### 2.4.1 Serial interface (SIO)

Two serial interfaces are provided. These serial interfaces have the following features:

- Serial clock : Supplied from external source to each interface. The same clock is used for input and output on the interface.

- Frame length: 8 or 16 bits, and MSB or LSB first selectable for each interface and input or output

- Handshake : Handshaking with external devices is implemented with a dedicated status signal. With the internal units, polling, wait, or interrupt are used.

#### 2.4.2 Host interface (HIO)

This is an 8-bit parallel port that inputs data from or outputs data to an external host CPU or DMA controller. In the DSP, a 16-bit register is mapped to memory for input data, output data, and status. Handshaking with an external device is implemented by using a dedicated status signal. Handshaking with internal units is achieved by means of polling, wait, or interrupts.

#### 2.4.3 General-purpose I/O port (PIO)

This is a 4-bit I/O port that can be set in the input or output mode in 1-bit units.

#### 2.4.4 Wait cycle register

The number of wait cycles to be inserted when the external data memory area is accessed can be specified in advance by using a register (DWTR)<sup>Note</sup>. The number of wait cycles that can be set is 1, 3, or 7.

**Note** This function is not available on the  $\mu$ PD77111 because this DSP does not have an external data area.

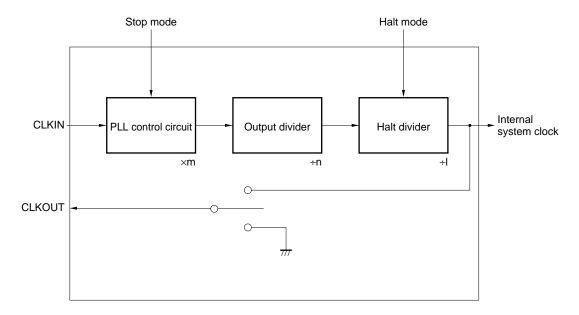

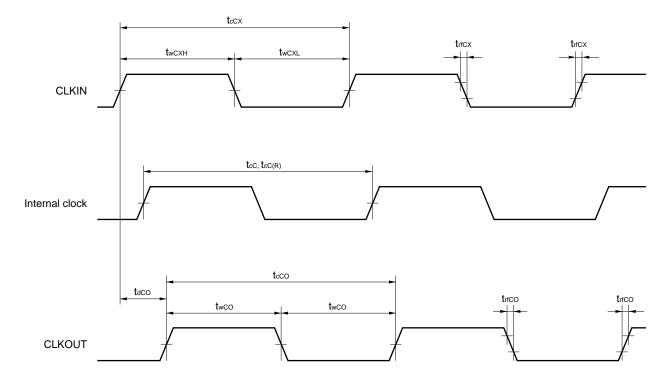

#### 3. CLOCK GENERATOR

The clock generator generates an internal system clock based on the external clock input from the CLKIN pin and supplies the generated clock to the internal units of the DSP.

For details of how to set the PLL multiple, refer to **4.2 Initializing PLL**, **8.1 Clock Control Options**, and **8.3.1 Settings related to clock control**.

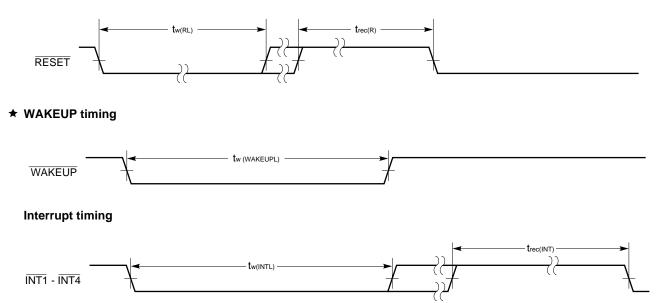

#### 4. RESET FUNCTION

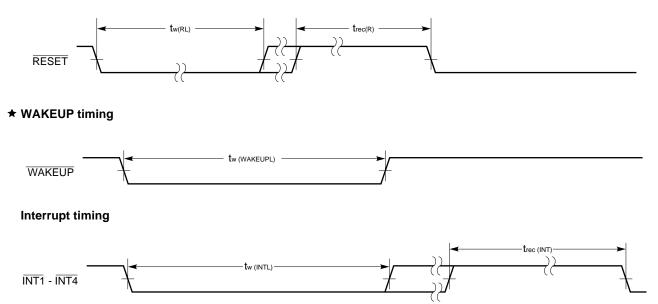

When a low level of a specified width is input to the RESET pin, the device is initialized.

#### 4.1 Hardware Reset

If the RESET pin is asserted active (low level) for a specified period, the internal circuitry of the DSP is initialized. If the RESET pin is then deasserted inactive (high level), boot processing of the instruction RAM is performed according to the status of the port pins (P0 and P1). After boot processing, processing is executed starting from the instruction at address 0x200 of instruction memory (reset entry).

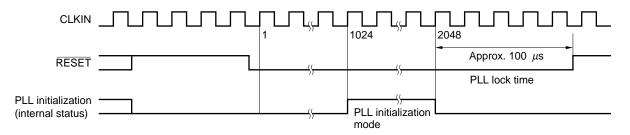

On power application, the RESET pin must be asserted active (low level) after 4 input clocks have been input with the RESET pin in the inactive status (high level), after the supply voltage has reached the level of the operating voltage. In other words, no power-ON reset function is available. On power application, the PLL must be initialized.

#### 4.2 Initializing PLL

NEC

Initializing the PLL starts from the 1024th input clock after the  $\overline{\text{RESET}}$  pin has been asserted active (low level). Initialization takes 1024 clocks and it takes the PLL 100  $\mu$ s to be locked.

After that, the DSP operates with the set value of the PLL specified by a mask option ( $\mu$ PD77111 or 77112) or an external pin ( $\mu$ PD77110) when the RESET pin is deasserted inactive (high level).

After initializing the PLL, be sure to execute boot-up processing to re-initialize the internal RAM. To initialize the PLL, the internal memory contents and register status of the DSP are not retained.

If the RESET pin is deasserted inactive before the PLL initialization mode is set, the DSP is normally reset (the PLL is not initialized).

# Caution Do not deassert the RESET signal inactive in the PLL initialization mode and during PLL lock period.

#### 5. FUNCTIONS OF BOOT-UP ROM

To rewrite the contents of the instruction memory on power application or from program, boot up the instruction RAM by using the internal boot-up ROM.

The  $\mu$ PD77110 has a function to verify the contents of the internal instruction RAM in the boot-up ROM.

#### 5.1 Boot at Reset

After hardware reset has been cleared, the boot program first reads the general-purpose I/O ports P0 and P1 and, depending on their bit pattern, determines the boot mode (self boot or host boot). After boot processing, processing is executed starting from the instruction at address 0x200 (reset entry) of the instruction memory.

The pins (P0 and P1) that specify the boot mode must be kept stable for the duration of 3 clocks before and for the duration of 12 clocks after reset has been cleared (the clock is input from CLKIN).

| P1 | P0 | Boot Mode                                                             |  |  |  |

|----|----|-----------------------------------------------------------------------|--|--|--|

| 0  | 0  | Does not execute boot but branches to address 0x200 <sup>Note</sup> . |  |  |  |

| 0  | 1  | Executes host boot and then branches to address 0x200.                |  |  |  |

| 1  | 1  | Executes self boot and then branches to address 0x200.                |  |  |  |

| 1  | 0  | Setting prohibited                                                    |  |  |  |

**Note** This setting is used when the DSP must be reset to recover from the standby mode after reset boot has been executed once.

#### 5.1.1 Self boot

The boot-up ROM transfers the instruction code stored in the data memory space to the instruction RAM, based on the boot parameter written to address 0x4000 of the Y data memory. Generally, with a mask ROM model ( $\mu$ PD77111 or 77112), this function is implemented by storing the instructions to be booted in the data ROM.

In addition, the instructions to be booted can be also stored in an external data area in the form of flash ROM, and self boot can be executed from this external data area.

With the  $\mu$ PD77110, the value of address 0x4000 of the Y data memory is undefined on power application, because this address is in RAM. Therefore, with the  $\mu$ PD77110, the self boot mode cannot be selected on power application, and host boot must be executed. This also applies when the PLL is initialized. By writing a boot parameter to address 0x4000 or those that follow of the Y data memory, self boot can be executed when the RESET signal is subsequently input (except the reset that initializes the PLL). In this case, however, the instructions to be booted are only those at address 0x0200 through 0x0FFF of the instruction RAM.

#### 5.1.2 Host boot

In this boot mode, a boot parameter and instruction code are obtained via the host interface, and transferred to the instruction RAM.

With the  $\mu$ PD77110, the host boot mode is used on power application. The boot instruction area is the instruction RAM from addresses 0x0200 through 0x0FFF. To boot up the instruction RAM from 0x4000 through 0xBFFF, host reboot is used.

#### 5.2 Reboot

By calling the next reboot entry from the program, the contents of the instruction RAM can be rewritten. In particular, the  $\mu$ PD77110 has a reboot function that boots up the instruction RAM from 0x4000 through 0xBFFF.

|           | Entry Address |             |                                         |

|-----------|---------------|-------------|-----------------------------------------|

| Self boot | X memory      | Word reboot | 0x2                                     |

|           |               | Byte reboot | 0x4                                     |

|           | Y memory      | Word reboot | 0x1                                     |

|           |               | Byte reboot | 0x3                                     |

| Host boot | Host reboot   |             | 0x6 (μPD77110)<br>0x5 (μPD77111, 77112) |

#### 5.2.1 Self reboot

The instruction codes stored in the data memory are transferred to the instruction RAM. This boot mode cannot be used with the  $\mu$ PD77110.

Set the following parameters and call the entry address of the corresponding reboot mode to execute self reboot.

- R7L: Number of instruction steps for rebooting

- DP3: First address of X memory in which instruction codes are stored (in the case of reboot from X memory), or first address of the instruction memory to be loaded (in the case of reboot from Y memory)

- DP7: First address of instruction memory to be loaded (in the case of reboot from X memory), or first address of X memory in which instruction codes are stored (in the case of reboot from Y memory)

## NEC

#### 5.2.2 Host reboot

An instruction code is obtained via the host interface and transferred to the instruction RAM.

With the  $\mu$ PD77110, the host reboot mode is used to boot up the instruction RAM from addresses 0x4000 through 0xBFFF. Areas 0x0200 through 0x0FFF and 0x4000 through 0xBFFF cannot be rebooted all at once.

The entry address of the  $\mu$ PD77110 is 0x6, and that of the  $\mu$ PD77111 and 77112 is 0x5. Host reboot is executed by calling this address after setting the following parameter:

- R7L: Number of instruction steps for rebooting

- DP3: First address of instruction memory to be loaded

#### 5.3 Signature Operation

The  $\mu$ PD77110 has a signature operation function so that the contents of the internal instruction RAM can be verified. The signature operation performs a specific arithmetic operation on the data in the instruction RAM booted up, and returns the result to a register. Perform the signature operation in advance on the device when it is operating normally, and repeat the signature operation later to check whether the data in RAM is correct by comparing the operation result with the previous result. If the results are identical, there is no problem.

The entry address is 0x9. Execute the operation by calling this address after setting the following parameter. Note that the operation cannot be performed on the areas 0x0200 through 0x0FFF and 0x4000 through 0xBFFF at the same time. The operation result is stored in register R7.

- R7L: Number of instruction steps for operation

- DP3: First address of instruction memory for operation

#### 6. STANDBY MODES

Two standby modes are available. By executing the corresponding instruction, each mode is set and the power consumption can be reduced.

#### 6.1 HALT Mode

To set this mode, execute the HALT instruction. In this mode, functions other than clock circuit and PLL are stopped to reduce the current consumption.

To release the HALT mode, use an interrupt or hardware reset. When releasing the HALT mode using an interrupt, the contents of the internal registers and memory are retained. It takes several 10 system clocks to release the HALT mode when the HALT mode is released using an interrupt.

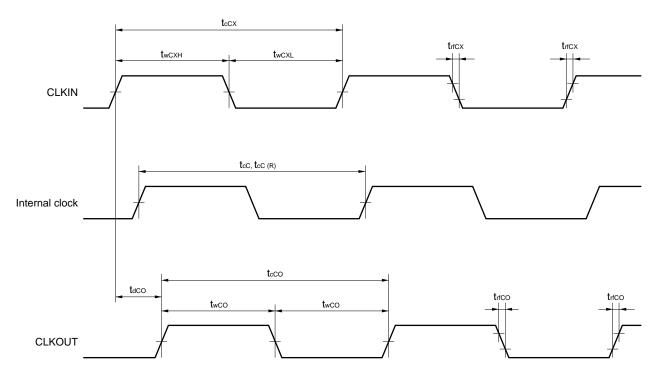

In the HALT Mode, the clock circuit of the  $\mu$ PD77111 family supplies the following clock as the internal system clock. The clock output from the CLKOUT pin is as follows.

The clock output from the CLKOUT pin, however, has a high-level width that is equivalent to 1 cycle of the normal operation (i.e., the duty factor is not 50%).

- μPD77110: 1/8 of internal system clock

- μPD77111, 77112: 1/l of internal system clock (I = integer from 1 to 16, specified by mask option)

#### 6.2 STOP Mode

To set this mode, execute the STOP instruction. In this mode, all the functions, including the clock circuit and PLL, are stopped and the power consumption is minimized with only leakage current flowing.

To release the STOP mode, use hardware reset or WAKEUP pin.

When releasing the STOP mode by using the WAKEUP pin, the contents of the internal registers and memory are retained, but it takes several 100  $\mu$ s to release the mode.

The WAKEUP pin is multiplexed with the INT4 pin. Usually, this pin functions as an interrupt pin, but functions as the WAKEUP pin when it is asserted active in the STOP mode. Whether the WAKEUP pin is used to release the STOP mode is selected by mask option. For details, refer to **8.2 WAKEUP Function** and **8.3.2 WAKEUP function**.

#### 7. MEMORY MAP

A Harvard architecture, in which the instruction memory space and data memory space are separated is employed.

#### 7.1 Instruction Memory

#### 7.1.1 Instruction memory map

The instruction memory space consists of 64K words  $\times$  32 bits, and the capacity and type of the memory differ depending on the product.

|                            | μPD77110                                   |        | μPD77111, 77112                               |

|----------------------------|--------------------------------------------|--------|-----------------------------------------------|

| 0xFFFF<br>0xC000<br>0xBFFF | System                                     | 0xBF00 | System                                        |

|                            | Internal instruction<br>RAM<br>(32K words) | 0xBEFF | Internal instruction<br>ROM<br>(31.75K words) |

| 0x4000<br>0x3FFF<br>0x1000 | System                                     | 0x0600 | System                                        |

| 0x0FFF<br>0x0240           | Internal instruction RAM<br>(3.5K words)   | 0x05FF | Internal instruction RAM<br>(1K words)        |

| 0x023F<br>0x0200           | Vector area (64 words)                     |        | Vector area (64 words)                        |

| 0x01FF<br>0x0100           | System                                     |        | System                                        |

| 0x00FF<br>0x0000           | Boot-up ROM<br>(256 words)                 |        | Boot-up ROM<br>(256 words)                    |

Caution Programs and data cannot be placed at addresses reserved for the system, nor can these addresses be accessed. If these addresses are accessed, the normal operation of the device cannot be guaranteed.

#### 7.1.2 Interrupt vector table

Addresses 0x200 through 0x23F of the instruction memory are entry points (vectors) of interrupts. Four instruction addresses are assigned to each interrupt source.

| Vector | Interrupt Source |

|--------|------------------|

| 0x200  | Reset            |

| 0x204  | Reserved         |

| 0x208  |                  |

| 0x20C  |                  |

| 0x210  | INT1             |

| 0x214  | INT2             |

| 0x218  | INT3             |

| 0x21C  | INT4             |

| 0x220  | SI1 input        |

| 0x224  | SO1 output       |

| 0x228  | SI2 input        |

| 0x22C  | SO2 output       |

| 0x230  | HI input         |

| 0x234  | HO output        |

| 0x238  | Reserved         |

| 0x23C  |                  |

Cautions 1. Although reset is not an interrupt, it is handled like an interrupt as an entry to a vector.

- 2. It is recommended that unused interrupt source vectors be used to branch an error processing routine.

- 3. Because a vector area also exists in the internal RAM area of the mask ROM model, this area must be booted up. In addition, because the entry address after reset is 0x200, address 0x200 must be booted up even when the internal instruction RAM and interrupts are not used.

#### 7.2 Data Memory

#### 7.2.1 Data memory map

The data memory space consists of an X memory space and a Y memory space of 64K words  $\times$  16 bits each, and the memory capacity and memory type differ depending on the product.

|                  | μPD77110                 |                  | μPD77111                 |                   | $\mu$ PD77112                          |

|------------------|--------------------------|------------------|--------------------------|-------------------|----------------------------------------|

| 0xFFFF           | External data<br>memory  |                  | System                   | 0xC000_<br>0xBFFF | External data<br>memory<br>(16K words) |

| 0×8000           | (32K words)              |                  |                          |                   | System                                 |

| 0x7FFF<br>0x4000 | Data RAM<br>(16K words)  |                  | Data ROM<br>(16K words)  |                   | Data ROM<br>(16K words)                |

| 0x3FFF<br>0x3840 | System                   |                  | System                   |                   | System                                 |

| 0x383F<br>0x3800 | Peripheral<br>(64 words) |                  | Peripheral<br>(64 words) |                   | Peripheral<br>(64 words)               |

| 0x37FF<br>0x3000 | System                   |                  | i                        |                   |                                        |

| 0x2FFF<br>0x2000 | Data RAM<br>(4K words)   |                  | System                   |                   | System                                 |

| 0x1FFF<br>0x1000 | System                   |                  |                          |                   |                                        |

| 0x0FFF<br>0x0000 | Data RAM<br>(4K words)   | 0x0C00<br>0x0BFF | Data RAM<br>(3K words)   |                   | Data RAM<br>(3K words)                 |

Caution Programs and data cannot be placed at addresses reserved for the system, nor can these addresses be accessed. If these addresses are accessed, the normal operation of the device cannot be guaranteed.

#### 7.2.2 Internal peripherals

The internal peripherals are mapped to the internal data memory space.

| X/Y Memory Address | Register Name | Function                         | Peripheral Name |

|--------------------|---------------|----------------------------------|-----------------|

| 0x3800             | SDT1          | First serial data register       | SIO             |

| 0x3801             | SST1          | First serial status register     |                 |

| 0x3802             | SDT2          | Second serial data register      |                 |

| 0x3803             | SST2          | Second serial status register    |                 |

| 0x3804             | PDT           | Port data register               | IOP             |

| 0x3805             | PCD           | Port command register            |                 |

| 0x3806             | HDT           | Host data register               | HIO             |

| 0x3807             | HST           | Host status register             |                 |

| 0x3808             | DWTR          | Data memory wait cycle register  | WTR             |

| 0x3809 - 0x383F    | Reserved area | Caution Do not access this area. | -               |

- Cautions 1. The register names listed in this table are not reserved words of the assembler or the C language. Therefore, when using these names in assembler or C, the user must define them.

- 2. The same register is accessed, as long as the address is the same, regardless of whether the X memory space or Y memory space is accessed.

- 3. Even different registers cannot be accessed at the same time from both the X and Y memory spaces.

#### 8. MASK OPTION

The  $\mu$ PD77111 and 77112 have mask options that must be specified when an order for a ROM is placed. This section explains these mask options. The mask options are specified in the Workbench (WB77016) development tool. To order a mask ROM, output a mask ROM ordering file format (.msk file) using WB77016.

#### 8.1 Clock Control Options

The following four clock related options must be specified.

- PLL multiple

- Output division ratio

- HALT division ratio

- Validity of CLKOUT pin

When the PLL multiple is m, output division ratio is n, and halt division ratio is I, the relationship between each operation mode and operating clock is as follows:

| Operation Mode        | Clock Supplied Inside DSP        |

|-----------------------|----------------------------------|

| Normal operation mode | m/n times external input clock   |

| HALT mode             | m/n/l times external input clock |

| STOP mode             | Stopped                          |

The PLL control circuit multiplies the input clock by an integer from 1 to 16. Specify the mask option of the PLL multiple so that the multiplied frequency falls within the specified PLL lock frequency range.

The output divider divides the clock multiplied by the PLL by an integer from 1 to 16. Specify the mask option of the output division ratio so that the frequency m/n times the external input clock supplied to the DSP falls within the specified operating frequency range of the DSP.

The HALT divider functions only in the HALT mode. It divides the clock of the output divider by an integer from 1 to 16 and supplies the divided clock to the internal circuitry. Specify the mask option of the HALT division ratio so that necessary division can be performed.

Whether the clock supplied to the internal circuitry of the DSP (internal system clock) is "output" or "not output" from the CLKOUT pin can be specified. Specify the mask option as necessary.

If an odd value (other than 1) is specified as the output division ratio, the high-level width of the clock output from the CLKOUT pin is equal to one cycle during normal operation (i.e., the clock does not have a duty factor of 50%).

#### 8.2 WAKEUP Function

The WAKEUP pin can be used to release the STOP mode as well as a hardware reset.

If the STOP mode is released by means of a hardware reset, the status before the STOP mode was set cannot be restored after the STOP mode has been released. If the WAKEUP pin is used, however, the status before the STOP mode is set can be retained and program execution can be resumed starting from the instruction after the STOP instruction.

Whether the WAKEUP pin is used to release the STOP mode can be specified by a mask option.

When the WAKEUP function is specified valid, the WAKEUP pin is multiplexed with the INT4 pin and it usually functions as an interrupt pin. The pin functions as the WAKEUP pin only in the STOP mode (if this pin is asserted active in the STOP mode, it is used only to release the STOP mode, and execution does not branch to an interrupt vector).

#### 8.3 Mask Option Equivalent Function of µPD77110

Because the  $\mu$ PD77110 does not have mask options, the multiple of the PLL cannot be specified in the same manner as the  $\mu$ PD77111 and 77112. However, an external pin on the  $\mu$ PD77110 has a function equivalent to the mask option. Care must be exercised when using the  $\mu$ PD77110, including when it is used to emulate the  $\mu$ PD77111 and 77112.

#### 8.3.1 Settings related to clock control