# INTEGRATED CIRCUITS

Product specification File under Integrated Circuits, IC02 1999 March 01

## **FEATURES**

- 16/32/64/128/256 QAM demodulator (DVB-C compatible : ETS 300-429).

- On chip 9-bit ADC.

- On chip PLL for crystal frequency multiplication.

- Digital down conversion.

- Half Nyquist filters (roll off = 15 %).

Automatic gain control PWM output

- (AGC).Symbol timing recovery, with

- Symbol timing recovery, with programmable second order loop filter.

Variable symbol rate capability from

- Variable symbol rate capability from SACLK/64 to SACLK/4 (SACLK max = 36 MHz)

- Programmable anti-aliasing filters.

- Full digital carrier recovery loop.

- Carrier acquisition range up to 8 % of symbol rate.

- Integrated adaptative equalizer (Linear Transversal Equalizer or Decision Feedback Equalizer).

- On chip FEC decoder (Deinterleaver & RS decoder), full DVB-C compliant.

- DVB compatible differential decoding and mapping.

- Parallel or serial transport stream interface.

- I2C bus interface, for easy control.

- CMOS 0.35µm technology.

# **APPLICATIONS**

- DVB-C fully compatible.

- Digital data transmission using QAM modulations.

- Cable demodulation.

- Cable modems

- MMDS (ETS 300-429).

# DESCRIPTION

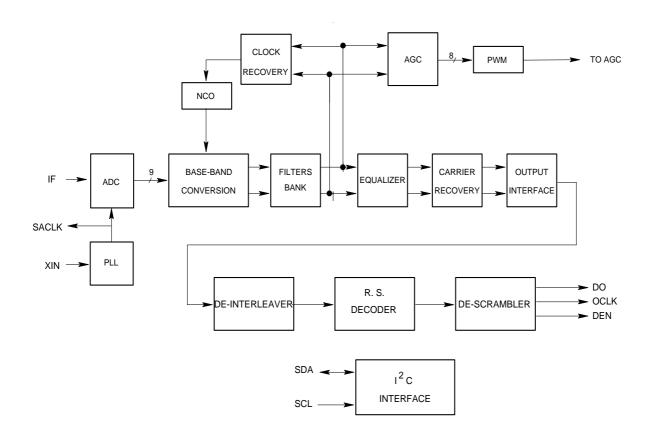

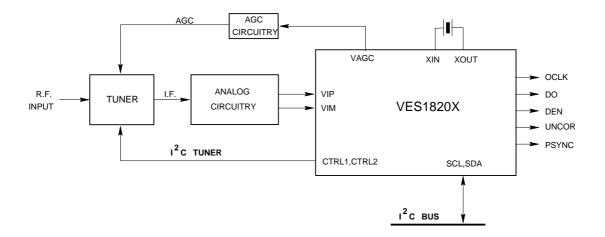

The VES1820X is a single chip channel receiver for 16, 32, 64, 128 and 256-QAM modulated signals. The device interfaces directly to the IF signal, which is sampled by a 9-bit AD converter.

The VES1820X performs the clock and the carrier recovery functions. The digital loop filters for both clock and carrier recovery are programmable in order to optimize their characteristics according to the current application.

After base band conversion, equalization filters are used for echo cancellation in cable applications. These filters are configured as Tspaced transversal equalizer or DFE equalizer, so that the system performance can be optimized according to the network characteristics. A proprietary equalization algorithm, independent of carrier offset, is achieved in order to assist carrier recovery. Then a decision directed algorithm takes place, to achieve final equalization convergence.

The VES1820X implements a FORNEY convolutional deinterleaver of depth 12 blocks and a Reed-Solomon decoder which corrects up to 8 erroneous bytes. The deinterleaver and the RS decoder are automatically synchronized thanks to the frame synchronization algorithm which uses the MPEG2 sync byte. Finally descrambling according to DVB-C standard, is achieved at the Reed Solomon output. This device is controlled via an I2C bus.

Designed in 0.35  $\mu$ m CMOS technology and housed in a 100 pin MQFP package, the VES1820X operates over the commercial temperature range.

# **VES1820X**

# VES1820X

## FIGURE 1 : FUNCTIONAL BLOCK DIAGRAM

# **VES1820X**

## **TABLE 1 : ABSOLUTE MAXIMUM RATINGS**

| Parameter                          | Min   | Min Max   |    |

|------------------------------------|-------|-----------|----|

| Ambient operating temperature : Ta | 0     | 70        | °C |

| DC supply voltage                  | - 0.5 | + 4.1     | V  |

| DC Input voltage                   | - 0.5 | VDD + 0.5 | V  |

| DC Input Current                   |       | ± 20      | mA |

| Lead Temperature                   |       | +300      | °C |

| Junction Temperature               |       | +150      | °C |

Stresses above the absolute maximum ratings may cause permanent damage to the device. Exposure to absolute maximum ratings conditions for extended periods may affect device reliability.

### **TABLE 2 : RECOMMENDED OPERATING CONDITIONS**

| Symbol           | Parameter                    | Min             | Тур  | Max        | Unit | Notes                                |

|------------------|------------------------------|-----------------|------|------------|------|--------------------------------------|

| VDD              | Digital supply voltage       | 3.14            | 3.3  | 3.46       | V    | 3.3V ±5%                             |

| VCC              | 5V supply                    | 4.75            | 5    | 5.25       | V    | pin 17                               |

| Та               | Operating temperature        | 0               |      | 70         | °C   | Ambient<br>temperature               |

| VIH <sup>1</sup> | High-level input voltage     | 2               |      | VCC + 0.3  | V    | TTL input                            |

| VIL              | Low-level input voltage      | -0.5            |      | 0.8        | V    | TTL input                            |

| VOH <sup>2</sup> | High-level output<br>voltage | VDD -0.1<br>2.4 |      |            | V    | @ IOH = -0.8 mA<br>@ IOH = + 2mA     |

| VOL <sup>2</sup> | Low-level output voltage     |                 |      | 0.1<br>0.4 | V    | @ IOL = 0.8 mA<br>@ IOL = + 2mA      |

| IDD              | Supply current               |                 | 200  |            | mA   | @XIN = 57.84Mhz<br>Symbol Rate =6Mbd |

| CIN              | Input capacitance            |                 | 15   |            | pF   |                                      |

| COUT             | Output capacitance           |                 | 15   |            | pF   |                                      |

| VD2, VD3, VD4    | Analog supply voltage        | 3.14            | 3.3  | 3.46       | V    | 3.3V ± 5%                            |

| VIP              | Positive analog input        |                 | 0.5  |            | V    |                                      |

| VIM              | Negative analog input        |                 | -0.5 |            | V    |                                      |

<sup>&</sup>lt;sup>1</sup> All inputs are 5V tolerant

$<sup>^{2}</sup>$  IOH, IOL = ± 4mA only for pins SACLK, OCLK, SDA, CTRL1, CTRL2, IT

## **VES1820X**

### **FUNCTIONAL DESCRIPTION**

#### > ADC

The VES1820X implements a 9-bit analog to digital converter. No external voltage references are required to use the ADC.

### > PLL

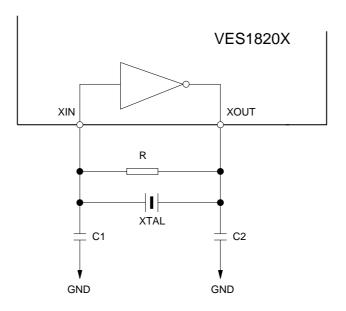

The VES1820X implements a PLL used as clock multiplier by 1, 2, 3, 4, 5, 6, 7 or 8, so that the crystal can be low frequency (fundamental tone).

#### > DOWN CONVERTER AND NYQUIST FILTERS

The digital down converter performs the down conversion of the bandpass input signal into the 2 classical quadrature I & Q channels. Then these two signals are passed through anti-alias filters and through a half Nyquist filter having a fixed roll-off of 0.15. The digital filter gives a stop band attenuation of more than 40 dB.

#### > EQUALIZER

After Nyquist filtering, the signal is fed to an equalization filter, for echo cancellation. This equalizer can be configured as either a transversal Equalizer or a decision feedback equalizer. The following table shows some echos configuration that the VES1820X corrects with an equivalent degradation of less than 1dB @ BER =  $10^{4}$ .

| DELAY<br>(nS) | AMPLITUDE<br>(dB) | PHASE |

|---------------|-------------------|-------|

| 50            | -10               | worst |

| 150           | -12               |       |

| and           | and               | worst |

| 800           | -20               |       |

| 1600          | -20               | worst |

#### > CARRIER RECOVERY

The carrier synchronizer implements a fully digital algorithm allowing to recover carrier frequency offsets up to  $\pm 8$  % symbol rate. A phase error detector followed by a programmable second order loop filter provides an estimation of the carrier phase, to compensate the input carrier frequency offset.

#### > CLOCK RECOVERY

A timing error detector implements an application of Gardner algorithm for digital clock recovery. The resulting error is fed to a programmable second order loop filter, which provides a 8-bit command to the NCO block. This one allows to determine the right sampling time instant of the input signal.

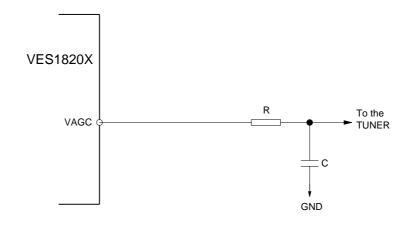

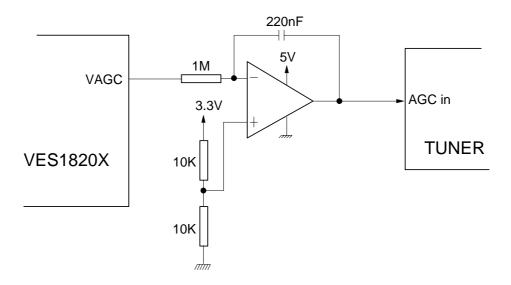

#### > AUTOMATIC GAIN CONTROL

An estimation of input signal magnitude is performed and compared to a threshold value which is programmable via the microcontroller interface. The resulting error is then filtered to produce an 10-bit command which is then PWM encoded and provided on pin VAGC. The PWM signal can be passed through a single RC filter to control the input gain amplifier.

#### > OUTPUT INTERFACE

After carrier recovery, the demodulated output symbol must be decoded according to the constellation diagram given by DVB standard for 16, 32, 64, 128 and 256 QAM. The resulting symbols are then differentially decoded (DVB compliant) and serially provided to the FEC part.

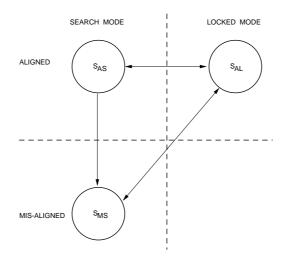

#### > BLOCK SYNCHRONIZATION

At demodulator output, the length of some error bursts may exceed that which can be reliably corrected by the Reed-Solomon decoder. The implemented de-interleaving is a convolutional one (Forney) of depth 12. The first operation consists in synchronizing the de-interleaver. This is accomplished by detecting  $\alpha$  consecutive MPEG2 sync words (or sync) which are present as the first byte of each packet.

## **VES1820X**

Next, the RAM memory associated with the deinterleaver fills up and the first deinterleaved bytes are provided to the input of the Reed-Solomon decoder. The state machine of the de-interleaver goes to the control phase which counts  $\beta$  consecutive missed MPEG2 sync words (or sync) before declaring the system desynchronized and going back to the synchronization phase.  $\alpha$  and  $\beta$  are programmable through the I2C interface.

When the inverted sync word is detected at the input of the de-interleaver, the bytes provided to the Reed-Solomon decoder are inverted at the output of the deinterleaver.

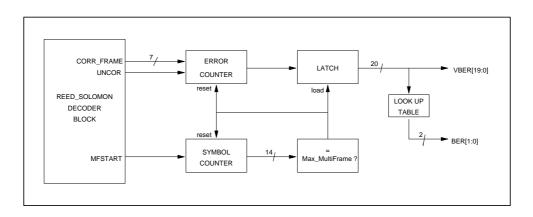

#### > REED-SOLOMON DECODER

The Reed-Solomon decoder decodes the symbol stream from the de-interleaver according to the (204, 188) shortened Reed-Solomon code. Synchronization to Reed-Solomon code is defined over the finite Galois field GF ( $2^8$ ). The field generator polynomial is given by :

$$G(\mathbf{x}) = \prod_{i=0}^{15} (\mathbf{x} + \alpha^{i})$$

This Reed-Solomon decoder corrects up to eight erroneous symbols in each block. When the correction capability of the decoder is exceeded, the block is not changed and is provided as it has been entered. In this case the flag UNCOR is set and the MSB of the second byte in the MPEG2 frame is forced to one (error indicator). The correction capability of the RS decoder can be inhibited.

#### > DESCRAMBLER

In order to comply with energy dispersal requirements of radio transmission regulations and to ensure adequate binary transitions, the MPEG2 frames are scrambled at the encoder side. Dual operation is achieved at the output of the Reed-Solomon decoder using the same scrambler/descrambler. The polynomial for the pseudo random binary sequence (PRBS generator is  $1 + x^{14} + x^{5}$ . The PRBS registers are initialized at the start of every eight transport packets. To provide an initialization signal for the descrambler, the MPEG2 sync byte of the first transport packet is inverted from 47 to B8. When detected, the descrambler is loaded with the initial sequence "1001010000000". The descrambler can be inhibited.

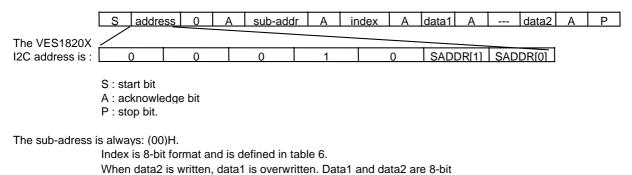

#### > INTERFACE

The VES1820X integrates an I2C interface in slave mode. This I2C interface fulfills the Philips component I2C bus specification.

VES1820X

## **INPUT - OUTPUT SIGNAL DESCRIPTION**

| SYMBOL      | PIN NUMBER                                                  | TYPE        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|-------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLR#        | 27                                                          | I           | The CLR# input is asynchronous and active low, and clears the VES1820X. When CLR# goes low, the circuit immediately enters its RESET mode and normal operation will resume 4 XIN falling edges later after CLR# returned high. The I2C register contents are all initialized to their default values. The minimum width of CLR# at low level is 4 XIN clock periods.                                                                |

| XIN         | 2                                                           | I           | XTAL oscillator input pin. Typically a fundamental XTAL oscillator is connected between the XIN and XOUT pins (see typical application on FIGURE 10 page 15). The XTAL frequency MUST be chosen so that the system frequency SYSCLK (= XIN * multiplying factor of the PLL) equals to 1.6 times the tuner output Intermediate Frequency : SYSCLK = 1.6 x IF.                                                                        |

| XOUT        | 3                                                           | 0           | XTAL oscillator output pin. Typically a fundamental XTAL oscillator is connected between the XIN and XOUT pins (see typical application FIGURE 10 page 15).                                                                                                                                                                                                                                                                         |

| SACLK       | 18                                                          | 0<br>(5V)   | Sampling CLocK. This output clock can be fed to an external 9-bit ADC as the sampling clock.SACLK = SYSCLK/2.                                                                                                                                                                                                                                                                                                                       |

| FI[8:0]     | 5,6,7,8,12,<br>13,14,15,16                                  | I           | FI [8:0] is the 9-bit input of the IF signal. FI[8:0] is the output of an external A/D converter. FI[8] is the MSB. When not used, must be tied to ground.                                                                                                                                                                                                                                                                          |

| VAGC        | 20                                                          | 0<br>(5V)   | PWM encoded output signal for AGC. This signal is typically fed to<br>the AGC amplifier through a single RC network (see typical<br>application FIGURE 11 page 16). The maximum signal frequency on<br>VAGC output is XIN/16. AGC information is refreshed every 1024<br>symbols.                                                                                                                                                   |

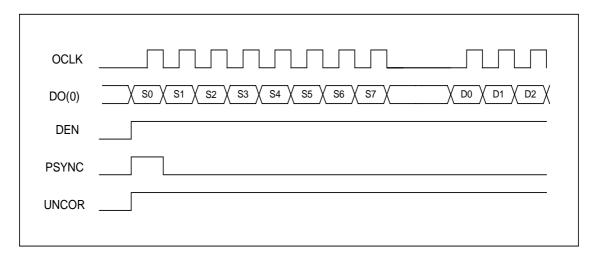

| DO[7:0]     | 46,49,50,51<br>52,53,54,55                                  | O<br>(3.3V) | Data Output bus . These 8-bit parallel data are the outputs of the VES1820X after demodulation, de-interleaving, RS decoding and descrambling.<br>When one of the two possible parallel interfaces is selected (Parameter SERINT=0, index $20_{16}$ ) then DO[7:0] is the transport stream output.<br>When the serial interface is selected (Parameter SERINT=1, index $20_{16}$ ) then the serial output is on pin DO[0] (pin 55). |

| OCLK        | 44                                                          | O<br>(3.3V) | Output CLock. OCLK is the output clock for the parallel DO[7:0] outputs. OCLK is internally generated depending on which interface is selected.                                                                                                                                                                                                                                                                                     |

| DEN         | 45                                                          | O<br>(3.3V) | Data ENable : this output signal is high when there is a valid data on output bus DO[7 :0].                                                                                                                                                                                                                                                                                                                                         |

| UNCOR       | 42                                                          | 0<br>(3.3V) | UNCORrectable packet. This output signal is high when the provided packet is uncorrectable (during the 188 bytes of the packet). The uncorrectable packet is not affected by the Reed Solomon decoder, but the MSB of the byte following the sync. byte is forced « 1 » for the MPEG2 process : Error Flag Indicator (if RSI and IEI are set low in the I2C table).                                                                 |

| PSYNC       | 43                                                          | O<br>(3.3V) | Pulse SYNChro. This output signal goes high when the sync byte $(47_{16})$ is provided, then it goes low until the next sync byte. If the serial interface is selected, then PSYNC is high only during the first bit of the sync byte $(47_{16})$ . See FIGURE 8 page 14.                                                                                                                                                           |

| TESTO[16:0] | 78,77,76,75,74<br>71,70,69,68,67<br>64,63,62,61,60<br>57,56 | O<br>(3.3V) | TESTO [16:0] is 17-bit Test output bus.                                                                                                                                                                                                                                                                                                                                                                                             |

| SYMBOL      | PIN NUMBER | TYPE      | DESCRIPTION                                                                                                                                                                                                      |

|-------------|------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IICDIV[1:0] | 21,22      |           | IICDIV[1:0] allow to select the frequency of the I2C internal system clock, depending on the crystal frequency. Internal I2C clock is a division of XIN by 2 <sup>IICDIV</sup> and must be between 6 and 20 MHz. |

| SADDR[1:0]  | 23,24      | 1         | SADDR[1:0] are the 2 LSBs of the I2C address of the VES1820X.                                                                                                                                                    |

|             |            |           | The MSBs are internally set to 00010. Therefore the complete I2C                                                                                                                                                 |

|             |            |           | address of the VES1820X is (MSB to LSB) : 0, 0, 0, 1, 0, SADDR[1],                                                                                                                                               |

|             |            |           | SADDR[0].                                                                                                                                                                                                        |

| SDA         | 26         | I/O       | SDA is a bidirectional signal. It is the serial input/output of the I2C                                                                                                                                          |

|             |            | (5V)      | internal block. A pull-up resistor (typically 4.7 k $\Omega$ ) must be connected between SDA and VDD for proper operation (Open Drain output).                                                                   |

| SCL         | 25         | I         | I2C clock input. SCL should nominally be a square wave with a                                                                                                                                                    |

|             |            |           | maximum frequency of 400KHz. SCL is generated by the system I2C master.                                                                                                                                          |

| TEST        | 19         | I         | Test input pin. For normal operation of the VES1820X, TEST must be grounded.                                                                                                                                     |

| TRST        | 35         | I         | Test ReSeT. This active low input signal is used to reset the TAP                                                                                                                                                |

|             |            |           | controller when in boundary scan mode. In normal mode of operation                                                                                                                                               |

|             |            |           | TRST must be set low.                                                                                                                                                                                            |

| TDO         | 37         | O<br>(5V) | Test Data Out. This is the serial Test output pin used in boundary scan mode. Serial Data are provided on the falling edge of TCK.                                                                               |

| TCK         | 33         | I         | Test ClocK : an independant clock used to drive the TAP controller                                                                                                                                               |

|             |            |           | when in boundary scan mode. In normal mode of operation, TCK                                                                                                                                                     |

|             |            |           | must be grounded.                                                                                                                                                                                                |

| TDI         | 34         | I         | Test Data In. The serial input for Test data and instruction when in                                                                                                                                             |

|             |            |           | boundary scan mode. In normal mode of operation, TDI must be set to GND.                                                                                                                                         |

| TMS         | 36         |           | Test Mode Select. This input signal provides the logic levels needed<br>to change the TAP controller from state to state. In normal mode of<br>operation, TMS must be set to VDD.                                |

| CTRL1       | 31         | I/O       | CTRL1 is equivalent to SDA I/O of VES1820X but can be tri-stated                                                                                                                                                 |

|             |            | (5V)      | by I2C programmation. It is actually the output of a switch controlled                                                                                                                                           |

|             |            |           | by parameter BYPIIC of register TEST (index 0F <sub>16</sub> ). CTRL1 is open                                                                                                                                    |

|             |            |           | drain output, and therefore requires an external pull up resistor.                                                                                                                                               |

| CTRL2       | 32         | 0         | CTRL2 can be configured to be a control line output or to output SCL                                                                                                                                             |

|             |            | (5V)      | input. This is controlled by parameter BYPIIC of register TEST (index                                                                                                                                            |

|             |            |           | $OF_{16}$ ). CTRL2 is an open drain output and therefore requires an                                                                                                                                             |

|             |            |           | external pull up resistor.                                                                                                                                                                                       |

| IT          | 38         | 0         | InTerrupt line. This active low output interrupt line can be configured                                                                                                                                          |

|             |            | (5V)      | by the I2C interface. See registers ITsel (index $32_{16}$ ) and ITstat                                                                                                                                          |

|             |            |           | (index 33 <sub>16</sub> ). IT is an open drain output and therefore requires an                                                                                                                                  |

|             | 00         | 0         | external pull up resistor.                                                                                                                                                                                       |

| FEL         | 39         | 0         | By default FEL is a front-end lock indicator. In this case FEL is an                                                                                                                                             |

|             |            | (5V)      | open drain output and therefore requires an external pull up resistor.                                                                                                                                           |

|             |            |           | But FEL can also be configured to output a PWM signal, which value                                                                                                                                               |

|             |            |           | can be programmed through the I2C interface (see register PWMREF, index $34_{16}$ ).                                                                                                                             |

| VIP         | 92         | 1         | Positive input to the A/D converter. This pin is DC biased to half-                                                                                                                                              |

| VII         | 52         |           | supply through an internal resistor divider (2 x $10k\Omega$ resistors). In                                                                                                                                      |

|             |            |           | order to remain in the range of the ADC, the voltage difference                                                                                                                                                  |

|             |            |           | between pins VIP and VIM should be between -0.5 and 0.5 volts.                                                                                                                                                   |

| VIM         | 91         |           | Negative input to the A/D converter. This pin is DC biased to half-                                                                                                                                              |

|             |            |           | supply through an internal resistor divider (2 x $10k\Omega$ resistors). In                                                                                                                                      |

|             |            |           | order to remain in the range of the ADC, the voltage difference                                                                                                                                                  |

|             |            |           | between pins VIP and VIM should be between -0.5 and 0.5 volts.                                                                                                                                                   |

|             |            |           |                                                                                                                                                                                                                  |

# VES1820X

| SYMBOL | PIN NUMBER | TYPE |  |

|--------|------------|------|--|

| CMCAP  | 85         |      |  |

| OTMODE |     |   |                                                                                                                                                                                                                                                                                                                |

|--------|-----|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

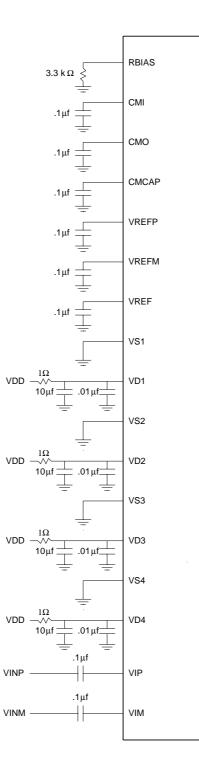

| CMCAP  | 85  | I | This pin is connected to a tap point on an internal resistor divider used to create CMO and CMI. An external capacitor of value $0.1 \mu f$ should be connected between this point and ground to provide good power supply rejection from the positive supply at higher frequencies.                           |

| RBIAS  | 82  | I | An external resistor of value $3.3k\Omega$ should be connected between<br>this pin and ground to provide good accurate bias currents for the<br>analog circuits on the ADC.                                                                                                                                    |

| VREF   | 88  | 0 | This is the output of an on-chip resistor divider. An external capacitor of value $0.1\mu f$ should be connected between this point and ground to provide good power supply rejection from the positive supply at higher frequencies. Reference voltages VREFP and VREFM are derived from the voltage on VREF. |

| VREFP  | 87  | 0 | This is a positive voltage reference for the A/D converter. It is derived from the voltage on pin VREF through an on-chip fully-differential amplifier. The voltage on this pin is nominally equal to CMO + 0.25 volts.                                                                                        |

| VREFM  | 86  | 0 | This is the negative voltage reference for the A/D converter. It is derived from the voltage on pin VREF through an on-chip fully-<br>differential amplifier. The voltage on this pin is nominally equal to CMO- 0.25 volts.                                                                                   |

| СМО    | 84  | 0 | This pin provides the common-mode out voltage for the analog circuits on the ADC. It is the buffered version of a voltage derived from an on-chip resistor devider, and has a nominal value of 0.5 x VD3.                                                                                                      |

| CMI    | 83  | 0 | This pin provides the common-mode in voltage for the analog circuits<br>on the ADC. It is the buffered version of a voltage derived from an<br>on-chip resistor devider, and has a nominal value of 0.75 x VD3.                                                                                                |

| VD1    | 81  |   | Power supply input for the digital switching circuitry (3.3 typ).                                                                                                                                                                                                                                              |

| VS1    | 80  |   | Ground return for the digital switching circuitry.                                                                                                                                                                                                                                                             |

| VD2    | 94  | I | Power supply input for the analog clock drivers (3.3V typ).                                                                                                                                                                                                                                                    |

| VS2    | 93  | I | Ground return for the analog clock drivers.                                                                                                                                                                                                                                                                    |

| VD3    | 89  | I | Power supply input for the analog circuits (3.3V typ).                                                                                                                                                                                                                                                         |

| VS3    | 90  |   | Ground return for analog circuits.                                                                                                                                                                                                                                                                             |

| VD4    | 95  |   | Power supply input that connects to an n-well guard ring that surrounds the ADC (3.3V typ).                                                                                                                                                                                                                    |

| DVCC   | 96  |   | 3.3V supply for the digital section of the PLL.                                                                                                                                                                                                                                                                |

| DGND   | 97  | I | Ground connection for the digital section of the PLL.                                                                                                                                                                                                                                                          |

| PLLGND | 98  | I | Ground connection for the analog section of the PLL.                                                                                                                                                                                                                                                           |

| PLLVCC | 99  | I | 3.3V supply for the analog section of the PLL.                                                                                                                                                                                                                                                                 |

|        | 100 |   |                                                                                                                                                                                                                                                                                                                |

DESCRIPTION

**Philips Semiconductors**

PPLUS

100

I

# **VES1820X**

P-well bias for the analog section of the PLL. Must be tied to 0V.

## **VES1820X**

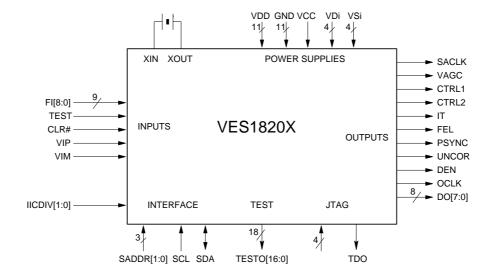

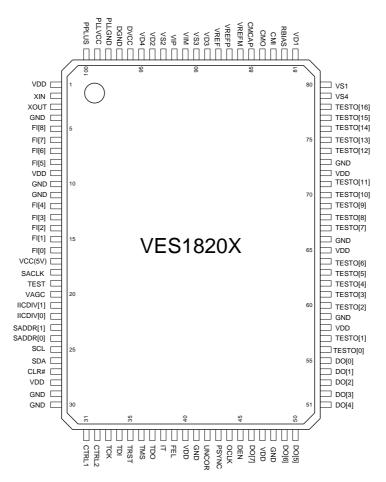

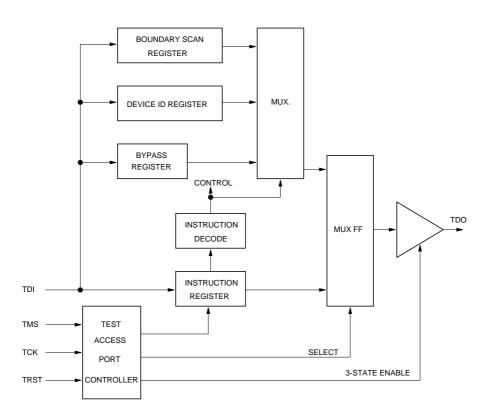

### FIGURE 2 : BLOCK DIAGRAM

## FIGURE 3 : PIN DIAGRAM

# VES1820X

## **TABLE 3 : PIN DESCRIPTION**

| Pin                        | Pin Name                                       | Direction |

|----------------------------|------------------------------------------------|-----------|

| 1                          | VDD                                            | -         |

| 2                          | XIN                                            | I         |

| 1<br>2<br>3<br>4<br>5<br>6 | XOUT                                           | 0         |

| 4                          | GND                                            | -         |

| 5                          | FI[8]                                          | I         |

| 6                          | FI[7]                                          | I         |

| 7                          | FI[6]                                          | I         |

| 8                          | FI[8]<br>FI[7]<br>FI[6]<br>FI[5]<br>VDD<br>GND | I         |

| 9                          | VDD                                            | -         |

| 10                         | GND                                            | -         |

| 11                         | GND                                            | -         |

| 12<br>13                   | FI[4]<br>FI[3]<br>FI[2]<br>FI[1]<br>FI[0]      | I         |

| 13                         | FI[3]                                          | I         |

| 14                         | FI[2]                                          | I         |

| 15                         | FI[1]                                          | I         |

| 16                         | FI[0]                                          | I         |

| 17                         | VUU                                            | -         |

| 18                         | SACLK<br>TEST                                  | 0         |

| 19                         | TEST                                           | I         |

| 20                         | VAGC                                           | 0         |

| 21                         | IICDIV[1]                                      | I         |

| 22                         | IICDIV[1]                                      | I         |

| 23                         | SADDR[1]                                       | I         |

| 24                         | SADDR[0]                                       | I         |

| 25                         | SCL<br>SDA                                     | I         |

| 26                         | SDA                                            | I/O       |

| 27                         | CLR#                                           | I         |

| 28                         | VDD                                            | -         |

| 29                         | GND                                            | -         |

| 30                         | GND                                            | -         |

| 31                         | CTRL1                                          | I/O       |

| 32                         | CTRL1<br>CTRL2<br>TCK                          | OD        |

| 33                         | TCK                                            | I         |

| Pin | Pin Name                    | Direction                                                                                                     |

|-----|-----------------------------|---------------------------------------------------------------------------------------------------------------|

| 34  | TDI                         | I                                                                                                             |

| 35  | TRST                        | I                                                                                                             |

| 36  | TMS                         | I                                                                                                             |

| 37  | TDO                         | OD                                                                                                            |

| 38  | IT                          | OD                                                                                                            |

| 39  | FEL                         | OD                                                                                                            |

| 40  | VDD                         | -                                                                                                             |

| 41  | GND                         | -                                                                                                             |

| 42  | UNCOR                       | 0                                                                                                             |

| 43  | PSYNC                       | 0                                                                                                             |

| 44  | OCLK                        | 0                                                                                                             |

| 45  | DEN<br>DO[7]                | 0                                                                                                             |

| 46  | DO[7]                       | 0                                                                                                             |

| 47  | VDD                         | -                                                                                                             |

| 48  | GND                         | -                                                                                                             |

| 49  | DO[6]                       | 0                                                                                                             |

| 50  | DO[5]                       | 0                                                                                                             |

| 51  | DO[4]                       | 0                                                                                                             |

| 52  | DO[3]                       | 0                                                                                                             |

| 53  | DO[2]                       | 0                                                                                                             |

| 54  | DO[1]                       | 0                                                                                                             |

| 55  | DO[0]                       | 0                                                                                                             |

| 56  | TESTO[0]                    | 0                                                                                                             |

| 57  | TESTO[1]                    | 0                                                                                                             |

| 58  | VDD                         | -                                                                                                             |

| 59  | GND                         | -                                                                                                             |

| 60  | TESTO[2]                    | 0                                                                                                             |

| 61  | TESTO[3]                    | 0                                                                                                             |

| 62  | TESTO[4]                    | 0                                                                                                             |

| 63  | TESTO[5]                    | 0                                                                                                             |

| 64  | TESTO[5]<br>TESTO[6]<br>VDD | OD<br>OD<br>OD<br>-<br>-<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |

| 65  | VDD                         | -                                                                                                             |

| 66  | GND                         | -                                                                                                             |

| Pin | Pin Name  | Direction        |

|-----|-----------|------------------|

| 67  | TESTO[7]  | 0                |

| 68  | TESTO[8]  | 0                |

| 69  | TESTO[9]  | 0                |

| 70  | TESTO[10] | 0                |

| 71  | TESTO[11] | 0<br>0<br>0<br>0 |

| 72  | VDD       | -                |

| 73  | GND       | -                |

| 74  | TESTO[12] | -<br>0           |

| 75  | TESTO[13] | 0                |

| 76  | TESTO[14] | 0                |

| 77  | TESTO[15] | 0                |

| 78  | TESTO[16] | 0                |

| 79  | VS4       | -                |

| 80  | VS1       | -                |

| 81  | VD1       | -                |

| 82  | RBIAS     | I                |

| 83  | CMI       | 0                |

| 84  | CMO       | 0                |

| 85  | CMCAP     | <br> <br>        |

| 86  | VREFM     | 0                |

| 87  | VREFP     | 0<br>0           |

| 88  | VREF      | 0                |

| 89  | VD3       | -                |

| 90  | VS3       | -                |

| 91  | VIM       | I                |

| 92  | VIP       |                  |

| 93  | VS2       | -                |

| 94  | VD2       | -                |

| 95  | VD4       | -                |

| 96  | DVCC      | -                |

| 97  | DGND      | -                |

| 98  | PLLGND    | -                |

| 99  | PLLVCC    | -                |

| 100 | PPLUS     | -                |

Notes :

1.All inputs (I) are TTL, 5V tolerant inputs

2.OD are Open Drain 5V outputs, so they must be connected to a pull-up resistor to either VDD or VCC

# VES1820X

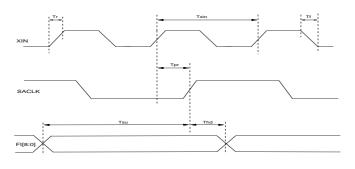

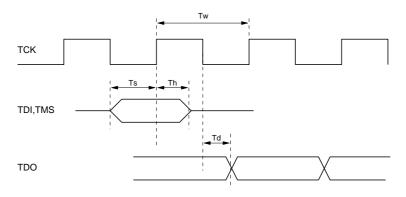

## **FIGURE 4 : INPUT TIMING**

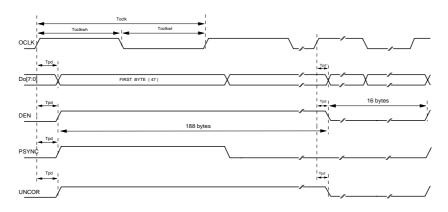

## FIGURE 5 : OUTPUT TIMING

## **TABLE 4 : TIMING CHARACTERISTICS**

| Symbol  | Parameter                                                          | Min | Max | Unit | Notes              |

|---------|--------------------------------------------------------------------|-----|-----|------|--------------------|

| Txin    | XIN period                                                         | 14  |     | nS   |                    |

| Tr      | Rising edge                                                        |     | 2   | nS   |                    |

| Tf      | Falling edge                                                       |     | 2   | nS   |                    |

| Tsu     | Set-up time to SACLK rising                                        | 3   |     | nS   |                    |

| Thd     | Hold time to SACLK rising                                          | 0   |     | nS   |                    |

| Tpr     | Propagation delay from rising edge of XIN                          | 3   | 8   | nS   |                    |

| Toclk   | OCLK period                                                        | 112 |     | nS   | Parallel interface |

|         |                                                                    | 14  |     | nS   | Serial interface   |

| Toclkwh | OCLK clock high                                                    | 56  |     | nS   | Parallel interface |

|         |                                                                    | 7   |     | nS   | Serial interface   |

| Toclkwl | OCLK clock low                                                     | 56  |     | nS   | Parallel interface |

|         |                                                                    | 7   |     | nS   | Serial interface   |

| Tsus    | Set-up time to OCLK falling                                        | 6   |     | nS   | Serial interface   |

| Thds    | Hold time to OCLK falling                                          | 6   |     | nS   | Serial interface   |

| Tpd     | Propagation delay from rising edge of OCLK (DO, DEN, PSYNC, UNCOR) | 1   |     | nS   | CL = 20 pF         |

# VES1820X

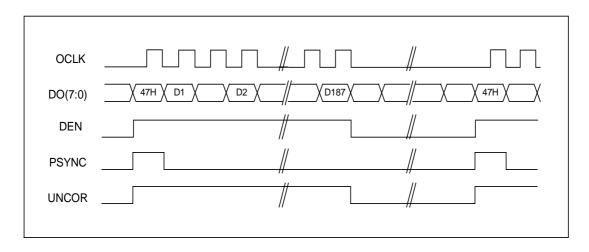

## FIGURE 6 : PARALLEL OUTPUT INTERFACE MODE A

- Notes : OCLK is a jittered clock which average frequency is N\*SymbolRate/8, where N is the spectral efficiency of the modulation. The polarity of OCLK is programmable.

- DEN is active high (if PDEN=0) only during the 188 bytes of a packet

- PSYNC is active high (if PPSYNC=0) only during the sync byte (47H)

### FIGURE 7 : PARALLEL OUTPUT INTERFACE MODE B

- Notes : OCLK is a division of the sampling clock by a programmable factor from 1 to 16. So it is a regular clock which frequency must be greater than N\*SymbolRate/8, where N is the spectral efficiency of the modulation. The polarity of OCLK is programmable.

- DEN is active high (if PDEN=0) only during the valid bytes

- PSYNC is active high (if PPSYNC=0) only during the sync byte (47H)

# **VES1820X**

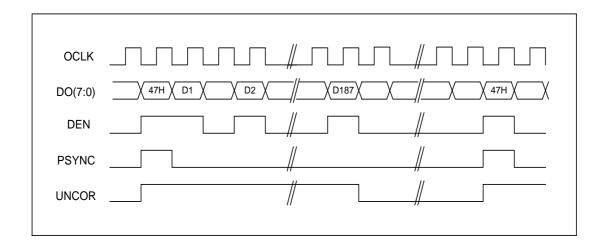

## **FIGURE 8 : SERIAL OUTPUT INTERFACE**

- OCLK is a jittered clock with average frequency N\*SymbolRate, where N is the spectral efficiency Notes : of the modulation. The polarity of OCLK is programmable.

DEN is active high (if PDEN=0) only during the 1504 bits of a packet

PSYNC is active high (if PPSYNC=0) only during the first bit of the sync byte (47H)

- The serialization of the output bytes can be either MSB first or LSB first

# **VES1820X**

### **TYPICAL APPLICATION**

## FIGURE 9 : FRONT END RECEIVER SCHEMATIC

### FIGURE 10 : XTAL OSCILLATOR

Notes : - Typical XTAL is on fundamental frequency - Values of passive components are dependant on XTAL manufacturer.

# **VES1820X**

## FIGURE 11 : EXTERNAL AGC CIRCUITRY (SELAGC = 0)

Notes : R and C are chosen to verify RS/1024 < Fc <<< XIN/16 with R = 1.5 k• and C = 1nF, Fc#100KHz.

## FIGURE 12 : EXTERNAL CIRCUITRY (SELAGC = 1)

# **VES1820X**

## FIGURE 13 : ADC EXTERNAL CONNECTIONS

## **MICROCONTROLLER SERIAL INTERFACE**

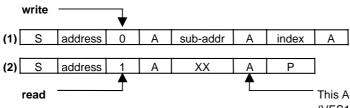

#### • I<sup>2</sup>C REGISTERS : WRITE MODE

• I<sup>2</sup>C REGISTERS : READ MODE

In this mode of operation you must first (1) write the index value of the register you will then read (2)

This Acknowledge bit is provided by the receiver (VES1820X is transmitting !)

Notes : at the end of line (1) there is no stop bit ! Line (2) can start just after the last ackowledge bit of line

# **VES1820X**

### TABLE 5 : MICROCONTROLLER INTERFACE REGISTERS

| CONF         00         STDBY         IFS         INVIO         QAM(2)         QAM(1)         QAM(1)         QAM(1)         QAM(1)         QAM(1)         QAG(1)         AGCR(1)         AGCR(1)         AGCR(1)         AGCR(1)         AGCR(1)         AGCR(1)         AGCR(1)         AGCR(1)         AGCR(1)         CLK C(1)         CLK C(2)         CLK C(1)         CLK C(2)         CLK C(1)         CLK C(2)         CLK C(1)         CLK C(1)         CLK C(2)         CLK C(1)         CLK C(2)         CLK C(1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PARAMETER | INDEX<br>HEXA | 7(MSB)    | 6         | 5         | 4         | 3         | 2         | 1         | 0(LSB)    | R/W    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--------|

| AGCCONF         02         FELPVM         ADCSEL         0         1         SELAGC         PVMAL         KAGC[1]         KAGC[1]         CAGCONF           CARCONF         04         0         CAR.P[1]         CAR.P[1]         CAR.P[1]         CAR.P[1]         CAR.C[1]         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CONF      | 00            | STDBY     | IFS       | INVIQ     | QAM[2]    | QAM[1]    | QAM[0]    | TRI       | CLB       | R/W    |

| CLKCONF         03         NDEC(1)         NDEC(1)         GAIN2         GAIN3         DYN         CLK_C(2)         CLK_C(1)         CLK_C(1)           CARCONF         04         0         CAR_P[2]         CAR_P[1)         CAR_P[1)         CAR_C[2]         CAR_C[2]         CAR_C[1]         CAR_C[2]         CAR_C[2]         CAR_C[1]         CAR_C[2]         CAR_C[1]         CAR_C[1] </td <td>AGCREF</td> <td>01</td> <td>AGCR[7]</td> <td>AGCR[6]</td> <td>AGCR[5]</td> <td>AGCR[4]</td> <td>AGCR[3]</td> <td>AGCR[2]</td> <td>AGCR[1]</td> <td>AGCR[0]</td> <td>R/W</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | AGCREF    | 01            | AGCR[7]   | AGCR[6]   | AGCR[5]   | AGCR[4]   | AGCR[3]   | AGCR[2]   | AGCR[1]   | AGCR[0]   | R/W    |

| CARCONF         04         0         CAR_P[2]         CAR_P[1]         CAR_P[0]         CAR_C[3]         CAR_C[2]         CAR_C[1]         CAR_C[0]           LOCKHR         05         LTHR[7]         LTHR[8]         LTHR[8]         LTHR[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | AGCCONF   | 02            | FELPWM    | ADCSEL    | 0         | 1         | SELAGC    | PWMA      | KAGC[1]   | KAGC[0]   | R/W    |

| LOCKTHR         05         LTHR[7]         LTHR[8]         LTHR[1]         PREQUAL         DFE           EQCONF1         06         POSI[2]         POSI[1]         POSI[2]         EQST2[2]         EQST2[0]         EQST2[1]         EQST2[1]         EQST2[2]         EQST2[1]         EQST2[2]         EQST2[1]         EQST2[1]         EQST1[2]         MSETH[1]         MSETH[2]         MSETH[2]         MSETH[1]         MSETH[2]         MSETH[2]         MSETH[1]         MSETH[2]         MSETH[1]         MSETH[2]         MSETH[1]         MSETH[2]         MSETH[1]         MSETH[2]         MSETH[2]         MSETH[1]         MSETH[2]         MSET[2]         MSET[2]         MSET[2]         MSET[2]         MSET[2]         MSET[2]         MSET[2]         MSET[2]         MSET[2] <td>CLKCONF</td> <td>03</td> <td>NDEC[1]</td> <td>NDEC[0]</td> <td>GAIN2</td> <td>GAIN3</td> <td>DYN</td> <td>CLK_C[2]</td> <td>CLK_C[1]</td> <td>CLK_C[0]</td> <td>R/W</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CLKCONF   | 03            | NDEC[1]   | NDEC[0]   | GAIN2     | GAIN3     | DYN       | CLK_C[2]  | CLK_C[1]  | CLK_C[0]  | R/W    |

| EQCONF1         06         POSI[2]         POSI[1]         POSI[0]         VALI         ENADAPT         ENEQUAL         DFE           EQSTEP         07         EQST[2]         MSETH[6]         MSETH[6]         MSETH[6]         MSETH[6]         MSETH[6]         MSETH[6]         MSETH[6]         MSETH[2]         AREF[2]         AREF[2]         AREF[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CARCONF   | 04            |           | CAR_P[2]  | CAR_P[1]  | CAR_P[0]  | CAR_C[3]  | CAR_C[2]  | CAR_C[1]  | CAR_C[0]  | R/W    |

| EQSTEP         07         EQST2[2]         EQST2[1]         EQST2[1]         EQST1[2]         EQST1[1]         EQST1[2]         EQST1[1]         EQS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LOCKTHR   | 05            | LTHR[7]   | LTHR[6]   | LTHR[5]   |           | LTHR[3]   | LTHR[2]   | LTHR[1]   | LTHR[0]   | R/W    |

| MSETH         08         MSETH[7]         MSETH[6]         MSETH[4]         MSETH[4]         MSETH[2]         MSETH[1]         AREF[2]         AREF[1]         BER         BDR1         BDR10         BDR10         BDR10         BDR16         BDR17         BDR16         BDR10         BDR10         BDR11         BDR10         BDR11         BDR10         BDR10         BDR10         BDR10         BDR10         BDR10         BDR10         BDR10         BDR10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | EQCONF1   | 06            |           | POSI[2]   | POSI[1]   |           | VALI      | ENADAPT   | ENEQUAL   | DFE       | R/W    |

| AREF         09         AREF[7]         AREF[6]         AREF[5]         AREF[4]         AREF[3]         AREF[2]         AREF[1]         BDR1         BDR1         BDR2         BDR1         BDR2         BDR1         BDR1         BDR3         BDR1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EQSTEP    | 07            |           |           | EQST2[2]  | EQST2[1]  | EQST2[0]  | EQST1[2]  | EQST1[1]  | EQST1[0]  | R/W    |

| BDR_LSB         0A         BDR7         BDR(6)         BDR5         BDR4         BDR3         BDR3         BDR2         BDR1         BDR0           BDR_MD         0B         BDR15         BDR14         BDR13         BDR12         BDR11         BDR10         BDR3         BDR17         BDR16           BDR_MSB         0C         BDR17         BDR16         BDR21         BDR20         BDR13         BDR13         BDR17         BDR16           BDR         0D         BDR17         BDR16         BDR17         BDR17         BDR16         BDR17         BDR14         BDR17         BDR17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MSETH     | 08            | MSETH[7]  | MSETH[6]  | MSETH[5]  |           | MSETH[3]  |           | MSETH[1]  |           | R/W    |

| BDR_MID         08         BDR15         BDR14         BDR13         BDR12         BDR11         BDR10         BDR30         BDR30           BDR_MNS         0C         BDR16         BDR21         BDR20         BDR19         BDR18         BDR17         BDR16           BDR_INV         0D         BDR17         BDR16         BDR15         BDR14         BDR13         BDR12         BDR11         BDR16           GAIN         0E         GNYQ[2]         GNYQ[1]         GNYQ[0]         SFL         GLPF[1]         GLPF[1]         GLPF[1]         GLPF[1]         GLPF[1]         GLPT[1]         SSAT[1]         SSAT[1]           SYNC         11         NODVB         BER[1]         BER[0]         FEL         FSYNC         CARLOCK         EQ.ALGO           POLA         12         1         POINT         P/MF         PFEL         PPSYNC         CARLOCK         EQ.ALGO           CPT_UNCOR         13         CPTU[6]         CPTU[6]         CPTU[4]         CPTU[3]         CPTU[2]         CPTU[0]         BER[13]         BER[13]         BER[13]         BER[13]         BER[13]         BER[14]         BER[13]         BER[13]         BER[14]         BER[14]         BER[13]         BER[13]         B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |               |           |           | AREF[5]   | AREF[4]   | AREF[3]   | AREF[2]   | AREF[1]   | AREF[0]   | R/W    |

| BDR_MSB         0C         BDR16         BDR21         BDR20         BDR19         BDR18         BDR17         BDR16           BDR_JNV         0D         BDR17         BDR16         BDR15         BDR14         BDR13         BDR12         BDR111         BDR10           GAIN         0E         GNYQ[2]         GNYQ[1]         GNYQ[0]         SFIL         GLPF[1]         GLPF[0]         SSAT[1]         SSAT[0]           TEST         0F         BYPIC         CTRL2         0         SELOUT[1]         SELOUT[0]         0         0         0         0           RSCONF         10         PVBER[1]         PVBER[0]         CLB_UNC         C[1]         C[0]         RSI         DESCI         IEI           SYNC         11         NODVB         BER[1]         BER[0]         FEL         FSYNC         CALGOK         EQ.LGO           POLA         12         1         POINT         P/MF         PFEL         PSYNC         PUNCOR         PDEN         POCLK           CPT_UROR         13         CPTU[6]         CPTU[4]         CPTU[4]         CPTU[4]         CPTU[3]         BER[10]         BER[10]         BER[10]         BER[11]         BER[11]         BER[13]         BE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |               |           |           |           |           |           |           |           |           | R/W    |

| BDR_INV         0D         BDR17         BDR16         BDR15         BDR14         BDR13         BDR12         BDR111         BDR10           GAIN         0E         GNYQ[2]         GNYQ[1]         GNYQ[0]         SFIL         GLPF[1]         GLPF[0]         SSAT[1]         SSAT[0]           TEST         0F         BYPIIC         CTRL2         0         SELOUT[1]         SELOUT[0]         0         0         0         0           RSCONF         10         PVBER[1]         PVBER[0]         CLB_UNC         C[1]         C[0]         RSI         DESCI         IEI           SYNC         11         NODVB         BER[1]         BER[0]         FEL         FSYNC         CARLOCK         EQ_ALGO           POLA         12         1         POINT         P/MF         PFEL         PSYNC         PUNCOR         PDEN         POCLK           CPT_UNCOR         13         CPTU[6]         CPTU[5]         CPTU[4]         CPTU[2]         CPTU[1]         BER[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _         |               | BDR15     | BDR14     |           |           |           |           |           |           | R/W    |

| GAIN         0E         GNYQ[2]         GNYQ[1]         GNYQ[0]         SFIL         GLPF[1]         GLPF[0]         SSAT[1]         SSAT[0]           TEST         0F         BYPIIC         CTRL2         0         SELOUT[1]         SELOUT[0]         0         0         0           RSCONF         10         PVBER[1]         PVBER[0]         CLB_UNC         C[1]         C[0]         RSI         DESCI         IEI           SYNC         11         NODVB         BER[1]         BER[0]         FEL         FSYNC         CALOCK         EQ_ALGO           POLA         12         1         POINT         P/MF         PFEL         PPSYNC         PULCOR         PDEN         POCLK           CPT_UNCOR         13         CPTU[6]         CPTU[5]         CPTU[4]         CPTU[3]         CPTU[2]         CPTU[1]         CPTU[0]           BER_LSB         14         BER[7]         BER[6]         BER[5]         BER[1]         BER[1] <td< td=""><td>_</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>R/W</td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _         |               |           |           |           |           |           |           |           |           | R/W    |

| TEST         OF         BYPIC         CTRL2         0         SELOUT[1]         SELOUT[0]         0         0         0           RSCONF         10         PVBER[1]         PVBER[0]         CLB_UNC         C[1]         C[0]         RSI         DESCI         IEI           SYNC         11         NODVB         BER[1]         BER[0]         FEL         FSYNC         CARLOCK         EQ_ALGO           POLA         12         1         POINT         P/MF         PFEL         PPSYNC         CARLOCK         EQ_ALGO           CPT_UNCOR         13         CPTU[6]         CPTU[4]         CPTU[3]         CPTU[2]         CPTU[1]         CPTU[0]           BER_LSB         14         BER[7]         BER[6]         BER[5]         BER[1]         BER[1]         BER[0]         BER[9]         BER[9]         BER[9]         BER[9]         BER[9]         BER[9]         BER[9]         BER[9]         BER[9]         BER[1]         BER[1]         BER[1]         BER[1]         BER[1]         BER[9]         BER[9]         MSE[1]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |               |           |           |           |           |           |           |           |           | R/W    |