Preliminary

VN16117

**Fibre Channel Transceiver**

# Applications

- 1062.5 MBd Fibre Channel Interface.

- High Speed Proprietary Interface

- FC Interface for Disk Drives and Arrays

- Mass storage system I/O Channel

- Work station server I/O

- High-speed backplane interface

# **General Description**

The VN16117 Fibre Channel 1062.5 MBd transceiver is a CMOS single-chip integrated circuit, in an LQFP package. It provides a low-power, low-cost physical layer interface solution for 1062.5MBd Fibre Channel or proprietary links, as specified by the ANSI X3.230-1994 standard. An internal loopback function is provided for system debugging.

The VN16117 is used in Fibre Channel applications to build cost effective, high-speed interfaces utilizing minimal space and power.

The transmitter accepts 10-bit-wide 8b/10b encoded data and converts it into a high-speed serial data stream. It transmits this converted data through a Pseudo Emitter Coupled Logic (PECL) driver, synchronized with a 106.25 MHz reference clock. The receiver accepts the PECL serial data stream at 1062.5 MBd and converts it to the original 10-bit wide parallel data format. Two 53.125 MHz clocks, which are 180 degrees out-of-phase, are also recovered. The parallel data is aligned with the rising edge of alternating clocks.

# Features

- ANSI X3.230-1994 Fibre Channel Compliant.

- Supports Full Speed (1062.5 MBd) **Fibre Channel**

- Fully-integrated CMOS Single IC

- Low Power Consumption

- 5-Volt Tolerant Inputs

- ESD rating >2000V (Human Body Model) or >200V (Machine Model)

- Pin-compatible with Agilent HDMP-1536A/46A or HDMP-1636A/46A and Vitesse VSC7123/25 transceivers. (See Appendix A)

- Available in both 10 mm x 10 mm and 14 mm x 14 mm LQFP Packages

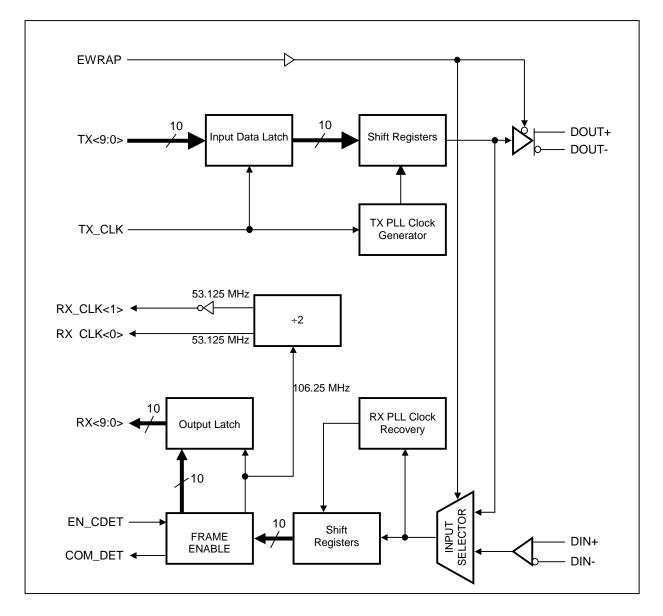

#### Table 1. Pin Description Pin # Description Name Type GND ESD 1.14 Power Power and ground pairs for pad ESD structure. VCC\_ESD 5, 10 2 TTL Input 10-bit parallel data input pins. This data should be 10b/8b TX<0> encoded. The least significant bit is TX<0> and is transmitted first. TX<1> 3 TX<2> 4 TX<3> 6 7 TX<4> 8 TX<5> TX<6> 9 TX<7> 11 TX<8> 12 TX<9> 13 15 GND\_TXA Power Power and ground pair for TX PLL analog circuits. VCC\_TXA 18 These pins are bonded to isolated pads and have no connection to NC 16, 17, No Connect internal circuits. 27, 48, 49 Wrap Enable. This pin is active HIGH. When asserted, the high-EWRAP 19 TTL Input speed serial data are internally wrapped from the transmitter serial data output back to the receiver data input. Also, when asserted, DOUT $\pm$ are held static at logic 1. When deasserted, DOUT $\pm$ and DIN± are active. VCC\_TXD 20 Power Power and ground pair for TX digital circuits. GND\_TXD 21 TX\_CLK 22 Reference clock and transmit byte clock. This is a 106.25 MHz TTL Input system clock supplied by the host system. On the positive edge of the clock, the input data, TX<9:0>, are latched into the register. This clock is multiplied by 10 internally, to generate the transmit serial bit clock. VCC RXD 23 28, Power Power and ground pair for digital circuits in the receiver portion. GND\_RXD 25 EN CDET 24 TTL Input Comma Detect Enable. This pin is active HIGH. When asserted, the internal byte alignment function is turned on, to allow the clock to synchronize with the comma character (0011111XXX). When de-asserted, the function is disabled and will not align the clock and data. In this mode COM\_DET is set to LOW. SIG\_DET 26 TTL Signal Detect. This pin is active HIGH. It indicates the loss of input Output signal on the high-speed serial inputs, DIN±. SIG\_DET is set to LOW when differential inputs are less than 50 mV. VCC\_RX 29 Power Power and ground pair for the clock signal of the receiver portion. GND\_RX 32 RX CLK<1> 30 TTL Receiver Byte Clocks. Two 180 degrees out-of-phase 53.125 MHz Output clock signals that are recovered by the receiver section. The RX\_CLK<0> 31 received bytes are alternately clocked by the rising edges of these signals. The rising edge of RX\_CLK<1> aligns with a comma character when detected.

## Table1. (Continued)

| Name       | Pin#   | Туре          | Description                                                                                                                                                  |

|------------|--------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND_RXT    | 33 46, | Power         | Power and ground pairs for ESD structure.                                                                                                                    |

| VCC_RXT    | 37, 42 |               |                                                                                                                                                              |

| RX<9>      | 34     | TTL           | Received Parallel Data Output. RX<0> is the least significant bit                                                                                            |

| RX<8>      | 35     | Output        | and is received first. When DIN± lose input data, all RX pins will                                                                                           |

| RX<7>      | 36     |               | be held HIGH.                                                                                                                                                |

| RX<6>      | 38     |               |                                                                                                                                                              |

| RX<5>      | 39     |               |                                                                                                                                                              |

| RX<4>      | 40     |               |                                                                                                                                                              |

| RX<3>      | 41     |               |                                                                                                                                                              |

| RX<2>      | 43     |               |                                                                                                                                                              |

| RX<1>      | 44     |               |                                                                                                                                                              |

| RX<0>      | 45     |               |                                                                                                                                                              |

| COM_DET    | 47     | TTL<br>Output | Comma detect. This pin is active HIGH. When asserted, it indicates the detection of comma character (0011111XXX). It is active only when EN_CEDT is enabled. |

| VCC_RXF    | 50     | Power         | Power and ground pair for the front-end of the receiver section.                                                                                             |

| GND_RXF    | 51     |               |                                                                                                                                                              |

| DIN-       | 52     | Input         | High-speed serial data input. Serial data input is received when                                                                                             |

| DIN+       | 54     |               | EWRAP is disabled.                                                                                                                                           |

| VCC_RXESD  | 53,55  | Power         | Power and ground pair for ESD structure.                                                                                                                     |

| GND_RXESD  | 56     |               |                                                                                                                                                              |

| VCC_RXA    | 57, 59 | Power         | Power and ground pair for analog circuits of the receiver section.                                                                                           |

| GND_RXA    | 58     |               |                                                                                                                                                              |

| VCC_TX_ECL | 60     | Power         | Power supply to line driver circuits. Ground supply is from pin 64.                                                                                          |

| DOUT-      | 61     | Output        | High-speed serial data output. These pins are active when                                                                                                    |

| DOUT+      | 62     |               | EWRAP is disabled and are held static at logic 1 when EWRAP is enable.                                                                                       |

| VCC_TX_HS  | 63     | Power         | Power and ground pair for high-speed transmit logic in the                                                                                                   |

| GND_TX_HS  | 64     |               | parallel-to-serial section.                                                                                                                                  |

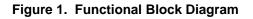

# **Functional Block Description**

#### Input Data Latch

The input data latch block latches the 10-bit TTL input parallel byte, TX<9:0>, on the rising edge of the 125 MHz user-provided TX\_CLK into the holding registers.

#### Parallel-to-Serial Converter

The received 10-bit TTL parallel input byte is converted to serial PECL level data stream by the parallel-toserial block, and is transmitted differentially to the line driver block at 1062.5 MBd. The 8b/10b encoded data is transmitted sequentially with bit 0 being sent first.

#### **Clock Generator**

The 106.25 MHz signal used for clocking the serial outputs is generated by the TX PLL block based on the user-provided TX\_CLK. This clock should have a  $\pm$ 100 ppm tolerance.

#### Internal Loopback

When EWRAP is set to a logic HIGH, the serial data stream generated by the transmitter is looped back to the receiver path instead of going out to the DOUT $\pm$  pins. When in loopback mode, a static logic 1 is transmitted at the line driver (DOUT+ is HIGH and DOUT- is LOW).

#### Signal Detect

Signal detect block is used to sense the serial input data stream at pins DIN $\pm$ . If the serial input is lower than 50 mV differentially, this block deasserts SIG\_DET and sets the output, RX<9:0>, to all logic ones. When the serial input at pins DIN $\pm$  is greater than 50 mV, the signal is directed to the receive path.

#### Equalizer and Slicer

The signal received from the line (DIN± pins) is distorted by the cable bandwidth. In order to maintain a low bit-error rate, an equalizer is used to compensate for the signal loss. The slicer recovers the differential low-level signal to a CMOS-level single-ended signal for clock recovery and data re-timing.

#### **Clock Recovery**

The serial input data stream contains both data and clock. The clock recovery block is used to extract both data and clocks from this input. In addition to data, two clocks of 53.125 MHz are recovered.

### **Table 2. Absolute Maximum Ratings**

$T_A = 25^{\circ}C$  except as specified.

| Symbol                | Parameter                      | Min. | Max.      | Units |

|-----------------------|--------------------------------|------|-----------|-------|

| V <sub>cc</sub>       | Supply voltage                 | -0.5 | 5.0       | V     |

| V <sub>IN,TTL</sub>   | TTL Input Voltage              | -0.7 | Vcc + 2.8 | V     |

| V <sub>IN,HS_IN</sub> | HS_IN Input Voltage            | 2.0  | Vcc       | V     |

| I <sub>O,TTL</sub>    | TTL Output Source Current      |      | 13        | mA    |

| T <sub>stg</sub>      | Storage Temperature            | -65  | +150      | °C    |

| Tj                    | Junction Operating Temperature | 0    | +150      | °C    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress specifications only and correct functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

#### Table 3. Guaranteed Operating Rates

$T_A = 0^{\circ}C$  to +70°C,  $V_{cc} = 3.15$  V to 3.45 V

| Parallel Cloc | k Rate (MHz) | Serial Baud F | Rate (Mbaud) |

|---------------|--------------|---------------|--------------|

| Min. Max.     |              | Min.          | Max.         |

| 106.20        | 106.30       | 1062.0        | 1063.0       |

#### **Table 4. AC Electrical Characteristics**

| Symbol                                | Parameter                                          | Min. | Тур. | Max. | Unit |

|---------------------------------------|----------------------------------------------------|------|------|------|------|

| t <sub>r,REFCLK</sub>                 | REFCLK Rise Time, 0.8 to 2.0 Volts                 |      |      | 2.4  | nsec |

| t <sub>f,REFCLK</sub>                 | REFCLK Fall Time, 2.0 to 0.8 Volts                 |      |      | 2.4  | nsec |

| t <sub>r,TTLin</sub>                  | Input TTL Rise Time, 0.8 to 2.0 Volts              |      | 2    |      | nsec |

| t <sub>f,TTLin</sub>                  | Input TTL Fall Time, 2.0 to 0.8 Volts              |      | 2    |      | nsec |

| t <sub>r,TTLout</sub>                 | Output TTL Rise Time, 0.8 to 2.0 Volts, 10 pF Load |      | 1.5  | 2.4  | nsec |

| t <sub>f,TTLout</sub>                 | Output TTL Fall Time, 2.0 to 0.8 Volts, 10 pF Load |      | 1.1  | 2.4  | nsec |

| t <sub>rs,HS_OUT</sub>                | HS_OUT Single-Ended (DOUT+) Rise Time              | 85   | 225  | 327  | psec |

| $t_{\rm fs,HS_OUT}$                   | HS_OUT Single-Ended (DOUT+) Fall Time              | 85   | 200  | 327  | psec |

| t <sub>rd,HS_OUT</sub>                | HS_OUT Differential Rise Time                      | 85   |      | 327  | psec |

| t <sub>fd,HS_OUT</sub>                | HS_OUT Differential Fall Time                      |      |      | 327  | psec |

| VIP,HS_IN                             | HS_IN Input Peak-to-Peak Differential Voltage      | 200  | 1200 | 2000 | mV   |

| V <sub>OP,HS_OUT</sub> <sup>[1]</sup> | HS_OUT Output Peal-to-Peak Differential Voltage    | 1200 | 1600 | 2000 | mV   |

$T_A = 0^{\circ}C$  to +70°C,  $V_{CC} = 3.15$  V to 3.45 V

Note:

1. Output Peak-to-Peak Differential Voltage specified as DOUT+ minus DOUT-

### **Table 5. DC Electrical Characteristics**

| Symbol                               | Parameter                                                                | Min. | Тур. | Max. | Unit |

|--------------------------------------|--------------------------------------------------------------------------|------|------|------|------|

| Vih,ttl                              | TTL Input High Voltage Level, Guaranteed High Signal for All Inputs      | 2    |      | 5.5  | V    |

| Vil,ttl                              | TTL Input Low Voltage Level, Guaranteed Low Signal for All Inputs        | 0    |      | 0.8  | V    |

| V <sub>OH,TTL</sub>                  | TTL Output High Voltage Level, $I_{OH}$ = -400 $\mu A$                   | 2.2  |      | Vcc  | V    |

| V <sub>OL,TTL</sub>                  | TTL Output Low Voltage Level, $I_{OL} = 1 \text{ mA}$                    | 0    |      | 0.6  | V    |

| I <sub>IH,TTL</sub>                  | Input High Current, $V_{IN} = 2.4 \text{ V}$ , $V_{CC} = 3.45 \text{ V}$ |      |      | 40   | μA   |

| I <sub>IL,TTL</sub>                  | Input Low Current, $V_{\text{IN}}$ = 0.4 V, $V_{\text{CC}}$ = 3.45 V     |      |      | -600 | μA   |

| I <sub>CC,TRX</sub> <sup>[1,2]</sup> | Transceiver V <sub>CC</sub> Supply Current, TA = $25^{\circ}$ C          |      | 220  |      | mA   |

$T_{\text{A}}$  = 0°C to +70°C,  $V_{\text{CC}}$  = 3.15 V to 3.45 V

Note:

1. Measurement Conditions: Tested sending 1062.5 MBd PRBS 27-1 sequence from a serial Bit Error Rate Tester (BERT) with DOUT $\pm$  outputs terminated with 150 $\Omega$  resistors to GND.

2. Typical values are at Vcc = 3.3 volts.

#### **Table 6. Transceiver Reference Clock Requirements**

| Symbol           | Parameter                                        | Min.   | Тур.   | Max.   | Unit |

|------------------|--------------------------------------------------|--------|--------|--------|------|

| F                | Nominal Frequency (for Fiber Channel Compliance) | 106.20 | 106.25 | 106.30 | MHz  |

| F <sub>tol</sub> | Frequency Tolerance                              | -100   |        | +100   | ppm  |

| Symm             | Symmetry (Duty Cycle)                            | 40     |        | 60     | %    |

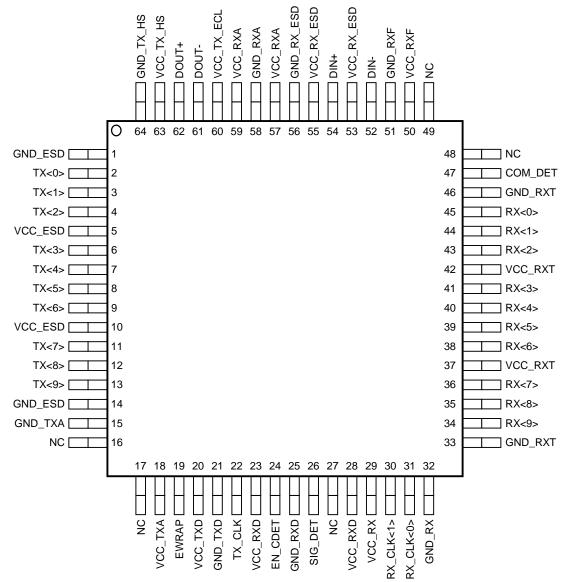

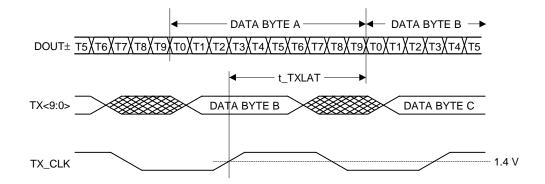

#### Table 7. Transmitter Timing Characteristics

$T_{\text{A}}$  = 0°C to +70°C, Vcc = 3.15 V to 3.45 V

| Symbol                 | Parameter                           | Min. | Тур. | Max. | Unit |

|------------------------|-------------------------------------|------|------|------|------|

| t <sub>setup</sub>     | Setup Time to Rising Edge of REFCLK | 2.0  |      |      | nsec |

| t <sub>hold</sub>      | Hold Time to Rising Edge of REFCLK  | 1.5  |      |      | nsec |

| T_txlat <sup>[1]</sup> | Transmitter Latency                 |      | 3.5  |      | nsec |

|                        |                                     |      | 4.4  |      | bits |

Note:

1. The transmitter latency, as shown in Figure 4, is defined as the time between the latching in of the parallel data word (as triggered by the rising edge of the transmit by clock, REFCLK) and the transmission of the first serial bit of that parallel word (defined by the rising edge of the first bit transmitted).

Figure 3. Transmitter Section Timing.

Figure 4. Transmitter Latency

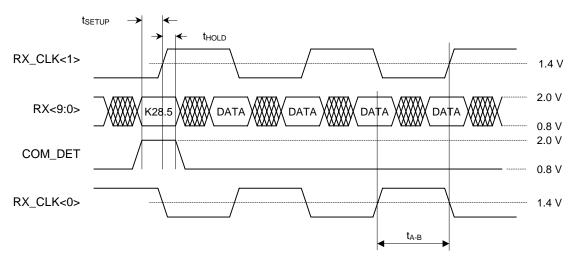

## **Table 8. Receiver Timing Characteristics**

| Symbol                 | Parameter                               | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------|------|------|------|------|

| b_sync <sup>[1]</sup>  | Bit Sync Time                           |      |      | 2500 | bits |

| t <sub>SETUP</sub>     | Data Setup Before Rising Edge of RX_CLK | 3.0  |      |      | nsec |

| t <sub>HOLD</sub>      | Data Hold After Rising Edge of RX_CLK   | 1.5  |      |      | nsec |

| t <sub>DUTY</sub>      | RX_CLK Duty Cycle                       | 40   |      | 60   | %    |

| t <sub>A-B</sub>       | RX_CLK Skew                             | 8.9  | 9.4  | 9.9  | nsec |

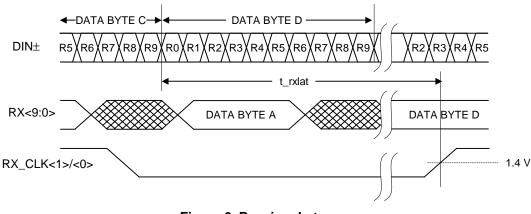

| T_rxlat <sup>[2]</sup> | Receiver Latency                        |      | 24.5 |      | nsec |

|                        |                                         |      | 26.0 |      | bits |

TA = 0°C to +70°C,  $V_{DD}$  = 3.15 V to 3.45 V

Notes:

1. This is the recovery for input phase jumps.

2. The receiver latency as shown inFigure 6, is defined as the time between receiving the first serial bit of a parallel data word (defined as the first edge of the first serial bit) and the clocking out of that parallel word (defined by the rising edge of the receive byte clock, either RBC1 or RBC0).

Figure 5. Receiver Section Timing

Figure 6. Receiver Latency

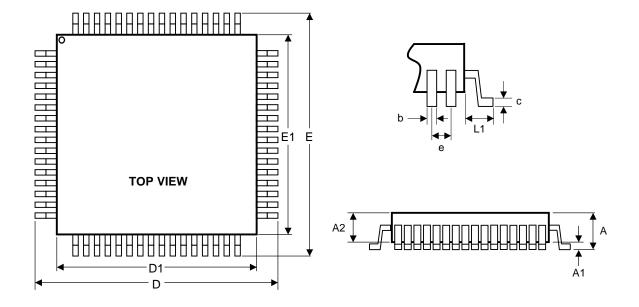

Figure 7. Mechanical Dimensions

All dimensions are in millimeters

| PART NUMBER | D1/E1 | D/E | b    | е   | L1  | С     | A2  | A1  | А   |

|-------------|-------|-----|------|-----|-----|-------|-----|-----|-----|

| VN16117L1   | 10    | 12  | 0.2  | 0.5 | 1.0 | 0.127 | 1.4 | 0.1 | 1.5 |

| VN16117L2   | 14    | 16  | 0.35 | 0.8 | 1.0 | 0.127 | 1.4 | 0.1 | 1.5 |

Package follows JEDEC Standards

# **Ordering Information**

| Part Number | No. of Pins | Package | Temperature  |

|-------------|-------------|---------|--------------|

| VN16117L1   | 64          | LQFP    | 0°C to +70°C |

| VN16117L2   | 64          | LQFP    | 0°C to +70°C |

#### Appendix A

#### Fibre Channel Transceiver Pin Cross Reference Guide VN16117, VSC7123/25, HDMP-1536A/46A and HDMP-1636A/46A

#### Summary:

Vaishali Semiconductor's VN16117 is functionally pin compatible with Vitesse's VSC7123/25 and Agilent's HDMP-1536A/46A or HDMP-1636/46A. Minor differences exist amongst the parts regarding the use of certain pins that are used by the manufacturer for internal tests, as is further clarified below. These differences will not affect plug compatibility during normal operations.

|       | Vaishali  | Vitesse    | Agilent        |                                     |

|-------|-----------|------------|----------------|-------------------------------------|

| Pin # | VN16117   | VSC7123/25 | HDMP-1536A/46A | Comments                            |

|       |           |            | or             |                                     |

|       |           |            | HDMP-1636A/46A |                                     |

| 1     | GND_ESD   | VSSD       | GND            | Connect to the ground plane.        |

| 2     | TX<0>     | Т0         | TX[0]          | 10-bit parallel data input pins.    |

| 3     | TX<1>     | T1         | TX[1]          |                                     |

| 4     | TX<2>     | T2         | TX[2]          |                                     |

| 6     | TX<3>     | Т3         | TX[3]          |                                     |

| 7     | TX<4>     | T4         | TX[4]          |                                     |

| 8     | TX<5>     | T5         | TX[5]          |                                     |

| 9     | TX<6>     | T6         | TX[6]          |                                     |

| 11    | TX<7>     | T7         | TX[7]          |                                     |

| 12    | TX<8>     | T8         | TX[8]          |                                     |

| 13    | TX<9>     | Т9         | TX[9]          |                                     |

| 5     | VDD_ESD   | VDDD       | VCC            | Connect to 3.3V                     |

| 10    | VDD_ESD   | VDDD       | VCC            | Connect to 3.3V                     |

| 14    | GND_ESD   | VSSD       | GND            | Connect to the ground plane.        |

| 15    | GND_TXA   | VSSA       | GND_TXA        | Connect to the ground plane.        |

| 16    | NC        | CAP0       | TXCAP1         | Vaishali requires no external caps. |

|       |           |            |                | External capacitor will not affect  |

|       |           |            |                | performance                         |

| 17    | NC        | CAP1       | TX_CAP0        | Vaishali requires no external caps. |

|       |           |            |                | External capacitor will not affect  |

|       |           |            |                | performance                         |

| 18    | VDD_TXA   | VDDA       | VCC_TXA        | Connect to 3.3V                     |

| 19    | EWRAP     | EWRAP      | LOOPEN         | Loop-back Enable when HIGH. Set     |

|       |           |            |                | LOW for normal operation            |

| 20    | VDD_TXD   | VDDD       | VCC            | Connect to 3.3V                     |

| 21    | GND_TXD   | VSSD       | GND            | Connect to the ground plane         |

| 22    | TX_CLK    | REFCLK     | REFCLK         | 125MHz reference clock.             |

| 23    | VDD_RXD   | VDDD       | VCC            | Connect to 3.3V                     |

| 24    | EN_CDET   | ENCDET     | ENBYTSYNC      | Comma Detect Enable (Active HIGH)   |

| 25    | GND_RXD   | VSSD       | GND            | Connect to the ground plane.        |

| 26    | SIG_DET   | SIGDET     | SIG_DET        | Signal Detect (Active HIGH)         |

| 27    | NC        | TD0        | N/C            | No connect for normal operation.    |

|       |           | (Note 1)   |                |                                     |

| 28    | VDD_RXD   | VDDD       | VCC            | Connect to 3.3V                     |

| 29    | VDD_RX    | VDDT       | VCC_RXTTL      | Connect to 3.3V                     |

| 30    | RX_CLK<1> | RCLKN      | RBC1           | Receiver Byte Clock                 |

| 31    | RX_CLK<0> | RCLK       | RBC0           | Receiver Byte Clock                 |

| 32    | GND_RX    | VSST       | GND_RXTTL      | Connect to the ground plane         |

| VN16 <sup>4</sup> | 117     |      |           | Preliminary                 |  |  |  |  |

|-------------------|---------|------|-----------|-----------------------------|--|--|--|--|

| 33                | GND_RXT | VSST | GND_RXTTL | Connect to the ground plane |  |  |  |  |

|       | Vaishali   | Vitesse    | Agilent        |                                     |

|-------|------------|------------|----------------|-------------------------------------|

| Pin # | VN16117    | VSC7123/25 | HDMP-1536A/46A | Comments                            |

|       |            |            | or             |                                     |

|       |            |            | HDMP-1636A/46A |                                     |

| 34    | RX<9>      | R9         | RX[9]          | Received Parallel Data Output       |

| 35    | RX<8>      | R8         | RX[8]          |                                     |

| 36    | RX<7>      | R7         | RX[7]          |                                     |

| 38    | RX<6>      | R6         | RX[6]          |                                     |

| 39    | RX<5>      | R5         | RX[5]          |                                     |

| 40    | RX<4>      | R4         | RX[4]          |                                     |

| 41    | RX<3>      | R3         | RX[3]          |                                     |

| 43    | RX<2>      | R2         | RX[2]          |                                     |

| 44    | RX<1>      | R1         | RX[1]          |                                     |

| 45    | RX<0>      | R0         | RX[0]          |                                     |

| 37    | VDD_RXT    | VDDT       | VCC_RXTTL      | Connect to 3.3V                     |

| 42    | VDD_RXT    | VDDT       | VCC_RXTTL      | Connect to 3.3V                     |

| 46    | GND_RXT    | VSST       | GND_RXTTL      | Connect to the ground plane         |

| 47    | COM_DET    | COMDET     | BYTSYNC        | Comma Detect (Byte Sync)            |

| 48    | NC         | TDI        | RXCAP0         | Vaishali requires no external caps. |

|       |            |            |                | External capacitor will not affect  |

|       |            |            |                | performance                         |

| 49    | NC         | ТСК        | RXCAP1         | Vaishali requires no external caps. |

|       |            |            |                | External capacitor will not affect  |

|       |            |            |                | performance                         |

| 50    | VDD_RXF    | VDDD       | VCC_RXA        | Connect to 3.3V                     |

| 51    | GND_RXF    | VSSD       | GND_RXA        | Connect to the ground plane         |

| 52    | DIN-       | RX-        | -DIN           | High-speed serial data input        |

| 53    | VDD_RXESD  | N/C        | VCC            | Connect to 3.3V                     |

| = 1   |            | (Note 2)   | DIN            |                                     |

| 54    | DIN+       | RX+        | +DIN           | High-speed serial data input        |

| 55    | VDD_RXESD  | TMS        | VCC            | Connect to 3.3V                     |

| 56    | GND_RXESD  | TRSTN      | GND            | Connect to the ground plane         |

| 57    | VDD_RXA    | VDDD       | VCC            | Connect to 3.3V                     |

| 58    | GND_RXA    | VSSD       | GND            | Connect to the ground plane         |

| 59    | VDD_RXA    | VDDD       | VCC            | Connect to 3.3V                     |

| 60    | VDD_TX_ECL | VDDP       | VCC_TXECL      | Connect to 3.3V                     |

| 61    | DOUT-      | TX-        | -DOUT          | High-speed serial data output       |

| 62    | DOUT+      | TX+        | +DOUT          | High-speed serial data output       |

| 63    | VDD_TX_HS  | VDDP       | VCC_TXHS       | Connect to 3.3V                     |

| 64    | GND_TX_HS  | VSSD       | GND_TXHS       | Connect to the ground plane         |

# Notes:

- 1. For VSC7123, this pin is in high-impedance state in normal operation.

- 2. For VSC7123, this pin has no internal connection.