Product Brief

Framers and Mappers

#### Features:

# **System / Packet Interface**

- 32-bit Industry Compliant POS-PHY-3, Single-PHY Packet Interface

- 32-bit Industry Compliant UTOPIA-3, Single-PHY Cell Interface

# Physical Layer Channelization Support

STS-48c / STM-16c

# **Payload Processing**

- Transparent Mode -Direct SPE Mapping

- ATM Cell Processing

- Programmable HDLC / PPP Encapsulation

### **SONET / SDH Processing**

- Full Section, Line, and Path Termination and Generation

- Performance Monitoring and Reporting

- Enhanced Bit Error Rate Monitoring

- Section and Path Trace Buffers

- Full Overhead Insertion and Extraction and Status Monitoring Through Dedicated Access Ports

# **General Description**

The VSC9112 is a dual mode STS-48c/ STM-16c Packet/ATM mapping device. In Packet over SONET (POS) mode, this device can be used in equipment interconnecting IP/PPP/HDLC data over public or private SONET/SDH networks. Similarly in the ATM mode, this device can be used in equipment interconnecting enterprise ATM switches.

Features of the VSC9112 include: Full insertion/extraction of the transport overhead, bit error rate and extensive

SONET/packet/cell performance monitoring, packet/cell filtering and discarding functionalities, transmit and receive, JTAG TAP controller, and an 8-bit CPU interface with 8 general purpose I/O ports.

This highly integrated device provides a complete low-power physical layer solution on a single chip for Packet/ATM over SONET/SDH at the STS-48 rate.

Framers and Mappers

## Features Continued:

#### **Line Interface**

- 16-bit 155 MHz Line Interface

- Synchronization for STS-192 Applications

# **Special Features**

- Extensive Packet / Cell Performance Monitoring Features

- 16 Kb Packet / Cell FIFO for Full Packet Encapsulation

- Programmable Error Discarding and Label Filtering

- Rx and Tx Timestamp Feature for Performance Monitoring Applications

#### **Miscellaneous Features**

- Generic 8-bit CPU Interface

- Compliant JTAG Boundary Scan Interface

- Five Loopback Modes for Test and Diagnostic Applications

- 0.35 micron CMOS, 352-pin SBGA, 3.0 Watts Maximum

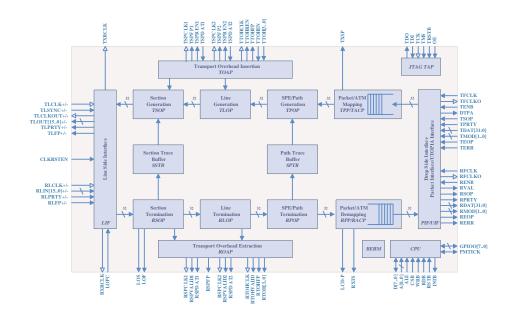

# VSC9112 Block Diagram

#### VSC9112 Reference Board

For more information on Vitesse Products visit the Vitesse web site at www.vitesse.com or contact Vitesse Sales at (800) VITESSE or sales@vitesse.com