#### AUGUST 2000

### **GENERAL DESCRIPTION**

The XRT4500 is a fully integrated multiprotocol serial interface. It supports all of the popular serial communication interface standards such as ITU-T V.35, ITU-T V.36, EIA530A, RS232 (ITU-T V.28), ITU-T X.21 and RS449. It can easily be interfaced with most common types of Serial Communications Controllers (SCCs). This device contains eight receivers and eight transmitters, in groups of six or seven. It is a complete solution containing all of the required source and load termination resistors in one 80-pin TQFP package. The XRT4500 operates at higher speeds (20MHz for V.35 and 256kbps for V.28).

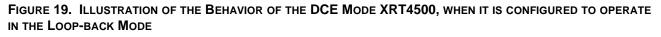

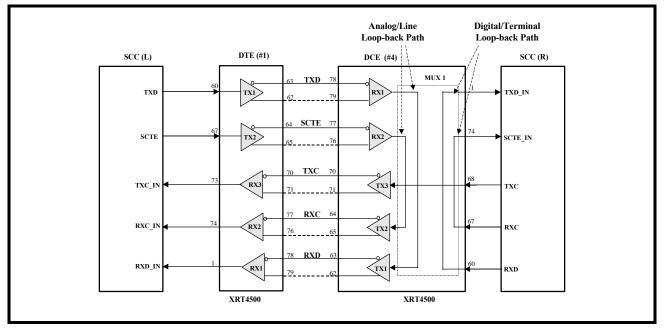

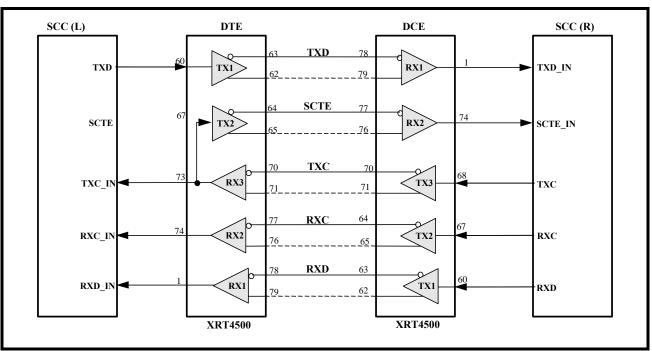

The XRT4500 can be configured to operate in one of the seven interface standards in either DTE, or DCE modes of operation and power down mode. It fully supports echoed clock as well as clock and data inversion. Loopbacks are supported in DTE and DCE modes of operation. This feature eliminates the need for external circuitry for loopback implementation.

Control signals such as RI, RL, DCD, DTR, DSR are protected against glitches by internal filters. These filters can be turned off. The XRT4500 provides an internal oscillator (clock signal) which can be used to conduct standalone diagnostics of DTE equipment.

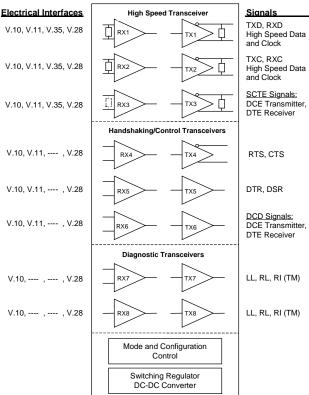

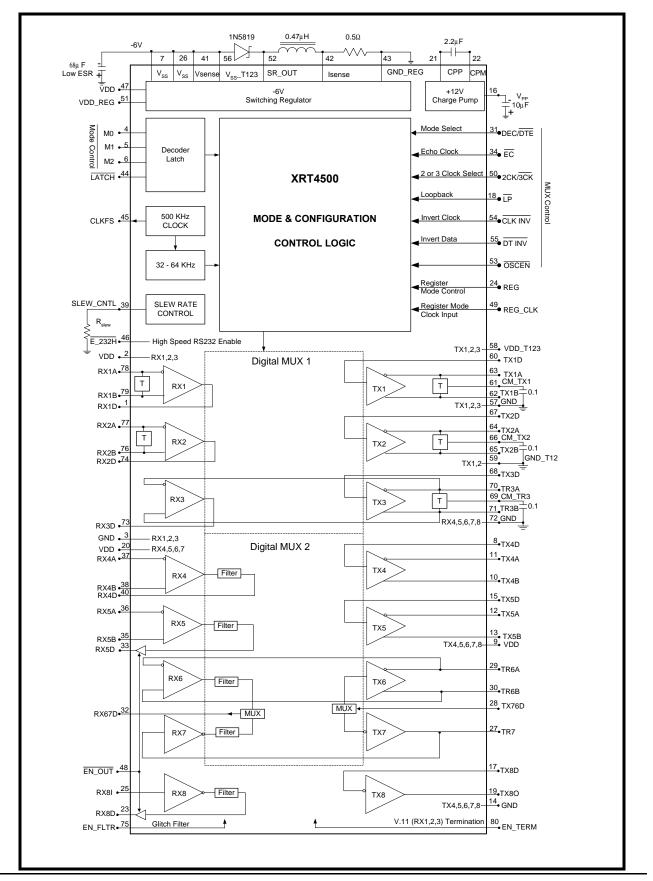

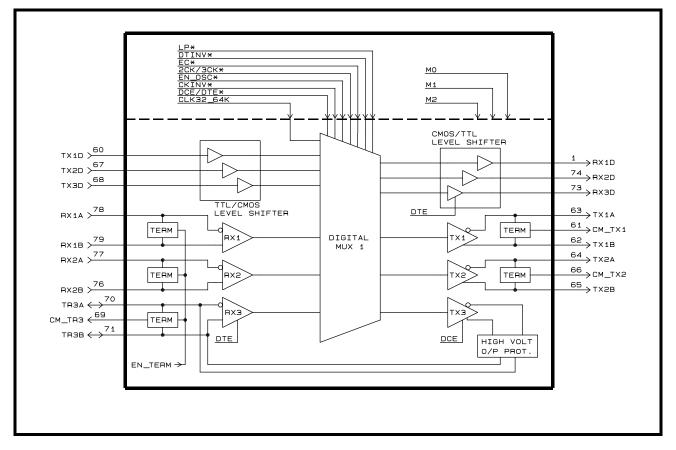

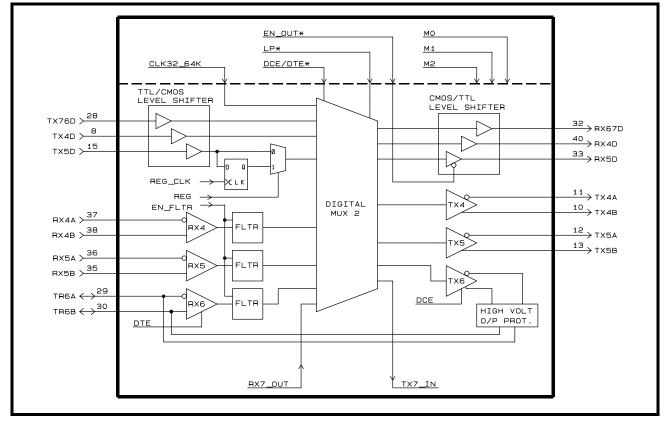

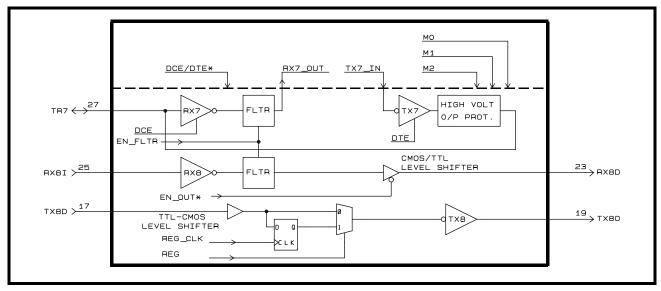

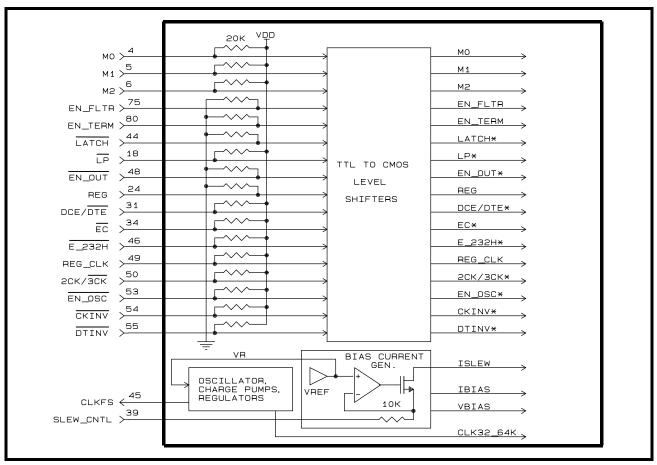

#### **BLOCK DIAGRAM**

#### **FEATURES**

- Pin Programmable Multiprotocol Serial Interface

- V.35, V.36, EIA-530 A, RS232 (V.28), V.10, V.11, X.21 and RS449 Communication Interface Standards

REV. 1.01

- V.28, V.10, V.11 and V.35 Electrical Interfaces are 'CTR2' Compliant

- Contains On-Chip Source and Load Termination Resistors

- Contains Eight Receivers and Eight Transmitters with Switchable DTE and DCE Modes

- Glitch Filters on the Control Signals (Selectable)

- +5V Single Power Supply with internal DC-DC Converter

- Full Support of Loopbacks, Data & Clock Inversion, and Echoed Clock in DTE and DCE Modes

- Full Support of Most Popular Types of HDLC Controllers (Single, Double, and Triple Clocks supported)

- High-speed V.28 Driver: 256KHz

- Internal Oscillator for Standalone DTE Loopback

Testing

- Control Signals Can Be Registered and Non-registered

- Control Signals Can Be Tri-stated for Bus-based

Designs

- "Cable Safe" Operation Supported

- ESD Protection Over ± 1KV Range

- TTL Level Digital Inputs

- TTL/CMOS Digital Outputs

#### APPLICATIONS

- Data Service Units (DSU)

- Channel Service Units (CSU)

- Routers

- Bridges

- Access Equipment

REV. 1.01

#### BLOCK DIAGRAM

REV. 1.01

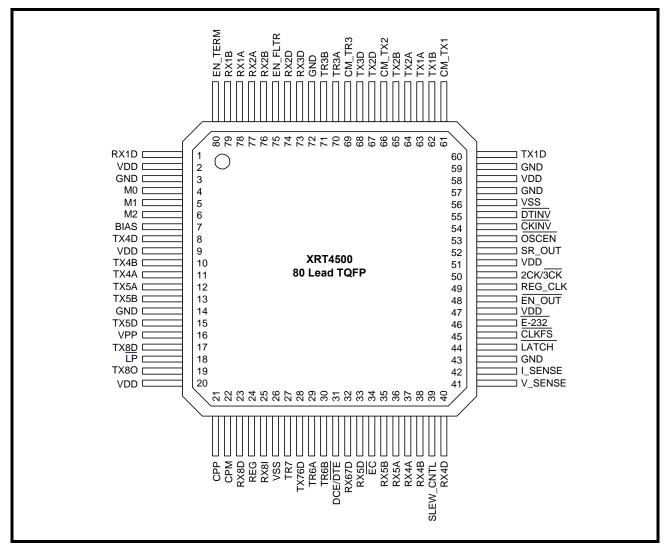

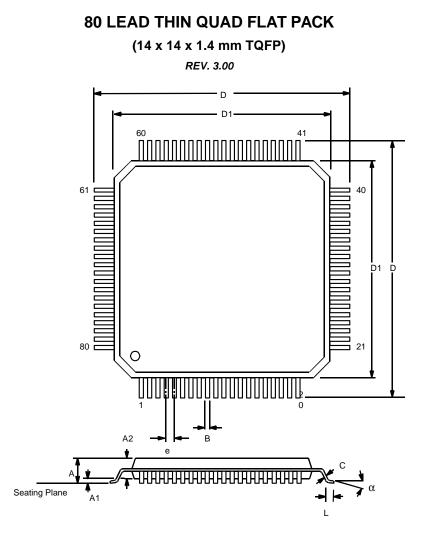

#### PIN OUT OF THE DEVICE

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE     | OPERATING TEMPERATURE RANGE |

|-------------|-------------|-----------------------------|

| XRT4500CV   | 80 Pin TQFP | 0°C to +70°C                |

REV. 1.01

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|--------|-------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | RX1D   | D_RXD       | D_TXD       | 0    | <ul> <li>Receiver 1 Digital Output – Digital Data Output to terminal equipment This output pin is the digital (TTL/CMOS level) representation of the line signal that has been received via the RX1A (pin 78) and RX1B (pin 79) input pins. The exact role that this pin plays depends upon whether the XRT4500 is operating in the DCE or DTE Mode. DCE Mode – TXD Digital Output Signal This output pin functions as the TXD Digital Output signal (which should be input to the Terminal Equipment). DTE Mode – RXD Digital Output Signal This output pin functions as the RXD Digital Output signal (which should be input to the Terminal Equipment). </li> </ul> |

| 2        | VDD    |             |             |      | Analog VDD for Receiver 1, 2, 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 3        | GND    |             |             | I    | Analog GND for Receiver 1, 2, 3 and Transmitter 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4        | МО     |             |             | -    | Mode Control – Mode Select Input 0This input pin, along with M1 and M2 are used to configure the<br>XRT4500 to operate in the desired "Communication Interface"<br>Mode. Tables 1 and 2 present the relationship between the<br>states of the M2, M1 and M0 input pins and the corresponding<br>communication interface modes selected.This input pin (along with M1 and M2) is internally latched into<br>the XRT4500, upon the rising edge of the "LATCH" signal. At this<br>point, changes in this input pin will not effect the "internally<br>latched" state of this pin.This input pin contains an Internal 20KΩ pull-up to V<br>DD.                             |

| 5        | M1     |             |             | Ι    | Mode Control – Mode Select Input 1This input pin, along with M0 and M2 are used to configure theXRT4500 to operate in the desired "Communication Interface"Mode. Tables 1 and 2 present the relationship between the statesof the M2, M1 and M0 input pins and the corresponding commu-nication interface modes selected.This input pin (along with M0 and M2) is internally latched into theXRT4500 device, upon the rising edge of the "LATCH" signal. Atthis point, changes in this input pin will not effect the "internallylatched" state of this pin.This input pin contains an Internal 20KΩ pull-up to V <sub>DD</sub> .                                       |

| PIN | SYMBOL          | DTE   | DCE   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-----------------|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #   | _               | MODE  | MODE  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 6   | M2              |       |       | I    | Mode Control – Mode Select Input 2This input pin, along with M0 and M1 are used to configure theXRT4500 to operate in the desired "Communication Interface"Mode. Tables 1 and 2 present the relationship between thestates of the M2, M1 and M0 input pins and the correspondingcommunication interface modes selected.This input pin (along with M0 and M1) is internally latched intothe XRT4500 device, upon the rising edge of the "LATCH" signal. At this point, changes in this input pin will not effect the"internally latched" state of this pin.This input pin contains an Internal 20KΩ pull-up to V <sub>DD</sub> .                                                                                                                                                                                           |

| 7   | V <sub>SS</sub> |       |       |      | <b>-6V Power Supply Signal:</b> This supply voltage is internally generated by the Switching Regulator Circuit within the XRT4500 device. The -6V is used by TX 4, 5, 6, 7, 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 8   | TX4D            | D_RTS | D_CTS | I    | <ul> <li>Transmitter 4 – Digital Data Input from Terminal Equipment<br/>The XRT4500 accepts binary TTL Level data stream, via this<br/>input pin, converts it into either a V.11 or V.28 format and outputs<br/>it via the TX4A and TX4B output pins.</li> <li>The exact role that this pin plays depends upon whether the<br/>XRT4500 is operating in the DCE or DTE Mode.</li> <li>DCE Mode – CTS (Clear to Send) Input<br/>If the XRT4500 is operating in the DCE Mode, then this input pin<br/>should be tied to the CTS Output pin of the Terminal Equipment.</li> <li>DTE Mode – RTS (Request to Send) Input<br/>If the XRT4500 is operating in the DTE Mode, then this input pin<br/>should be tied to the RTS output pin of the Terminal Equipment.</li> </ul>                                                    |

| 9   | VDD             |       |       |      | Analog VDD – For Transmitters 4, 5, 6, 7 and 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 10  | TX4B            | RTSB  | CTSB  | 0    | <ul> <li>Transmitter 4 – Positive Data Differential Output to Line<br/>The XRT4500 accepts a TTL binary data stream from the Termi-<br/>nal Equipment via the TX4D (pin 8) input pin. The XRT4500 will<br/>convert this data into either the V.10, V.11 or V.28 modes, and<br/>will output it via this pin and TX4A (pin 11).</li> <li>The exact role that this pin plays depends upon whether the<br/>XRT4500 is operating in the DTE or DCE mode.</li> <li>DTE Mode – Positive Polarity portion of RTS Line Signal.</li> <li>DCE Mode – Positive Polarity portion of CTS Line Signal.</li> <li>Note: If the XRT4500 has been configured to operate in either<br/>the V.35, V.28/EIA-232 or V.10 Modes, then all of the data will be<br/>outputted (to the line) in a single-rail manner via this output pin.</li> </ul> |

REV. 1.01

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------|--------|-------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11       | TX4A   | RTSA        | CTSA        | 0    | <ul> <li>Transmitter 4 – Negative Data Differential Output to Line The XRT4500 accepts a TTL binary data stream from the Terminal Equipment via the TX4D (pin 8) input pin. The XRT4500 will convert this data into either the V.10, V.11 or V.28 modes, and will output it via this pin and TX4B (pin 10). The exact function of this output pin depends upon whether the XRT4500 device is operating in the DTE or DCE mode. </li> <li>DTE Mode – Negative Polarity portion of the RTS Line Signal.</li> <li>DCE Mode – Negative Polarity portion of the CTS Line Signal.</li> <li>Note: This output pin is not used if the XRT4500 has been con- figured to operate in either the V.35, V.28/EIA-232 or V.10 Modes.</li></ul>                                                                                                                    |

| 12       | TX5A   | DTRA        | DSRA        | 0    | <ul> <li>Transmitter 5 – Negative Data Differential Output to Line<br/>The XRT4500 accepts a TTL binary data stream via the TX5D (pin<br/>15) input pin. The XRT4500 will convert this data into either the V.11<br/>or V.28 modes, and will output it via this pin and TX5B (pin 13). The<br/>exact function of this output pin depends upon whether the<br/>XRT4500 device is operating in the DTE or DCE mode.</li> <li>DTE Mode – Negative Polarity portion of the DTR Line Signal.<br/>Transmitter 5 accepts a TTL level binary data stream (as the<br/>Data Terminal Read – DTR) from the terminal equipment.</li> <li>DCE Mode – Negative Polarity portion of the DSR Line Signal.</li> <li>Note: This output pin is not used if the XRT4500 has been config-<br/>ured to operate in either the V.35, V.28/EIA-232 or V.10 Modes.</li> </ul> |

| 13       | TX5B   | DTRB        | DSRB        | 0    | <ul> <li>Transmitter 5 – Positive Data Differential Output to Line The XRT4500 accepts a TTL binary data stream via the TX5D (pin 15) input pin. The XRT4500 will convert this data into either the V.11 or V.28 modes, and will output it via this pin and TX5A (pin 12). The exact function of this output pin depends upon whether the XRT4500 device is operating in the DTE or DCE mode.</li> <li>DTE Mode – Positive Polarity portion of DTR Line signal.</li> <li>DCE Mode – Positive Polarity portion of DSR Line signal.</li> <li>Note: If the XRT4500 has been configured to operate in either the V.35, V.28/EIA-232 or V.10 Modes, then all of the data will be outputted (to the line) in a single-ended manner, via this output pin.</li> </ul>                                                                                       |

| 14       | GND    |             |             |      | Analog GND – For Transmitters 4, 5, 6, 7, and 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>#</b><br>15 |      |       | DCE   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------|------|-------|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15             |      | MODE  | MODE  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | TX5D | D_DTR | D_DSR | Ι    | <ul> <li>Transmitter 5 – Digital Data Input from Terminal Equipment<br/>This input pin accepts a TTL level binary data stream, from the<br/>local terminal equipment, and outputs it, in either a V.10, V.11 or<br/>V.28 manner, via the TX5A (pin 12) and TX5B (pin 13) output<br/>pins. The exact role that this input pin plays depends upon<br/>whether the XRT4500 is operating in the DTE or DCE Modes.</li> <li>DTE Mode – Data Terminal Ready (DTR) Input Pin<br/>If the XRT4500 is operating in the DTE mode, then this input pin<br/>should be tied to the DTR output pin of the terminal equipment.</li> <li>DCE Mode – Data Set Ready (DSR) Input Pin<br/>If the XRT4500 is operating in the DCE mode, then this input pin<br/>should be tied to the DSR output pin of the terminal equipment.</li> <li>Note: If the XRT4500 has been configured to operate in the<br/>"Registered" Mode, then data applied to this input pin will be<br/>latched (into the XRT4500) upon the rising edge of the<br/>REG_CLK input signal.</li> </ul> |

| 16             | VPP  |       |       |      | <b>+12V Power Supply Bias Signal:</b> This supply voltage is internally generated by the Charge Pump Circuit within the XRT4500 device. If +12V is available, then the external components can be eliminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17             | TX8D | D_RL  | D_RI  | Ι    | <ul> <li>Transmitter 8 – Digital Data Input from Terminal Equipment<br/>This input accepts a TTL level binary data stream, from the local<br/>terminal equipment, and outputs it, in either a V.10 or V.28 man-<br/>ner via the TX8O (pin 19) output pin.</li> <li>DCE Mode – Ring Indicator (or Test Mode) Input Pin<br/>If the XRT4500 has been configured to operate in the<br/>DCE Mode – This input pin should be connected to either the<br/>"RI" (Ring Indicator) or the "TM" (Test Mode) indicator output pin<br/>of the Terminal Equipment.</li> <li>DTE Mode – Remote Loop-back Indicator Input Pin<br/>If the XRT4500 has been configured to operate in the<br/>DTE Mode – This input pin should be connected to the "RL"<br/>(Remote Loop-back) indicator output pin of the Terminal Equip-<br/>ment.</li> <li>Note: If the XRT4500 has been configured to operate in the<br/>"Registered" Mode, then data applied to this input pin will be</li> </ul>                                                                               |

REV. 1.01

### **PIN DESCRIPTIONS**

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|--------|-------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18       | ΓP     |             |             | Ι    | Loopback Command Input Pin – Active Low:<br>This active-low input pin permits the user to configure the<br>XRT4500 into a "Loop-Back" Mode. The exact loop-back will<br>depend upon whether the XRT4500 is operating in the DTE or<br>DCE Modes.<br>Setting this input pin to "LOW" enables the Loop-back Operation.<br>Setting this input pin to "HIGH" disables the Loop-back Operation.<br>This input pin contains an Internal 20KΩ pull-up to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                |

| 19       | TX8O   | RLA         | RIA         | 0    | <ul> <li>Transmitter 8 – Single Ended Data Output to Line The XRT4500 accepts a TTL level binary data stream, from the local terminal equipment via the "TX8D" input pin (pin 17), and outputs it, in either a V.10 or V.28 manner via this output pin. The exact role that this output pin plays depends upon whether the XRT4500 is operating in the DTE or DCE Modes. </li> <li>If the XRT4500 is configured to operate in the DCE Mode: This output pin will typically drive the state of either the "RI" (Ring Indicator) or "TM" (Test Mode) signals to the Remote  Terminal Equipment. </li> <li>If the XRT4500 is configured to operate in the DTE Mode: This output pin will typically drive the state of the "RL" (Remote  Loop-back) signal to the Remote Terminal Equipment.</li></ul> |

| 20       | VDD    |             |             |      | Analog VDD – For Receivers 4, 5, 6, 7 and 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21       | CPP    |             |             |      | <b>Charge Pump Capacitor Pin:</b> The user is expected to apply a 2.2µF tantalum capacitor between pin 21 and pin 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22       | СРМ    |             |             |      | <b>Charge Pump Capacitor Pin:</b> The user is expected to apply a 2.2µF tantalum capacitor between pin 21 and pin 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

**Note:** Sample names beginning with D\_ are digital signals.

**NOTE:** Sample names ending with B and A are the positive and negative polarities of differential signals respectively.

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|--------|-------------|-------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23       | RX8D   | D_RI        | D_RL        | 0    | <b>Receiver 8 – Digital Data Output to Terminal Equipment</b><br>The XRT4500 receives a line signal (in either the V.10 or V.28<br>manner) via the RX8I input pin (Pin 25). The XRT4500 then con-<br>verts this data into a digital format (e.g., a CMOS level binary<br>data stream) and outputs it via this pin. The exact functionality of<br>this output pin depends upon whether the XRT4500 is operating<br>in the DCE or DTE Modes. |

|          |        |             |             |      | DCE Mode – Remote Loop-back Indicator Output<br>If the XRT4500 has been configured to operate in the DCE<br>Mode – This output pin should be connected to the "RL" (Remote<br>Loop-back) indicator input pin (of the Terminal Equipment).                                                                                                                                                                                                  |

|          |        |             |             |      | DTE Mode – Ring Indicator (or Test Mode Indicator) Output<br>If the XRT4500 has been configured to operate in the DTE<br>Mode – This output pin should be connected to either the "RI"<br>(Ring Indicator) or "TM" (Test Mode) input pin of the Terminal<br>Equipment.                                                                                                                                                                     |

|          |        |             |             |      | <b>Notes:</b> This output pin is tri-stated if the EN_OUT* input pin (pin 48) is "HIGH". If the XRT4500 has been configured to operate in the "Registered" Mode, then data will be outputted via this pin, upon the rising edge of the REG_CLK clock signal.                                                                                                                                                                               |

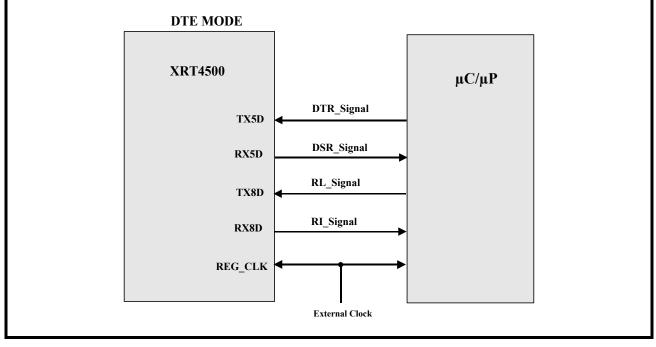

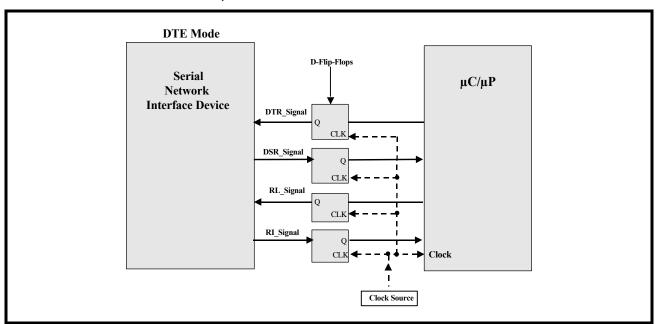

| 24       | REG    |             |             | I    | <b>Register Mode Control Select Input Pin:</b><br>This input pin permits the user to configure the XRT4500 to<br>operate in either the "Registered" Mode or in the "non-Regis-<br>tered" Mode. If the XRT4500 has been configured to operate in<br>the "Registered" Mode, then the following will happen.                                                                                                                                  |

|          |        |             |             |      | <ul> <li>Data at the "TX5D" and "TX8D" input pins (Pins 15 &amp; 17) will<br/>be latched into the XRT4500 circuitry upon the rising edge of<br/>the clock signal applied at the "REG_CLK" input pin.</li> </ul>                                                                                                                                                                                                                            |

|          |        |             |             |      | <ul> <li>Data will be output via the "RX5D" and "RX8D" pins, upon the<br/>rising edge of the clock signal applied at the "REG_CLK" input<br/>pin.</li> </ul>                                                                                                                                                                                                                                                                               |

|          |        |             |             |      | If the XRT4500 has been configured to operate in the "Non-Reg-<br>istered" Mode, then the "REG_CLK" clock signal will have no<br>effect on the processing of signals via the "TX5D", "TX8D",<br>"RX5D" and "RX8D" pins.                                                                                                                                                                                                                    |

|          |        |             |             |      | Setting the "REG" input to "HIGH" configures the XRT4500 to operate in the "Registered" Mode.                                                                                                                                                                                                                                                                                                                                              |

|          |        |             |             |      | Setting the "REG" input to "LOW" configures the XRT4500 to operate in the "Non-Registered" Mode.                                                                                                                                                                                                                                                                                                                                           |

|          |        |             |             |      | This pin contains an internal $20 \text{K}\Omega$ pull-down to ground.                                                                                                                                                                                                                                                                                                                                                                     |

×r

REV. 1.01

| PIN<br># | SYMBOL          | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------------|-------------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25       | RX8I            | RIA         | RLA         | Ι    | <ul> <li>Receiver 8 – Line Input Pin:<br/>This input pin accepts either a V.10 or V.28 type signal from the<br/>line. Receiver 8 will then convert this signal into a "CMOS" level<br/>(digital) signal and output this signal to the Terminal Equipment<br/>via the RX8D output pin (Pin 23). The exact function of this out-<br/>put pin depends upon whether the XRT4500 device is operating<br/>in the DTE or DCE mode.</li> <li>DTE Mode – Negative polarity portion of RI line signal</li> <li>DCE Mode – Negative polarity portion of RL line signal</li> <li>Notes: <ol> <li>For some DTE applications, this input pin would accept<br/>the "RI" (Ring Indicator) line signal (in either the V.10 or<br/>V.28 format) form the DCE Terminal Equipment.</li> </ol> </li> <li>For some DCE applications, this input pin would accept the<br/>"RL" (Remote Loop-back") line signal (in either the V.10 or<br/>the V.28 format) from the DTE Terminal Equipment.</li> </ul> |

| 26       | V <sub>SS</sub> |             |             |      | <b>-6V Power Supply:</b> This supply voltage is internally generated by the Switching Regulator Circuit within the XRT4500 device. The -6V power supply is used by receivers 4, 5, 6, 7 and 8. If a -6V supply is available then the external components can be eliminated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 27       | TR7             | LLA         | LLA         | 1/0  | <ul> <li>Transceiver # 7 I/O Pins The exact function of this pin depends upon whether the XRT4500 is operating in the DCE or DTE Modes. </li> <li>DTE Mode – Transmitter 7 – Single Ended Data Output to Line Transceiver 7 accepts a CMOS level signal via the "TX76D" input pin (pin 28). This digital data is converted into either a V.10 or V.28 electrical signal; which is then output (via this pin), on the line to the Remote Terminal Equipment. </li> <li>DCE Mode – Receiver 7 – Single Ended Data Input from Line This input pin accepts the line signal, from the Remote Terminal  Equipment, in a "single-ended" manner. This line signal is converted into a CMOS level signal and is output (to the local Terminal  Equipment) via the "RX67D" output pin (Pin 32).</li></ul>                                                                                                                                                                                 |

| 28       | TX76D           | D_LL        | D_DCD       | I    | Digital Input – Refer to Mode Control Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                          |

|----------|--------|-------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29       | TR6A   | DCDA        | DCDA        | I/O  | <b>Transceiver # 6 Line Signal I/O Pin:</b><br>The exact function of this pin depends upon whether the<br>XRT4500 has been configured to operate in the DCE or DTE<br>Mode.                                                                                                                                                                                                       |

|          |        |             |             |      | <b>DTE Mode: Negative Polarity Input of DCD (Data Carrier Detect) Signal:</b><br>This input pin (along with TR6B, pin 30) accepts the line signal, from the remote terminal equipment, in either a Single-Ended or Differential manner. This line signal is converted to CMOS level signals and is outputted (to the local terminal equipment) via the RX67D output pin (Pin 32). |

|          |        |             |             |      | DCE Mode: Negative Polarity Output Signal (of DCD-Data<br>Carrier Detect) to the Line:<br>Transceiver 6 accepts TTL level binary data stream, via the<br>"TX67D" (pin 28) input pin. This output pin, along with "TR6B"<br>(pin 30) will output this data to the Remote Terminal Equipment).<br>via an Analog Line Signal.                                                        |

|          |        |             |             |      | <b>Note:</b> This I/O pin will not be used if the XRT4500 has been con-<br>figured to operate in either the V.28/RS-232 or the V.35 Commu-<br>nications Interface Mode.                                                                                                                                                                                                           |

| 30       | TR6B   | DCDB        | DCDB        | I/O  | <b>Transceiver #6 Line Signal I/O Pin</b><br>The exact function of this pin, depends upon whether the<br>XRT4500 has been configured to operate in the DCE or DTE<br>Mode.                                                                                                                                                                                                        |

|          |        |             |             |      | DTE Mode: Receiver 6 – Positive Polarity Input of DCD (Data Carrier Detect) Signal:<br>This input pin (along with TR6A, pin 29) accepts the line signal, from the remote terminal equipment, in either a Single-Ended or Differential manner. This line is converted to CMOS signal levels and is output (to the local terminal equipment) via the RX67D output pin (Pin 32).     |

|          |        |             |             |      | DCE Mode: Transmitter 6 – Positive Polarity Output of DCD<br>(Data Carrier Data Signal) Pin:<br>Transceiver 6 accepts a TTL level binary data stream, via the<br>TX67D (pin 28) input pin. This output pin (along with TR6A, pin<br>29) will output this data (to the remote terminal equipment) via<br>an Analog line signal.                                                    |

REV. 1.01

#### **PIN DESCRIPTIONS**

| PIN<br># | SYMBOL  | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|---------|-------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31       | DCE/DTE | LOW         | HIGH        | Ι    | <ul> <li>DCE/DTE Mode Select:<br/>This input pin permits the user to configure the XRT4500 to operate in either the DCE Mode or in the DTE Mode.</li> <li>Logic 0: DTE Mode Operation<br/>When the XRT4500 is configured to operate in the "DTE" Mode, then "Transceiver # 3" will be configured to function as a Receiver.</li> <li>Logic 1: DCE Mode Operation<br/>When the XRT4500 is configured to operate in the "DCE" Mode, then "Transceiver # 3" will be configured to function as a Receiver.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 32       | RX67D   | D_DCD       | D_LL        | 0    | <ul> <li>Transceiver 6/7 Digital Output Pin:<br/>The exact function of this pin depends upon whether the XRT4500 has been configured to operate in the DCE or DTE Mode.</li> <li>DTE Mode – Data Carrier Detect (DCD) Output Pin</li> <li>When the XRT4500 is operating in the DTE Mode, this transceiver functions as a "line receiver". This line receiver accepts either a V.10, V.28 or V.11 line signal via the TR6A and TR6B input pins (pins 29 and 30) and converts this line signal into a CMOS level binary data stream. This binary data stream is output via this pin. For DTE applications, this input pin should be connected to the "DCD" input pin of the "Terminal Equipment".</li> <li>DCE Mode – Local Loop-back (LL) Indicator Output Pin</li> <li>When the XRT4500 is operating in the DCE Mode, this transceiver functions as a "line receiver". This line receiver accepts either a V.10, V.28 or V.11 line signal via the TR6A and TR6B input pins (pins 29 and 30) and converts this input pin should be connected to the "DCD" input pin of the "Terminal Equipment".</li> <li>DCE Mode – Local Loop-back (LL) Indicator Output Pin</li> <li>When the XRT4500 is operating in the DCE Mode, this transceiver functions as a "line receiver". This line receiver accepts either a V.10, V.28 or V.11 line signal via the TR6A and TR6B input pins (pins 29 and 30) and converts this line signal into a CMOS level binary data stream. This binary data stream is output via this pin. For DTE applications, this input pin should be connected to the "LL" input pin of the "Terminal Equipment".</li> </ul> |

**Note:** Sample names beginning with D\_ are digital signals.

**NOTE:** Sample names ending with B and A are the positive and negative polarities of differential signals respectively.

### **PIN DESCRIPTIONS**

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|--------|-------------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 33       | RX5D   | D_DSR       | D_DTR       | 0    | <ul> <li>Receiver 5 – Digital Data Output to Terminal Equipment The XRT4500 accepts a line signal (in either the V.10, V.11 or V.28 manner) via the RX5A and RX5B input pins (Pins 35 &amp; 36). The XRT4500 then converts this data into digital format (e.g., a CMOS level binary data stream) and outputs it to the Terminal Equipment via this pin.</li> <li>The exact role that this pin plays depends upon whether the XRT4500 device is operating in the DCE or DTE modes.</li> <li>DTE Mode – Data Set Ready (DSR) Output Pin For DTE applications, this output pin should be connected to the "DSR" input of the Terminal Equipment.</li> <li>DCE Mode – Data Terminal Ready (DTR) Output Pin For DCE applications, this output pin should be connected to the "DTR" input pin of the Terminal Equipment.</li> <li>Note: <ol> <li>This output pin is tri-stated if the EN_OUT input pin (pin 48) is "HIGH".</li> <li>If the XRT4500 has been configured to operate in the "Registered" Mode, then data will be outputted via this pin upon the rising edge of the "REG_CLK" clock signal.</li> </ol> </li> </ul> |

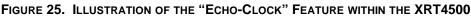

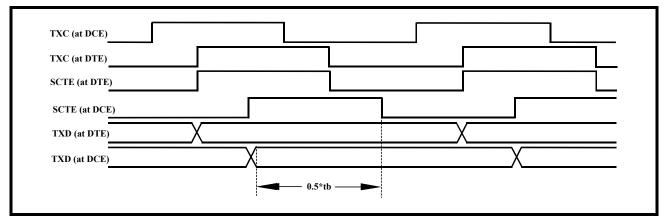

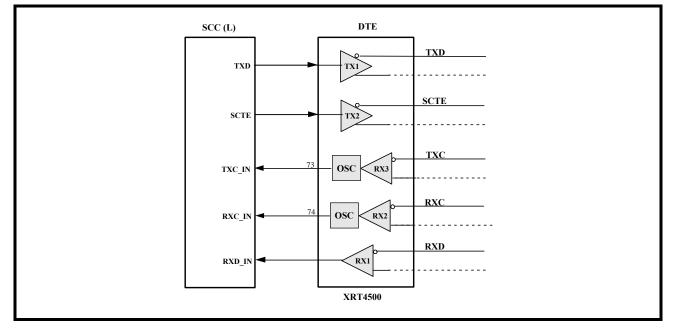

| 34       | EC     |             |             | Ι    | <b>Echo Clock Mode Select Input Pin</b><br>This input pin permits the user to enable or disable the "Echo-<br>Clock" Mode feature within the XRT4500 device. If the user con-<br>figures the XRT4500 to operate in the "Echo-Clock" Mode, then<br>the RX3D output pin (Pin 73) will be internally looped into the<br>"TX2D" input pin (Pin 67).<br>Setting this input pin "LOW" enables the "Echo-Clock" Mode.<br>Setting this input pin "HIGH" disables the "Echo-Clock" Mode.<br><i>Note: The "Echo-Clock" Mode feature is only available if the</i><br><i>XRT4500 is operating in the DTE Mode.</i><br>This input pin contains an internal 20KΩ pull-up to V <sub>DD</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                           |

**Note:** Symbol names beginning with D\_ are digital signals.

Note: Symbol names ending with B and A are the positive and negative polarities of differential signals respectively.

REV. 1.01

### **PIN DESCRIPTIONS**

| PIN<br># | SYMBOL | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|--------|-------------|-------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35       | RX5B   | DSRB        | DTRB        | I    | <b>Receiver 5 – Positive Data Differential Input from Line</b><br>The XRT4500 will accept either a V.10, V.11 or V.28 type signal<br>via this input pin, along with RX5A (Pin 36) and will generate a<br>resulting CMOS level binary data stream, via the RX5D (Pin 33)<br>output pin. The exact function of this input pin depends upon<br>whether the XRT4500 device is operating in the DTE or DCE<br>mode.                                                                                                                                                 |

|          |        |             |             |      | <b>DTE Mode</b> – Positive polarity portion of the DSR line signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |        |             |             |      | <b>DCE Mode</b> – Positive polarity portion of the DTR line signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|          |        |             |             |      | <b>Note:</b> If the XRT4500 has been configured to operate in either the V.35, V.28/EIA-232 or V.10 modes, then all of the data will be output (to the line) in a single-ended manner, via this output pin.                                                                                                                                                                                                                                                                                                                                                    |

| 36       | RX5A   | DSRA        | DTRA        | I    | <ul> <li>Receiver 5 – Negative Data Differential Input from Line</li> <li>The XRT4500 will accept either a V.10, V.11 or V.28 type signal via this input pin, along with RX5B (pin 35) and will generate a resulting CMOS level binary data stream, via the RX5D (Pin 33) output pin. The exact function of this input pin depends upon whether the XRT4500 device is operating in the DTE or DCE mode.</li> <li>DTE Mode – Negative polarity portion of the DSR line signal.</li> <li>DCE Mode – Negative polarity portion of the DTR line signal.</li> </ul> |

|          |        |             |             |      | <b>Note:</b> This input pin is not used if the XRT4500 has been configured to operate in either the V.35, V.28/EIA-232, or V.10 Modes.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 37       | RX4A   | CTSA        | RTSA        | I    | Receiver 4 – Negative Data Differential Input from Line<br>The XRT4500 will accept either a V.11 or V.28 type signal via<br>this input pin, along with RX4B (pin 38) and will generate a<br>resulting CMOS level binary data stream, via the RX4D output<br>pin (Pin 40). The exact function of this input pin depends upon<br>whether the XRT4500 device is operating in the DTE or DCE<br>mode.<br>Note: This input pin is not used if the XRT4500 has been config-<br>ured to operate in either the V.35, V.28/EIA-232, or V.10 Modes.                      |

| 38       | RX4B   | CTSB        | RTSB        | I    | <b>Receiver 4 – Positive Data Differential Input from Line</b><br>The XRT4500 will accept either a V.11 or V.28 type signal via<br>this input pin, along with RX4A (pin 37) and will generate a<br>resulting CMOS level binary data stream, via the RX4D output<br>pin (Pin 40). The exact function of this input pin depends upon<br>whether the XRT4500 device is operating in the DTE or DCE<br>mode.                                                                                                                                                       |

**Note:** Symbol names beginning with D\_ are digital signals.

Note: Symbol names ending with B and A are the positive and negative polarities of differential signals respectively.

### **PIN DESCRIPTIONS**

| PIN | SYMBOL    | DTE   | DCE   | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|-----------|-------|-------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #   |           | MODE  | MODE  |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

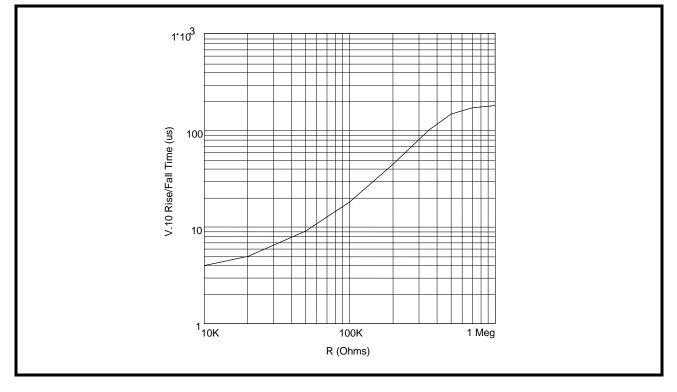

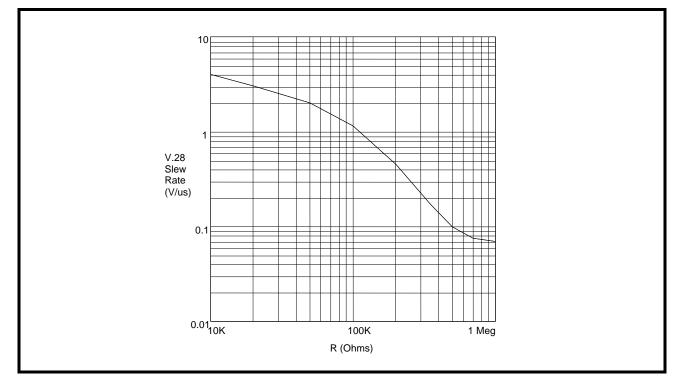

| 39  | SLEW_CNTL |       |       | 0    | <ul> <li>V.28/V.10 Slew-Rate Control Pin – This pin permits the user to specify the slew rate of the V.10 or V.28 output driver. The user accompanies this by connecting a resistor (of a specific value) between this pin and ground.</li> <li>Figure 24 presents a plot which depicts the relationship between the 'Rise/Fall Time' of a V.10 output signal (from the XRT4500) and the value of this resistor.</li> <li>Figure 25 presents a plot which depicts the relationship between the slew-rate (expressed in terms of V/µs) of a V.28 output signal (from the XRT4500) and the value of this resistor.</li> </ul>                    |

| 40  | RX4D      | D_CTS | D_RTS | 0    | <b>Receiver 4 – Digital Data Output to Terminal Equipment</b><br>This output pin is the digital (CMOS level) representation of the<br>line signal that is applied to the RX4A (pin 37) and RX4B (pin 38)<br>input pins.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |           |       |       |      | The exact role that this pin plays depends upon whether the XRT4500 is operating in the DCE or DTE Mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|     |           |       |       |      | <b>DCE Mode – CTS (Clear to Send) Output Signal</b><br>For DCE Mode applications, this output pin should be connected<br>to the "CTS" input pin of the Terminal Equipment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |           |       |       |      | <b>DTE Mode – RTS (Request to Send) Output Signal</b><br>For DTE Mode applications, this output pin should be connected<br>to the "RTS" input pin of the Terminal Equipment.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 41  | Vsense    |       |       | I    | Switching Regulator – Voltage sense input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 42  | Isense    |       |       | I    | Switching Regulator – Current sense input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 43  | GND_REG   |       |       |      | Switching Regulator Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 44  | LATCH     |       |       | I    | Mode Control Input Latch Enable – Logic 0:<br>This input pin permits the user to latch the states of the Mode<br>Control Input pins (4, 5, and 6) (M0, M1, and M2) into the<br>XRT4500 circuitry. This feature frees up the signals (driving the<br>Mode Control Input pins) for other purposes.<br>Driving this input, from "low" to "high" latches the contents of the<br>Mode Control pins of the XRT4500 (into the XRT4500 circuitry).<br>For the duration that the LATCH input pin is "high", the user can<br>change the state of the signals controller the M0, M1 and M2<br>input pins, without effecting the operation of the XRT4500. |

| 45  | CLKFS     |       |       | 0    | Internally Generated 500kHz Clock – This clock signal is inter-<br>nally used to drive both the switching regulator and the digital<br>'Glitch' filters. The user is advised to leave this pin floating.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

**Note:** Symbol names beginning with D\_ are digital signals.

**NOTE:** Symbol names ending with B and A are the positive and negative polarities of differential signals respectively.

REV. 1.01

#### **PIN DESCRIPTIONS**

| PIN<br># | SYMBOL          | DTE<br>MODE | DCE<br>MODE | TYPE | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|----------|-----------------|-------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 46       | E_232H          |             |             | Ι    | High Speed RS-232 Enable – Logic 0 enables high speed RS-<br>232 mode (drives $3K\Omega$ in parallel with 1000pF at 256 KHz).<br>Internal $20K\Omega$ pull-up to $V_{DD}$ .This input pin permits the user to either enable or disable the<br>'High-Speed RS-232 Driver' feature. The non high speed mode<br>provides a 120 Kbps clock rate.Note: This pin setting applies to all 'RS-232/V.28 Drivers' within<br>the XRT4500.                                                                                                                                                                                                          |  |

| 47       | V <sub>DD</sub> |             |             |      | Analog V <sub>DD</sub> for the Internal Switching Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

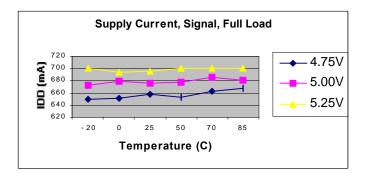

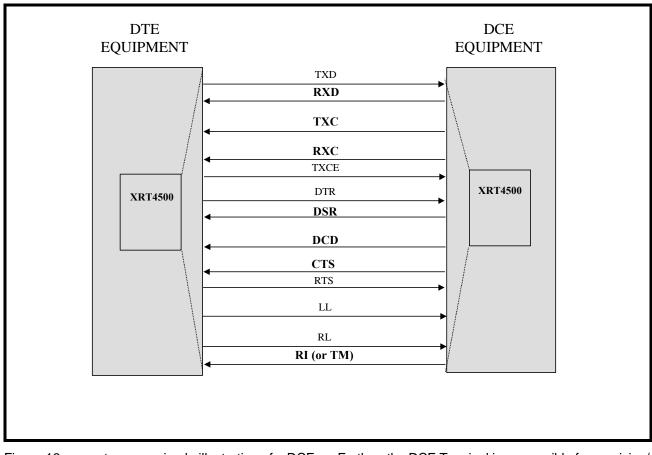

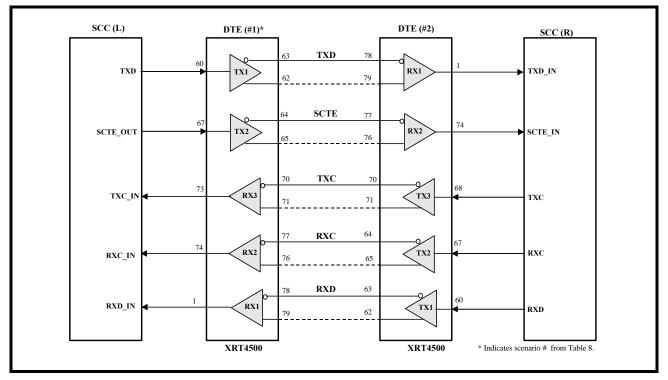

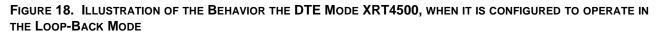

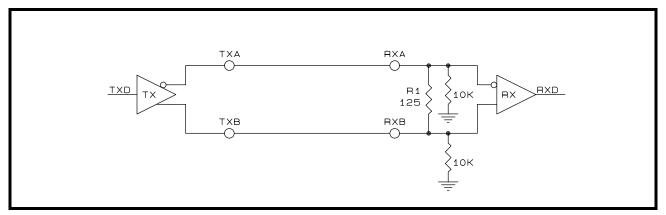

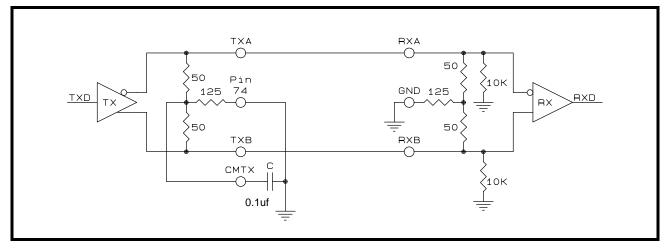

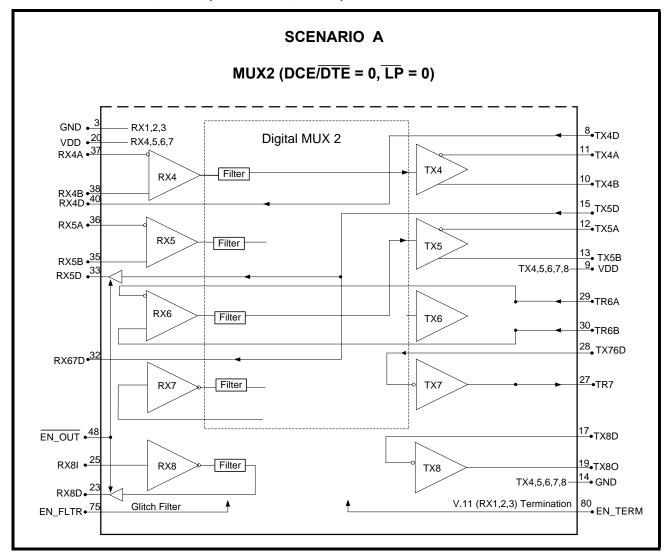

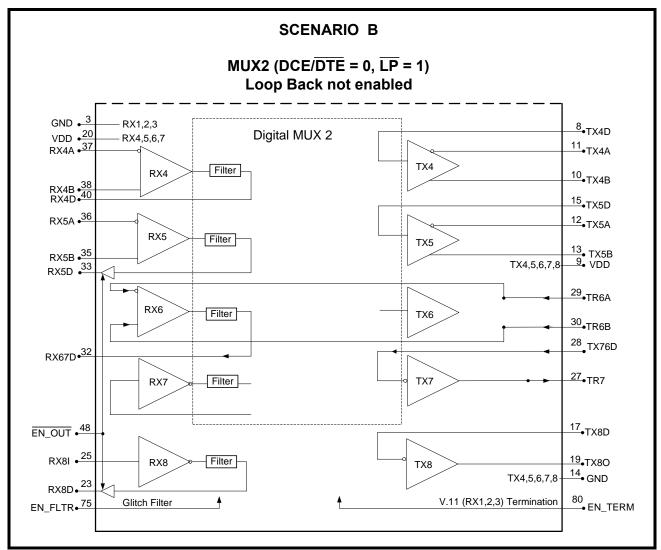

| 48       | EN_OUT          |             |             | Ι    | Output Enable Pin for Receiver 5 and 8This active-low output pin permits the user to tri-state the<br>"RX5D" and "RX8D" output pins (Pins 23 & 33).Setting this input pin "low" causes the XRT4500 to tri-state the<br>"RX5D" and "RX8D" output pins. Conversely, setting this input<br>pin "high" enables the "RX5D" and the "RX8D" output drivers for<br>signal transmission to the local Terminal Equipment.This input pin contains an internal 20kΩ pull-down resistor to<br>ground.                                                                                                                                                |  |