WM8170

3.3V Integrated Signal Processor for Area Array CCDs

Product Preview Rev 1.0 March 2000

# DESCRIPTION

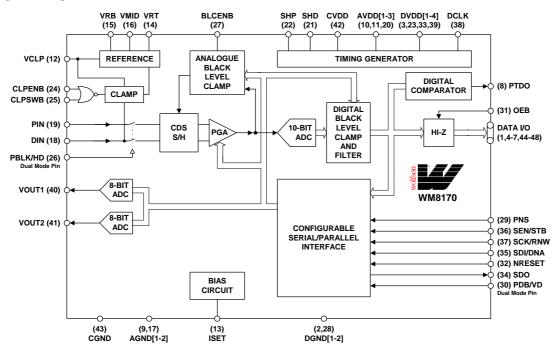

The WM8170 is a 10-bit analogue front end/digitiser IC, which processes and digitises the analogue output signals from area array CCD sensors at pixel sample rates of up to 21MSPS.

The device contains input blanking, correlated double sampling (CDS), programmable gain amplifier, black level clamp, on-board voltage reference and a 10-bit, 21MSPS ADC. Two auxiliary 8 bit DACs are provided which may be used for bias voltage control or camera functions such as auto-focus.

Fine black level adjustment is performed digitally after the ADC. This digital adjustment will follow DC shifts in the video input without introducing digital correction noise into the image.

The WM8170 is designed to interface to a wide range of area array CCDs and can operate at lower power for slower sample rates by setting the reference bias current via an external resistor connected to the ISET pin.

All signal timing within the device is derived from the CCD clock signals. The WM8170 is controlled via a configurable serial interface, which is compatible with all of Wolfson's imaging devices.

The user is able to control the device functions and monitor on-chip register settings via the easy-to-use digital management interface.

# FEATURES

- 10-bit, 21MSPS ADC

- No missing codes guaranteed

- Correlated double sampling

- Programmable gain amplifier

- Black level clamp

- Input blanking

- Two auxiliary 8-bit DACs

- Power save mode Serial or parallel control bus

- Serial of parallel control t

Adjustable sample rate

- User selectable sampling on rising or falling edge of clocks

- Single 3.3V power supply (3V minimum)

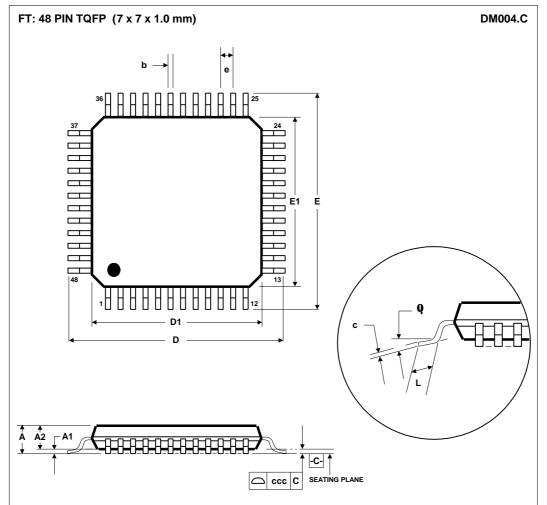

- 48-pin TQFP package

- Standby mode I<sub>CC</sub><10mA

- Power consumption typically 190mW at 12MHz, 270mW at 21MHz

## **APPLICATIONS**

- Digital still cameras

- Digital camcorders

- PC cameras

- Progressive scan CCDs

- NTSC, PAL interline CCDs

#### WOLFSON MICROELECTRONICS LTD. Lutton Court, Bernard Terrace, Edinburgh, EH8 9NX, UK Tel: +44 (0) 131 667 9386 Fax: +44 (0) 131 667 5176 Email: sales@wolfson.co.uk http://www.wolfson.co.uk

**Product Preview** data sheets contain specifications for products in the formative phase of development. These products may be changed or discontinued without notice.

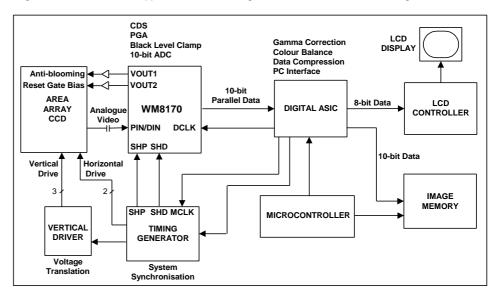

# **BLOCK DIAGRAM**

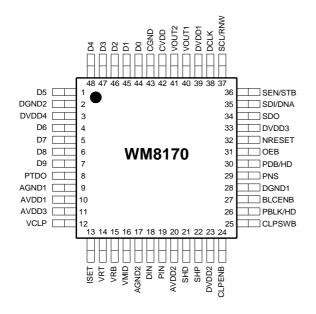

## **PIN CONFIGURATION**

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

As per JEDEC specifications A112-A and A113-A this product requires specific storage conditions prior to surface mount assembly and as such will be supplied in vacuum sealed moisture barrier bags.

| CONDITION                                                                       | MIN                | MAX                 |

|---------------------------------------------------------------------------------|--------------------|---------------------|

| Analogue supply voltages (AVDD1 to AVDD3)                                       | AGND -0.3V         | AGND +7V            |

| Digital supply voltages (DVDD1 to DVDD4)                                        | DGND -0.3V         | DGND +7V            |

| Clock supply voltage, CVDD                                                      | CGND -0.3V         | CGND +7V            |

| Digital inputs BLCENB, CLPENB, CLPSWB, PBLK, SHD, SHP pins                      | DGND -0.3V         | DVDD2 +0.3V         |

| Digital inputs PDB, NRESET, SCK/RNW, SEN/STB, PNS, SDI/DNA, OEB, DCLK, SDO pins | DGND -0.3V         | DVDD3 +0.3V         |

| Digital outputs, D0 to D9, PTDO                                                 | DGND -0.3V         | DVDD4 +0.3V         |

| Analogue inputs and analogue outputs                                            | AGND -0.3V         | AVDD +0.3V          |

| Maximum difference between AGND, DGND and CGND                                  | - 0.1V             | +0.1V               |

| Maximum difference between DVDD1, AVDD and CVDD                                 | - 0.1V             | +0.1V               |

| Operating temperature range, T <sub>A</sub>                                     | 0°C                | +70°C               |

| Storage temperature                                                             | -65 <sup>°</sup> C | +150 <sup>°</sup> C |

| Lead temperature (soldering, 10 seconds)                                        |                    | +260 <sup>°</sup> C |

Note 1:

AGND denotes the voltage on any analogue ground pin.

DGND denotes the voltage on any digital ground pin.

CGND denotes the voltage on the clock ground pin.

For this device all GND pins should be star connected as close as possible to the device.

Note 2:

AVDD denotes the voltage on any AVDD pin.

For this device all AVDD supplies should be connected together.

#### WOLFSON MICROELECTRONICS LTD

| DEVICE       | TEMP. RANGE | PACKAGE     |

|--------------|-------------|-------------|

| XWM8170CFT/V | 0 to 70°C   | 48-pin TQFP |

# **RECOMMENDED OPERATING CONDITIONS**

## SHD/SHP = 21MHz RISET=15kW

| PARAMETER                                | SYMBOL            | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|------------------------------------------|-------------------|-----------------|------|-----|------|------|

| Supply voltage                           |                   |                 | 2.97 |     | 3.63 | V    |

| Analogue supply current - active         | IAACT             |                 |      | 68  | 80   | mA   |

| Digital supply current - active (Note 1) | I <sub>DACT</sub> |                 |      | 8   |      | mA   |

| Clock supply current - active            | ICACT             |                 |      | 6   | 10   | mA   |

| Supply current - standby (Total)         | I <sub>SDBY</sub> | SHD/SHP = 0MHz  |      |     | 10   | μA   |

### SHD/SHP = 12MHz RISET=22kW

| PARAMETER                                | SYMBOL            | TEST CONDITIONS | MIN  | TYP | MAX  | UNIT |

|------------------------------------------|-------------------|-----------------|------|-----|------|------|

| Supply voltage                           |                   |                 | 2.97 |     | 3.63 | V    |

| Analogue supply current - active         | IAACT             |                 |      | 50  |      | mA   |

| Digital supply current - active (Note 1) | Idact             |                 |      | 4   |      | mA   |

| Clock supply current - active            | I <sub>CACT</sub> |                 |      | 4   |      | mA   |

| Supply current – standby (Total)         | I <sub>SDBY</sub> | SHD/SHP = 0MHz  |      |     | 10   | μA   |

Note 1: Digital supply current - active includes DVDD4 current, which is dependent on the D[9:0] capacitive load.

# WM8170

# **PIN DESCRIPTION**

| PIN NO | NAME         | TYPE                         | DESCRIPTION                                                                         |

|--------|--------------|------------------------------|-------------------------------------------------------------------------------------|

| 1      | D5           | Digital IO                   | Data output 5/parallel data IO3                                                     |

| 2      | DGND2        | Supply                       | Digital ground for D0 to D9, PTDO pins                                              |

| 3      | DVDD4        | Supply                       | Digital supply for D0 to D9, PTDO pins                                              |

| 4      | D6           | Digital IO                   | Data output 6/parallel data IO4                                                     |

| 5      | D7           | Digital IO                   | Data output 7/parallel data IO5                                                     |

| 6      | D8           | Digital IO                   | Data output 8/parallel data IO6                                                     |

| 7      | D9           | Digital IO                   | Data output 9 (MSB)/parallel data IO7                                               |

| 8      | PTDO         | Digital output               | Programmable threshold detect output                                                |

| 9      | AGND1        | Supply                       | Analogue ground and device substrate                                                |

| 10     | AVDD1        | Supply                       | Analogue supply for ADC                                                             |

| 11     | AVDD3        | Supply                       | Analogue supply for references, bias voltage                                        |

| 12     | VCLP         | Analogue output              | Reset level clamping voltage output                                                 |

| 13     | ISET         | Analogue output              | External resistor for bias current control                                          |

| 14     | VRT          | Analogue output              | Upper ADC reference voltage output                                                  |

| 15     | VRB          | Analogue output              | Lower ADC reference voltage output                                                  |

| 16     | VMID         | Analogue output              | Midrail reference voltage output                                                    |

| 17     | AGND2        | Supply                       | Analogue ground and device substrate                                                |

| 18     | DIN          | Analogue input               | Video data input                                                                    |

| 19     | PIN          | Analogue input               | Video preset input                                                                  |

| 20     | AVDD2        | Supply                       | Analogue supply for S/H, PGA, analogue DC correction loop and                       |

|        |              |                              | auxiliary DACs                                                                      |

| 21     | SHD          | Digital input                | Sample and Hold data control                                                        |

| 22     | SHP          | Digital input                | Sample and Hold preset control                                                      |

| 23     | DVDD2        | Supply                       | Digital supply BLCENB, CLPENB, CLPSWB, PBLK, SHD, SHP pins                          |

| 24     | CLPENB       | Digital input                | Reset level clamp enable input, active low                                          |

| 25     | CLPSWB       | Digital input                | Reset level clamp enable switch, active low                                         |

| 26     | PBLK/HD      | Digital input                | Input blocking control, active low/Horizontal drive timing signal input             |

| 27     | BLCENB       | Digital input                | Black level clamp control, active low                                               |

| 28     | DGND1        | Supply                       | Digital ground for DVDD1, DVDD2, DVDD3 supplies                                     |

| 29     | PNS          | Digital input                | Parallel not serial control                                                         |

| 30     | PDB/VD       | Digital input                | External power down, active low/Vertical drive timing signal input                  |

| 31     | OEB          | Digital input                | Output enable bar, active low                                                       |

| 32     | NRESET       | Digital input                | Master chip reset, active low                                                       |

| 33     | DVDD3        | Supply                       | Digital supply for PDB, NRESET, SCK/RNW, SEN/STB, PNS, SDI/DNA, OEB, DCLK, SDO pins |

| 34     | SDO          | Digital tri-stateable output | Serial data output, tri-stateable                                                   |

| 35     | SDI/DNA      | Digital input                | Serial data in/parallel data not address (management interface)                     |

| 36     | SEN/STB      | Digital input                | Serial enable/parallel strobe (management interface)                                |

| 37     | SCK/RNW      | Digital input                | Serial clock/parallel read not write (management interface)                         |

| 38     | DCLK         | Digital input                | Output data retiming clock input                                                    |

| 39     | DVDD1        | Supply                       | Digital supply for internal logic                                                   |

| 40     | VOUT1        | Analogue output              | Auxiliary DAC1 output                                                               |

| 41     | VOUT2        | Analogue output              | Auxiliary DAC2 output                                                               |

| 42     | CVDD         | Supply                       | Positive supply for internal clock generation circuitry                             |

| 43     | CGND         | Supply                       | Ground for internal clock generation circuitry                                      |

| 44     | D0           | Digital output               | Data output 0 (LSB), tri-stateable                                                  |

| 45     | D1           | Digital output               | Data output 1, tri-stateable                                                        |

| 46     | D2           | Digital IO                   | Data output 2/parallel data IO0                                                     |

| 47     | D3           | Digital IO                   | Data output 3/parallel data IO1                                                     |

|        | <del>-</del> | 3                            |                                                                                     |

# **ELECTRICAL CHARACTERISTICS**

### **Test Characteristics**

| PARAMETER                                       | SYMBOL             | TE          | EST CONDITIONS    | MIN          | TYP      | MAX      | UNIT     |

|-------------------------------------------------|--------------------|-------------|-------------------|--------------|----------|----------|----------|

| Digital Inputs                                  |                    |             |                   |              |          |          |          |

| High level input voltage                        | V <sub>IH</sub>    |             |                   | 0.8*DVDD     |          |          | V        |

| Low level input voltage                         | VIL                |             |                   |              |          | 0.2*DVDD | V        |

| High level input current                        | IIH                |             |                   |              |          | 1        | μA       |

| Low level input current                         | IIL                |             |                   |              |          | 1        | μA       |

| Input capacitance                               | CIN                |             |                   |              | 5        |          | pF       |

| Digital Outputs                                 |                    |             |                   |              |          | <u>.</u> |          |

| High level output voltage                       | V <sub>он</sub>    |             | Іон = 1mA         | DVDD-0.6     |          |          | V        |

| Low level output voltage                        | V <sub>OL</sub>    |             | IoL = 1mA         |              |          | 0.6      | V        |

| High impedance O/P current                      | l <sub>oz</sub>    |             |                   |              |          | 1        | μA       |

| Analogue Inputs                                 |                    |             |                   |              |          | <u>.</u> |          |

| Input common mode range                         | V <sub>CMR</sub>   |             |                   | 0.3          |          | AVDD-0.3 | V        |

| 10-bit ADC Performance Inclu                    |                    | d PGA I     | Functions NO MISS | ING CODES GU | JARANTEE | D        |          |

| Resolution                                      |                    |             |                   | 10           |          |          | Bits     |

| Maximum differential non-<br>linearity          | DNL                | PG          | A at minimum gain |              |          | +/-1     | LSB      |

| Maximum integral non-<br>linearity              | INL                | PG          | A at minimum gain |              | +/-2     |          | LSB      |

| Maximum sampling rate                           | S <sub>MAX</sub>   |             |                   | 21.5         |          |          | MSPS     |

| CDS S/H                                         |                    |             |                   |              |          | <u>.</u> |          |

| Maximum input voltage for                       | VINMAX             |             | PGA = 00hex       |              |          |          |          |

| full scale ADC output                           |                    | <u>V375</u> | TIMES2            |              |          |          |          |

|                                                 |                    | 0           | 0                 |              | 1        |          | V        |

|                                                 |                    | 0           | 1                 |              | 0.5      |          | V        |

|                                                 |                    | 1           | 0                 |              | 1.5      |          | V        |

|                                                 |                    | 1           | 1                 | _            | 0.75     |          | V        |

| Minimum input voltage for full scale ADC output | V <sub>INMIN</sub> |             | PGA = FFhex       |              |          |          |          |

| scale ADC output                                |                    | <u>V375</u> | TIMES2            |              | 40       |          |          |

|                                                 |                    | 0           | 0                 |              | 40<br>20 |          | mV       |

|                                                 |                    | 1           | 0                 |              | 60       |          | mV<br>mV |

|                                                 |                    | 1           | 1                 |              | 30       | + +      | mV       |

| PGA                                             |                    | 1 '         | · ·               | 1            | 50       |          |          |

| Minimum gain                                    | G <sub>NTMIN</sub> | TI          | MES2=0, V375=1    |              | 0        |          | dB       |

| Minimum gain                                    | G <sub>TMIN</sub>  |             | MES2=1, V375=1    | 5            | 6        | 7        | dB       |

| Maximum gain                                    | G <sub>NTMAX</sub> |             | MES2=0, V375=1    | 27           | 28       | 29       | dB       |

| Maximum gain                                    | GTMAX              | _           | MES2=1, V375=1    | 33           | 34       | 35       | dB       |

| LSB step size                                   | G <sub>LSB</sub>   |             | ,                 |              | 0.11     |          | dB       |

| Resolution                                      | - 200              |             |                   | 8            | -        | 1 1      | Bits     |

| PGA maximum differential non-linearity          | P <sub>DNL</sub>   |             |                   |              |          |          | LSB      |

| PGA maximum integral non-linearity              | P <sub>INL</sub>   |             |                   |              |          |          | LSB      |

## WM8170

#### **Test Characteristics**

CVDD = AVDD = DVDD = 3.3V, AGND = DGND = CGND = 0V, RISET=15k\Omega, TA = 0°C to +70°C, unless otherwise stated.

| PARAMETER                              | SYMBOL            | TEST C                | ONDITIONS             | MIN   | TYP    | MAX           | UNIT   |

|----------------------------------------|-------------------|-----------------------|-----------------------|-------|--------|---------------|--------|

| Reset Level Clamp Switch/AC            | C Coupling Re     | sistance              |                       |       |        |               |        |

| AC coupling resistance, ON             | R <sub>CON</sub>  | AC                    | ACINP=1               |       | 50     | 70            | kΩ     |

| AC coupling resistance, OFF            | R <sub>COFF</sub> | AC                    | CINP=0                | 20    |        |               | MΩ     |

| Reset level clamp switch resistance    | R <sub>ON</sub>   |                       | ), CLPENB=0<br>PSWB=0 | 115   | 150    | 185           | Ω      |

| Black Level Clamp                      |                   |                       |                       |       |        |               |        |

| DC offset correction range             | VBLCR             | V                     | 375=1                 | 80    |        |               | mV     |

| References                             |                   |                       |                       |       |        |               | •      |

| VMID voltage                           | VMID              |                       |                       | 1.575 | 1.65   | 1.725         | V      |

| VRT - VRB, Note 1                      | Vrefl             | V                     | 375=0                 |       | 0.5    |               | V      |

| VRT - VRB, Note 1                      | Vrefh             | V                     | 375=1                 |       | 0.75   |               | V      |

| VCLP voltage referenced to             |                   | Vclp[1.0]             | <u>V375</u>           |       |        |               | 1      |

| VMID                                   | Vcooo             | 00                    | 0                     |       | -0.25  |               | V      |

|                                        | V <sub>CO10</sub> | 01                    | 0                     |       | 0      |               | V      |

|                                        | V <sub>C100</sub> | 10                    | 0                     |       | +0.25  |               | V      |

|                                        | V <sub>COO1</sub> | 0 0                   | 1                     |       | -0.375 |               | V      |

|                                        | V <sub>CO11</sub> | 0 1                   | 1                     |       | 0      |               | V      |

|                                        | V <sub>C101</sub> | 10                    | 1                     |       | +0.375 |               | V      |

| Voltage on ISET pin                    | VISET             |                       |                       | 1.203 | 1.234  | 1.265         | V      |

| VISET temperature coefficient          | VITEMP            |                       |                       |       |        |               | mV/ºC  |

| Auxiliary DACs                         |                   |                       |                       |       |        |               |        |

| Resolution                             |                   |                       |                       | 8     |        |               | Bits   |

| Maximum integral non-<br>linearity     | INL               |                       |                       |       |        | <u>+</u> 1    | LSB    |

| Maximum differential non-<br>linearity | DNL               |                       |                       |       |        | <u>+</u> 0.75 | LSB    |

| Full scale output, TIMES 2             | DFSO              |                       | JX1X1,<br><2X1 = 0    |       | AVDD   |               | V      |

| Full scale output, TIMES 1             | DFSOH             | AUX1X1,<br>AUX2X1 = 1 |                       |       | AVDD/2 |               | V      |

| Output slew rate                       | Dsr               |                       |                       |       |        |               | V/µsec |

| Output settling time                   | DTS               |                       |                       |       |        |               | μsec   |

| Load regulation                        | Dlr               |                       |                       |       |        |               | mV/mA  |

Note 1: ADC input voltage is twice VRT- VRB voltage.

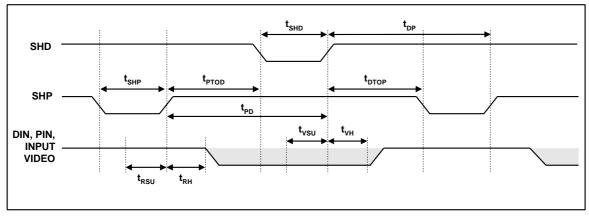

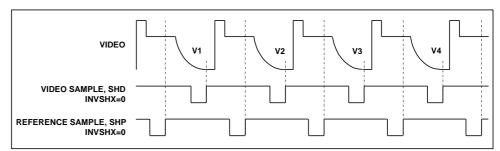

## **DETAILED TIMING DIAGRAMS**

## **INPUT VIDEO SAMPLING**

### Figure 1 Input Video Sampling Diagram

### **Test Characteristics**

| PARAMETER                                                               | SYMBOL            | TEST CONDITIONS | MIN  | TYP | MAX | UNIT |

|-------------------------------------------------------------------------|-------------------|-----------------|------|-----|-----|------|

| Input video (DIN) set-up time with reference to SHD trailing edge       | t <sub>VSU</sub>  |                 | 5    |     |     | ns   |

| Input video (DIN) hold time with reference to SHD trailing edge         | t <sub>VH</sub>   |                 | 5    |     |     | ns   |

| Reset video (PIN) set-up time<br>with reference to SHP trailing<br>edge | t <sub>RSU</sub>  |                 | 5    |     |     | ns   |

| Reset video (PIN) hold time with reference to SHP trailing edge         | t <sub>RH</sub>   |                 | 5    |     |     | ns   |

| SHD active low time                                                     | t <sub>SHD</sub>  |                 | 7.5  |     |     | ns   |

| SHP active low time                                                     | t <sub>SHP</sub>  |                 | 7.5  |     |     | ns   |

| SHP high to SHD low time                                                | t <sub>PTOD</sub> |                 | 10   |     |     | ns   |

| SHD high to SHP low time                                                | t <sub>DTOP</sub> |                 | 10   |     |     | ns   |

| SHD trailing edge to SHP trailing edge                                  | t <sub>DP</sub>   |                 | 21.4 |     |     | ns   |

| SHP trailing edge to SHD trailing edge                                  | t <sub>PD</sub>   |                 | 21.4 |     |     | ns   |

## WM8170

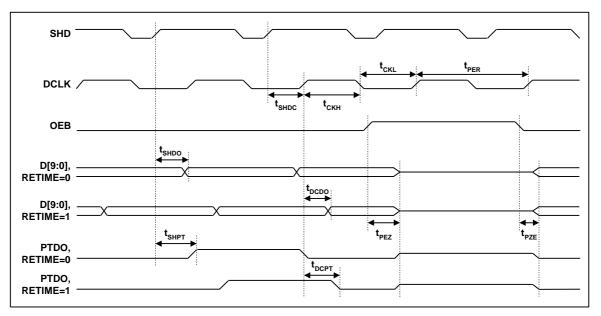

## **OUTPUT DATA**

#### Figure 2 Output Data Timing Diagram

#### **Test Characteristics**

| PARAMETER                                                                   | SYMBOL            | TEST<br>CONDITIONS | MIN  | ТҮР  | МАХ | UNIT |

|-----------------------------------------------------------------------------|-------------------|--------------------|------|------|-----|------|

| DCLK period                                                                 | t <sub>PER</sub>  |                    | 47.6 |      |     | ns   |

| DCLK high                                                                   | t <sub>CKH</sub>  |                    | 19   |      |     | ns   |

| DCLK low                                                                    | t <sub>CKL</sub>  |                    | 19   |      |     | ns   |

| Output propagation delay,<br>RETIME = 0, SHD trailing<br>edge to D[9:0] out | t <sub>SHDO</sub> |                    |      | 23.0 |     | ns   |

| Output propagation delay,<br>RETIME = 1, DCLK leading<br>edge to D[9:0] out | t <sub>DCDO</sub> |                    |      | 11.2 |     | ns   |

| Trailing edge of SHD to<br>leading edge of DCLK                             | t <sub>SHDC</sub> |                    |      |      |     | ns   |

| Output disable time, OEB<br>rising to D[9:0] and PTDO<br>tristate           | tpez              |                    |      | 8.3  |     | ns   |

| Output enable time, OEB falling to D[9:0] and PTDO out                      | t <sub>PZE</sub>  |                    |      | 6.8  |     | ns   |

| PTDO propagation delay,<br>RETIME = 0, SHD trailing<br>edge to PTDO out     | t <sub>SHPT</sub> |                    |      |      |     | ns   |

| PTDO propagation delay,<br>RETIME=1, DCLK leading<br>edge to PTDO out       | t <sub>DCPT</sub> |                    |      |      |     | ns   |

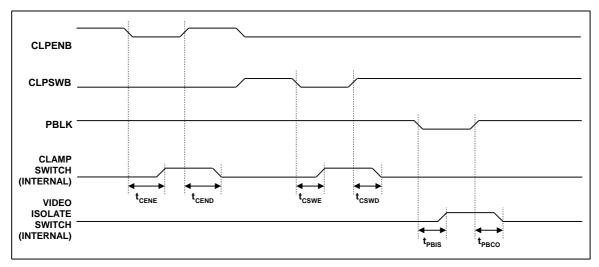

## **CLAMPING CONTROLS**

#### Figure 3 Clamping Controls Timing Diagram

#### **Test Characteristics**

CVDD = AVDD = DVDD = 3.3V, AGND = DGND = CGND = 0V, RISET=15k\Omega, TA = 0°C to +70°C, unless otherwise stated.

| PARAMETER           | SYMBOL            | TEST<br>CONDITIONS | MIN | ТҮР | MAX | UNIT |

|---------------------|-------------------|--------------------|-----|-----|-----|------|

| CLPENB enable time  | t <sub>CENE</sub> |                    |     | 4.0 |     | ns   |

| CLPENB disable time | t <sub>CEND</sub> |                    |     | 4.0 |     | ns   |

| CLPSWB enable time  | t <sub>CSWE</sub> |                    |     | 4.4 |     | ns   |

| CLPSWB disable time | t <sub>CSWD</sub> |                    |     | 5.2 |     | ns   |

| PBLK isolate time   | t <sub>PBIS</sub> |                    |     |     |     | ns   |

| PBLK connect time   | t <sub>PBCO</sub> |                    |     |     |     | ns   |

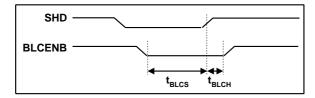

### **BLCENB INPUT**

Figure 4 BLCENB Input Timing Diagram

#### **Test Characteristics**

| PARAMETER                                  | SYMBOL            | TEST<br>CONDITIONS | MIN | TYP | MAX | UNIT |

|--------------------------------------------|-------------------|--------------------|-----|-----|-----|------|

| BLCENB setup time to SHD trailing edge     | t <sub>BLCS</sub> |                    |     |     |     | ns   |

| BLCENB hold time from<br>SHD trailing edge | t <sub>BLCH</sub> |                    |     |     |     | ns   |

## WM8170

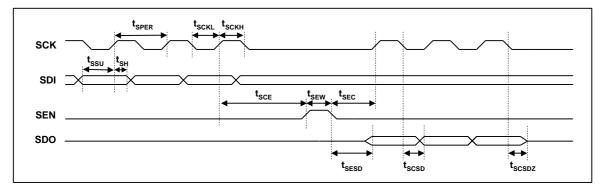

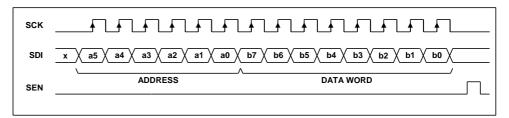

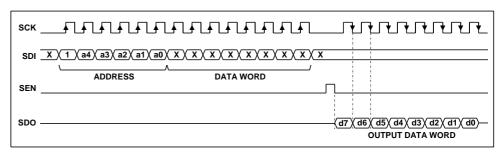

## SERIAL INTERFACE

Figure 5 Serial Interface Timing Diagram

### **Test Characteristics**

| PARAMETER                        | SYMBOL             | TEST<br>CONDITIONS | MIN  | ТҮР | MAX | UNIT |

|----------------------------------|--------------------|--------------------|------|-----|-----|------|

| SCK period                       | t <sub>SPER</sub>  |                    | 83.3 |     |     | ns   |

| SCK high                         | t <sub>scкн</sub>  |                    | 37.5 |     |     | ns   |

| SCK low                          | t <sub>SCKL</sub>  |                    | 37.5 |     |     | ns   |

| SDI set up time                  | t <sub>SSU</sub>   |                    | 10   |     |     | ns   |

| SDI hold time                    | t <sub>SH</sub>    |                    | 10   |     |     | ns   |

| SCK high to SEN high             | t <sub>SCE</sub>   |                    | 20   |     |     | ns   |

| SEN low to SCK high              | t <sub>SEC</sub>   |                    | 20   |     |     | ns   |

| SEN pulse width                  | t <sub>SEW</sub>   |                    | 50   |     |     | ns   |

| SEN low to SDO out               | t <sub>SESD</sub>  |                    |      | 9.7 |     | ns   |

| SCK low to SDO out               | t <sub>SCSD</sub>  |                    |      | 6.7 |     | ns   |

| SCK low to SDO high<br>impedance | t <sub>SCSDZ</sub> |                    |      | 20  |     | ns   |

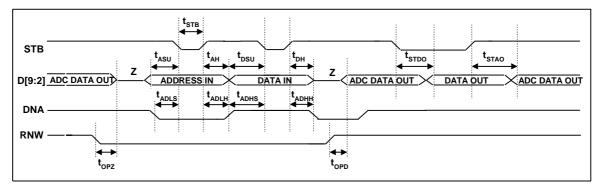

## PARALLEL INTERFACE

Figure 6 Parallel Interface Timing Diagram

### **Test Characteristics**

| PARAMETER                                    | SYMBOL            | TEST<br>CONDITIONS | MIN | ТҮР | MAX | UNIT |

|----------------------------------------------|-------------------|--------------------|-----|-----|-----|------|

| RNW low to OP[9:2] Tri-<br>state             | t <sub>OPZ</sub>  |                    |     |     | 20  | ns   |

| Address setup time to STB low                | t <sub>ASU</sub>  |                    | 0   |     |     | ns   |

| DNA low setup time to STB low                | t <sub>ADLS</sub> |                    | 10  |     |     | ns   |

| STB low time                                 | t <sub>STB</sub>  |                    | 50  |     |     | ns   |

| Address hold time from<br>STB high           | t <sub>AH</sub>   |                    | 10  |     |     | ns   |

| DNA low hold time from<br>STB high           | t <sub>ADLH</sub> |                    | 10  |     |     | ns   |

| Data setup time to STB low                   | t <sub>DSU</sub>  |                    | 0   |     |     | ns   |

| DNA high setup time to<br>STB low            | t <sub>ADHS</sub> |                    | 10  |     |     | ns   |

| Data hold time from STB<br>high              | t <sub>DH</sub>   |                    | 10  |     |     | ns   |

| DNA high hold time from<br>STB high          | t <sub>ADHH</sub> |                    | 10  |     |     | ns   |

| RNW high to OP[9:2] output                   | t <sub>OPD</sub>  |                    | 0   |     |     | ns   |

| Data output propagation delay from STB low   | t <sub>STDO</sub> |                    |     |     |     | ns   |

| ADC data out propagation delay from STB high | t <sub>STAO</sub> |                    |     |     |     | ns   |

## SYSTEM INFORMATION

The WM8170 is a complete signal processing and data acquisition system which is designed to interface directly to the analogue output of area array CCDs. The device digitises the video signals from the CCD for subsequent digital processing of the data. The WM8170 can be used in a wide range of CCD-based video applications such as digital still cameras, as shown in Figure 7.

Figure 7 Digital Still Camera System Block Diagram

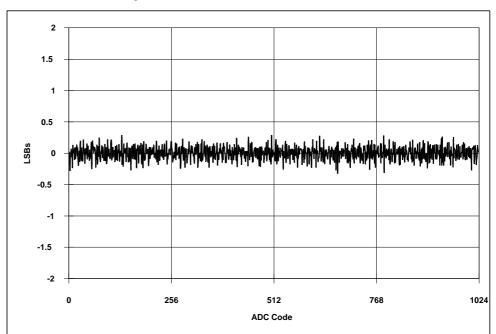

## **TYPICAL PERFORMANCE**

SHD, SHP = 21MHz, PGA gain = 0dB, VRT-VRB = 750mV, RISET =  $15K\Omega$

Figure 8 WM8170 10-bit DNL Plot

## **DEVICE DESCRIPTION**

### **GENERAL OPERATION**

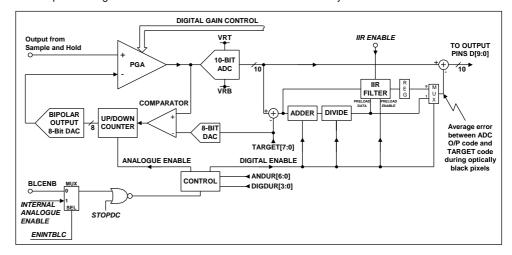

The analogue circuitry within the WM8170 consists of a Sample/Hold (S/H) block, a Programmable Gain Amplifier (PGA), a DC Offset Correction loop, and a 10-bit 21MSPS Analogue to Digital Converter (ADC). The Sample/Hold block takes a Correlated Double Sample (CDS) of the incoming video. The CDS video sample is transferred differentially into the PGA block, which is used to gain the signal to the full dynamic range of the ADC. The PGA is controlled digitally via the management interface. The 10-bit pipeline ADC takes the output from the PGA and converts the analogue voltage into a digital representation of the signal.

To correct for DC offsets in the input video, the Sample/Hold block and the PGA, DC offset correction circuitry is provided under the control of external inputs. An analogue correction loop using mixed mode circuitry removes the majority of the DC offset by summing the output of a DAC into the main signal path. An up/down counter controlled from the output of a comparator updates the DAC. The comparator checks the output from the PGA against a voltage representing the target black level. As the analogue correction loop does not correct for DC offsets in either the ADC or the comparator in the feedback loop, a further digital offset is automatically calculated within the digital section following the ADC, which forces the digital output to the previously programmed value.

Two auxiliary 8-bit DACs are provided, which can be used within the camera system to control bias voltages to the area CCD, or to provide DC voltages for peripheral camera functions, such as autofocus control.

To allow the registers within the WM8170 to be programmed a management interface is provided which allows either serial or parallel control. The interface allows the user to both write to, and read from the internal registers, which eases system debug as values previously programmed can be checked.

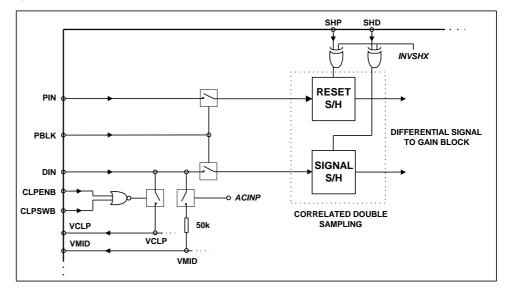

### INPUT SAMPLE AND HOLD, AND VIDEO TIMING

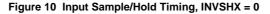

The WM8170 includes a Sample/Hold section at its input, which is used to acquire samples from the analogue output of the area array CCD. The Sample/Hold is configured as shown in Figure 9, and can be operated in a basic Sample and Hold mode or in Correlated Double Sampling (CDS) mode.

In CDS, the input video reset level is sampled under the control of the signal applied to the SHP digital input and the input video signal level is sampled under the control of the signal applied to the SHD digital input.

The Sample/Hold produces a differential voltage output signal, which is passed to the following PGA.

Detailed input timing of the Sample/Hold is shown in Figures 10 and 11. Note that there should be no overlap between the SHP and SHD pulses. Any overlap will cause the WM8170 to operate incorrectly. The WM8170 can be programmed via the management interface to accept SHP and SHD inputs as either both positive, or both negative pulses. Control of this function is via the control bit INVSHX.

### **INPUT BLANKING**

In some cases the output signals from the CCD can be larger than the input stage of WM8170 could normally handle without overload and saturation. To avoid this situation the Sample/Hold stage is preceded by a pair of analogue switches, which can be used to block the analogue input signals at PIN and DIN from passing to the Sample/Hold stage. These switches are turned on or off by placing a high or low level on the PBLK pin respectively.

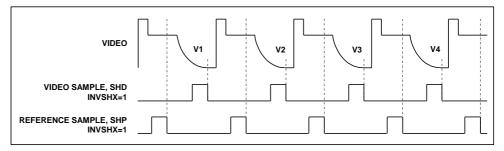

### **RESET LEVEL CLAMP OR AC COUPLING**

The input video can be interfaced via a capacitor to the WM8170 by two methods. A Reset Level Clamp facility is provided which can be used in both Sample and Hold and in CDS modes of operation. The clamp switch is closed if a low level is applied to both CLPENB and CLPSWB digital inputs. The clamp voltage, VCLP, can be programmed via the management interface to be equal to VRB, VMID, or VRT. A typical use of the Reset Level Clamp facility using CDS is shown in Figure 12.

Alternatively, the CLPENB and CLPSWB digital inputs can be tied high, which will disable the Reset Level Clamp switch, and the control bit ACINP set. This control bit connects an internal AC coupling resistor to the DIN input, which allows the user to simply AC couple the analogue video signal into the WM8170. If CDS is also used, then any drift on the WM8170 side of the coupling capacitor due to input video DC content will be removed.

Figure 11 Input Sample/Hold Timing, INVSHX = 1

Figure 12 Reset Level Clamp Timing

### **PROGRAMMABLE GAIN AMPLIFIER**

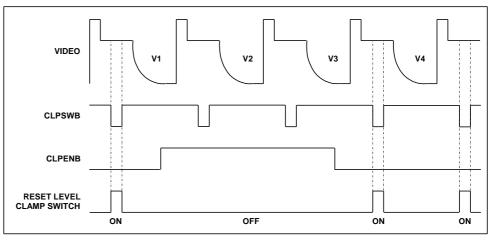

The WM8170 contains a Programmable Gain Amplifier (PGA), which precedes the analogue-todigital converter (ADC). The gain of the PGA is set digitally via the management interface to a level which delivers the maximum signal to the input of the ADC without it over ranging, and thus obtaining the maximum dynamic range from the ADC.

The gain control on the WM8170 is separated into two sections, a programmable gain section, and a fixed gain section. The programmable gain section is controlled via an 8-bit word written by the management interface, and has a typical range of between 0dB and 28dB. The gain response of the programmable gain section is linear on a logarithmic scale. This means that each LSB increase (or decrease) of digital gain setting represents an equal fraction of a dB (typically 0.11dB) of actual gain increase (or decrease).

There is also a fixed gain section, which is programmable to be either 0dB or 6dB. Setting the TIMES2 control bit via the management interface enables this additional gain.

Figure 13 shows the typical WM8170 gain response with and without the additional 6dB.

Figure 13 Graph of typical WM8170 Gain Response

### **REFERENCE VOLTAGES**

All references used on the WM8170 are derived from an internal bandgap reference voltage. The ADC uses two reference voltages, VRT and VRB. The Sample/Hold and PGA use a midrail voltage reference, VMID. The voltage for Reset Level Clamp, VCLP, can be selected to be equal to VRT, VRB or VMID. These four voltages are buffered on-chip and are each available at output pins. Each of these pins should be carefully decoupled with capacitors of the type and size detailed in the Recommended External Components section.

The voltage difference between VRT and VRB can be programmed, in order to accommodate different input signal ranges, to two values via the management interface. The WM8170 default condition is VRT-VRB typically 0.5V but can be increased to 0.75V by setting the V375 control bit. Due to the nature of the ADC design, the difference between VRT and VRB is typically half the maximum input signal which the ADC can convert successfully, i.e. if VRT-VRB is 0.75V, then the ADC can accommodate an input signal after the PGA of greater than 1.5V.

### INPUT SIGNAL AMPLITUDE

The PGA gain setting allows the WM8170 to amplify the input video signal to be equal to the fullscale input of the ADC. The minimum input video signal that can be scaled to the full-scale input of the ADC is defined when the PGA is at the maximum gain. The maximum input video signal that can be scaled to the full-scale input of the ADC is defined when the PGA is at minimum gain.

The minimum and maximum video input signal, which the WM8170 can accommodate, is set by a combination of the TIMES2 and the V375 control bits. The input video conditions are summarised in Table 1

| TIMES2 | V375 | MAXIMUM VIN FOR FULL SCALE<br>ADC INPUT<br>PGA GAIN = 00(HEX) | MINIMUM VIN FOR FULL SCALE<br>ADC INPUT<br>PGA GAIN = FF(HEX) |

|--------|------|---------------------------------------------------------------|---------------------------------------------------------------|

| 0      | 0    | 1.0V                                                          | 40mV                                                          |

| 0      | 1    | 1.5V                                                          | 60mV                                                          |

| 1      | 0    | 0.5V                                                          | 20mV                                                          |

| 1      | 1    | 0.75V                                                         | 30mV                                                          |

**Table 1 Input Signal Amplitude Conditions**

## ANALOGUE TO DIGITAL CONVERTER, DEVICE LATENCY AND OUTPUT TIMING

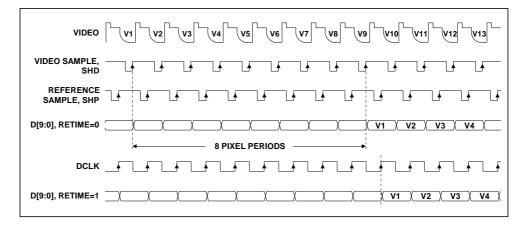

The 10-bit resolution ADC uses a pipelined architecture. The latency is the time delay between the video sample (SHD) occurring and the corresponding valid output data being available. There are two possible inputs that control the detailed timing of data output from the WM8170. These are SHD and DCLK. The selection between SHD and DCLK is dependent on the control bit RETIME. If RETIME is set low, then the output data on the D[9:0] pins is referenced to the rising edge of the SHD control input. If RETIME is set high, the output data on the D[9:0] pins is reference to the rising edge of the DCLK clock input. The use of RETIME allows the user to accurately control the output data timing, which can ease the design of the interface between the WM8170 and following digital ASIC, especially for high pixel rate systems.

With RETIME set low, the WM8170 latency is equal to eight pixel periods. With RETIME set high, the WM8170 latency is equal to eight pixel periods plus the difference in timing between SHD and DCLK. These two conditions are shown in Figure 14.

Figure 14 WM8170 Latency

### SETTING THE MAXIMUM CONVERSION RATE

The maximum conversion rate of the ADC, S/H and PGA stages within the WM8170 are directly related to the value of bias current at which the signal path operates. Within limits an increase in bias current allows an increase in maximum conversion rate to be achieved. Inserting a resistor between the ISET pin and AGND sets the value of bias current.

The value should be set to that recommended in Table 2 corresponding to the maximum conversion rate at which the device is required to operate.

Note that the higher the value of RISET the lower the power consumption of the device will be.

| RISET | MAX. CONVERSION RATE (MSPS) |

|-------|-----------------------------|

| 22kΩ  | 12                          |

| 20kΩ  | 15                          |

| 17kΩ  | 18                          |

| 15kΩ  | 21                          |

Table 2 RISET vs Maximum Conversion Rate

### BLACK LEVEL OFFSET CORRECTION CIRCUITRY

Unless compensated for, the analogue signal applied to the input of the ADC would contain unacceptably high and variable DC offsets. The offsets consist of the sum of two principal components. These are black level offsets in the output video from the CCD, which can be monitored during optically black pixel phases, and offsets from the amplifiers in the analogue signal path of the WM8170. These offsets would reduce the maximum dynamic range that the ADC can achieve and can vary significantly with time and temperature. Additionally, any DC offsets in the signal path are multiplied by the PGA gain, which can cause the internal amplifiers to limit, particularly if the gain is at a high setting.

The DC correction circuitry within the WM8170 has two distinct modes of operation.

- Basic DC correction mode

- Extended DC correction mode

The Basic mode is intended for applications where there is a large difference in the video DC value on adjacent lines in the video stream.

The Extended mode is intended for continuous time video applications, where it is necessary to track the video signal DC component without introducing any digital correction noise to the image. This mode is recommended for most of the popular area array CCDs.

### **BASIC DC CORRECTION MODE**

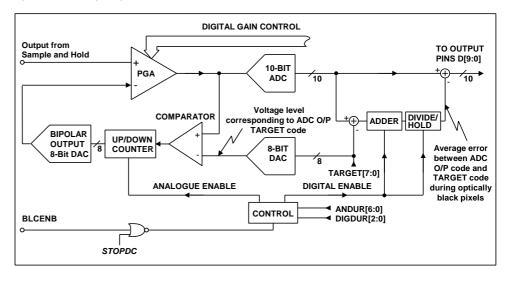

In the Basic DC correction mode, the DC offset correction is performed in two stages. There is an analogue DC correction loop that removes the majority of the offset, and a digital clamp that removes the rest. Applying a falling edge to the BLCENB digital input pin enables firstly the analogue correction loop and then the digital correction circuitry. This correction circuitry is to be used during periods when optically black pixels are being output from the CCD. The block diagram of the Basic offset correction circuitry is shown in Figure 15.

#### ANALOGUE CORRECTION LOOP

The Analogue Correction Loop functions by comparing the output from the PGA during the optically black video period with a DAC output voltage, derived from the ADC reference voltages, which corresponds to a 10-bit code which is programmable between 0 and 255 (dec). This code is the required TARGET for the WM8170 to output for optically black pixels. The output of the comparator, sampled ANDUR times per analogue enable, controls an up/down counter, the contents of which provide the input data to an 8-bit bipolar DAC. The output of this DAC is subtracted from the input of the PGA such that the PGA output becomes closer to the TARGET value programmed. Using this method the majority of any DC offset from either the input video signal, or the signal chain amplifiers is removed.

The Analogue Correction Loop does not correct for DC offsets in the ADC or the comparator in the feedback path, and is quantised, in terms of ADC codes, to the resolution of the 8-bit DAC, which changes depending on the actual PGA gain set. Therefore the resulting output code from the ADC during these optically black pixels will not be exactly equal to the TARGET value. The residual error in the black level is corrected in the digital correction circuitry.

#### DIGITAL CORRECTION CIRCUITRY IN BASIC DC CORRECTION MODE

The Digital Correction Circuitry that follows the ADC corrects for any difference between the actual ADC output code and the programmed TARGET value.

During the period when the Digital Correction Circuitry is enabled, the circuit calculates the average digital error between the programmed TARGET value and the ADC output code, over a certain number of ADC conversions. This average digital error is subsequently subtracted from all ADC conversions until the Digital Correction Circuitry is enabled again.

The number of ADC conversions that the Digital Correction Circuitry calculates the average over is programmable via the management interface. This number is set in the DIGDUR register, and is equal to 2<sup>[DIGDUR]</sup> pixel periods.

Figure 15 Basic DC Offset Correction Block Diagram

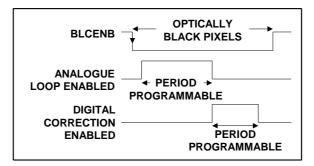

#### **BASIC DC OFFSET CORRECTION INITIATION AND TIMING**

The overall timing of the Basic DC correction algorithm is shown in Figure 16. The duration of the analogue and digital correction loops are independent. The user must ensure that the overall correction period, which is equal to the analogue loop enable time plus the Digital Correction Circuitry enable time, is no longer than the duration of the optically black pixels output from the CCD. This will prevent the potential error of active video being included in the digital average calculated within the WM8170, which would cause an incorrect error value to be stored.

Applying a falling edge to the BLCENB digital input pin enables the Analogue loop and the Digital Correction Circuitry. Once the correction has been initiated, the internal WM8170 control circuitry runs until both the analogue and digital correction enables are complete. All issues associated with latency through the WM8170 have been considered in the internal controller design.

The total period (P) of the combined Analogue Correction Loop and Digital Correction Circuitry, measured in Pixel Periods, is given by the following formula:

$P = ([ANDUR] \times 4 + 2^{[DIGDUR]})$  Pixel Periods

Where:

[ANDUR] is the contents of the Analogue Duration register ANDUR[6:0].

[DIGDUR] is the contents of the Digital Duration register DIGDUR[2:0].

The selection of ANDUR and DIGDUR values is at the discretion of the user, but the following considerations should be made. The internal up/down counter is 8-bit, which covers 256 steps. The counter is incremented/decremented ANDUR times per BLCENB falling edge, which implies that the minimum number of falling edges on BLCENB to guarantee that the analogue loop has reached its final value is 256/ANDUR. In actual use however, the change in DC conditions through the WM8170 will be relatively small, which will mean that the analogue loop will settle to the new value quicker. The value chosen for DIGDUR depends on the number of black pixels available, but a larger value means that any black pixel noise is averaged over a greater number, which will result in a more accurate error value being stored.

The analogue DC correction loop error voltage within the WM8170 is not subject to drift because it is derived from a digitally controlled DAC, which implies that once the DC correction circuitry has settled, the correction circuitry can be turned off. This can be achieved by setting the control bit STOPDC via the Management Interface. The correction circuitry should be re-enabled after any write to the PGA register so that DC change due to the different gain is accommodated for.

There are two main ways that the DC correction circuitry can be used. The BLCENB can be activated either during the optically black lines at the beginning or end of the CCD output field, or during the optically black pixels at the beginning or end of each video line. Using the first option results in the DC conditions being established before any active video is present, and since completely optically black lines are present large values can be programmed to ANDUR and DIGDUR respectfully. With the second option, smaller values for ANDUR and DIGDUR would have to be used, as the number of black pixels in each line is limited. With both options, it is recommended that the correction circuitry be enabled for one frame of video, and then turned off again.

Although the WM8170 only requires a falling edge on BLCENB to initiate the correction circuitry users may input BLCENB signals which are low for the complete duration of the optically black pixels if preferred (this signal format is generally available from CCD timing generator devices). In this case the WM8170 can be programmed to output an error flag on the PTDO pin if the BLCENB input returns to a high state before both the Analogue and Digital Enables are complete. This allows checking that the ANDUR and DIGDUR values programmed to the device will not cause a potential error in the correction circuitry because active video has been included in the internal calculations. See the Programmable Threshold Detect Output section for details of all error flags available.

## EXTENDED DC CORRECTION MODE

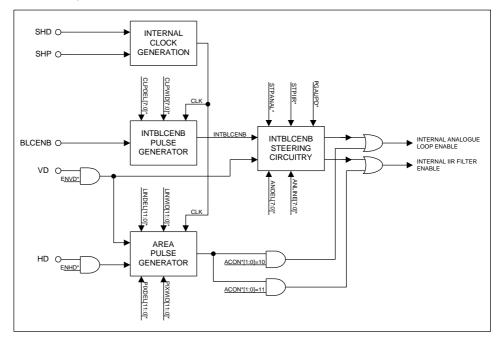

The WM8170 device has extended Black Level Correction Circuitry, which make it suitable for continuous video applications. The Black Level Clamp correction circuitry in the WM8170 consists of two main components, an Analogue correction loop which is used to remove the majority of the dc offset using analogue circuit techniques, and a digital filter which can be programmed with different filter responses. Figure 17 shows the Black Level Correction Circuitry in Detail.

#### Figure 17 Black Level Correction Circuitry

In order to control the Correction Circuitry there are two Pulse Generators incorporated within the WM8170. These Pulse Generators and their associated Control Register Bits are shown in Figure 18. This diagram shows all signals associated with the Pulse Generators. External signals are shown with a O, internal register settings with a \*. One Pulse Generator is used to generate an internal pulse relative to the falling edge of the BLCENB input. This pulse, called INTBLCENB, is then steered using the Steering Circuitry to be either the enable for the Analogue Correction Circuitry or for the Digital IIR filter. This allows the user to select which lines of the input video frame the Analogue correction loop will be enabled, and for which lines the IIR Filter will be enabled.

### Figure 18 WM8170 Pulse Generators

Following a falling edge on the Analogue Correction Loop Enable the internal circuitry is active for ANDUR\*4 pixels, which allows the majority of the DC error to be removed by the analogue circuitry. After this has completed the remaining offset is removed by a digital clamp that averages the ADC error from the programmed TARGET value for 2<sup>DIGDUR</sup> pixels and subsequently subtracts that

averaged error from all ADC conversions until the Analogue Black Level Correction circuitry is enabled again. The calculated average is also used to preload the Digital IIR Filter, so that there are no discontinuities in the correction value applied when the IIR Filter is enabled. For further details of the operation of the Analogue Correction Loop, ANDUR and DIGDUR, refer to the Basic DC Correction Mode section.

The IIR Filter allows the WM8170 to track relatively slow changes in the input video DC content across a single frame of input video. The main advantage of the IIR Filter approach is to allow the number of pixels over which the digital correction value is calculated to be much larger than the number of black pixels available on a single line. This results in a stable correction value that does not vary on a line to line basis due to the RMS noise during the black pixels.

The WM8170 also contains a second Pulse Generator that can be programmed to complement either the Analogue Loop Enable or the IIR Filter Enable as required.

#### ENABLING THE HD AND VD INPUTS TO THE WM8170

To enable the use of all the Black Level Control Circuitry within the WM8170, both the Vertical Drive (VD) and the Horizontal Drive (HD) control signals are required from the CCD Timing Generator device. There are two dual mode pins on the WM8170 which are programmed via the Management Interface register bits ENVD and ENHD. Details of the dual mode pins are covered in the Tables 3 and 4:

| ENVD | FUNCTION                             |

|------|--------------------------------------|

| 0    | Pin 30 is PDB (Power Down Bar) Input |

| 1    | Pin 30 is VD (Vertical Drive) Input  |

#### Table 3 ENVD control bit operation

| Ī | ENHD | FUNCTION                              |

|---|------|---------------------------------------|

|   | 0    | Pin 26 is PBLK (Video Blocking) Input |

|   | 1    | Pin 26 is HD (Horizontal Drive) Input |

#### Table 4 ENHD control bit operation

When ENVD is set, PDB is held high internally in the WM8170. The Power Down Function remains available via the Management Interface. When ENVD is reset, the internal circuitry requiring Vertical Drive will not function.

When ENHD is set, PBLK is held high internally in the WM8170. The Video Blocking function is not available in this mode. When ENHD is reset, the internal circuitry requiring Horizontal Drive will not function.

#### INTERNAL BLACK LEVEL CLAMP ENABLE

The control for the Analogue Correction Loop can be programmed to be either the BLCENB pin, or the INTBLCENB signal under control of the register bit ENINTBLC. To benefit from the extended Black Level Control Circuitry within the WM8170 this bit must be set. Table 5 shows the operation of the ENINTBLC control bit.

| ENINTBLC | FUNCTION                                                                                             |

|----------|------------------------------------------------------------------------------------------------------|

| 0        | Analogue Loop Enable is controlled by BLCENB pin directly.                                           |

| 1        | Analogue Black Level Enable is controlled by the signals generated by the INTBLCENB Pulse Generator. |

#### Table 5 ENINTBLC control bit operation

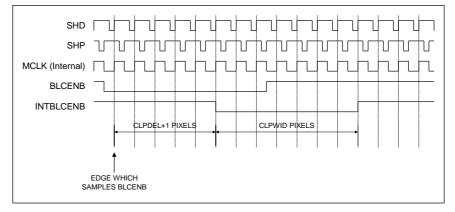

#### **BLCENB CONTROLLED PULSE GENERATOR**

The internal master clock derived from the SHP and SHD digital inputs clocks the INTBLCENB pulse generator. The pulse generator is controlled by the BLCENB input, and is used to generate an internal pulse that is timed relative to the falling edge of the BLCENB input. This pulse can be selectively used to control either the analogue control loop or the IIR filter. The Pulse Steering Circuit is reset by a falling edge on the VD input so that the user can determine which video lines will enable the Analogue Correction Circuitry and which will enable the IIR Filter.

Enabling the analogue DC correction circuitry is required to remove the majority of the offset from the incoming video. The value of this offset at the input to the ADC is dependent on the gain of the PGA, hence the analogue DC correction circuitry should be enabled either at the beginning of each frame, or only when the PGA gain is changed.

Figure 19 shows the generation of the INTBLCENB pulse relative to the falling edge of the BLCENB pin. There are two Management Interface registers that control the generation of the INTBLCENB signal. CLPDEL[7:0] defines the delay in pixel periods from the falling edge of BLCENB pin to the falling edge of the INTBLCENB signal. The delay is equal to CLPDEL+1 pixels. CLPWID[7:0] defines the width of the INTBLCENB signal. The width of the signal is CLPWID pixels.

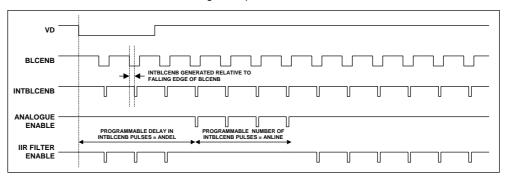

#### Figure 19 Generating the INTBLCENB Pulse STEERING THE INTBLCENB SIGNAL

Figure 20 shows how the INTBLCENB signal can be steered to either the Analogue Loop Enable, or to the IIR Filter Enable. There are two Management Interface Registers which control how the INTBLCENB signal is steered. ANDEL[7:0] defines the delay in INTBLCENB pulses from the falling edge of the VD input. The INTBLCENB pulses during this period are steered to the IIR Filter. The delay is equal to ANDEL. ANLINE[7:0] is defines the number of INTBLCENB pulses steered to the Analogue Loop Enable. The number is equal to ANLINE. The INTBLCENB pulse is steered to the IIR Filter whenever it is not used for the Analogue Loop Enable.

#### Figure 20 Steering the INTBLCENB Signal

The steering circuitry allows the user to select which lines of the input video the analogue DC correction loop will be enabled for, and to place these lines in a non viewed section of the frame. The lines which have the analogue DC correction loop enabled will be subject to line noise due to the correction value that is being applied only having been calculated over only a small number of pixels. The effect of line noise during the analogue loop enables can be minimized if a large number of pixels are used to calculate the digital average. This can be achieved if the analogue loop is enabled during the optically black lines at the beginning of a video frame.

#### CONTROLLING THE BLACK LEVEL CLAMP CIRCUITRY

There are three Management Interface control bits that are associated with the INTBLCENB pulse generator, STPANAL, STPIIR, and PGAUPD. Their function is shown in Tables 6, 7 and 8:

| STPANAL | FUNCTION                                                                                                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Allows the INTBLCENB signal to be steered to the Analogue DC correction Loop.                                                                                                                               |

| 1       | Disables the INTBLCENB signal from being steered to the Analogue DC correction Loop. The INTBLCENB pulses that would have been steered to the Analogue Enable are steered to the IIR Filter enable instead. |

#### Table 6 STPANAL control bit operation

| STPIIR | FUNCTION                                                           |

|--------|--------------------------------------------------------------------|

| 0      | Allows the INTBLCENB signal to be steered to the IIR Filter        |

| 1      | Disables the INTBLCENB signal from being steered to the IIR Filter |

Table 7 STPIIR control bit operation

| PGAUPD | FUNCTION                                                                                                                                 |

|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | The INTBLCENB signal will be steered to the Analogue DC correction loop as programmed on every frame.                                    |

| 1      | The INTBLCENB signal will only be steered to the Analogue DC correction loop as programmed if the PGA gain register has been written to. |

#### Table 8 PGAUPD control bit operation

The PGAUPD control bit enables the internal WM8170 circuitry to steer the INTBLCENB signals to the Analogue Control Loop for one frame only following a write to the PGA Gain register. The INTBLCENB signals will be steered to the IIR Filter on all other frames. This implies that there will only be ANLINE lines subject to line noise, only for a single video frame, and only if the PGA gain register has been written to. If the PGAUPD control bit has not been set, then the INTBLCENB signals will be steered to the Analogue Control Circuitry on every frame.

#### SETTING THE IIR FILTER COEFFICIENT

Writing to the COEFF register controls the IIR filter response. Table 9 shows the coefficients available on the WM8170, and the effective attenuation of the RMS noise during the optically black pixels that will be present on the calculated error.

| COEFF<br>REGISTER<br>VALUE | IIR<br>FILTER<br>COEFF | RMS Noise<br>Attenuation<br>(dB) | RMS Noise<br>Attenuation<br>(Times) | 10%  | 1.0%  | 0.1%   |

|----------------------------|------------------------|----------------------------------|-------------------------------------|------|-------|--------|

| 000                        | 5                      | 18.0                             | 7.9                                 | 72   | 334   | 2307   |

| 001                        | 6                      | 21.0                             | 11.3                                | 146  | 673   | 4651   |

| 010                        | 7                      | 24.1                             | 16.0                                | 293  | 1352  | 9339   |

| 011                        | 8                      | 27.1                             | 22.6                                | 588  | 2709  | 18714  |

| 100                        | 9                      | 30.1                             | 32.0                                | 1177 | 5423  | 37466  |

| 101                        | 10                     | 33.1                             | 45.2                                | 2356 | 10853 | 74969  |

| 110                        | 11                     | 36.1                             | 64.0                                | 4714 | 21711 | 149976 |

| 111                        | 12                     | 39.1                             | 90.5                                | 9430 | 43427 | 299988 |

#### **Table 9: IIR Filter Coefficients**

The 10%, 1.0% and 0.1% columns give the number of pixels that the IIR filter has to be enabled for to achieve the percentage settling, i.e. if the input has a 100LSB step then the number of pixels required for the filter to settle to 1LSB is equal to the number in the 1% column. For example, if the filter coefficient is set to 7, and the input has a 100LSB step, it will require 1352 enabled pixels for the filter to settle to 1LSB of the final error value. There is a trade-off between the number of pixels required for the filter to settle, and the RMS noise attenuation achieved on the calculated error value.

## **INTERNAL AREA PULSE GENERATOR**

In addition to the INTBLCENB pulse generator described above, the WM8170 includes an independent pulse generator which can be use to define any area within the video frame. The output of the Area Pulse Generator can be used either independently of the INTBLCENB pulse (if the BLCENB pulse generator is turned off using the STPANAL and STPIIR control bits), or to define additional areas where the user wishes either the Analogue Control Loop or the IIR filter to operate.

This pulse generator works in a similar way to the pulse generator described above, but uses the Vertical Drive (VD) and Horizontal Drive (HD) inputs, along with the Master Clock, to allow the user to define any area within the active video signal.

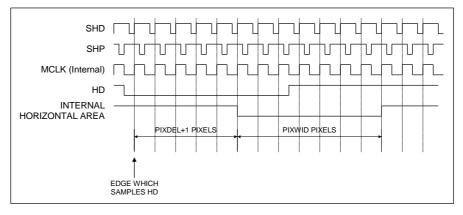

The horizontal area enable operates as shown in Figure 21. The Management Interface registers PIXDEL[11:0] and PIXWID[11:0] are used to define the pulse. The horizontal Area Pulse will have a delay of PIXDEL+1 pixels from the falling edge of the HD input, and will be PIXWID pixels wide.

#### Figure 21 Generating the Horizontal Area Pulse

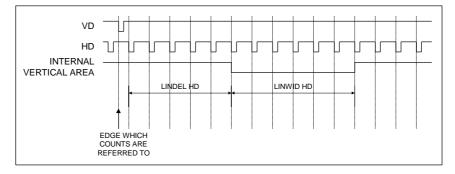

The vertical area enable operates as shown in Figure 22. The Management Interface registers LINDEL[11:0] and LINWID[11:0] are used to define the pulse. The Vertical Area Pulse will have a delay of LINDEL HD pulses from the falling edge of the VD input, and will be LINWID HD pulses wide.

#### Figure 22 Generating the Vertical Area Pulse

The logical combination of the active low, horizontal area pulse and the active low, vertical area pulse is used to define the area of the input video required.

#### USING THE AREA PULSE GENERATOR

The area defining pulse can be used under control of the ACON register bits to enable various functions as detailed in the Table 10:

| ACON1 | ACON0 | FUNCTION                                                                                                                                                                                                                                                            |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | 0     | Area define signal turned off.                                                                                                                                                                                                                                      |

| 0     | 1     | Area define signal used to update the internal register<br>which holds the error calculated by the IIR filter. In other<br>conditions the internal register which holds the error<br>calculated by the IIR filter is enabled whenever the IIR filter<br>is enabled. |

| 1     | 0     | Area Define signal used to enable the Analogue DC<br>Correction circuitry in addition to the analogue enable<br>generated from the INTBLCENB pulse generator.                                                                                                       |

| 1     | 1     | Area Define signal is used to enable the IIR filter in addition<br>to the IIR filter enable generated from the INTBLCENB<br>pulse generator.                                                                                                                        |

Table 10 ACON[1:0] control bits operation

### VIEWING THE INTERNALLY GENERATED PULSES ON THE PTDO PIN

For system debug purposes all the internally generated pulses can be multiplexed onto the PTDO signal pin, under control of the PTDO[2:0] register bits as described in the Table 11:

| PTDO2 | PTDO1 | PTDO0 | PTDO PIN FUNCTION                                                                                                                                                   |  |

|-------|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0     | 0     | 0     | Programmable Threshold Detect Output                                                                                                                                |  |

| 0     | 0     | 1     | ADC Out of Range Signal                                                                                                                                             |  |

| 0     | 1     | 0     | Clip 1 Error – Digital correction error (ADC output is outside the digital correction range)                                                                        |  |

| 0     | 1     | 1     | BLCENB Error – caused by BLCENB going<br>high before the internal DC offset correction<br>circuitry associated with the analogue DC<br>correction loop has finished |  |

| 1     | 0     | 0     | Active low going, analogue DC loop enable pulse                                                                                                                     |  |

| 1     | 0     | 1     | Active low going, IIR enable pulse                                                                                                                                  |  |

| 1     | 1     | 0     | Active low going, Area Define pulse                                                                                                                                 |  |

| 1     | 1     | 1     | Reserved for Test Purposes                                                                                                                                          |  |

Table 11 PTDO[2:0] control bits operation

## PROGRAMMABLE THRESHOLD DETECT OUTPUT

The Programmable Threshold Detect Output, (PTDO), primary function is to indicate to the user when the ADC output has exceeded a value programmed into the THRES[9:0] registers via the Management Interface. The PTDO output will output a high state, which is aligned to the output data, if the ADC output exceeds the programmed value. Typically this pin would be used in conjunction with external gain calibration algorithms to set the PGA gain.

The PTDO output can also be used to indicate a number of system error flags which are available to the user. These flags are multiplexed onto the PTDO pin under control of the Management Interface.

An error can be flagged if the pixel data during the black pixels is outside the correction range of the logic within the WM8170, or if the BLCENB pin has returned high before both the analogue and digital DC correction circuitry has completed their tasks. An error can also be flagged if the output from the ADC is out of range, i.e. the ADC output code is trying to exceed 3FF(hex), or be less than 0(hex).

The error flag can be programmed to be output on the PTDO pin under control of the register bits PTDO[1:0].

## AUXILIARY DIGITAL TO ANALOGUE CONVERTERS

The WM8170 includes two independent 8-Bit Digital to Analogue Converters. Their analogue outputs are available at pins VOUT1 and VOUT2 respectively. Their output voltages are controlled in two ways. The maximum output voltage from the DACs can be independently set to be either AVDD or AVDD/2 under control of the AUX1X1 and AUX2X1 control bits. Each DAC can then be programmed to one of 256 codes by the 8-bit contents of the Auxiliary DAC registers defined in the register map shown in Table 15.

These DACs can be used to trim CCD control voltages such as the anti-blooming or reset gate bias voltages, or used within the camera system for features such as auto-focus.

### MANAGEMENT INTERFACE

The WM8170 includes an easy-to-use and comprehensive Management Interface that allows the user to write to and read from on-board registers and thus control all the digitally programmable features of the device. The Management Interface can be configured to operate in either Parallel or Serial Mode by setting the Parallel Not Serial (PNS) pin high or low respectively. Serial Mode is recommended for real time video applications because writing and reading from the device can be carried out at any time. If Parallel Mode is used, writing and reading must be performed within areas of inactive video to prevent valid ADC output data from being replaced with the Management Interface data.

### MANAGEMENT INTERFACE CONFIGURATION

The pins used to control the Management Interface are described in Table 12.

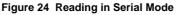

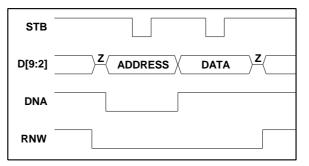

The timing for writing in Serial and Parallel Mode is shown in Figures 23 and 24 respectively.

Selected registers can also be read via the interface thus allowing stored values to be checked by the user. The timing for reading in Serial and Parallel Mode is shown in Figures 25 and 26 respectively.

| PIN NAME | SERIAL MODE FUNCTION                    | PARALLEL MODE FUNCTION                |

|----------|-----------------------------------------|---------------------------------------|

| PNS      | Set Low to indicate Serial<br>Mode      | Set High to indicate Parallel Mode    |

| SEN/STB  | Serial interface ENable, active<br>High | Parallel interface STrobe, active Low |

| SDI/DNA  | Serial Data Interface                   | Data Not Address input                |

| SCK/RNW  | Serial interface Clock                  | Read Not Write input                  |

| SDO      | Serial Data Out                         | Not Used                              |

| D2-D9    | Not Used                                | Parallel data I/O pins                |

Table 12 Management Interface Pins and Functions

Figure 23 Writing in Serial Mode

Figure25 Writing in Parallel Mode

Figure 26 Reading in Parallel Mode

### **POWER DOWN CONTROL**

The WM8170 includes a separate power down pin, PDB. When this pin is taken low the whole device is powered down and all internal registers maintain their currently programmed value. Setting the PD0 bit in the Power Down 1 register can perform a similar power down operation. These two global power downs are logically OR'd.

In addition to the above power down facilities the WM8170 contains seven other selective power downs of individual sections of the device. Setting the appropriate bit in the Power Down 2 register, as described in the Device Configuration section of this data sheet, will power down the particular part of the circuit. These bits are logically ANDed so that any combination of the available device sections can be powered down simultaneously

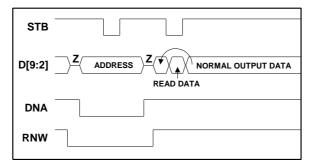

### **POWER SUPPLIES**