TDAT021G2 Просмотр технического описания (PDF) - Agere -> LSI Corporation

Номер в каталоге

Компоненты Описание

производитель

TDAT021G2 Datasheet PDF : 310 Pages

| |||

TDAT042G5 Device Advisory

for Version 1 and 1A of the Device

Advisory

May 2001

UTOPIA (UT) (continued)

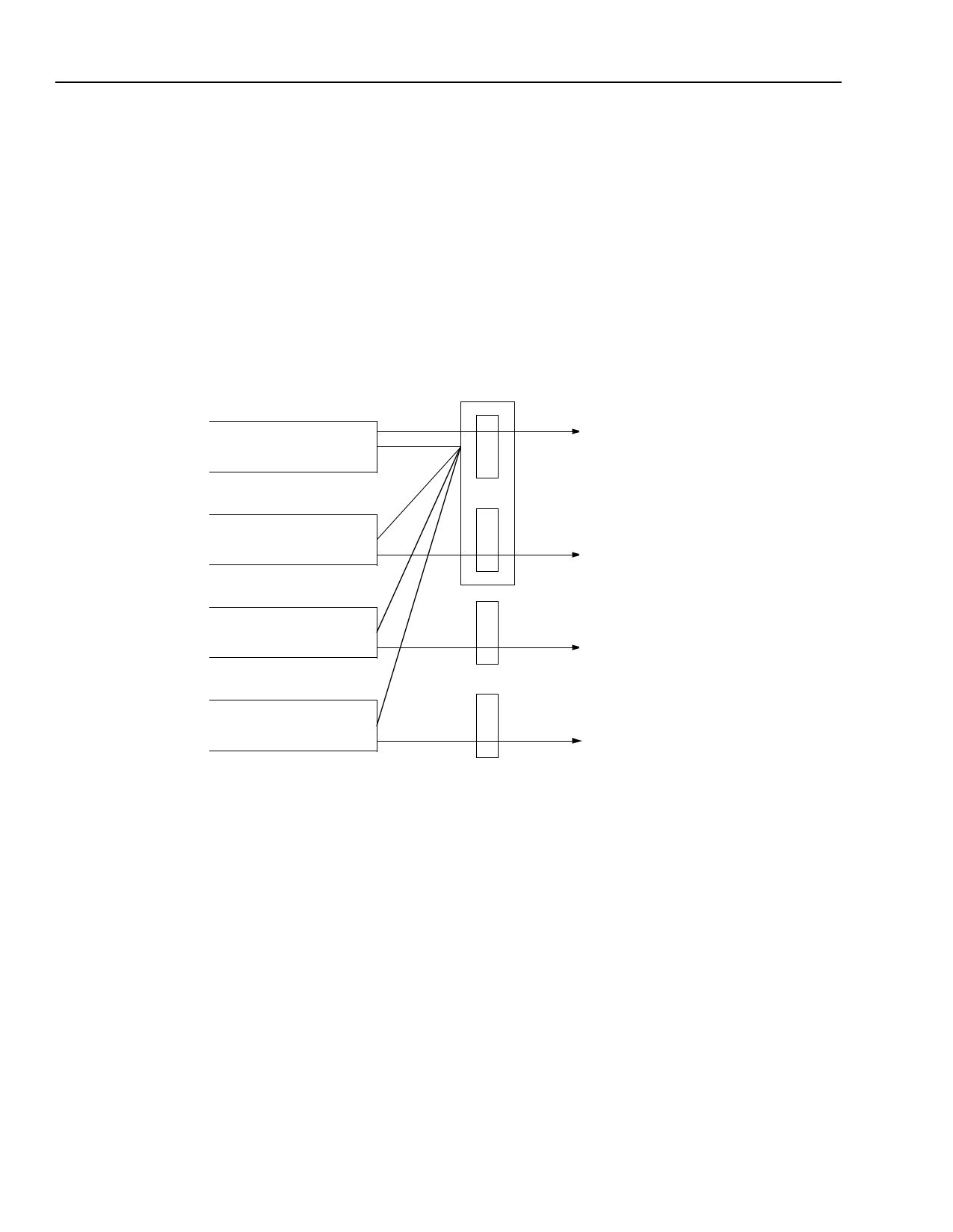

UT14. Nonfunctional RxPA Signal for Channels B and D in Packet Direct Status MPHY Mode

When using MPHY direct status for all operational modes (8-bit, 16-bit, and 32-bit), the RxPA signal for channels B

and D is not functional. The RxPA signal is functional only for channels A and C.

Workaround

The TDAT UTOPIA interface currently has nonfunctioning RxPAB and RxPAD output signals when used in four-

channel Multi-PHY mode as shown in Figure 1. The result of this problem is the unavailability of direct status polling

on the receive-side UTOPIA interface. To work around this problem, the following analysis is done to aid the user in

doing a round-robin data extraction procedure.

INGRESS CHANNEL A FIFO

256 bytes DEEP

INGRESS CHANNEL B FIFO

256 bytes DEEP

RXPAA

A

32-bit INTERFACE (A AND B)

B

X

RXPAB

INGRESS CHANNEL C FIFO

256 bytes DEEP

C

RXPAC

INGRESS CHANNEL D FIFO

256 bytes DEEP

D

X

RXPAD

Figure 1. Receive-Side UTOPIA Interface and Channel FIFOs

1664 (F)

The rate at which data fills and drains the receive-side UTOPIA FIFOs is calculated as follows:

I The data enters each UTOPIA FIFO from the data engine bytewise running on a 77.76 MHz system clock.

I If we assume each channel (worst case) is filled with an STS-12c rate signal, then the amount of data (excluding

SONET overhead, both section/line, path, and three stuff columns) per second is

(87 x12 x 9 x 8000) – (4 x 9 x 8000) = 74.88 Mbytes/STS-12c/s or 599.040 Mbits/STS-12c/s.

I Since each FIFO contains a maximum of 256 bytes/FIFO, it takes on average

(256/74,880,000) = 3.4188 µs to fill a FIFO, and with a clock cycle of 77.76 MHz, it requires as a worst case,

3.2922 µs to fill the FIFO.

I Since there are four FIFOs all receiving data at 74.88 Mbytes/s, then the total bandwidth requirements of all four

channels combined is (4 x 74,880,000) = 299.52 Mbytes/s.

I The servicing rate on each FIFO is based on the UTOPIA interface width and frequency. If we assume a

32-bit A/B UTOPIA interface operating at 100 MHz, then the service rate is 400 Mbytes/s to service all the

channels.

18

Agere Systems Inc.