MT90863AG1 Просмотр технического описания (PDF) - Mitel Networks

Номер в каталоге

Компоненты Описание

производитель

MT90863AG1 Datasheet PDF : 35 Pages

| |||

MT90863

Advance Information

Pin Description (continued)

128 MQFP

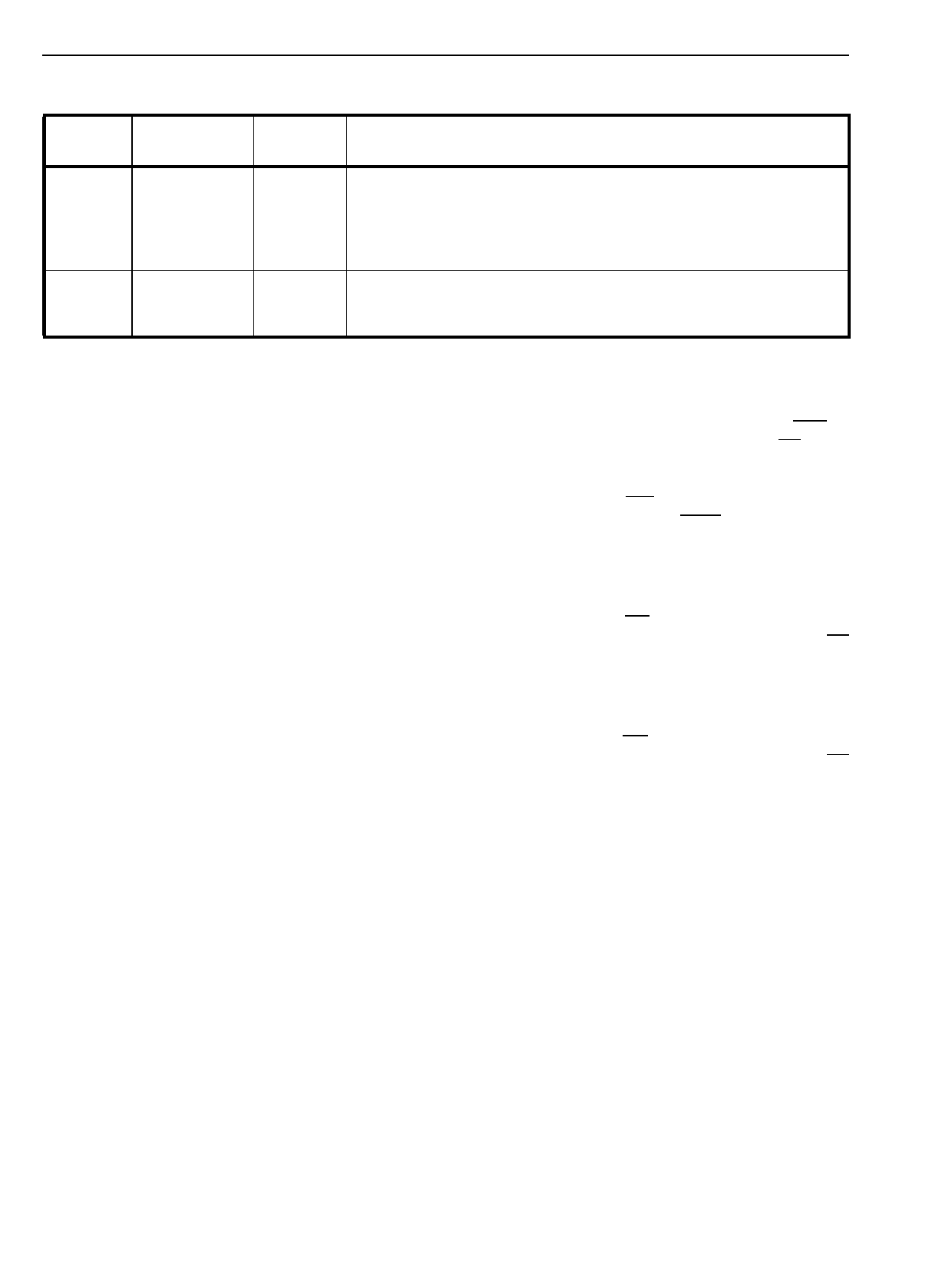

Pin#

144 BGA

Pin#

Name

Description

84

E12

STo12 Serial Output Streams 12 (5V Tolerant Three-state Output): In

2Mb/s mode, this output has data rate of 2.048Mb/s with 32 channels

per stream. In Sub-rate Switching mode, this pin has data rate of

2.048Mb/s with 128 channels per stream for Sub-rate switching

application.

85-87

D13, E11, C13 STo13 - 15 Serial Output Streams 13 to 15 (5V Tolerant Three-state Outputs):

In 2Mb/s mode, these outputs have a data rate of 2.048Mb/s with 32

channels per stream.

Device Overview

The Rate conversion Switch (MT90863) can switch

up to 2,048 × 512 channels while also providing a

rate conversion capability. It is designed to switch 64

kb/s PCM or N X 64 kb/s data between the

backplane and local interfaces. When the device is in

the sub-rate switching mode, 2-bit wide 16 kb/s data

channels can be switched within the device. The

device maintains frame integrity in data applications

and minimum throughput delay for voice application

on a per channel basis.

The backplane interface can operate at 2.048, 4.096

or 8.192 Mb/s, arranged in 125µs wide frames that

contain 32, 64 or 128 channels, respectively. A built-

in rate conversion circuit allows users to interface

between backplane interface and the local interface

which operates at 2.048 Mb/s or 8.192 Mb/s.

By using Mitel’s message mode capability, the

microprocessor can access input and output time-

slots on a per channel basis. This feature is useful

for transferring control and status information for

external circuits or other ST-Bus devices.

The frame offset calibration function allows users to

measure the frame offset delay for streams STio0 to

STio23. The offset calibration is activated by a frame

evaluation bit in the frame evaluation register. The

evaluation result is stored in the frame evaluation

registers and can be used to programme the input

offset delay for individual streams using internal

frame input offset registers.

Functional Description

A functional Block Diagram of the MT90863 is shown

in Figure 1. One end of the MT90863 is used to

interface with backplane applications, such as

HMVIP or H.100 environments, while the other end

supports the local switching environments.

Frame Alignment Timing

The Device Mode Selection (DMS) register allows

users to select three different frame alignment timing

modes. In ST-BUS modes, the master clock (C16i) is

always at 16.384 MHz. The frame pulse (F0i) input

accepts a negative frame pulse at 8kHz. The frame

pulse goes low at the frame boundary for 61ns. The

frame pulse output F0o provides a 244ns wide

negative frame pulse and the C4o output provides a

4.094MHz clock. These two signals are used to

support local switching applications. See Figure 4 for

the ST-BUS timings.

In CT Bus mode, the C4i/C8i pin accepts 8.192MHz

clock for the CT Bus frame pulse alignment. The F0i

is the CT bus frame pulse input. The CT frame pulse

goes low at the frame boundary for 122ns. See

Figure 5 for the CT Bus timing.

In HMVIP mode, the C4i/C8i pin accepts 4.096MHz

clock for the HMVIP frame pulse alignment. The F0i

is the HMVIP frame pulse input. The HMVIP frame

pulse goes low at the frame boundary for 244ns. See

Figure 6 for the HMVIP timing.

Table 1 describes the input timing requirements for

ST-BUS, CT Bus and HMVIP modes.

Switching Configuration

The device has four operation modes for the

backplane interface and three operation modes for

the local interface. These modes can be

programmed via the Device Mode Selection (DMS)

register. Mode selections between the backplane

and local interfaces are independent. See Table 2

and Table 3 for the selection of various operation

modes via the programming of the DMS register.

6