GS9090 –ü—Ä–æ—Å–º–æ—Ç—Ä —Ç–µ—Ö–Ω–∏—á–µ—Å–∫–æ–≥–æ –æ–ø–∏—Å–∞–Ω–∏—è (PDF) - Gennum -> Semtech

–ù–æ–º–µ—Ä –≤ –∫–∞—Ç–∞–ª–æ–≥–µ

–ö–æ–º–ø–æ–Ω–µ–Ω—Ç—ã –û–ø–∏—Å–∞–Ω–∏–µ

–ø—Ä–æ–∏–∑–≤–æ–¥–∏—Ç–µ–ª—å

GS9090 Datasheet PDF : 70 Pages

| |||

GS9090 Data Sheet

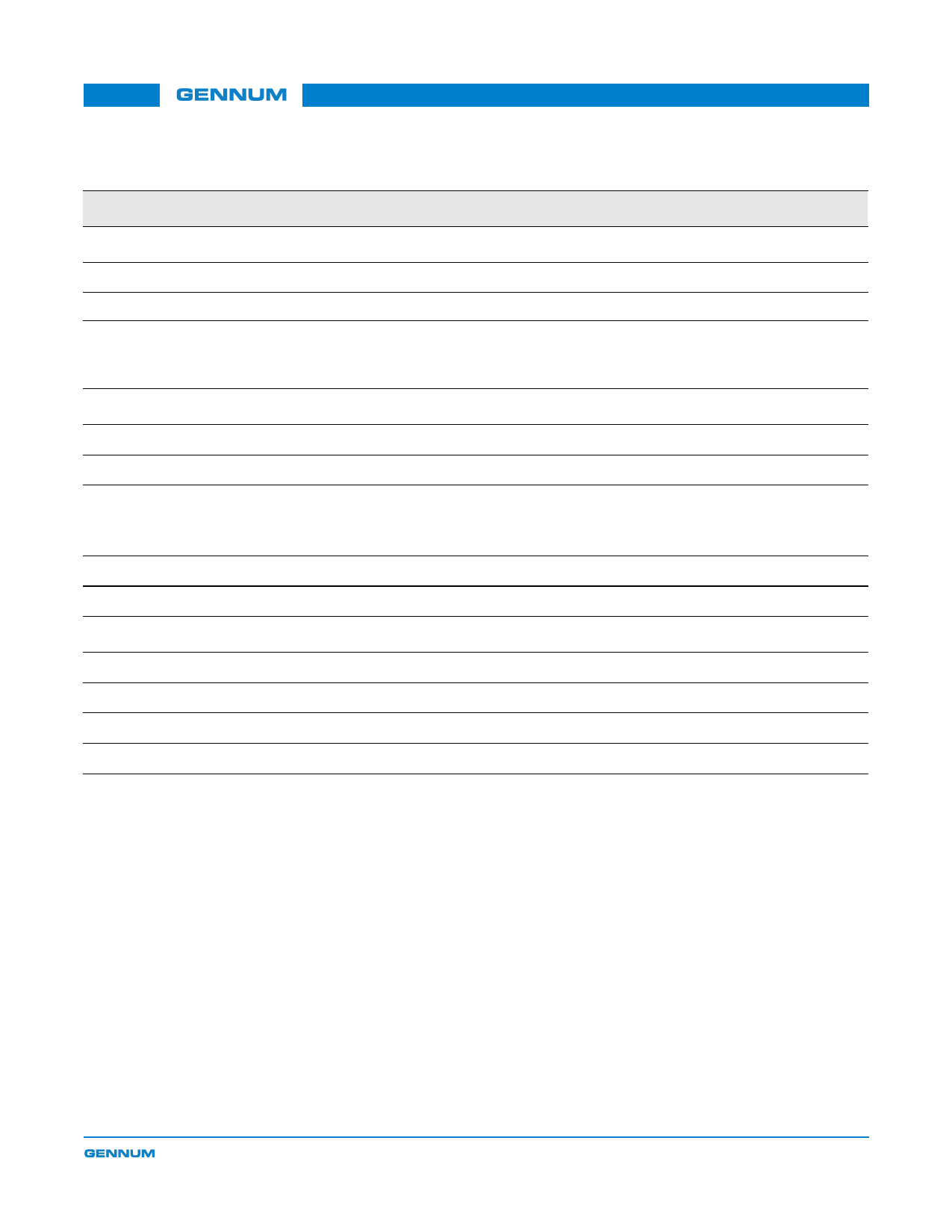

Table 2-3: AC Electrical Characteristics (Continued)

VDD = 1.8V, TA = 0°C to 70°C, unless otherwise specified.

Parameter

Symbol Condition

Min

Typ

Max Units Notes

Serial Digital Input

Serial Input Data Rate

Serial Input Jitter Tolerance

Serial Digital Input Signal Swing

Parallel Output

Parallel Output Clock Frequency

Parallel Output Clock Duty Cycle

Variation of Parallel Output Clock

(from 27MHz)

Output Data Hold Time

Output Delay Time

GSPI

DRSDI

IJT

ΔVDDI

–

–

Differential with

internal 100Ω input

termination

fPCLK

DCPCLK

–

tOH

tOD

–

–

Device Unlocked

TA = -20°C to +85°C

IO_VDD = 1.8V

With 15pF load

With 15pF load

–

270

–

Mb/s

–

–

0.4

–

UI

2

400

800

1700

mVp-p

3

–

27

–

MHz

–

40

–

60

%

–

-7.5

–

+7.5

%

4

3.0

–

–

ns

5

–

–

10.0

ns

5

GSPI Input Clock Frequency

fGSPI

–

–

–

54.0

MHz

–

GSPI Clock Duty Cycle

DCGSPI

–

40

–

60

%

–

GSPI Setup Time

tGS

–

1.5

–

–

ns

–

GSPI Hold Time

tGH

–

–

–

1.5

ns

–

NOTES:

1. No signal to signal present, or a switch from another data rate to 270Mb/s.

2. Power supply noise 50mVpp at 15kHz, 100kHz, 1MHz sinusoidal modulation.

3. See Figure 2-1.

4. When the serial input to the GS9090 is removed, the PCLK output signal will continue to operate at 27MHz and the internal VCO will

remain at this frequency within +/- 7.5% over the range -20oC to +85oC.

5. Timing includes the following outputs: DOUT[9:0], STAT[3:0]. When the FIFO is enabled, the outputs are measured with respect to

RD_CLK.

28201 - 1 July 2005

14 of 70