IP101ALF-DS-R03 Просмотр технического описания (PDF) - Unspecified

Номер в каталоге

Компоненты Описание

производитель

IP101ALF-DS-R03 Datasheet PDF : 36 Pages

| |||

IP101A LF

Data Sheet

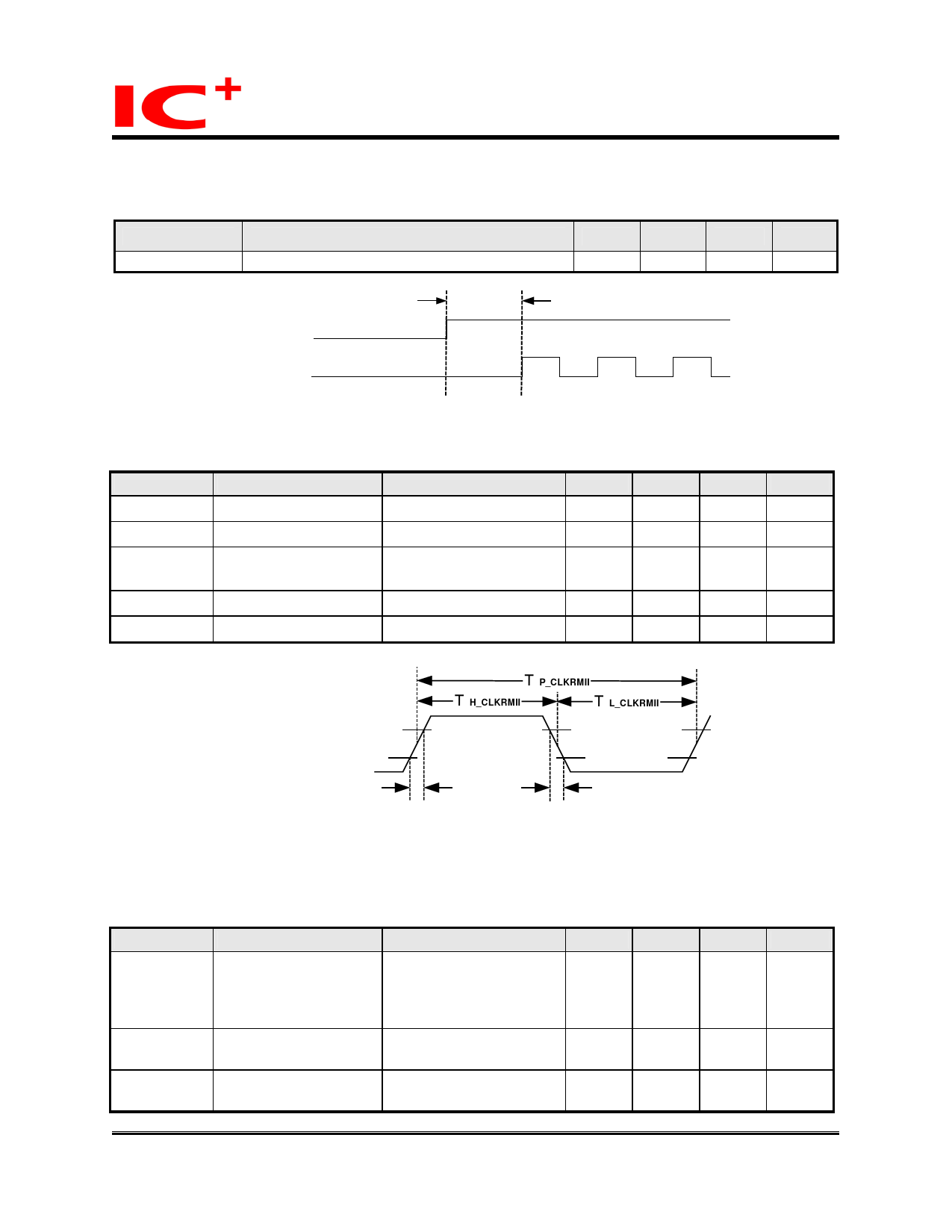

7.2.2 RMII Timing

a. Pin Reset and Clock output timing relationship (If pin 16 has been configured as 50MHz output )

Symbol

Tdelay

Description

Delay time after reset to clock output

Min. Typ. Max. Unit

-

40

-

us

RESET_N

Tdelay

C50M_O

b. Clock Timing RMII

Symbol

TR_CLKRMII

TF_CLKRMII

TP_CLKRMII

Description

REFCLK Rise time

REFCLK Fall time

REFCLK Period

TH_CLKRMII

TL_CLKRMII

REFCLK High

REFCLK Low

Notes

VIL (max) to VIH (min)

VIH (min) to VIL (max)

Min

-

-

8.0

8.0

Typ Max

-

3.0

-

3.0

20.0 ± 50

ppm

10.0 12.0

10.0 12.0

Units

ns

ns

ns

ns

ns

V IH

V IL

REFCLK

T P_CLKRMII

T H_CLKRMII

T L_CLKRMII

T R_CLKRMII

T F_CLKRMII

Figure 4: Clock Timing RMII

c. RMII Receive Timing

Symbol

TDLY_RXD

TR_RXD

TF_RXD

Description

REFCLK rising edge

to RXD[1:0], RX_ER

and CRS_DV delay

RXD[1:0], RX_ER,

CRS_DV Rise time

RXD[1:0], RX_ER,

CRS_DV Fall time

Notes

Initial rising edge of

CRS_DV is

asynchronous to

REFCLK

VIL (max) to VIH (min)

VIH (min) to VIL (max)

Copyright © 2004, IC Plus Corp.

33/36

Min

12.0

1.0

1.0

Typ Max Units

15.0 ns

2.5

ns

2.5

ns

Oct 22, 2007

IP101A LF-DS-R12