MK52N512CMD100 Просмотр технического описания (PDF) - Freescale Semiconductor

Номер в каталоге

Компоненты Описание

производитель

MK52N512CMD100 Datasheet PDF : 75 Pages

| |||

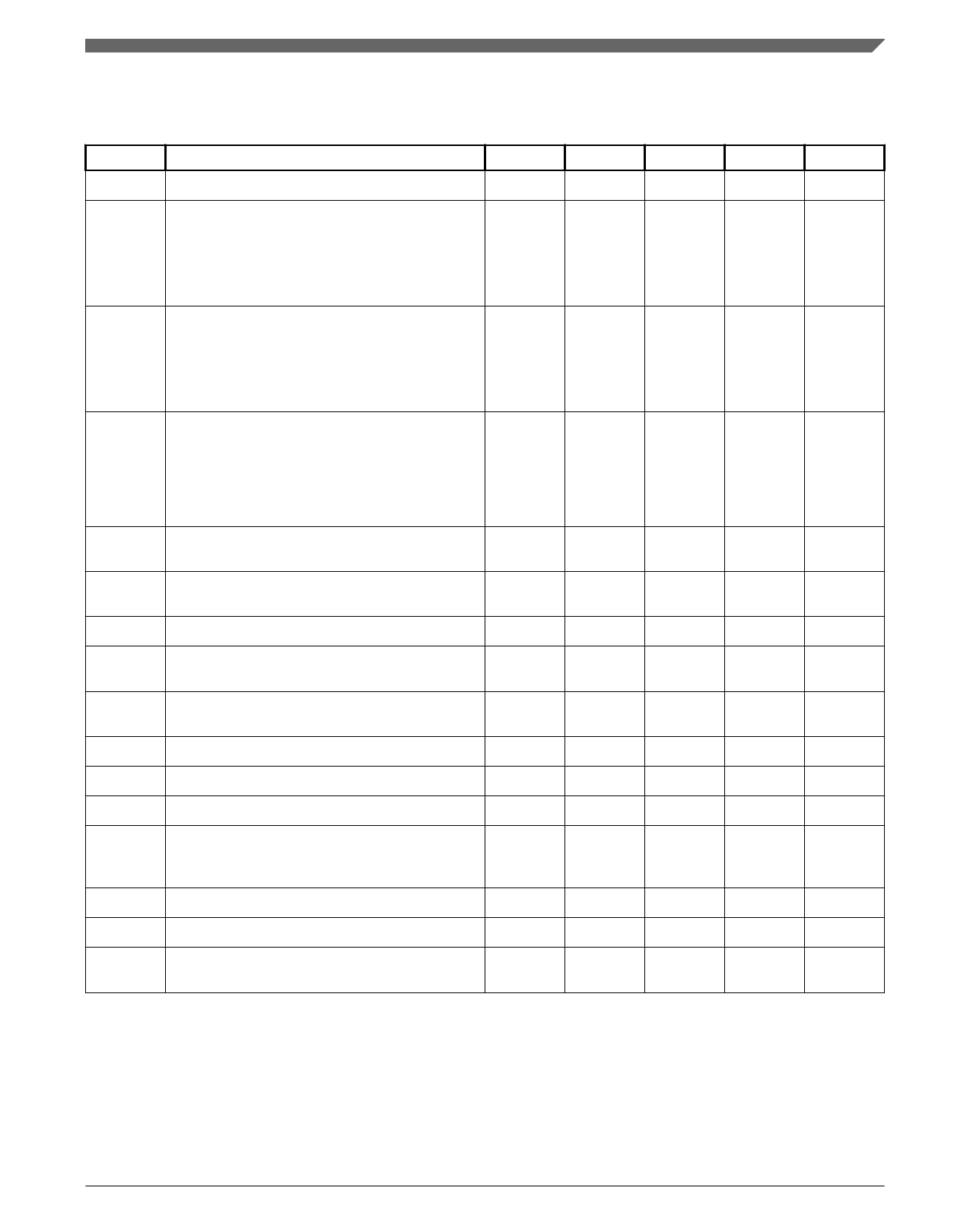

5.1.5 Power consumption operating behaviors

Table 6. Power consumption operating behaviors

Symbol Description

Min.

Typ.

Max.

Unit

IDDA Analog supply current

—

—

TBD

mA

IDD_RUN Run mode current — all peripheral clocks

disabled, code executing from flash

• @ 1.8V

• @ 3.0V

—

40

TBD

mA

—

42

TBD

mA

IDD_RUN Run mode current — all peripheral clocks

enabled, code executing from flash

• @ 1.8V

• @ 3.0V

—

55

TBD

mA

—

56

TBD

mA

IDD_RUN_M Run mode current — all peripheral clocks

AX

enabled and peripherals active, code executing

from flash

• @ 1.8V

—

85

TBD

mA

• @ 3.0V

—

85

TBD

mA

General

Notes

1

2

3

4

IDD_WAIT Wait mode high frequency current at 3.0 V — all

—

35

TBD

mA

2

peripheral clocks disabled

IDD_WAIT Wait mode reduced frequency current at 3.0 V

—

15

TBD

mA

5

— all peripheral clocks disabled

IDD_STOP Stop mode current at 3.0 V

—

0.4

TBD

mA

IDD_VLPR Very-low-power run mode current at 3.0 V — all

—

1.25

TBD

mA

6

peripheral clocks disabled

IDD_VLPR Very-low-power run mode current at 3.0 V — all

—

TBD

TBD

mA

7

peripheral clocks enabled

IDD_VLPW Very-low-power wait mode current at 3.0 V

—

1.05

TBD

mA

8

IDD_VLPS Very-low-power stop mode current at 3.0 V

—

50

TBD

μA

IDD_LLS Low leakage stop mode current at 3.0 V

—

12

TBD

μA

IDD_VLLS3 Very low-leakage stop mode 3 current at 3.0 V

• 128KB RAM devices

—

8

TBD

μA

IDD_VLLS2 Very low-leakage stop mode 2 current at 3.0 V

—

4

TBD

μA

IDD_VLLS1 Very low-leakage stop mode 1 current at 3.0 V

—

2

TBD

μA

IDD_VBAT Average current when CPU is not accessing

—

550

TBD

nA

9

RTC registers at 3.0 V

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See

each module's specification for its supply current.

2. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock . MCG configured for FEI mode.

All peripheral clocks disabled.

3. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock. MCG configured for FEI mode. All

peripheral clocks enabled, but peripherals are not in active operation.

4. 100MHz core and system clock, 50MHz bus and FlexBus clock, and 25MHz flash clock. MCG configured for FEI mode. All

peripheral clocks enabled, and peripherals are in active operation.

K52 Sub-Family Data Sheet Data Sheet, Rev. 4, 3/2011.

Freescale Semiconductor, Inc.

Preliminary

15