M52743 查看數據表(PDF) - MITSUBISHI ELECTRIC

零件编号

产品描述 (功能)

生产厂家

M52743 Datasheet PDF : 19 Pages

| |||

MITSUBISHI ICs (Monitor)

M52743SP/M52744SP

I2C BUS CONTROLLED 3-CHANNEL VIDEO PREAMPLIFIER

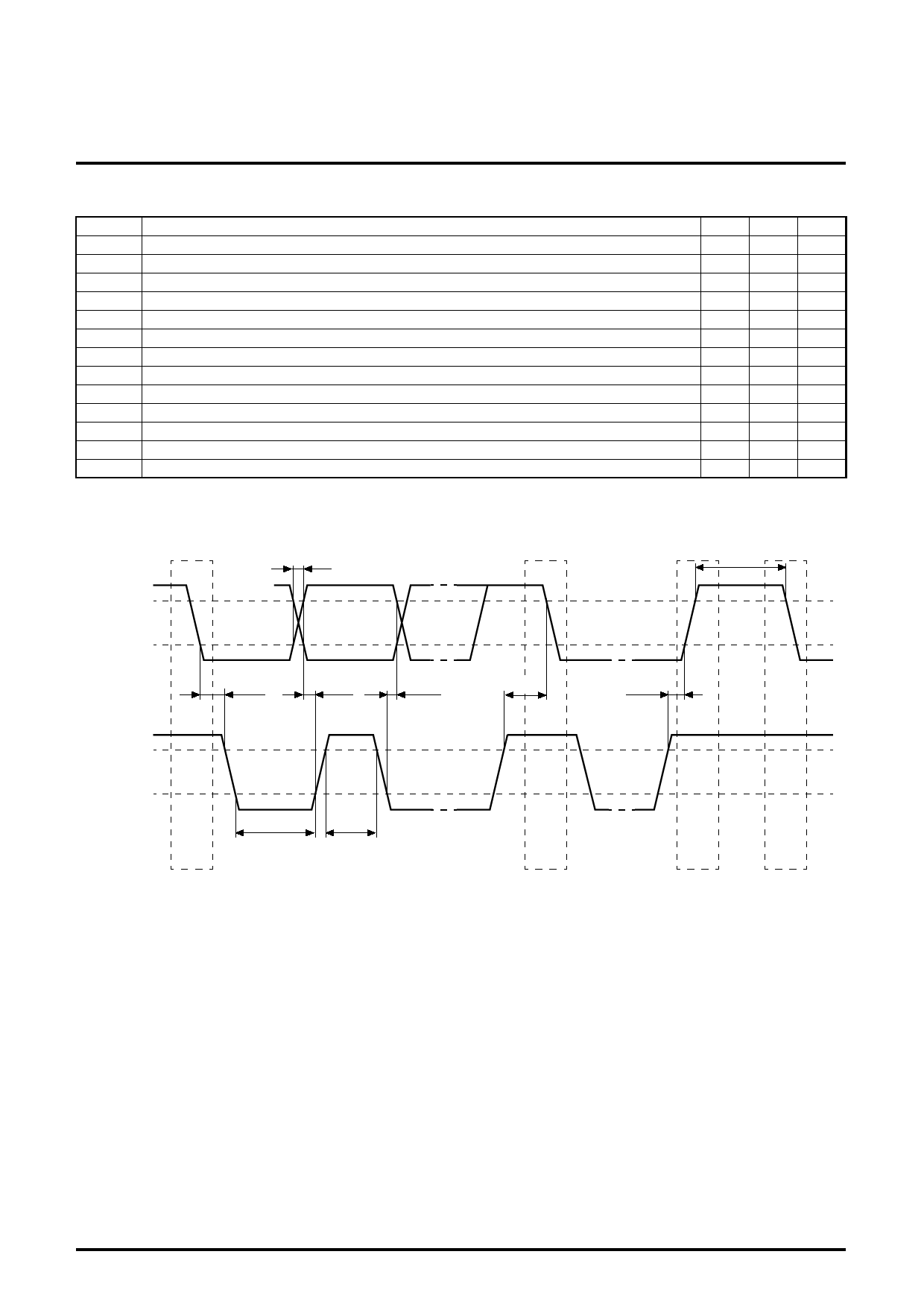

I2C BUS CONTROL SECTION SDA, SCL CHARACTERISTICS

Symbol

VIL

VIH

fSCL

tBUF

tHD:STA

tLOW

tHIGH

tSU:STA

tHD:DAT

tSU:DAT

tr

tf

tSU:STO

Parameter

min. input LOW voltage

max. input HIGH voltage

SCL clock frequency

Time the bus must be free before a new transmission can start

Hold time start condition. After this period the first clock pulse is generated

The LOW period of the clock

The HIGH period of the clock

Set up time for start condition (Only relevant for a repeated start condition)

Hold time DATA

Set-up time DATA

Rise time of both SDA and SCL lines

Fall time of both SDA and SCL lines

Set-up time for stop condition

Min. Max. Unit

-0.5

1.5 V

3.0

5.5 V

0 100 kHz

4.7

−

µs

4.0

−

µs

4.7

−

µs

4.0

−

µs

4.7

−

µs

0

−

µs

250

−

ns

− 1000 ns

−

300 ns

4.0

−

µs

TIMING DIAGRAM

VIH

SDA

VIL

tHD:STA

tr, tf

tSU:DAT

tHD:DAT

VIH

SCL

VIL

S

tLOW

tHIGH

tSU:STA

S

tBUF

tSU:STO

P

S

11