WM8960 查看數據表(PDF) - Wolfson Microelectronics plc

零件编号

产品描述 (功能)

生产厂家

WM8960

Wolfson Microelectronics plc

WM8960 Datasheet PDF : 91 Pages

| |||

WM8960

Production Data

Test Conditions

DCVDD=1.8V, DBVDD=AVDD=SPKVDD1=SPKVDD2=3.3V, DGND=AGND=SPKGND1=SPKGND2=0V, TA=+25oC, Slave

Mode, fs=48kHz, MCLK=256fs, 24-bit data, unless otherwise stated.

PARAMETER

SYMBOL

MIN

TYP

MAX

UNIT

Audio Data Input Timing Information

ADCLRC/DACLRC propagation delay from BCLK falling edge

tDL

ADCDAT propagation delay from BCLK falling edge

tDDA

DACDAT setup time to BCLK rising edge

tDST

10

10

ns

10

ns

ns

DACDAT hold time from BCLK rising edge

tDHT

10

ns

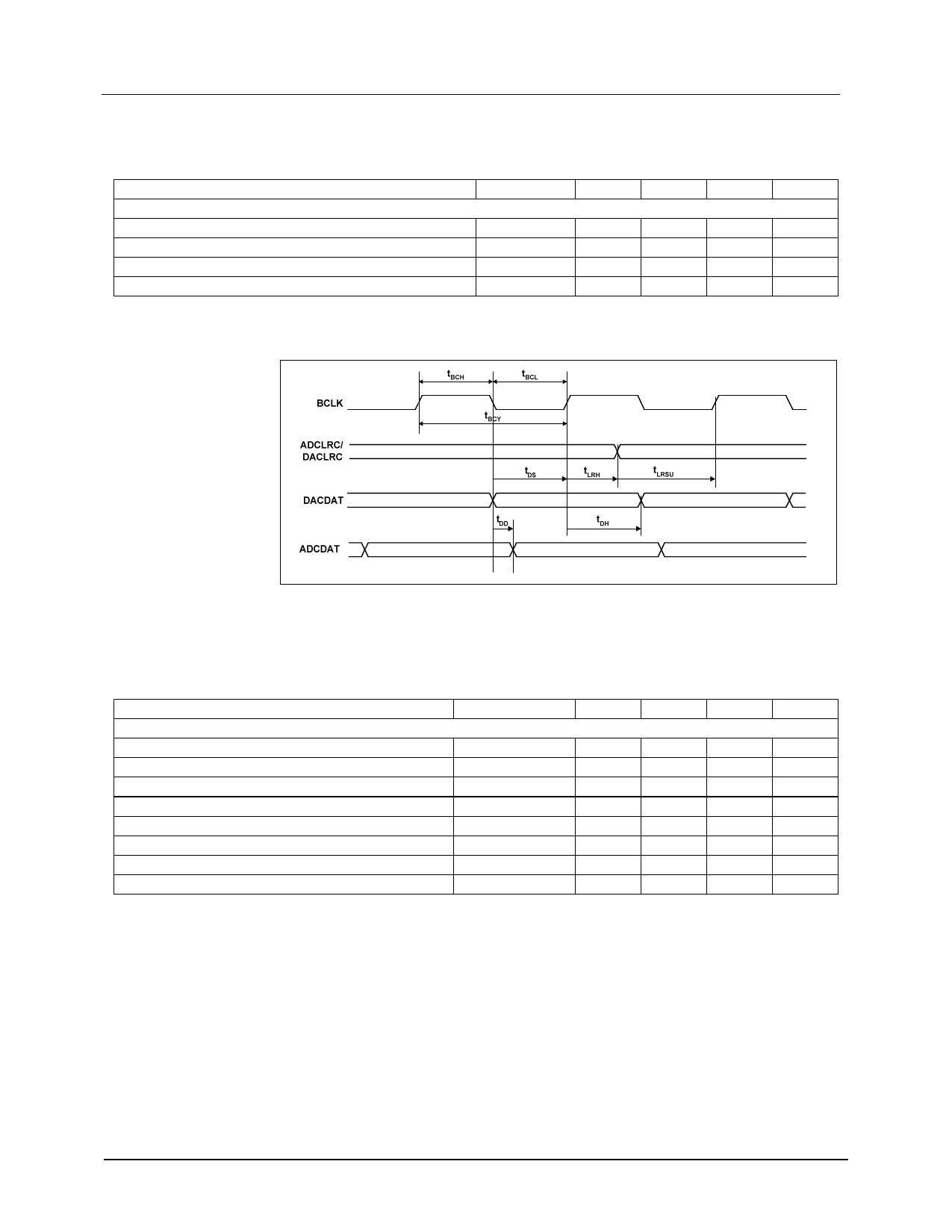

AUDIO INTERFACE TIMING – SLAVE MODE

Figure 3 Digital Audio Data Timing – Slave Mode

Test Conditions

DCVDD=1.8V, DBVDD=AVDD=SPKVDD1=SPKVDD2=3.3V, DGND=AGND=SPKGND1=SPKGND2=0V, TA=+25oC, Slave

Mode, fs=48kHz,

MCLK= 256fs, 24-bit data, unless otherwise stated.

PARAMETER

Audio Data Input Timing Information

BCLK cycle time

BCLK pulse width high

BCLK pulse width low

ADCLRC/DACLRC set-up time to BCLK rising edge

ADCLRC/DACLRC hold time from BCLK rising edge

DACDAT hold time from BCLK rising edge

ADCDAT propagation delay from BCLK falling edge

DACDAT set-up time to BCLK rising edge

Note:

SYMBOL

tBCY

tBCH

tBCL

tLRSU

tLRH

tDH

tDD

tDS

MIN

TYP

MAX

UNIT

50

ns

20

ns

20

ns

10

ns

10

ns

10

ns

10

ns

10

ns

BCLK period should always be greater than or equal to MCLK period.

w

PD, August 2013, Rev 4.2

14