81C55 View Datasheet(PDF) - Oki Electric Industry

Part Name

Description

Manufacturer

81C55 Datasheet PDF : 19 Pages

| |||

¡ Semiconductor

MSM81C55-5RS/GS/JS

M2 M1

00

01

10

11

Outputs a low-level signal in the latter half (Note 1) of a count period.

Outputs a low-level signal in the latter half of a count period, automatically

loads the programmed count length, and restarts counting when the TC

value is reached.

Outputs a pulse when the TC value is reached.

Outputs a pulse each time the preset TC value is reached, automatically

loads the programmed count length, and restarts from the beginning.

Notes: 1. When counting an asymmetrical value such as (9), a high level is output during

the first period of five,and a low level is output during the second period of four.

2. If an internal counter of the MSM81C55-5 receives a reset signal, count operation

stops but the counter is not set to a specific initial value or output mode. When

restarting count operation after reset, the START command must be executed

again through the C/S register.

Note that while the counter is counting, you may load a new count and mode into the CLR.

Before the new count and mode will be used by the counter, you must issue a START

command to the counter. Please note the timer circuit on the MSM81C55-5 is designed to

be a square-wave timer, not a event counter. To achieve this, it counts down by twos twice

in completing one cycle. Thus, its registers do not contain values directly representing the

number of TIMER IN pulse received. After the timer has started counting down, the values

residing in the count registers can be used to calculate the actual number of TIMER IN pulse

required to complete the timer cycle if desired. To obtain the remaining count, perform the

following operations in order.

1. STOP the counter

2. Read in the 16-bit value from the count registers.

3. Reset the upper two mode bits

4. Reset the carry and rotate right one position all 16 bits through carry

5. If carry is set, add 1/2 of the full original count (1/2 full count-1 if full count is odd).

Note: If you started with an odd count and you read the count registers before the third

count

pulse occurs, you will not be able to recognize whether one or two

counts have

occurred. Regardless of this, the MSM81C55-

5 always counts out the right number of pulses

in generating the

TIMER OUTTIwMaERv-eIfNorms.

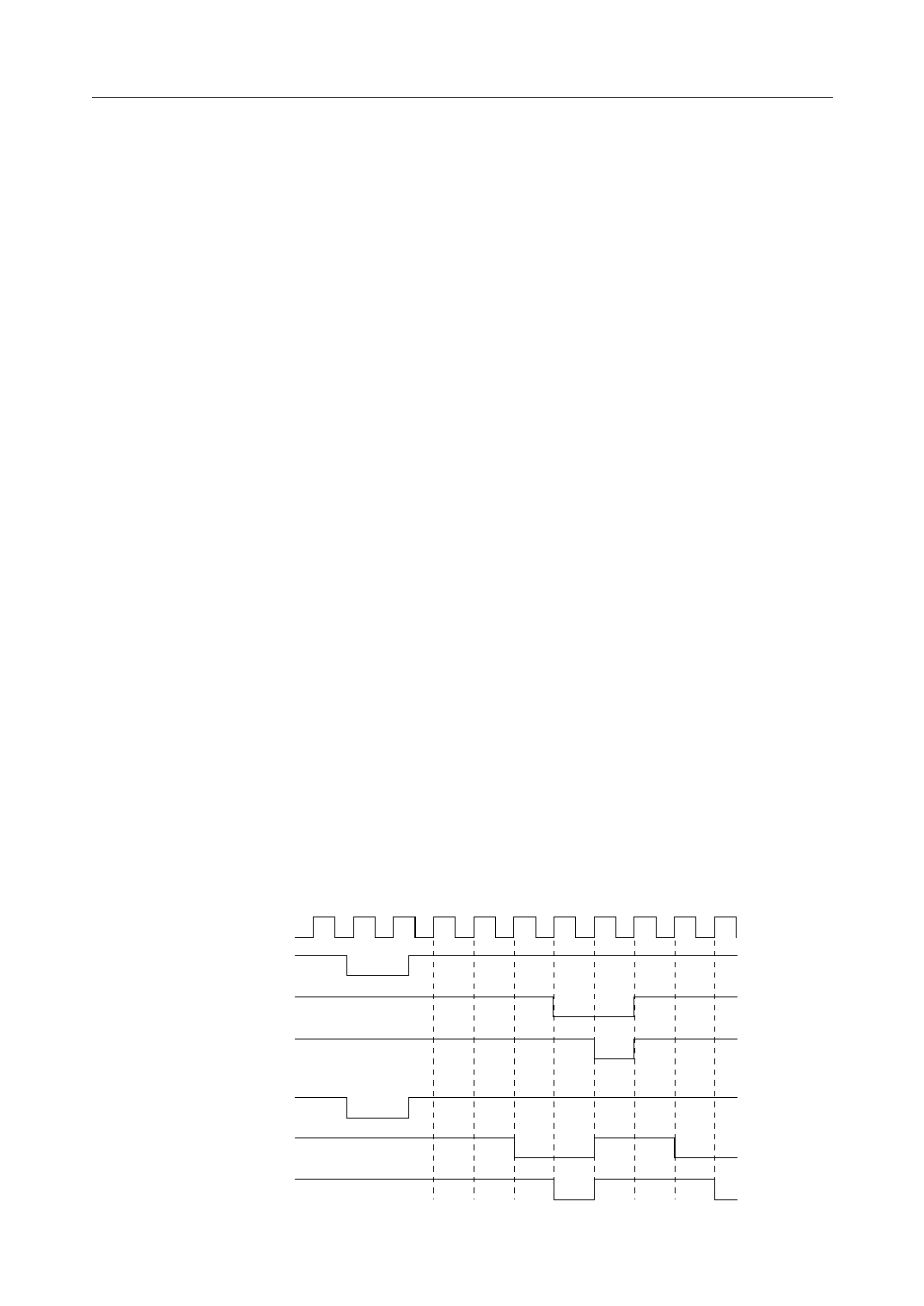

WR n=5

Start

TIMER-OUT (Square Wave)

55 34 2 5 5

(TC)

TIMER-OUT (Pulse)

WR n=4

Start

TIMER-OUT (Square Wave)

53 42 5 3 4

(TC)

TIMER-OUT (Pulse)

Note: n is the value set in the CLR. Figures in the diagram refer to counter values

13/19