AS3931 View Datasheet(PDF) - austriamicrosystems AG

Part Name

Description

Manufacturer

AS3931 Datasheet PDF : 31 Pages

| |||

AS3931

Datasheet - Detailed Description

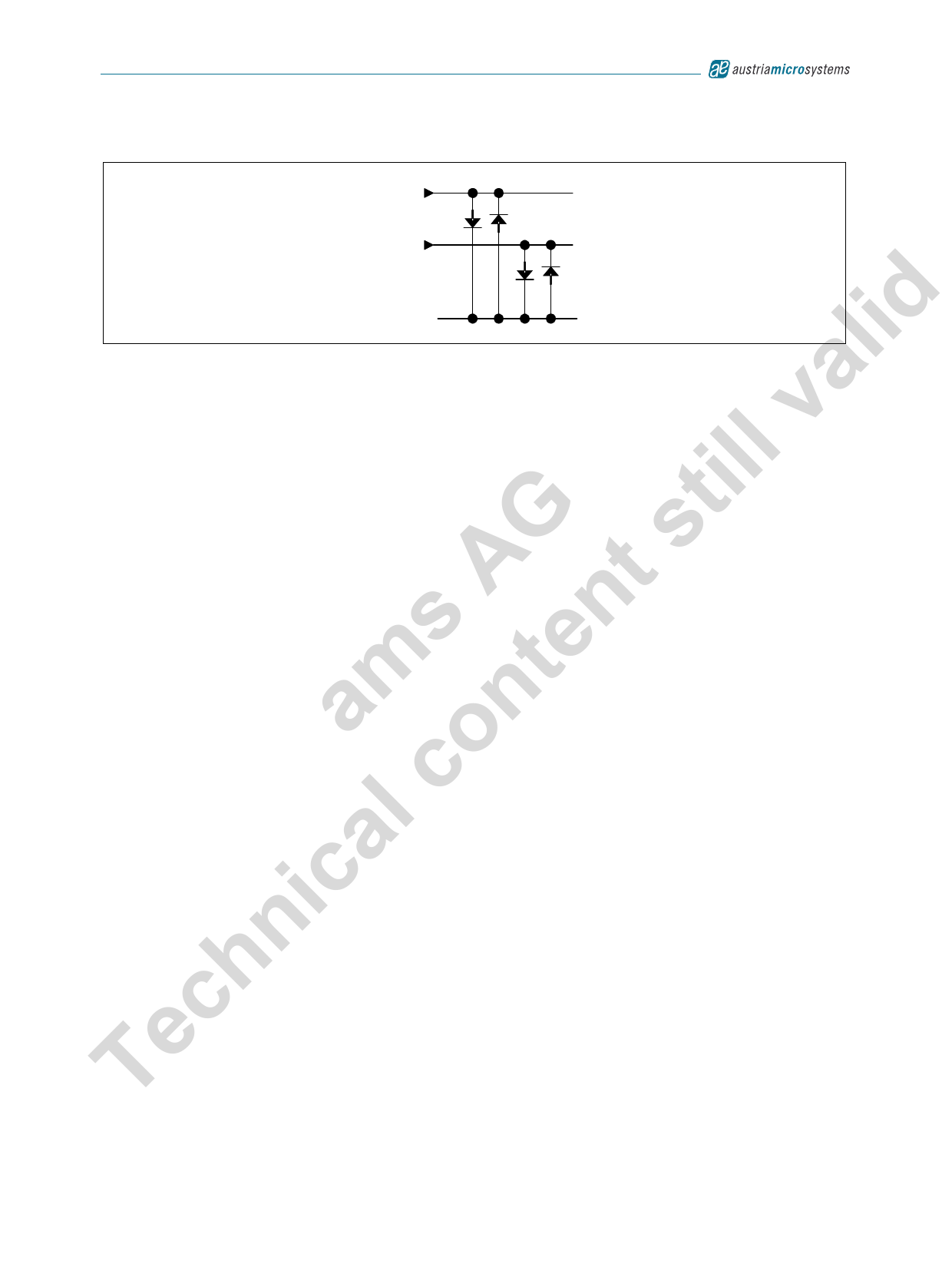

Figure 14. Input Protection Circuit

LFN

LFP

lid GND

8.2.5 Logarithmic Envelope Amplifiers

a The logarithmic envelope amplifiers amplify the ASK coded LF input signals. They generate Received Signal Strength Indicator (RSSI) signals,

which are proportional to the logarithm of the received field strengths within the specified dynamic range. These signals are used for data

v detection and distance measurements. The RSSI signals are bandwidth limited to reduce noise influence. The slope of the amplifiers in the low

signal range can be controlled by register settings: a high slope for increased sensitivity but also increased current consumption and a weak

ill slope with reduced current consumption are possible.

8.2.6 Detectors

t The detectors convert the logarithmic envelope signal containing ASK coded data into digital signals. Each detector consists of a lowpass filter

for generation of an adaptive threshold and a slicing comparator. A preamble is required for a proper adaptation of the threshold prior to the

G s decision of the first valid data bit. A constant positive threshold offset is included in the comparator to ensure no data output in case of no input

signal. This increases the overall system noise immunity.

A t 8.2.7 Digital Correlators

s n The AS3931 uses a 16-bit digital wakeup pattern. Digital correlators perform the identification of this pattern. They use a sophisticated detection

algorithm that provides high immunity against noise injection as a result of stochastic and periodic interference’s. The AS3931 provides the

e possibility to double the length of the wake pattern to 32 bit. This is useful in environments with high noise levels to reduce the possibility of

m t spurious (parasitic) wakeups. In this case the usual wake pattern must be sent twice before a wake up is recognized and a WAKE signal is

generated. This active low WAKE signal is generated after successful pattern identification. Otherwise WAKE is high. Setting a register bit via the

serial-programming interface resets the correlators. In order to save power the correlators are stopped when no data has been received for a

a n specified amount of time. The correlators can be configured regarding their error tolerance by register settings.

o 8.2.8 Wake Generator

c A counter, clocked by the 32 kHz crystal oscillator, generates an artificial wake up app. every 2 hours. This wake up can be used to manage the

quiescent current consumption of the AS3931. The idea behind is, to switch off one or more of the receiving channels in case of no true wake up

l detection for long times; that is when only parasitic wakeups or no wakeup at all is detected. An external controlling unit (µC) can identify this

case by counting the parasitic wake ups and powering down one or more of the receiver channels to save current. When no wake ups are

a detected at all, e.g. if the application device is stored in a stock, then the wake generator’s artificial parasitic wakeups (every 2 hours) can be

used to identify the situation.

ic 8.2.9 Crystal Oscillator

The crystal oscillator generates the clock signal for the digital correlators. It has been optimized for a 32.768 kHz quartz crystal connected to pins

n XIN and XOUT. The oscillator provides extremely low current consumption, so it can be operated permanently by a battery.

8.2.10 Regulator

h A regulator is implemented to provide the amplifiers and digital circuits with a stable and clean supply. The regulator can be switched off; in this

c case the external supply voltage is bypassed to the amplifiers and digital circuits. The regulator shall always be used for external supply voltages

higher then 3.3V, otherwise the current consumption is significantly increased. The regulated voltage can be seen at the VREG pin, but may not

e be used to supply any other external circuits.

T8.2.11 Power On Reset (POR)

A power on reset circuit guarantees proper circuit operation after power supply starts up. All internal registers are reset to their default states

after power on. After the Power On Reset time, the active low WAKE output is activated and set to low (Power On Wake Up). During the Power

On Reset time, the WAKE output pin is set to high. By this, it is ensured that this triggers the Power On Wake Up triggered only when the internal

registers are reset and ready to be programmed.

www.austriamicrosystems.com/AS3931

Revision 6.2

14 - 30