AS3931 View Datasheet(PDF) - austriamicrosystems AG

Part Name

Description

Manufacturer

AS3931 Datasheet PDF : 31 Pages

| |||

AS3931

Datasheet - Detailed Description

8.3.2 Wake Up Detection

A WAKE signal is generated if and only if all 8 LOGIC 1 half-bits and a predefined number of LOGIC 0 half-bits have been identified as correct.

The wakeup detection criteria can be changed: the number of invalid zero half-bits can be programmed from 0 to 3. A valid Wake Up Frame can

be detected at only one of the 3 channels or at more then one channel simultaneously. The single WAKE signals of each channel are ored

together to a common WAKE signal Figure 13.

In case of using the double wake up feature, the settings of the allowed zero half-bit errors apply for each of the sent data pattern individually.

E.g. if you configure the AS3931 to allow 2 zero half-bit errors, the first data pattern can contain up to two invalid zero half-bits as well as the

second data pattern, but it is not possible that the first pattern contains 3 and the second data pattern contains one zero half-bit error (what in

total would give the same number of allowed zero half-bit errors as before). Note that a Double-Wake-Pattern detection is possible also if the two

lid consecutive Single-Wake-Patterns are assigned to different channels: e.g. if the first pattern is recognized at channel 2 and the second pattern is

recognized at channel 3, then a Double-Wake-Pattern is recognized and the WAKE Pin is activated. All channel combinations are possible. In

case of different channels, it is not possible to decide which channel received the first and which channel received the second data pattern.

a 8.3.3 WAKE Signal Clearing

After a Wake Up detection, the WAKE output signal must be reset via the Serial Programming Interface. This is done by toggling the bit C5 in the

v Channel Select register from low to high and vice versa. This is valid for both cases the Single Wake pattern and the Double Wake pattern

detection. Furthermore, it is also valid for an internal generated Artificial Wakeup (see Extended Operation on page 24).

ill 8.3.4 WAKE Signal After POR

After a power on reset (POR), the WAKE signal is activated (LOW). Therefore, after startup the WAKE signal must be cleared as if a valid Wake

t Up would have been detected.

G s 8.3.5 RSSI Operation

The RSSI signal of a selected channel can be measured at the RSSI pin. Each channel can be selected by register settings. To calibrate the

A t RSSI measurement, the LF inputs can be shortcutted with approximately 500 Ω by internal register settings. Doing so, the RSSI voltage offset

can be measured. The RSSI – signal is buffered at the RSSI pin. The buffer can be deactivated by register settings; in this case the RSSI pin is

s n tristated (high impedance). However, if the CS signal is not activated, the RSSI pin is tristated. This has to be kept in mind when programming

the AS3931 via the Serial Programming Interface (the CS signal is used to latch the serial data into the selected register at the falling edge of

e CS).

m t 8.4 Serial Programming Interface Timing

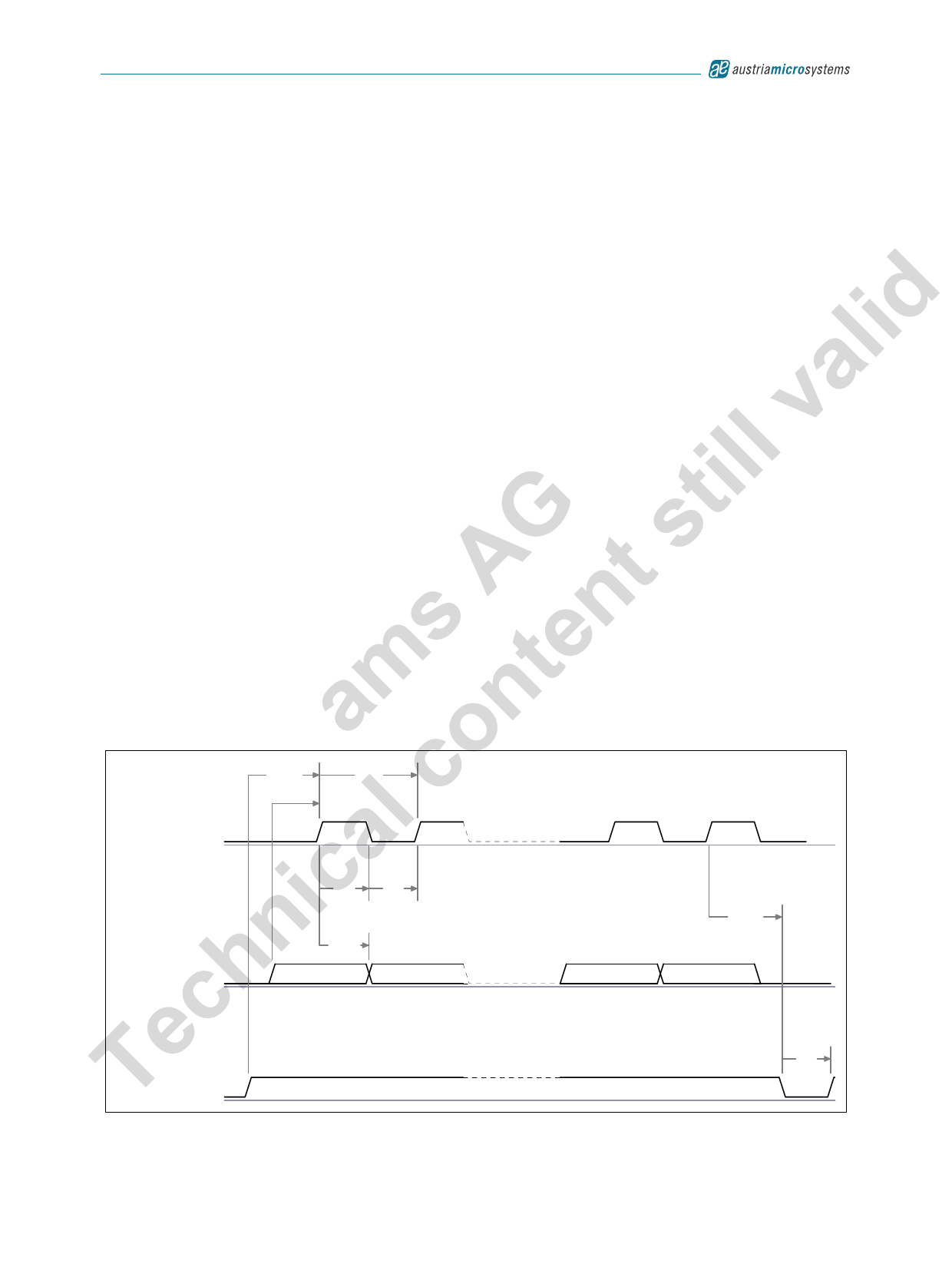

a n Figure 17. SPI Timing Waveforms

l co SCL

TSHCH

TCLK

TDVCH

nica SDA

TCH TCL

TCHDI

A0

A1

TCHSL

D4

D5

ech TSL

T CS

www.austriamicrosystems.com/AS3931

Revision 6.2

16 - 30