DSP56307/D View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

DSP56307/D Datasheet PDF : 156 Pages

| |||

Signals/Connections

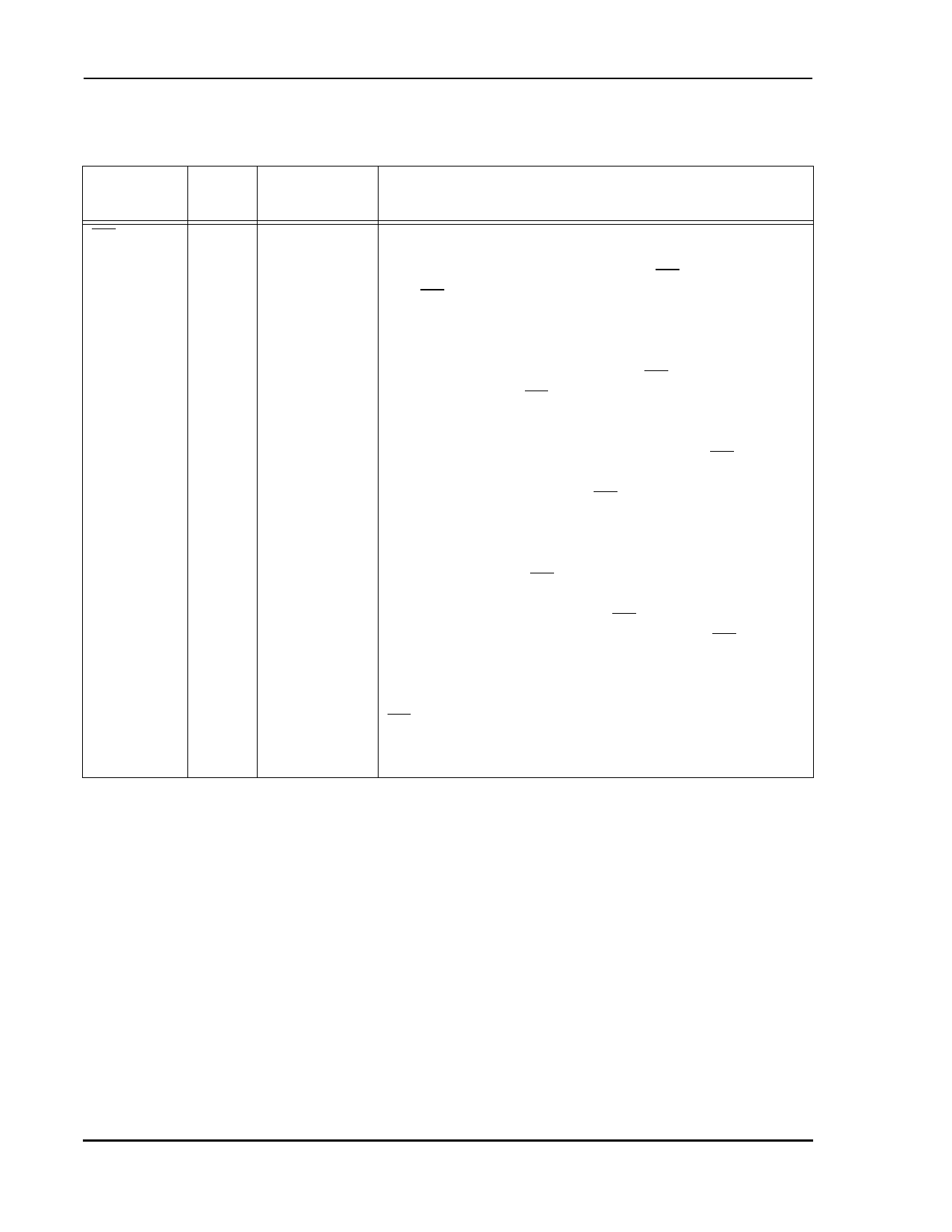

External Memory Expansion Port (Port A)

Signal

Name

TA

Table 1-8 External Bus Control Signals (Continued)

Type

State During

Reset

Signal Description

Input

Ignored Input Transfer AcknowledgeÑIf the DSP56307 is the bus

master and there is no external bus activity, or the

DSP56307 is not the bus master, the TA input is ignored.

The TA input is a data transfer acknowledge (DTACK)

function that can extend an external bus cycle

indefinitely. Any number of wait states (1, 2. . .infinity)

may be added to the wait states inserted by the bus

control register (BCR) by keeping TA deasserted. In

typical operation, TA is deasserted at the start of a bus

cycle, is asserted to enable completion of the bus cycle,

and is deasserted before the next bus cycle. The current

bus cycle completes one clock period after TA is

asserted synchronous to CLKOUT. The number of wait

states is determined by the TA input or by the BCR,

whichever is longer. The BCR can be used to set the

minimum number of wait states in external bus cycles.

In order to use the TA functionality, the BCR must be

programmed to at least one wait state. A zero wait state

access cannot be extended by TA deassertion;

otherwise, improper operation may result. TA can

operate synchronously or asynchronously depending

on the setting of the TAS bit in the OMR.

TA functionality may not be used while performing

DRAM type accesses; otherwise, improper operation

may result.

Not Recommended for New Design

1-8

DSP56307 Technical Data

MOTOROLA