DSP56307/D View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

DSP56307/D Datasheet PDF : 156 Pages

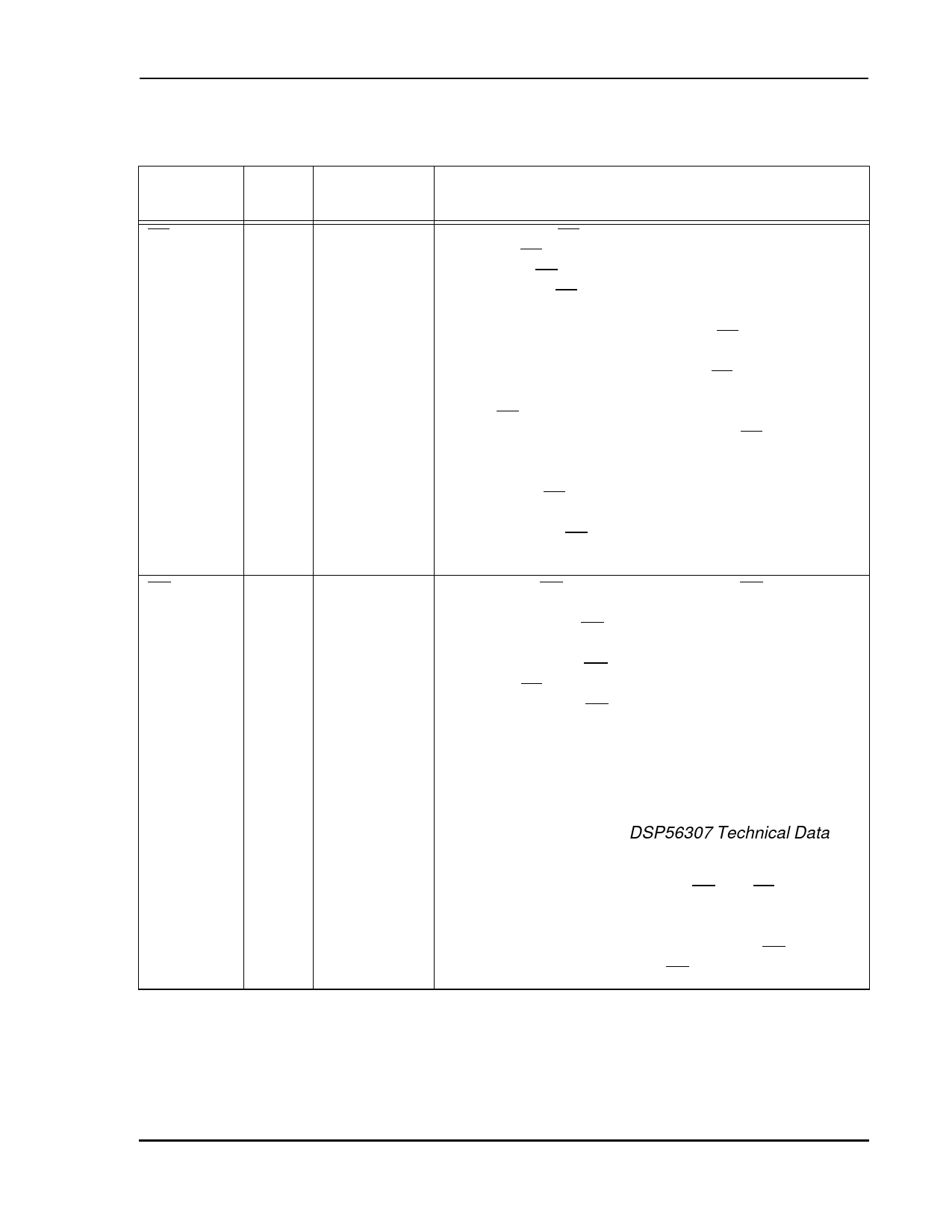

| |||

Signals/Connections

External Memory Expansion Port (Port A)

Signal

Name

BR

BG

Table 1-8 External Bus Control Signals (Continued)

Type

State During

Reset

Signal Description

Output Output

(deasserted)

Bus RequestÑBR is an active-low output, never

tri-stated. BR is asserted when the DSP requests bus

mastership. BR is deasserted when the DSP no longer

needs the bus. BR may be asserted or deasserted

independently of whether the DSP56307 is a bus master

or a bus slave. Bus ÒparkingÓ allows BR to be deasserted

even though the DSP56307 is the bus master. (See the

description of bus ÒparkingÓ in the BB signal

description.) The bus request hole (BRH) bit in the BCR

allows BR to be asserted under software control even

though the DSP does not need the bus. BR is typically

sent to an external bus arbitrator that controls the

priority, parking, and tenure of each master on the same

external bus. BR is only affected by DSP requests for the

external bus, never for the internal bus. During

hardware reset, BR is deasserted and the arbitration is

reset to the bus slave state.

Input

Ignored Input Bus GrantÑBG is an active-low input. BG must be

asserted/deasserted synchronous to CLKOUT for

proper operation. BG is asserted by an external bus

arbitration circuit when the DSP56307 becomes the next

bus master. When BG is asserted, the DSP56307 must

wait until BB is deasserted before taking bus

mastership. When BG is deasserted, bus mastership is

typically given up at the end of the current bus cycle.

This may occur in the middle of an instruction that

requires more than one external bus cycle for execution.

The default operation of this bit requires a setup and

hold time as specified in DSP56307 Technical Data (the

data sheet). An alternate mode can be invoked: set the

asynchronous bus arbitration enable (ABE) bit (Bit 13)

in the OMR. When this bit is set, BG and BB are

synchronized internally. This eliminates the respective

setup and hold time requirements but adds a required

delay between the deassertion of an initial BG input and

the assertion of a subsequent BG input.

Not Recommended for New Design

MOTOROLA

DSP56307 Technical Data

1-9