DSP56307UM View Datasheet(PDF) - Motorola => Freescale

Part Name

Description

Manufacturer

DSP56307UM Datasheet PDF : 156 Pages

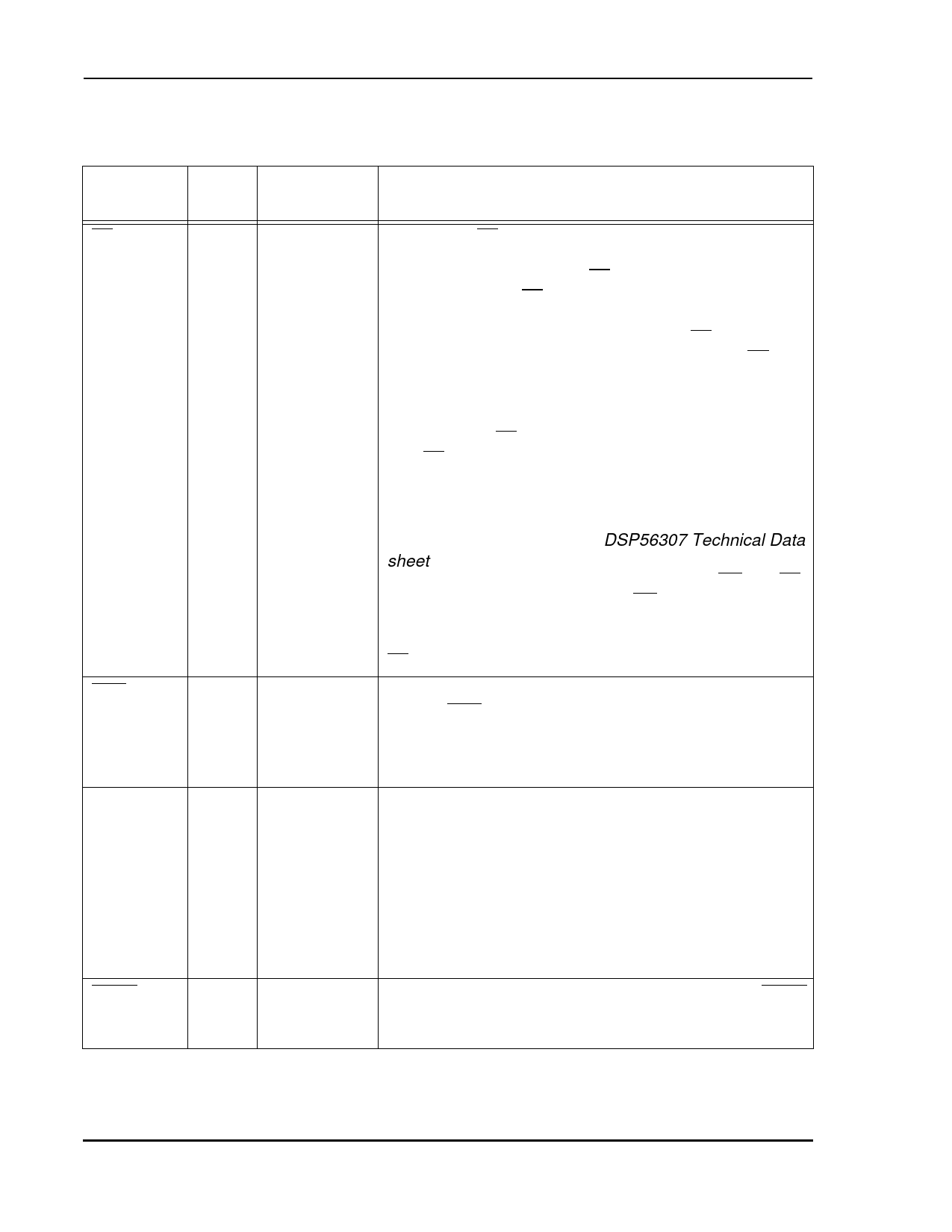

| |||

Signals/Connections

External Memory Expansion Port (Port A)

Signal

Name

BB

CAS

BCLK

BCLK

Table 1-8 External Bus Control Signals (Continued)

Type

State During

Reset

Signal Description

Input/ Input

Output

Bus BusyÑBB is a bidirectional active-low

input/output and must be asserted and deasserted

synchronous to CLKOUT. BB indicates that the bus is

active. Only after BB is deasserted can the pending bus

master become the bus master (and then assert the

signal again). The bus master may keep BB asserted

after ceasing bus activity regardless of whether BR is

asserted or deasserted. Called Òbus parking,Ó this

allows the current bus master to reuse the bus without

rearbitration until another device requires the bus. The

deassertion of BB is done by an Òactive pull-upÓ method

(i.e., BB is driven high and then released and held high

by an external pull-up resistor).

The default operation of this bit requires a setup and

hold time as specified in the DSP56307 Technical Data

sheet. An alternate mode can be invoked: set the ABE

bit (Bit 13) in the OMR. When this bit is set, BG and BB

are synchronized internally. See BG for additional

information.

Output Tri-stated

Output Tri-stated

Output Tri-stated

BB requires an external pull-up resistor.

Column Address StrobeÑWhen the DSP is the bus

master, CAS is an active-low output used by DRAM to

strobe the column address. Otherwise, if the bus

mastership enable (BME) bit in the DRAM control

register is cleared, the signal is tri-stated.

Bus ClockÑWhen the DSP is the bus master, BCLK is

an active-high output. BCLK is active as a sampling

signal when the program address tracing mode is

enabled (i.e., the ATE bit in the OMR is set). When

BCLK is active and synchronized to CLKOUT by the

internal PLL, BCLK precedes CLKOUT by one-fourth of

a clock cycle. The BCLK rising edge may be used to

sample the internal program memory access on the

A0ÐA23 address lines.

Bus Clock NotÑWhen the DSP is the bus master, BCLK

is an active-low output and is the inverse of the BCLK

signal. Otherwise, the signal is tri-stated.

Not Recommended for New Design

1-10

DSP56307 Technical Data

MOTOROLA