H5PS1G43EFR View Datasheet(PDF) - Hynix Semiconductor

Part Name

Description

Manufacturer

H5PS1G43EFR Datasheet PDF : 44 Pages

| |||

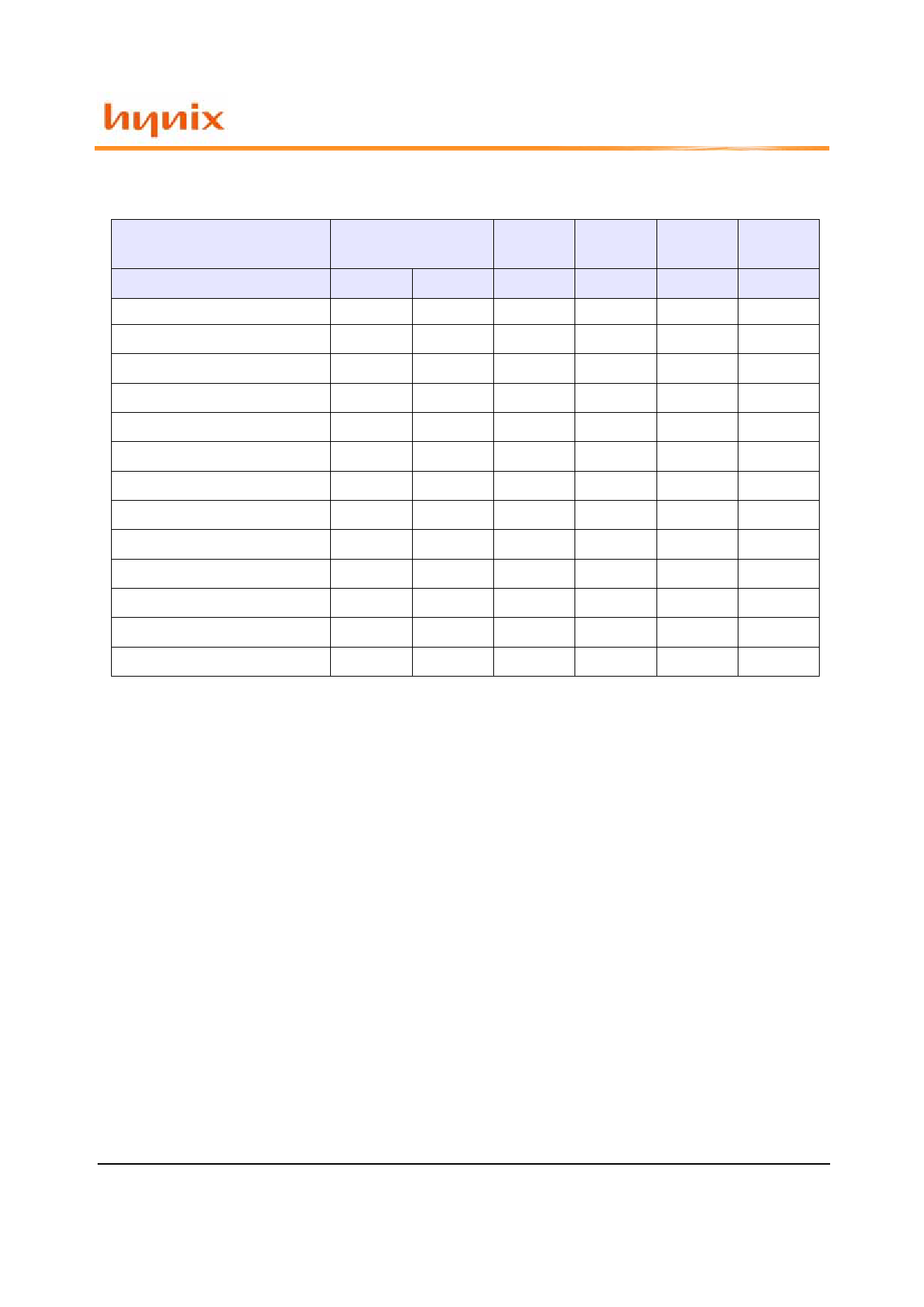

IDD Testing Parameters

For purposes of IDD testing, the following parameters are to be utilized.

H5PS1G43EFR

H5PS1G83EFR

H5PS1G63EFR

Parameter

CL(IDD)

tRCD(IDD)

tRC(IDD)

tRRD(IDD)-x4/x8

tRRD(IDD)-x16

tCK(IDD)

tRASmin(IDD)

tRASmax(IDD)

tRP(IDD)

tRFC(IDD)-256Mb

tRFC(IDD)-512Mb

tRFC(IDD)-1Gb

tRFC(IDD)-2Gb

DDR2-800

5-5-5

5

12.5

57.5

7.5

10

2.5

45

70000

12.5

75

105

127.5

197.5

6-6-6

6

15

60

7.5

10

2.5

45

70000

15

75

105

127.5

197.5

DDR2-

667

5-5-5

5

15

60

7.5

10

3

45

70000

15

75

105

127.5

197.5

DDR2-

533

4-4-4

4

15

60

7.5

10

3.75

45

70000

15

75

105

127.5

197.5

DDR2-

400

3-3-3

3

15

55

7.5

10

5

40

70000

15

75

105

127.5

197.5

Units

tCK

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Detailed IDD7

The detailed timings are shown below for IDD7. Changes will be required if timing parameter changes are made to the

specification.

Legend: A = Active; RA = Read with Autoprecharge; D = Deselect

IDD7: Operating Current: All Bank Interleave Read operation

All banks are being interleaved at minimum tRC(IDD) without violating tRRD(IDD) and tFAW (IDD) using a burst length

of 4. Control and address bus inputs are STABLE during DESELECTs. IOUT = 0mA

Timing Patterns for 4 bank devices x4/ x8/ x16

-DDR2-400 4/4/4: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D D D

-DDR2-400 3/3/3: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D D D

-DDR2-533 4/4/4: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D D

-DDR2-533 4/4/4: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D D D

-DDR2-667 5/5/5: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D

-DDR2-667 4/4/4: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D

-DDR2-800 6/6/6: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D D D D D

-DDR2-800 5/5/5: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D D D D

-DDR2-800 4/4/4: A0 RA0 D D A1 RA1 D D A2 RA2 D D A3 RA3 D D D D D D D D

Timing Patterns for 8 bank devices x4/8

-DDR2-400 all bins: A0 RA0 A1 RA1 A2 RA2 A3 RA3 A4 RA4 A5 RA5 A6 RA6 A7 RA7

-DDR2-533 all bins: A0 RA0 A1 RA1 A2 RA2 A3 RA3 D D A4 RA4 A5 RA5 A6 RA6 A7 RA7 D D

-DDR2-667 all bins: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D

-DDR2-800 all bins: A0 RA0 D A1 RA1 D A2 RA2 D A3 RA3 D D D A4 RA4 D A5 RA5 D A6 RA6 D A7 RA7 D D D

Rev. 0.4 / Nov 2008

19