MPC8540(2004) View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

MPC8540 Datasheet PDF : 1302 Pages

| |||

Paragraph

Number

11.5.3

11.5.4

11.5.5

11.5.6

11.5.7

11.5.7.1

11.5.7.2

11.5.8

Contents

Title

Page

Number

Post-Transfer Software Response ............................................................................ 11-21

Generation of STOP................................................................................................. 11-22

Generation of Repeated START .............................................................................. 11-22

Generation of SCL When SDA Low ....................................................................... 11-22

Slave Mode Interrupt Service Routine..................................................................... 11-23

Slave Transmitter and Received Acknowledge ................................................... 11-23

Loss of Arbitration and Forcing of Slave Mode.................................................. 11-23

Interrupt Service Routine Flowchart........................................................................ 11-23

12.1

12.1.1

12.1.2

12.2

12.2.1

12.2.2

12.3

12.3.1

12.3.1.1

12.3.1.2

12.3.1.3

12.3.1.4

12.3.1.5

12.3.1.6

12.3.1.7

12.3.1.8

12.3.1.9

12.3.1.10

12.3.1.11

12.3.1.12

12.3.1.13

12.4

12.4.1

12.4.1.1

12.4.1.2

12.4.1.3

12.4.1.4

Chapter 12

DUART

Overview........................................................................................................................ 12-1

Features...................................................................................................................... 12-2

Modes of Operation ................................................................................................... 12-3

External Signal Descriptions ......................................................................................... 12-3

Signal Overview ........................................................................................................ 12-3

Detailed Signal Descriptions ..................................................................................... 12-3

Memory Map/Register Definition ................................................................................. 12-4

Register Descriptions................................................................................................. 12-6

Receiver Buffer Registers (URBR0, URBR1) ...................................................... 12-6

Transmitter Holding Registers (UTHR0, UTHR1) ............................................... 12-6

Divisor Most and Least Significant Byte Registers

(UDMB and UDLB).......................................................................................... 12-7

Interrupt Enable Register (UIER).......................................................................... 12-9

Interrupt ID Registers (UIIR0, UIIR1) ................................................................ 12-10

FIFO Control Registers (UFCR0, UFCR1) ......................................................... 12-11

Line Control Registers (ULCR0, ULCR1).......................................................... 12-12

MODEM Control Registers (UMCR0, UMCR1)................................................ 12-14

Line Status Registers (ULSR0, ULSR1) ............................................................. 12-15

MODEM Status Registers (UMSR0, UMSR1) ................................................... 12-16

Scratch Registers (USCR0, USCR1) ................................................................... 12-17

Alternate Function Registers (UAFR0, UAFR1) ................................................ 12-17

DMA Status Registers (UDSR0, UDSR1) .......................................................... 12-18

Functional Description................................................................................................. 12-20

Serial Interface......................................................................................................... 12-20

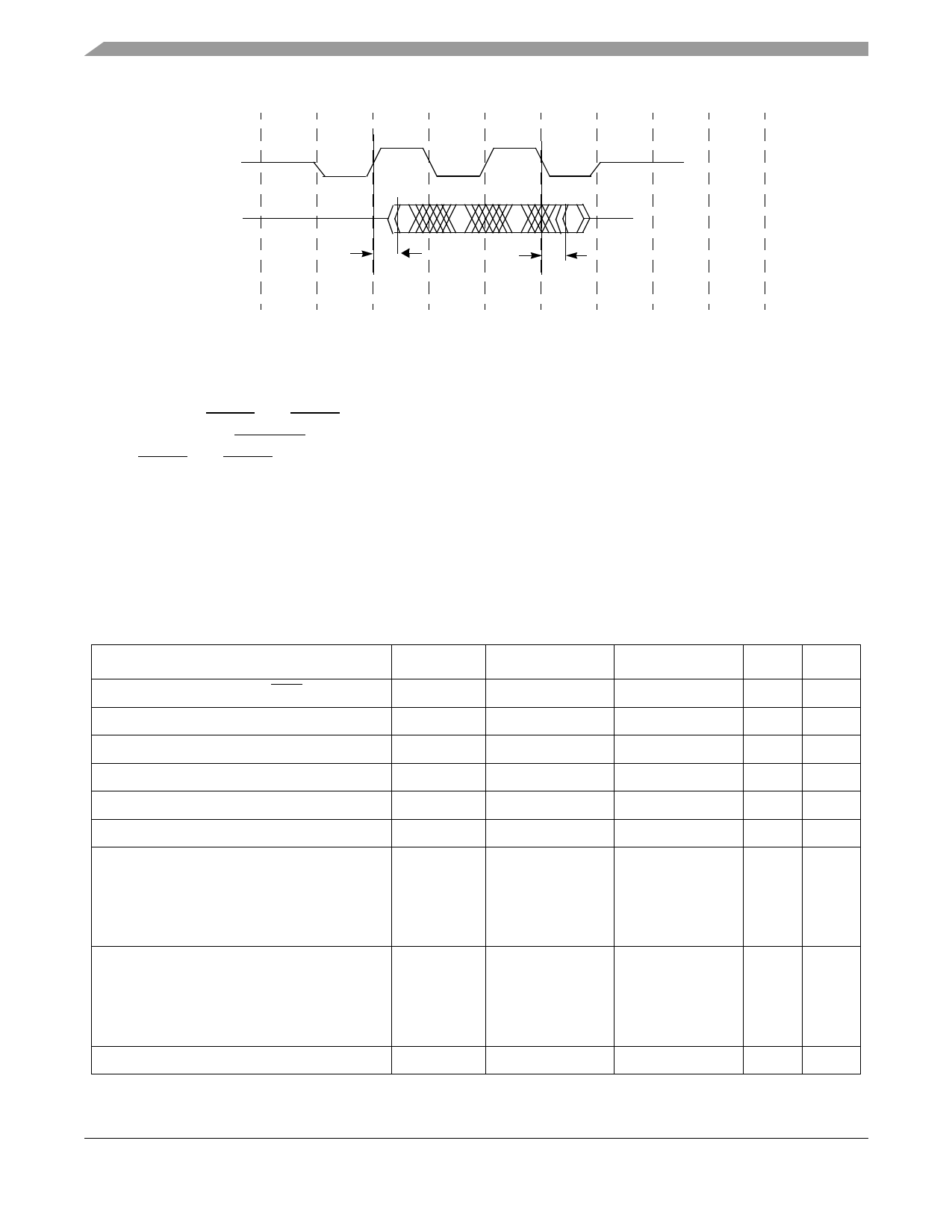

START Bit ........................................................................................................... 12-21

Data Transfer ....................................................................................................... 12-21

Parity Bit .............................................................................................................. 12-22

STOP Bit.............................................................................................................. 12-22

MPC8540 PowerQUICC III Integrated Host Processor Reference Manual, Rev. 1

xviii

Freescale Semiconductor