S5L9284 View Datasheet(PDF) - Samsung

Part Name

Description

Manufacturer

S5L9284 Datasheet PDF : 24 Pages

| |||

S5L9284D

DIGITAL SIGNAL PROCESSOR

EFM DEMODULATION BLOCK

This block consists of an EFM demodulator which demodulates EFM data obtained from a disc, an EFM

phasedetector and a controller, etc.

EFM PHASE DETECTOR

As the EFM signal input from a disc includes the components of 2.1609 MHz, the EFM phase detector uses the bit

clock (/PBCK) of 4.3218 MHz, to detect the phase of this signal.

This PBCK detects the phase at the edge of the EFM signal and the result is output to the APDO1 or APDO2

terminals.

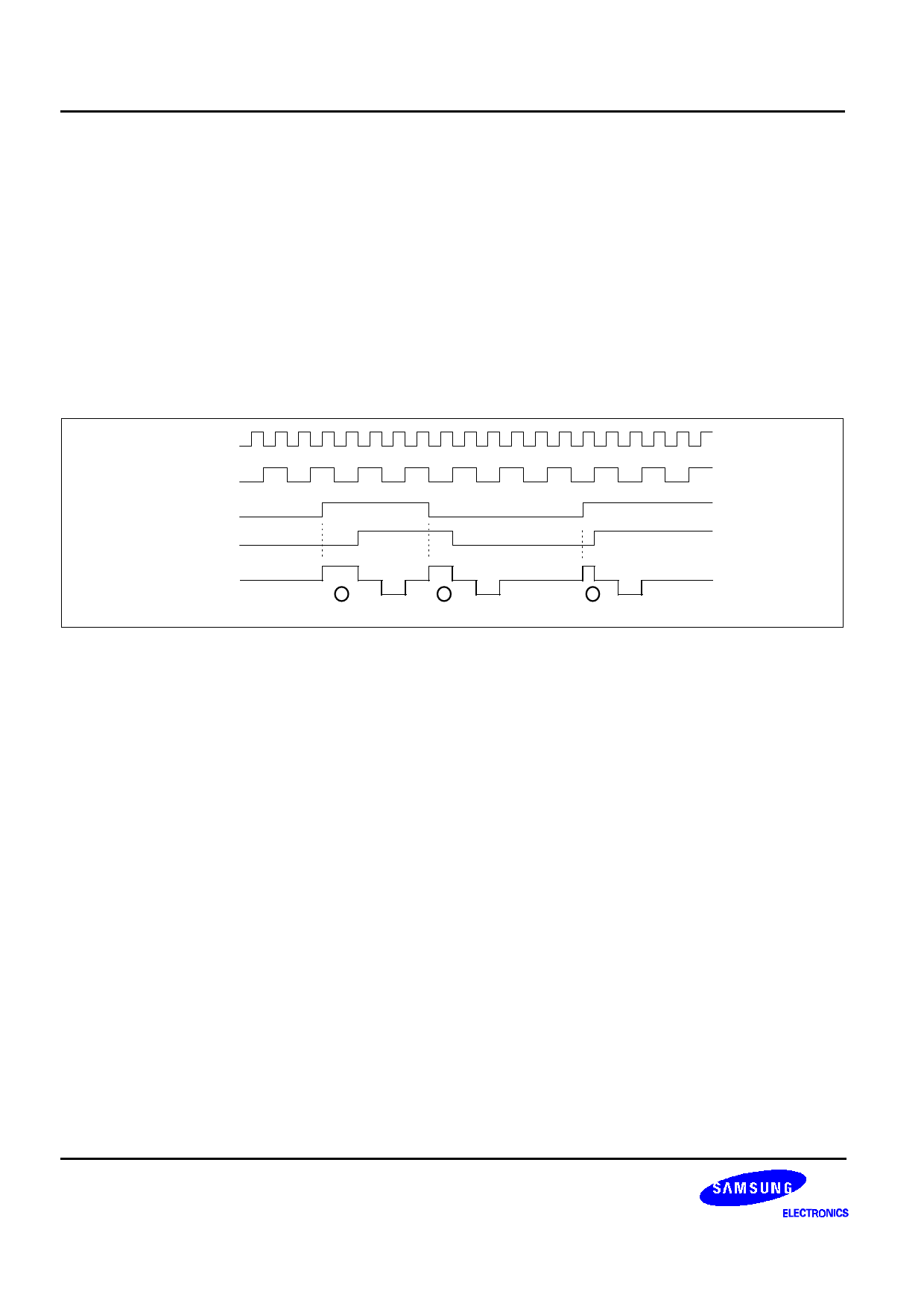

A. At Normal Operating

VCOI:

PBCK:

EFMI:

EFMD:

APDO:

Hi-Z

Hi-Z

1

2

Hi-Z

3

Hi-Z

In case of (1) : When the EFM signal is slower than VCO

In case of (2) : When the EFM signal is locked with VCO

In case of (3) : When the EFM signal is faster than VCO

Figure 6. Timing Chart of the EFM Phase Detector

B. At Abnormal Operating

If the HIPD of CNTL-Z is “H” and “L” of the LKFS is shorter than 3.5T (a period PBFR is T), the Hi-Z is output to the

APDO terminal as many as “L” , and if it is over 3.5T, the Hi-Z is output as many as 3.5T.

EFM DEMODULATOR

The 14-bit data is channeled through the circuit, and is de modulated to 8-bit data.

Demodulated data has two kinds of signals, One is subcode data and the other is audio data. They are respectively

input into the subcode block written in the internal 16K SRAM to perform error correction.

14