W83626D View Datasheet(PDF) - Winbond

Part Name

Description

Manufacturer

W83626D Datasheet PDF : 23 Pages

| |||

W83626F/W83626D/W83626G

5. PIN DESCRIPTION

I/O12t

- TTL level bi-directional pin with 12 m A source-sink capability

I/O24t

- TTL level bi-directional pin with 24 m A source-sink capability

I/O12tp3

I/O24tp3

- 3.3V TTL level bi-directional pin with 12 m A source-sink capability

- 3.3V TTL level bi-directional pin with 24 m A source-sink capability

I/OD12t

I/O24t

- TTL level bi-directional pin open drain output with 12 m A sink capability

- TTL level bi-directional pin with 24 m A source-sink capability

OUT12

OUT24

- TTL level output pin with 12 m A source-sink capability

- TTL level output pin with 24 m A source-sink capability

O12p3

O24p3

- 3.3V TTL level output pin with 12 m A source-sink capability

- 3.3V TTL level output pin with 24 m A source-sink capability

OD12

OD24

- Open-drain output pin with 12 m A sink capability

- Open-drain output pin with 24 m A sink capability

INcs

INt

- CMOS level Schmitt-trigger input pin

- TTL level input pin

INtd

- TTL level input pin with internal pull down resistor

INtu

- TTL level input pin with internal pull up resistor

INts

- TTL level Schmitt-trigger input pin

INtsp3

- 3.3V TTL level Schmitt-trigger input pin

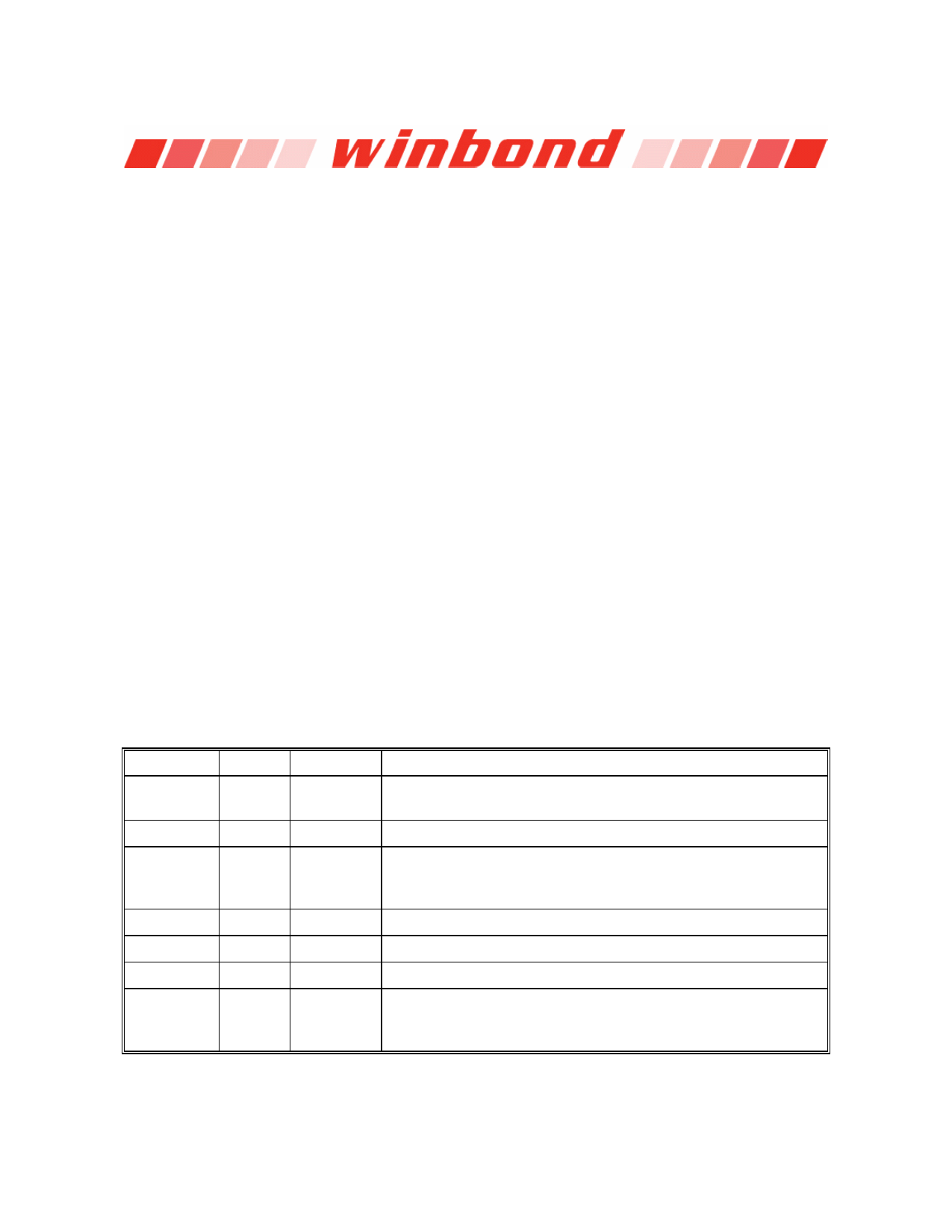

5.1 W83626F/G PIN DESCRIPTION

5.1.1 LPC Interface

SYMBOL

LAD[3:0]

LFRAME#

PIN

16-19

13

PCICLK

21

PCIRST#

14

SERIRQ

23

LDRQ#

22

PWRDN#

24

I/O

I/O12tp3

INtsp3

INt

INtsp3

I/OD12t

O12tp3

INtu

FUNCTION

These signal lines communicate address, control and data

information over the LPC bus between a host and a peripheral.

Indicates start of a new cycle or termination of a broken cycle.

PCICLK provides timing for all transactions on the LPC bus. All

LPC signals are sampled on the rising edge of PCICLK, and all

timing parameters are defined with respect to this edge.

Reset signal. It can connect to PCIRST# signal on the host.

Serial IRQ Input/Output.

Encoded DMA Request signal.

Power Down. The signal is active low according to CR 44 Bit

7and wake-up enable by hardware setting. There are eight

different power-down states (Power down Mode 3).

Publication Release Date: May 25, 2005

-5-

Revision A1