DSP16410C View Datasheet(PDF) - Agere -> LSI Corporation

Part Name

Description

Manufacturer

DSP16410C Datasheet PDF : 373 Pages

| |||

Data Addendum

May 2001

DSP16410C Digital Signal Processor

5 Ball Grid Array Information (continued)

5.1 208-Ball PBGA Package (continued)

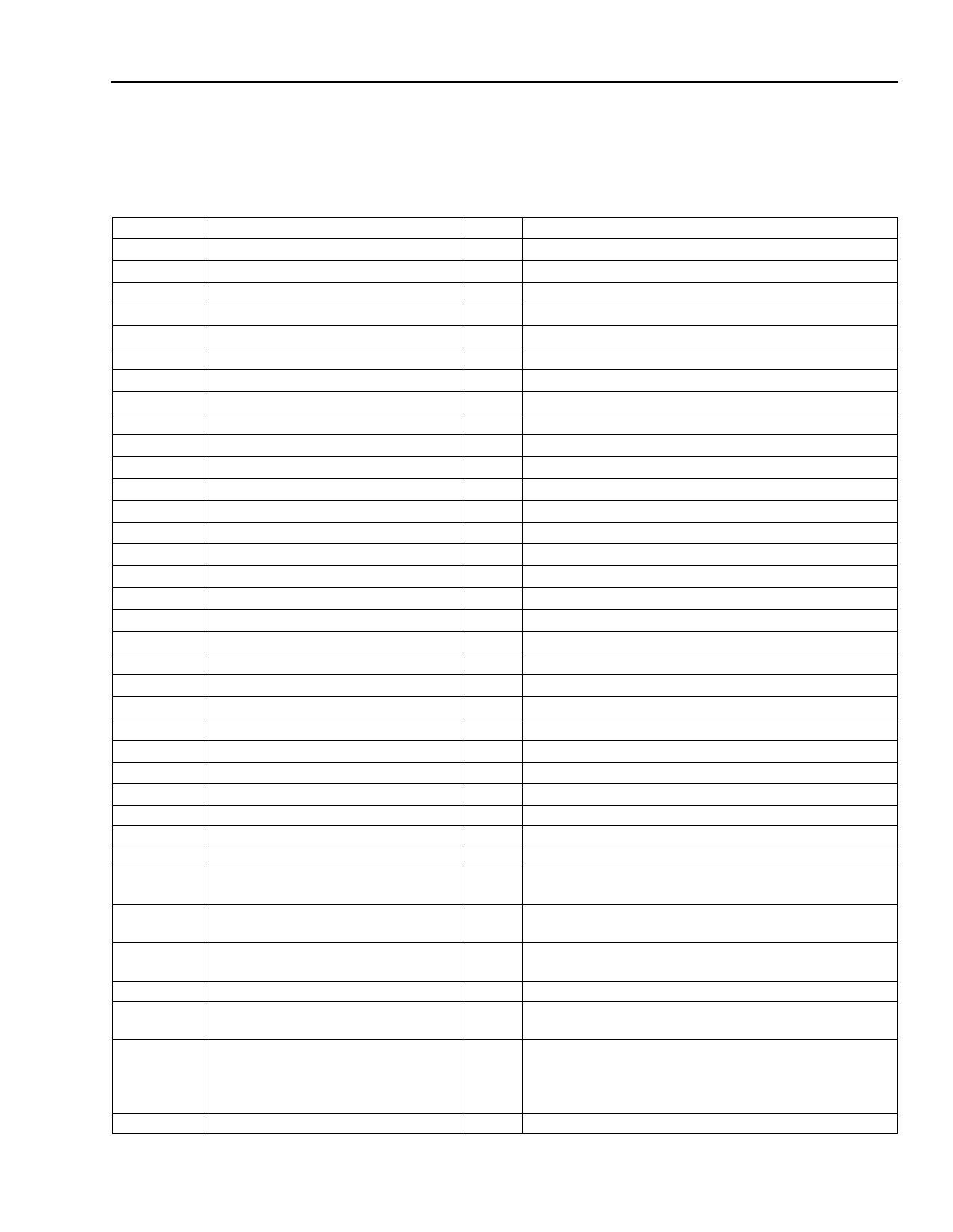

Table 2. 208-Ball PBGA Ball Assignments Sorted Alphabetically by Symbol (continued)

Symbol

POBE

PODS

PRDY

PRDYMD

PRWN

RSTN

SCK0

SCK1

SICK0

SICK1

SID0

SID1

SIFS0

SIFS1

SOCK0

SOCK1

SOD0

SOD1

SOFS0

SOFS1

TCK0

TCK1

TDI0

TDI1

TDO0

TDO1

TMS0

TMS1

TRAP

TRST0N

TRST1N

VDD1

VDD1A

VDD2

VSS

VSS1A

208-Ball PBGA Coordinate

P9

R10

N10

T10

R11

H4

M4

M14

K1

P16

M3

M13

K2

N15

L1

M15

M1

L15

L2

M16

F4

L13

G1

K16

F1

L16

G2

K15

J4

F3

L14

A9, B2, B15, C6, D4, D13, F14, J15,

L3, N4, N13, P11, R2, R8, R15

H1

A1, A16, C13, D3, D6, F13, G3, K14,

L4, N11, N14, P4, P7, T1, T16, C10

A13, A8, B5, D1, D10, E15, G7, G8,

G9, G10, G4, H7, H8, H9, H10, H16,

J1, J7, J8, J9, J10, K7, K8, K9, K10,

K13, M2, N7, N16, R12, T2, T4, T9

H3

Type

O

I

O

I

I

I

I

I

I/O

I/O

I

I

I/O

I/O

I/O

I/O

O/Z

O/Z

I/O

I/O

I

I

I

I

O

O

I

I

I/O

I

I

P

Description

PIU Output Buffer Empty Flag.

PIU Output Data Strobe.

PIU Host Ready.

PRDY Mode.

PIU Read/Write (negative assertion).

Device Reset (negative assertion).

External Clock for SIU0 Active Generator.

External Clock for SIU1 Active Generator.

SIU0 Input Clock.

SIU1 Input Clock.

SIU0 Input Data.

SIU1 Input Data.

SIU0 Input Frame Sync.

SIU1 Input Frame Sync.

SIU0 Output Clock.

SIU1 Output Clock.

SIU0 Output Data.

SIU1 Output Data.

SIU0 Output Frame Sync.

SIU1 Output Frame Sync.

JTAG Test Clock for CORE0.

JTAG Test Clock for CORE1.

JTAG Test Data Input for CORE0.

JTAG Test Data Input for CORE1.

JTAG Test Data Output for CORE0.

JTAG Test Data Output for CORE1.

JTAG Test Mode Select for CORE0.

JTAG Test Mode Select for CORE1.

TRAP/Breakpoint Indication.

JTAG TAP Controller Reset for CORE0 (negative asser-

tion).

JTAG TAP Controller Reset for CORE1 (negative asser-

tion).

Power Supply for Internal Circuitry.

P Power Supply for PLL Circuitry.

P Power Supply for External Circuitry (I/O).

G Ground.

G Ground for PLL Circuitry.

Agere Systems Inc.

9