IT66121FN View Datasheet(PDF) - ITE Tech. INC.

Part Name

Description

Manufacturer

IT66121FN Datasheet PDF : 39 Pages

| |||

IT66121FN

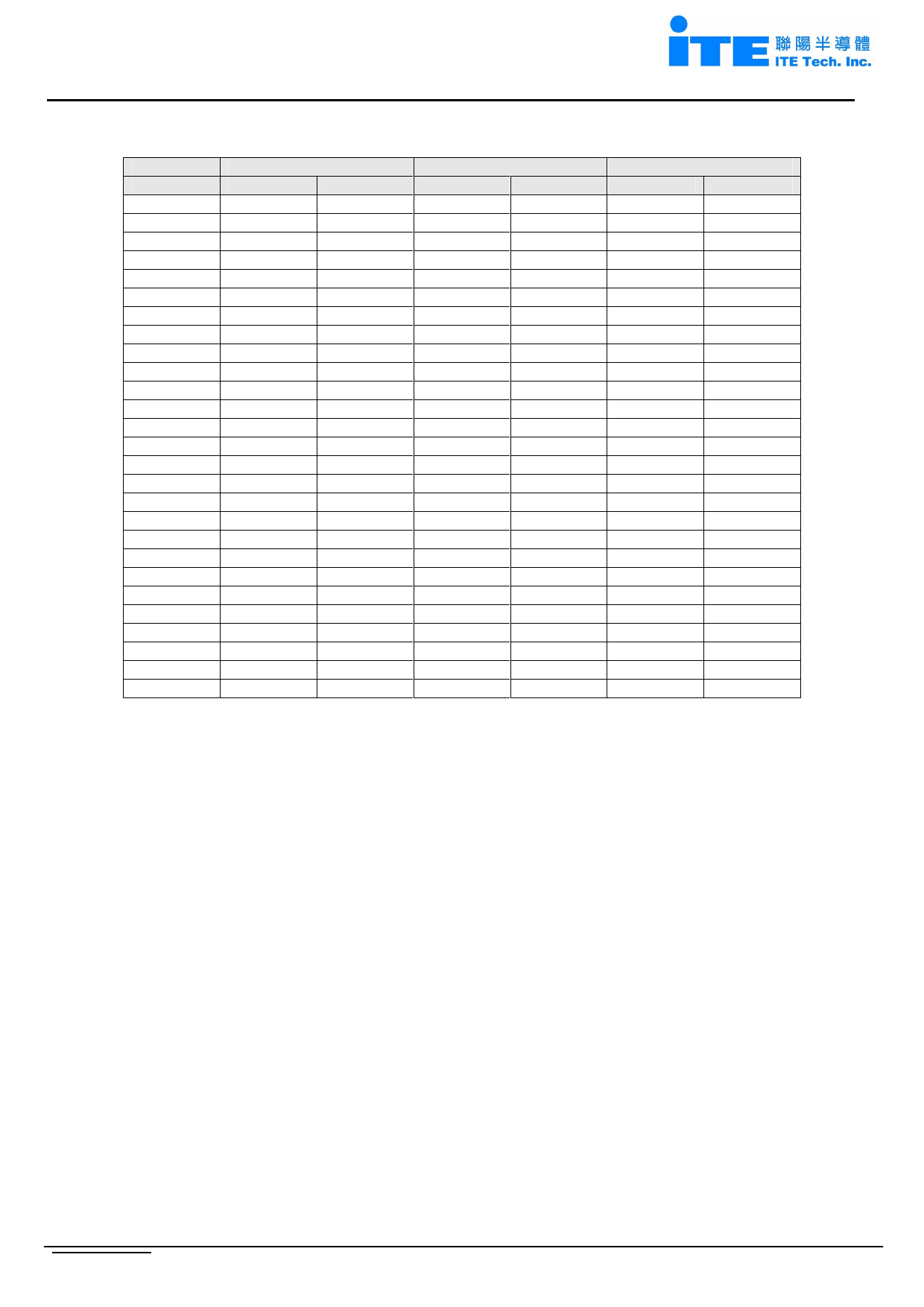

Non-sequential IO mode of 8/10/12-bit YCbCr422

Pin Name

D0

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D20

D21

D22

D23

HSYNC

VSYNC

DE

YCbCr 4:2:2 8-bit

1st PCLK 2nd PCLK

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

C0

Y0

C1

Y1

C2

Y2

C3

Y3

C4

Y4

C5

Y5

C6

Y6

C7

Y7

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

YCbCr 4:2:2 10-bit

1st PCLK 2nd PCLK

grounded grounded

grounded grounded

C0

Y0

C1

Y1

grounded grounded

grounded grounded

grounded grounded

grounded grounded

C2

Y2

C3

Y3

C4

Y4

C5

Y5

C6

Y6

C7

Y7

C8

Y8

C9

Y9

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

YCbCr 4:2:2 12-bit

Pixel#2N Pixel#2N+1

C0

Y0

C1

Y1

C2

Y2

C3

Y3

grounded grounded

grounded grounded

grounded grounded

grounded grounded

C4

Y4

C5

Y5

C6

Y6

C7

Y7

C8

Y9

C9

Y9

C10

Y10

C11

Y11

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

grounded grounded

Table 10. Mappings of 8/10/12-bit YCbCr422 non-sequential IO mode

In additional to the previous input formats, there are three options can be supported by the IT66121.

DE-only option can be used for those input formats without H/VSync information. Dual-edge triggering

with half bus width option can be used to reduce the necessary bus width and dual-edge triggering

with half pixel clock option allows half input pixel clock. No all the input formats listed above can

support three options and please refer to the IT66121 programming guide for more information. Some

examples shown below are the corresponding timing relations when these options are enabled.

www.ite.com.tw

Nov-2011 Rev:0.99 30/39