W78354 View Datasheet(PDF) - Winbond

Part Name

Description

Manufacturer

W78354 Datasheet PDF : 45 Pages

| |||

W78E354

Pin Description, continued

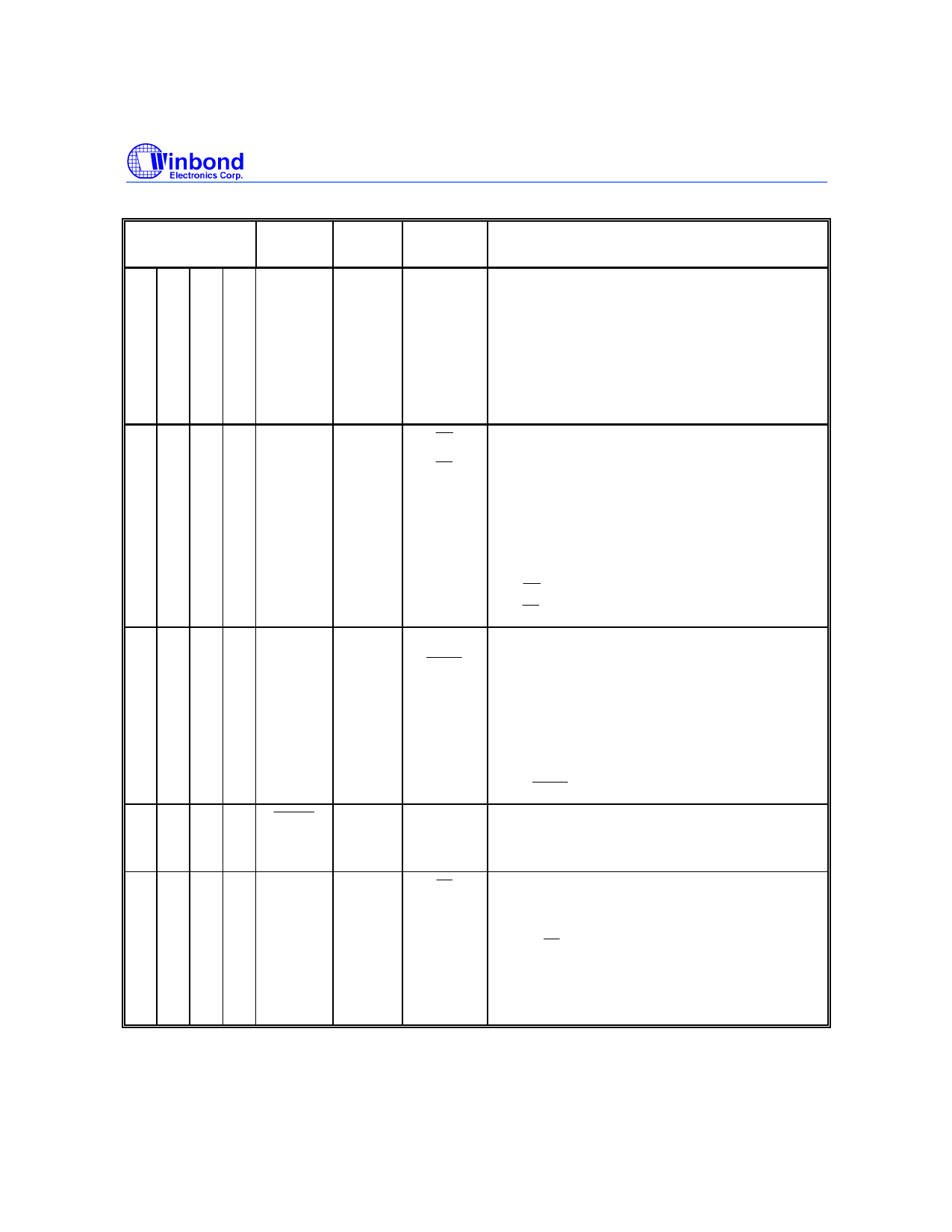

PIN NO.

68P 64P 48P 40P

PIN

NAME

44 42 - -

45 43 - -

P4.0

P4.1

53 51 - -

P4.2

55 - - -

64 - - -

1- - -

2- - -

P4.3

P4.4

P4.5

P4.6

25 23 17 15

HIN

26 24 18 16

VIN

I/O

TYPE

O/P

I/P

27 25 19 17

HOUT

I/O

28 26 20 18

VOUT

33 31 24 22 RESET

I/P

41 39 28 24 TestCLK

I/P

TEST

NAME

-

-

-

-

-

-

-

OE

CE

OECTRL

PROG

-

EA

FUNCTIONAL DESCRIPTION

Output port (Latch output).

Sink/Source current 2 mA/-2 mA.

HIN: Hsync/Composite sync input.

VIN: Vsync input.

Schmitt trigger I/P.

With Internal high value pull-down (about 200 KΩ).

No PMOS ESD diode.

---------------------------------------------------------

* In the Flash/RAM-test mode

(when the chip is in reset state):

HIN: OE input.

VIN: CE input.

HOUT: Hsync output.

VOUT: Vsync output with internal weak pull-up (above 200

KΩ).

Sink/Source current 4 mA/-4 mA.

---------------------------------------------------------

* In the Flash/RAM-test mode

(when the chip is in reset state):

HOUT: OECTRL input.

VOUT: PROG input.

Reset the controller (active low).

Schmitt trigger I/P.

With internal pull-up (about 30 KΩ).

Clock input while in internal (glue logic's) function test.

With internal pull-up (about 30 KΩ).

---------------------------------------------------------

* If the EA (TestCLK) pin is pulled low when the chip is

being reset, and remains low for at least 24 clock periods

after the reset, the CPU will execute from the external

program memory regardless of the PC value. i.e., the CPU is

forced to enter the functional test mode.

-8-