SST25VF032B View Datasheet(PDF) - Silicon Storage Technology

Part Name

Description

Manufacturer

SST25VF032B Datasheet PDF : 28 Pages

| |||

Data Sheet

Write-Enable (WREN)

The Write-Enable (WREN) instruction sets the Write-

Enable-Latch bit in the Status Register to ‘1’ allowing Write

operations to occur. The WREN instruction must be exe-

cuted prior to any Write (Program/Erase) operation. The

WREN instruction may also be used to allow execution of

the Write-Status-Register (WRSR) instruction; however,

32 Mbit SPI Serial Flash

SST25VF032B

the Write-Enable-Latch bit in the Status Register will be

cleared upon the rising edge CE# of the WRSR instruction.

CE# must be driven high before the WREN instruction is

executed.

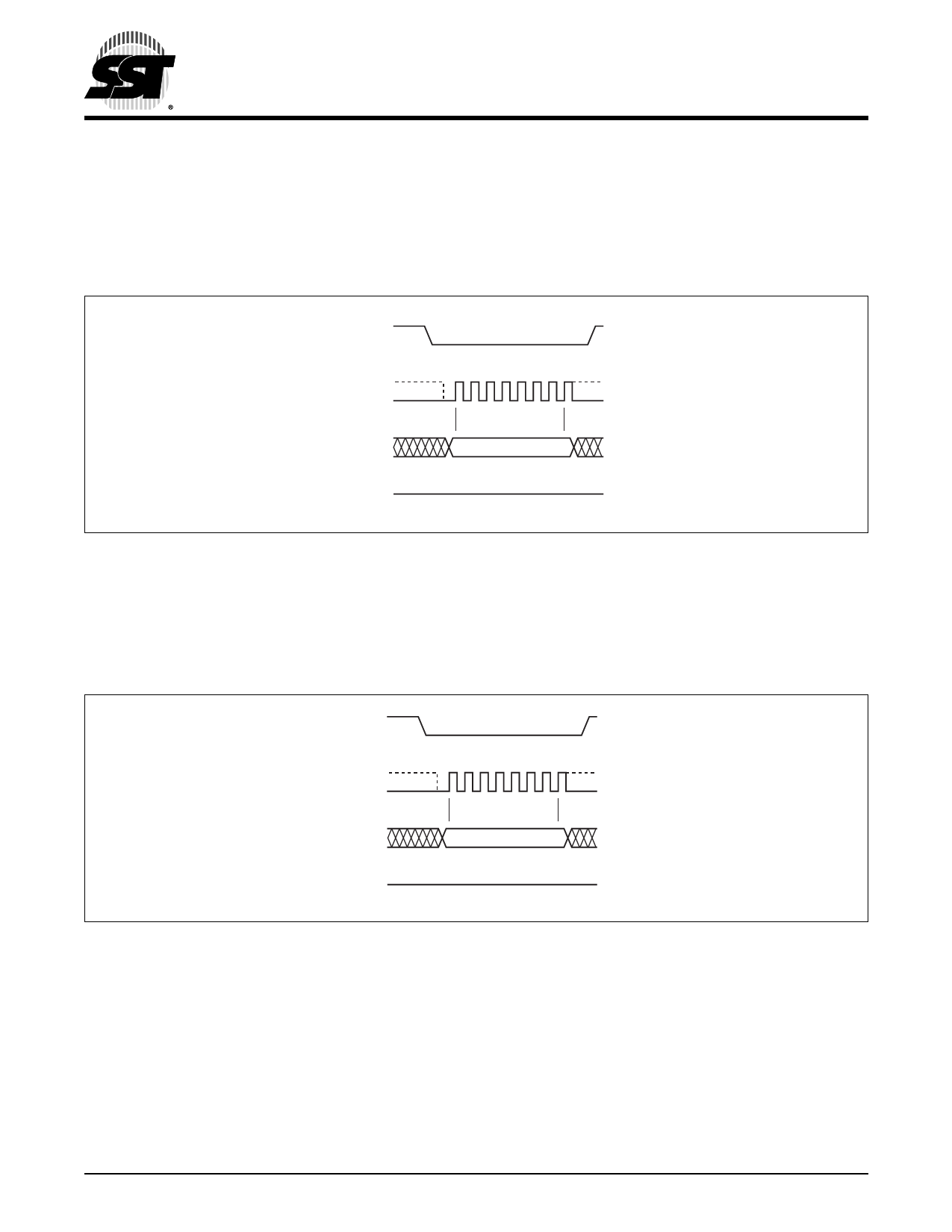

CE#

MODE 3

SCK MODE 0

0 1 2345 6 7

SI

06

MSB

SO

HIGH IMPEDANCE

1327 F18.0

FIGURE 17: Write Enable (WREN) Sequence

Write-Disable (WRDI)

The Write-Disable (WRDI) instruction resets the Write-

Enable-Latch bit and AAI bit to ‘0,’ therefore, preventing any

new Write operations. The WRDI instruction will not termi-

nate any programming operation in progress. Any program

operation in progress may continue up to TBP after execut-

ing the WRDI instruction. CE# must be driven high before

the WRDI instruction is executed.

CE#

MODE 3

SCK MODE 0

0 1 2345 6 7

SI

04

MSB

SO

HIGH IMPEDANCE

1327 F19.0

FIGURE 18: Write Disable (WRDI) Sequence

Enable-Write-Status-Register (EWSR)

The Enable-Write-Status-Register (EWSR) instruction

arms the Write-Status-Register (WRSR) instruction and

opens the status register for alteration. The Write-Status-

Register instruction must be executed immediately after the

execution of the Enable-Write-Status-Register instruction.

This two-step instruction sequence of the EWSR instruc-

tion followed by the WRSR instruction works like software

data protection (SDP) command structure which prevents

any accidental alteration of the status register values. CE#

must be driven low before the EWSR instruction is entered

and must be driven high before the EWSR instruction is

executed.

©2009 Silicon Storage Technology, Inc.

16

S71327-03-000

05/09