LC75817NW View Datasheet(PDF) - SANYO -> Panasonic

Part Name

Description

Manufacturer

LC75817NW

LC75817NW Datasheet PDF : 43 Pages

| |||

LC75817NE, 75817NW

Specifications

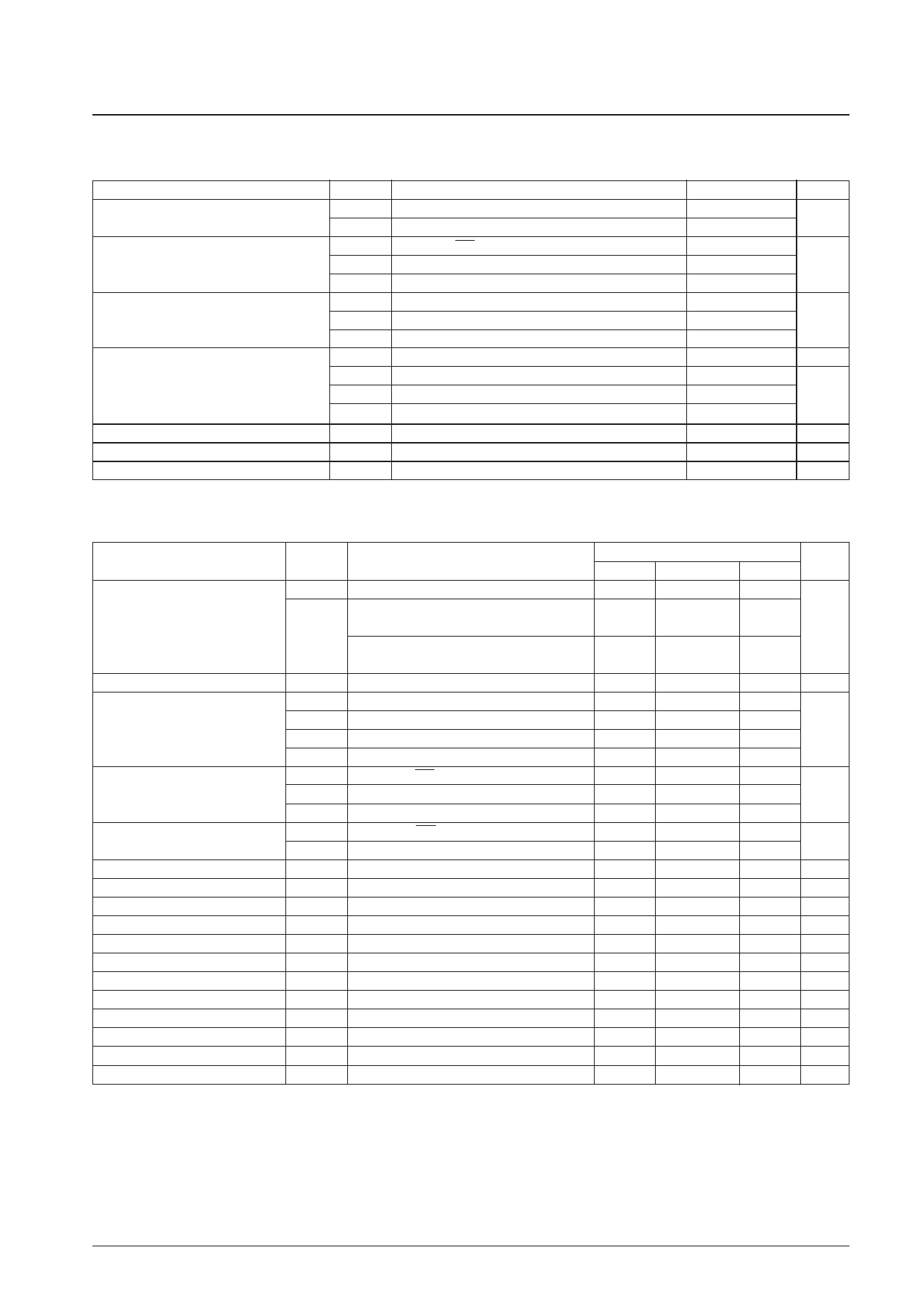

Absolute Maximum Ratings at Ta = 25°C, VSS = 0 V

Parameter

Maximum supply voltage

Input voltage

Output voltage

Output current

Allowable power dissipation

Operating temperature

Storage temperature

Symbol

VDD max

VLCD max

VIN1

VIN2

VIN3

VOUT1

VOUT2

VOUT3

IOUT1

IOUT2

IOUT3

IOUT4

Pd max

Topr

Tstg

Conditions

VDD

VLCD

CE, CL, DI, INH

OSCI, KI1 to KI5, TEST

VLCD1, VLCD2, VLCD3, VLCD4

DO

OSCO, KS1 to KS6, P1 to P4

VLCD0, S1 to S60, COM1 to COM10

S1 to S60

COM1 to COM10

KS1 to KS6

P1 to P4

Ta = 85°C

Ratings

Unit

–0.3 to +7.0

V

–0.3 to +11.0

–0.3 to +7.0

–0.3 to VDD + 0.3

V

–0.3 to VLCD + 0.3

–0.3 to +7.0

–0.3 to VDD + 0.3

V

–0.3 to VLCD + 0.3

300

µA

3

1

mA

5

200

mW

–40 to +85

°C

–55 to +125

°C

Allowable Operating Ranges at Ta = –40 to +85°C, VSS = 0 V

Parameter

Supply voltage

Symbol

Conditions

VDD

VLCD

VDD

VLCD: When the display contrast adjustment circuit

is used.

VLCD: When the display contrast adjustment circuit

is not used.

min

4.5

7.0

Ratings

typ

4.5

Unit

max

6.0

10.0

V

10.0

Output voltage

Input voltage

Input high level voltage

Input low level voltage

Recommended external resistance

Recommended external capacitance

Guaranteed oscillation range

Data setup time

Data hold time

CE wait time

CE setup time

CE hold time

High level clock pulse width

VLCD0

VLCD1

VLCD2

VLCD3

VLCD4

VIH1

VIH2

VIH3

VIL1

VIL2

ROSC

COSC

fOSC

tds

tdh

tcp

tcs

tch

tøH

VLCD0

VLCD1

VLCD2

VLCD3

VLCD4

CE, CL, DI, INH

OSCI

KI1 to KI5

CE, CL, DI, INH, KI1 to KI5

OSCI

OSCI, OSCO

OSCI, OSCO

OSC

CL, DI: Figure 2

CL, DI: Figure 2

CE, CL: Figure 2

CE, CL: Figure 2

CE, CL: Figure 2

CL: Figure 2

VLCD4+4.5

VLCD

V

3/4 (VLCD0–VLCD4) VLCD0

2/4 (VLCD0–VLCD4) VLCD0

V

1/4 (VLCD0–VLCD4) VLCD0

0

1.5

0.8 VDD

0.7 VDD

0.6 VDD

0

0

6.0

VDD

V

VDD

0.2 VDD

V

0.3 VDD

33

kΩ

220

pF

150

300

600 kHz

160

ns

160

ns

160

ns

160

ns

160

ns

160

ns

Low level clock pulse width

tøL

CL: Figure 2

160

ns

DO output delay time

DO rise time

tdc

DO, RPU = 4.7kΩ, CL = 10pF*1: Figure 2

tdr

DO, RPU = 4.7kΩ, CL = 10pF*1: Figure 2

1.5

µs

1.5

µs

Note: *1. Since DO is an open-drain output, these times depend on the values of the pull-up resistor RPU and the load capacitance CL.

No. 6144-4/43