SAF-C167CR-16RM View Datasheet(PDF) - Siemens AG

Part Name

Description

Manufacturer

SAF-C167CR-16RM Datasheet PDF : 67 Pages

| |||

C167CR-16RM 20Dec96@09:25h Intermediate Version

Functional Description

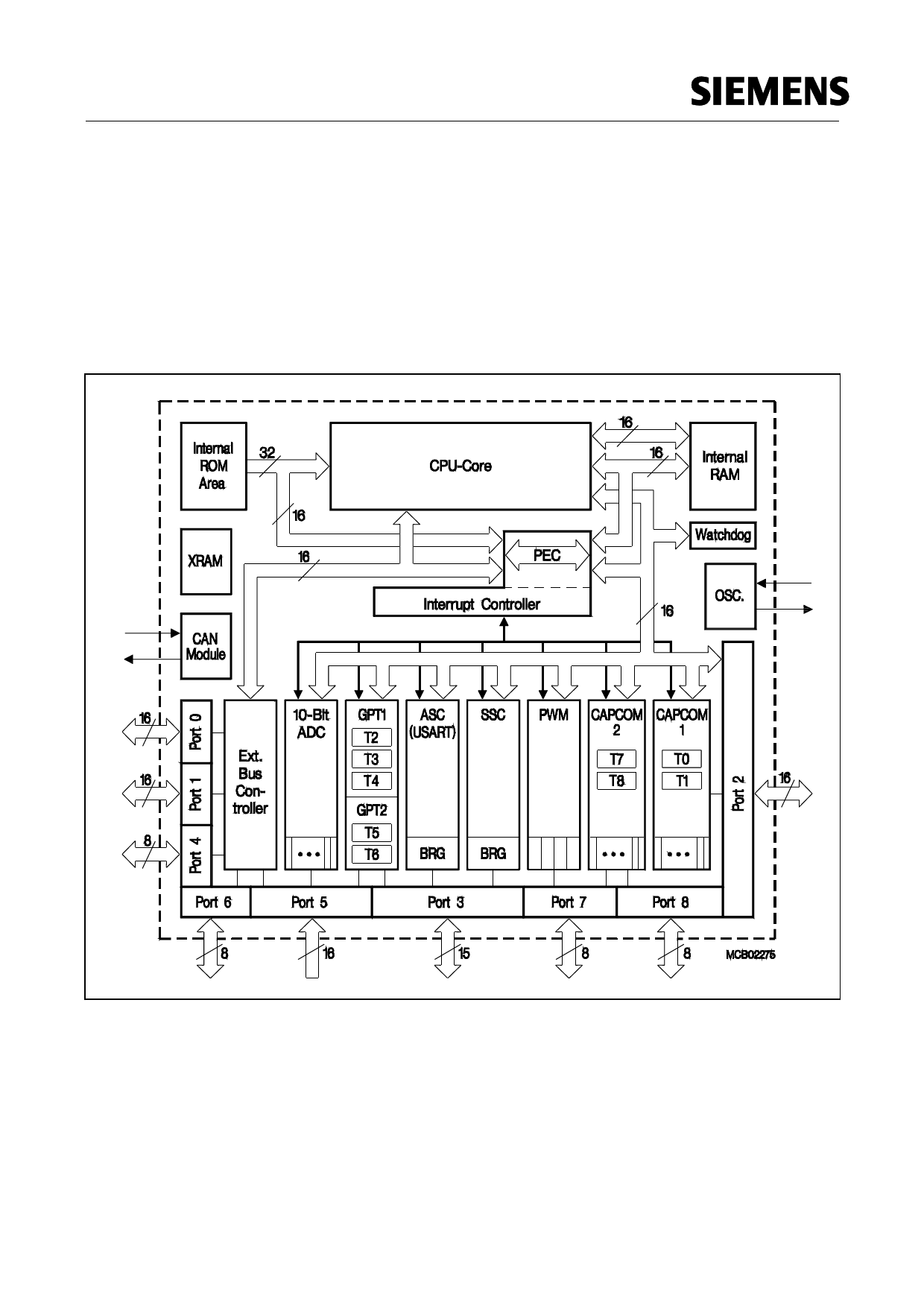

The architecture of the C167CR-16RM combines advantages of both RISC and CISC processors

and of advanced peripheral subsystems in a very well-balanced way. The following block diagram

gives an overview of the different on-chip components and of the advanced, high bandwidth internal

bus structure of the C167CR-16RM.

Note: All time specifications refer to a CPU clock of 20 MHz

(see definition in the AC Characteristics section).

Figure 3

Block Diagram

Semiconductor Group

10