SAF-C167CR-16RM View Datasheet(PDF) - Siemens AG

Part Name

Description

Manufacturer

SAF-C167CR-16RM Datasheet PDF : 67 Pages

| |||

C167CR-16RM 20Dec96@09:25h Intermediate Version

(CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via

a programmable prescaler or with external signals. The count direction (up/down) for each timer is

programmable by software or may additionally be altered dynamically by an external signal on a

port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of

timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on a port pin (T6OUT).

The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM timers T0 or

T1, and to cause a reload from the CAPREL register. The CAPREL register may capture the

contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN),

and timer T5 may optionally be cleared after the capture procedure. This allows absolute time

differences to be measured or pulse multiplication to be performed without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of GPT1 timer

T3’s inputs T3IN and/or T3EUD. This is especially advantageous when T3 operates in Incremental

Interface Mode.

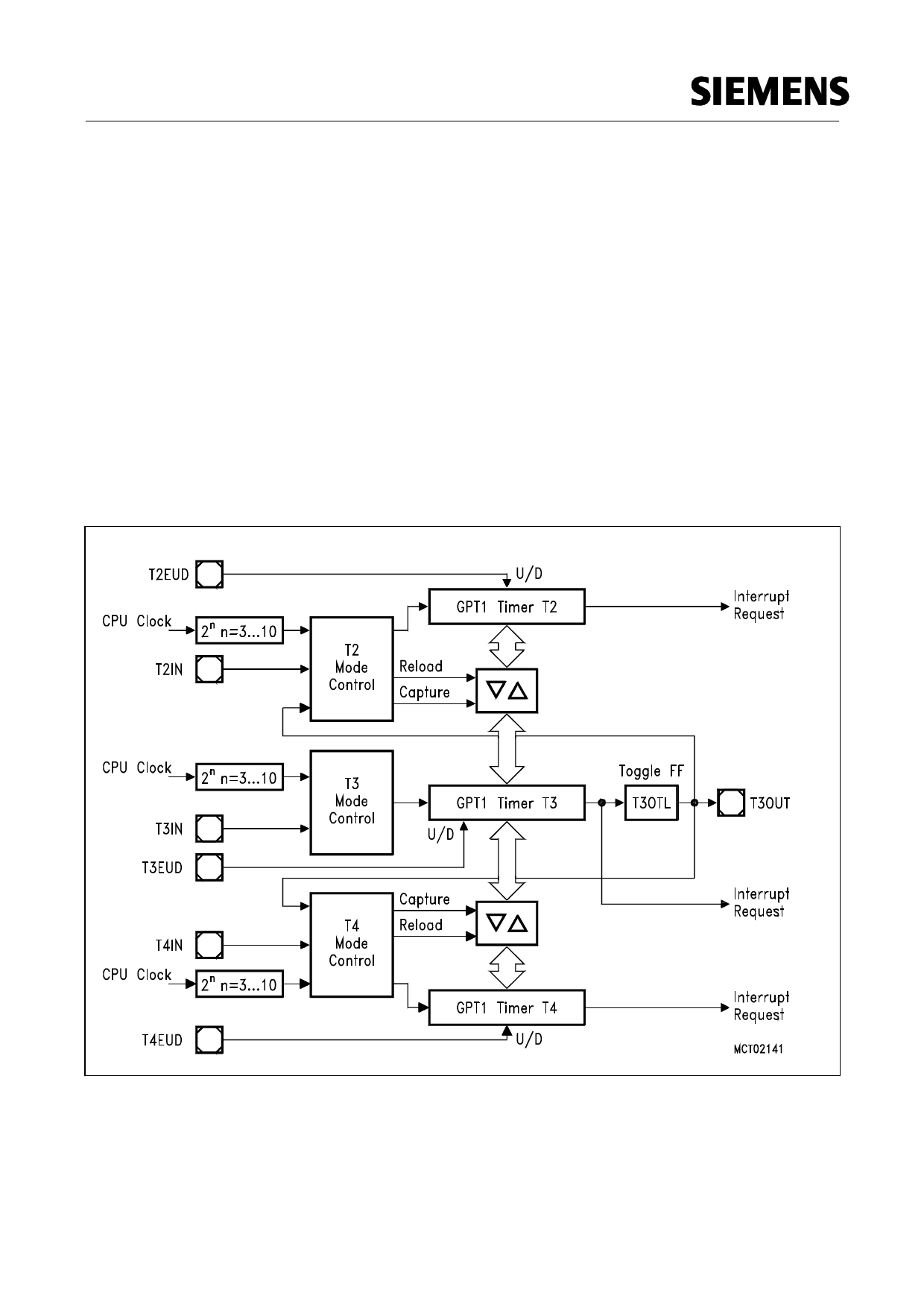

Figure 6

Block Diagram of GPT1

Semiconductor Group

22