SAF-C167CR-16RM View Datasheet(PDF) - Siemens AG

Part Name

Description

Manufacturer

SAF-C167CR-16RM Datasheet PDF : 67 Pages

| |||

20Dec96@09:25h Intermediate Version

C167CR-16RM

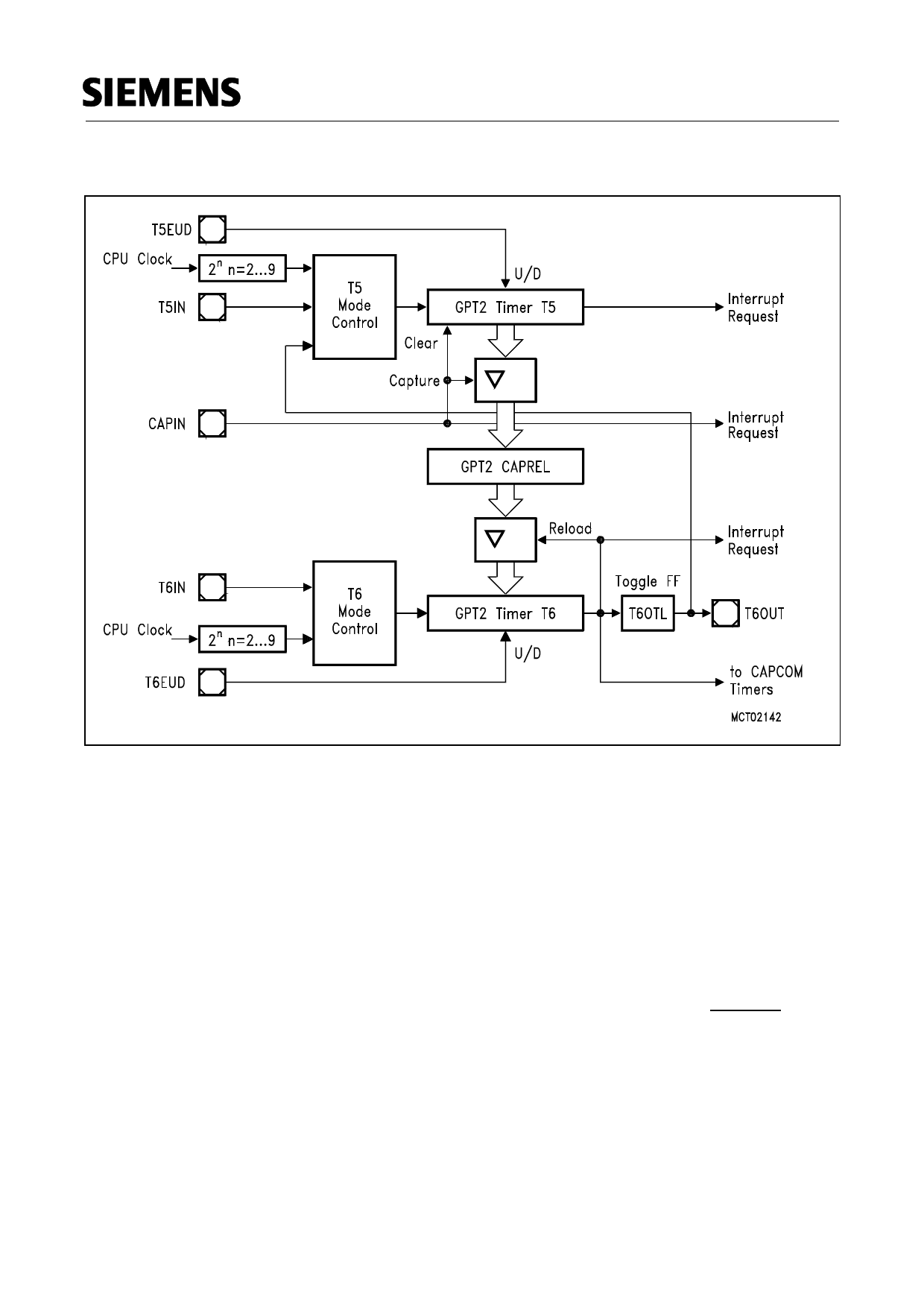

Figure 7

Block Diagram of GPT2

Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechanisms which have been implemented to

prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after a reset of the chip, and can only be disabled in the time

interval until the EINIT (end of initialization) instruction has been executed. Thus, the chip’s start-up

procedure is always monitored. The software has to be designed to service the Watchdog Timer

before it overflows. If, due to hardware or software related failures, the software fails to do so, the

Watchdog Timer overflows and generates an internal hardware reset and pulls the RSTOUT pin low

in order to allow external hardware components to be reset.

The Watchdog Timer is a 16-bit timer, clocked with the system clock divided either by 2 or by 128.

The high byte of the Watchdog Timer register can be set to a prespecified reload value (stored in

WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced

by the application software, the high byte of the Watchdog Timer is reloaded. Thus, time intervals

between 25 µs and 420 ms can be monitored (@ 20 MHz). The default Watchdog Timer interval

after reset is 6.55 ms (@ 20 MHz).

23

Semiconductor Group