DSP56367P View Datasheet(PDF) - Freescale Semiconductor

Part Name

Description

Manufacturer

DSP56367P Datasheet PDF : 100 Pages

| |||

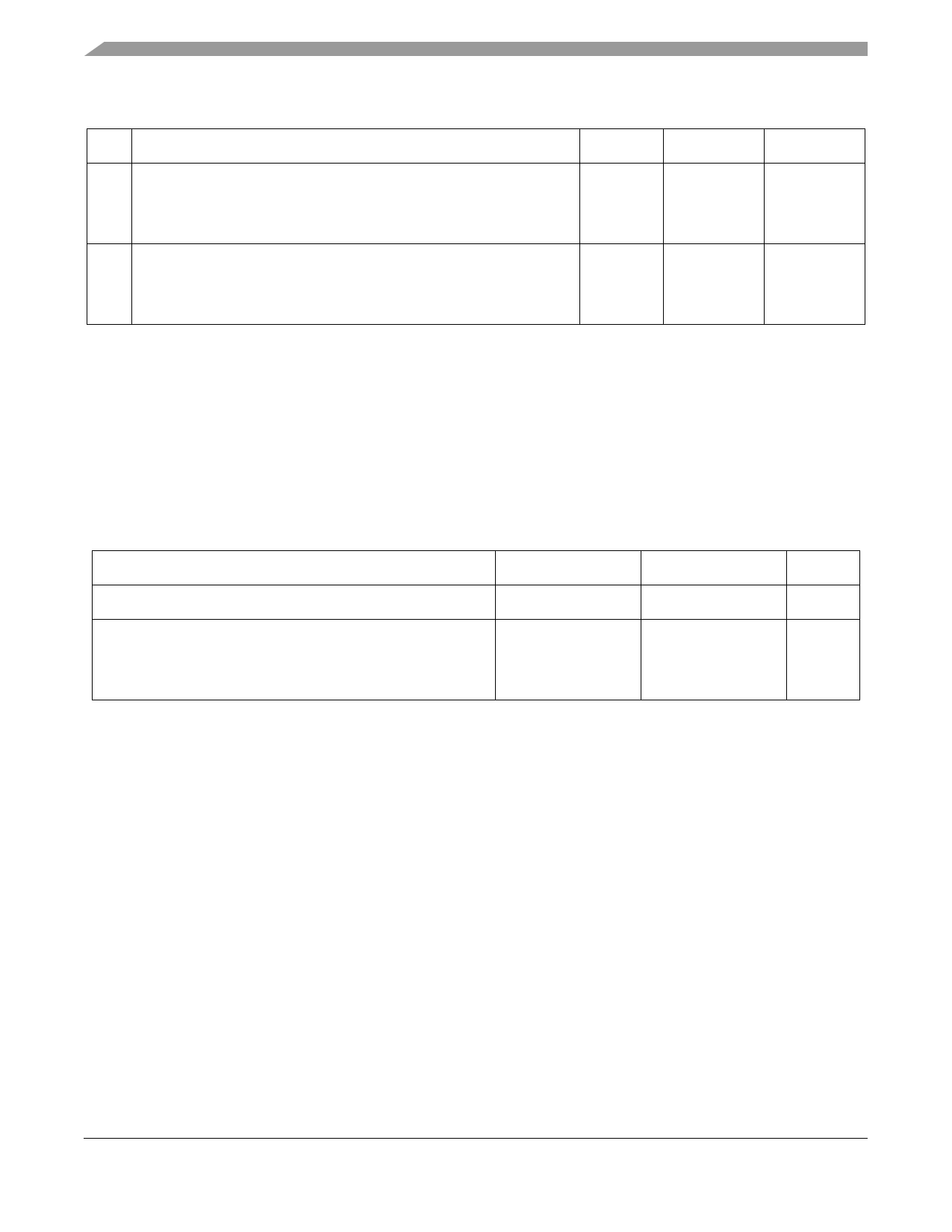

Phase Lock Loop (PLL) Characteristics

Table 3-5 Clock Operation (continued)

No.

Characteristics

Symbol

Min

Max

4 EXTAL cycle time2

• With PLL disabled

• With PLL enabled

ETC

6.7 ns

∞

6.7 ns

273.1 µs

7 Instruction cycle time = ICYC = TC4

• With PLL disabled

• With PLL enabled

ICYC

13.33 ns

6.67 ns

∞

8.53 µs

1 Measured at 50% of the input transition.

2 The maximum value for PLL enabled is given for minimum VCO and maximum MF.

3 The indicated duty cycle is for the specified maximum frequency for which a part is rated. The minimum clock high or low time

required for correct operation, however, remains the same at lower operating frequencies; therefore, when a lower clock

frequency is used, the signal symmetry may vary from the specified duty cycle as long as the minimum high time and low time

requirements are met.

4 The maximum value for PLL enabled is given for minimum VCO and maximum DF.

3.8 Phase Lock Loop (PLL) Characteristics

Table 3-6 PLL Characteristics

Characteristics

Min

Max

Unit

VCO frequency when PLL enabled (MF × Ef × 2/PDF)

30

300

MHz

PLL external capacitor (PCAP pin to VCCP) (CPCAP1)

• @ MF ≤ 4

• @ MF > 4

pF

(MF × 580) − 100

(MF × 780) − 140

MF × 830

MF × 1470

1 CPCAP is the value of the PLL capacitor (connected between the PCAP pin and VCCP). The recommended value in pF for

CPCAP can be computed from one of the following equations:

(MF x 680)-120, for MF ≤ 4, or

MF x 1100, for MF > 4.

DSP56367 Technical Data, Rev. 2.1

3-6

Freescale Semiconductor